# There is never enough dynamic range DEPFET active pixel sensors with analog signal compression

## **Stefan Michael Aschauer**

Vollständiger Abdruck der von der Fakultät für Physik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation

Vorsitzender: Univ.-Prof. Dr. N. Kaiser

Prüfer der Dissertation: 1. Univ.-Prof. Dr. L. Oberauer

2. Priv. Doz. Dr. A. Ulrich

Die Dissertation wurde am 27.11.2013 bei der Technischen Universität München eingereicht und durch die Fakultät für Physik am 04.02.2014 angenommen.

## **Abstract**

In recent years, the continuous exploration of accelerator-based X-ray sources has led to the development of what is now the 4th generation: so-called free electron lasers (FELs). FELs provide coherent, extremely intense and ultra-short X-ray flashes that bring completely new experimental opportunities to various fields of research including material science, chemistry, biology and physics.

Within the DSSC project, a new DEPFET active pixel sensor is being developed. It is dedicated to X-ray imaging at the European X-ray free electron laser facility currently under construction in Hamburg. In order to resolve the enormous contrasts occurring in FEL experiments, this new DSSC-DEPFET sensor is designed for nonlinear amplification, that is, high gain for low intensities in order to obtain single-photon detection capability, and reduced gain for high intensities to achieve high dynamic range for several thousand photons per pixel and frame.

This thesis addresses all crucial aspects of the DSSC-DEPFET development, including the fabrication process of the sensor as well as the experimental characterization of the first prototypes with respect to their amplification properties. In particular, experiments have been done on the impact of different layouts and changing operating conditions on the detector response. Moreover, a new internal charge injection mechanism will be presented which allows for fast, in-situ, pixel-wise calibration of the nonlinear detector response for large arrays of DSSC-DEPFET pixels. In addition to the measurement results, 2D and 3D device simulations allow for a better understanding of the complex physical processes during the operation of the DEPFET.

Finally, the findings of this thesis will form the basis for identifying the optimization potentials of DSSC prototypes as well as for presenting the expected performance of the next generation of DSSC-DEPFET devices.

# Zusammenfassung

In den letzten Jahren führte die kontinuierliche Weiterentwicklung der beschleunigerbasierten Röntgenlichtquellen zur vierten und neuesten Generation, den sogenannten Freien-Elektronen-Lasern (FEL). Die FELs erzeugen kohärente, extrem intensive und ultrakurze Röntgenblitze, die völlig neue experimentelle Möglichkeiten in verschiedensten Bereichen der Wissenschaft, unter anderem in den Materialwissenschaften, der Chemie, der Biologie und der Physik, eröffnen werden.

Im Rahmen des DSSC Projekts wird für den europäischen XFEL, der derzeit in Hamburg gebaut wird, ein neuartiger aktiver DEPFET Pixelsensor zur bildgebenden Messung von Röntgenstrahlung entwickelt. Um die enormen Kontraste, die bei FEL Experimenten auftreten, überhaupt auflösen zu können, soll der neuartige DSSC-DEPFET Sensor eine nichtlineare Verstärkung aufweisen. Dabei soll eine hohe Verstärkung für kleine Signale den Nachweis einzelner niederenergetischer Photonen ermöglichen und eine reduzierte Verstärkung für große Signale den dynamischen Bereich auf mehrere Tausend Photonen pro Pixel und Bild erweitern.

Die folgende Arbeit befasst sich mit allen relevanten Aspekten der DSSC Sensorentwicklung. Dies umfasst sowohl den Herstellungsprozess der Sensoren als auch die experimentelle Charakterisierung der ersten Prototypen hinsichtlich ihrer Verstärkungseigenschaften. Insbesondere werden die Auswirkungen von Layout-Variationen und wechselnden Betriebsbedingungen auf die Detektorantwort untersucht. Darüber hinaus wird ein neuer Mechanismus einer internen Ladungsinjektion vorgestellt, die eine schnelle und pixelweise in-situ Kalibrierung der nichtlinearen Verstärkungskurve für große Arrays von DEPFET Pixeln ermöglicht. Neben den Messergebnissen werden 2D und 3D Bauelementesimulationen vorgestellt, die ein besseres Verständnis der beteiligten physikalischen Prozesse während des Betriebs des DEPFET erlauben.

Auf Basis der gezeigten Untersuchungen werden schließlich Optimierungspotenziale aufgezeigt und die zu erwartenden Eigenschaften der nächsten Bauelementegeneration zusammengefasst.

# **Contents**

| 1. | Intro | Dduction                                                 | 1  |

|----|-------|----------------------------------------------------------|----|

| 2. | The   | European X-ray free electron laser                       | 3  |

|    | 2.1.  | Working principle of free electron lasers                | 3  |

|    | 2.2.  | New Opportunities at the FELs                            | 8  |

|    |       | 2.2.1. Imaging of biological samples                     | 9  |

|    |       | 2.2.2. Filming chemical reactions with atomic resolution | 10 |

|    | 2.3.  | Detector requirements of the European XFEL               | 11 |

|    |       | 2.3.1. Single-photon resolution and high dynamic range   | 11 |

|    |       | 2.3.2. Readout speed                                     | 12 |

|    |       | 2.3.3. Radiation hardness                                | 13 |

|    | 2.4.  | DSSC detector system                                     | 13 |

| 3. | DEF   | PFET concept                                             | 19 |

|    | 3.1.  | Interaction of radiation with matter                     | 19 |

|    |       | 3.1.1. Electromagnetic radiation                         | 19 |

|    |       | 3.1.2. Particle radiation                                | 22 |

|    | 3.2.  | The DEPFET working principle                             | 23 |

|    | 3.3.  | Noise considerations                                     | 27 |

|    |       | 3.3.1. Fano noise                                        | 27 |

|    |       | 3.3.2. Thermal noise                                     | 28 |

|    |       | 3.3.3. 1/f noise                                         | 28 |

|    |       | 3.3.4. Shot noise                                        | 29 |

|    |       | 3.3.5. Energy resolution                                 | 30 |

|    | 3.4.  | Matrix operation                                         | 32 |

|    | 3.5.  | Fields of application                                    | 36 |

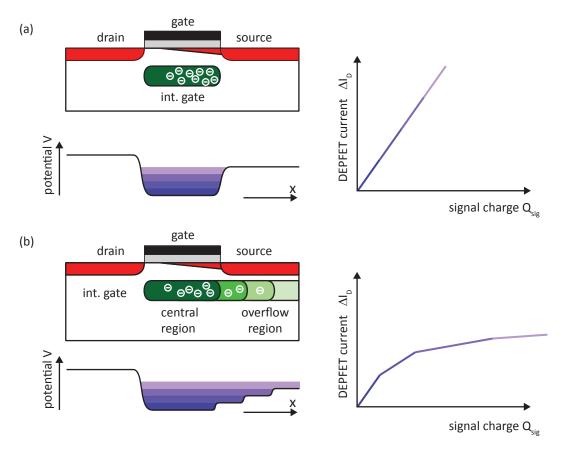

|    | 3.6.  | Functional principle of new DSSC-DEPFET                  | 39 |

| 4. | DSS   | C-DEPFET prototypes                                      | 41 |

|    | 4.1.  | Prototype fabrication                                    | 41 |

|    |       | 4.1.1. Technology                                        | 42 |

|    |       | 4.1.2. Layout                                            | 45 |

|    | 4.2.  | Experimental setup                                       | 48 |

|    | 4.3.  | Nonlinear response curve                                 | 50 |

|    |       | 4.3.1. Validation of nonlinear amplification             | 50 |

|    |       | 4.3.2.   | Measurements on layout variants                          | 57  |

|----|-------|----------|----------------------------------------------------------|-----|

|    |       |          | 4.3.2.1. Traditional variants                            | 58  |

|    |       |          | 4.3.2.2. New variants                                    | 60  |

|    |       |          | 4.3.2.3. Comparison with simulations                     | 62  |

|    |       |          | 4.3.2.4. 2D simulations with area correction             | 65  |

|    |       |          | 4.3.2.5. 3D corrections                                  | 68  |

|    |       |          | 4.3.2.6. Conclusion                                      | 73  |

|    |       | 4.3.3.   | Variation of DEPFET supply voltages                      | 78  |

|    |       |          | 4.3.3.1. Backside voltage                                | 78  |

|    |       |          | 4.3.3.2. Clear gate voltage                              | 81  |

|    |       |          | 4.3.3.3. Drain voltage                                   | 84  |

|    | 4.4.  | Intern   | al charge injection                                      | 86  |

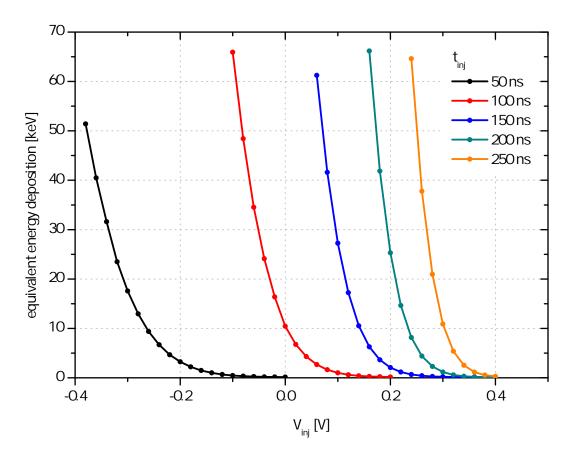

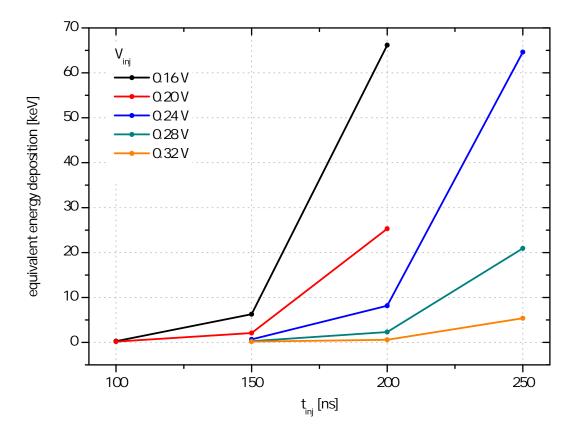

|    |       | 4.4.1.   | Charge injection using the inner substrate contact       | 88  |

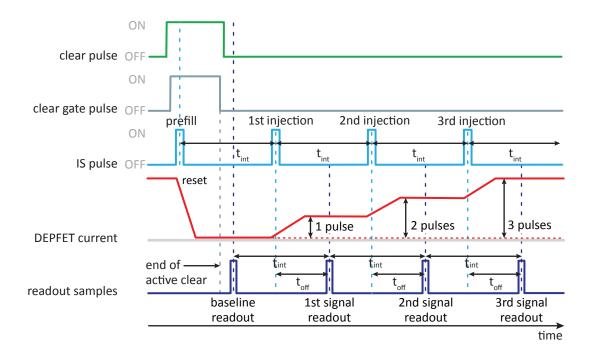

|    |       | 4.4.2.   | Measurement sequences                                    | 92  |

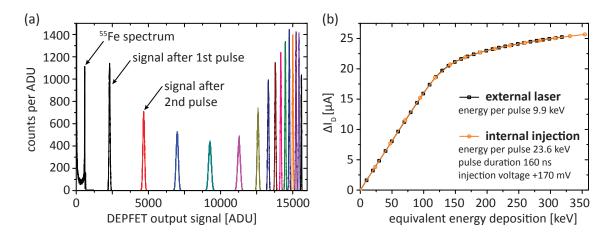

|    |       | 4.4.3.   | Validation of the internal charge injection              | 94  |

| 5. | Desi  | gn of f  | final DSSC sensors                                       | 99  |

|    | 5.1.  | Radiat   | tion hardness                                            | 99  |

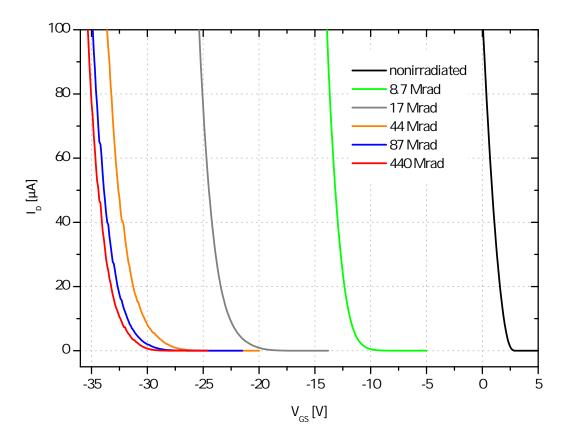

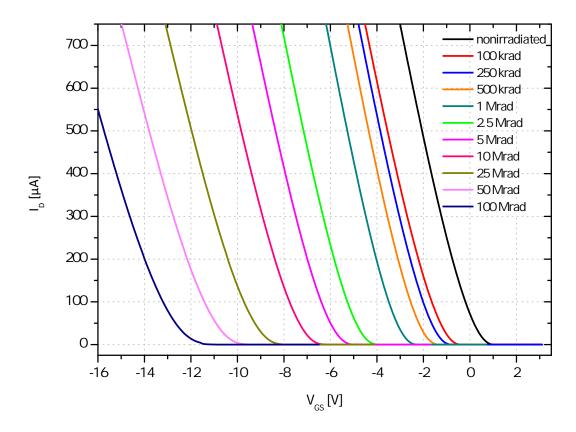

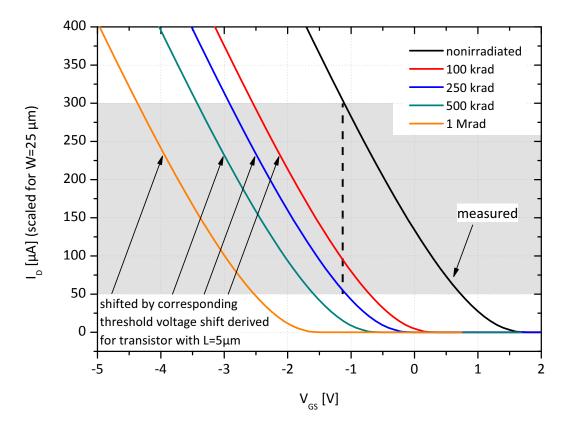

|    |       | 5.1.1.   | Damaging mechanism                                       | 99  |

|    |       | 5.1.2.   | Results of irradiation test using standard technology    | 105 |

|    |       | 5.1.3.   | Results of irradiation test with thinned gate insulators | 107 |

|    |       | 5.1.4.   | Conclusion                                               | 111 |

|    | 5.2.  | Reado    | out speed                                                | 113 |

|    | 5.3.  | Design   | n of final nonlinear response curve                      | 121 |

| 6. | Sum   | ımary    |                                                          | 127 |

| Α. | Bibli | iograph  | ny                                                       | 131 |

|    |       |          |                                                          |     |

| В. | IS in | njection | ו                                                        | 139 |

## 1. Introduction

In history of science, hardly any technology has yielded more breakthrough developments in as many disciplines as microscopy. Progress in fields from biology, medicine and physics to electronics, pharmaceuticals and materials research still depends on microscopy. Within the discipline of light microscopy, a number of other techniques have been developed to investigate matter using electromagnetic waves. In order to explore ever-smaller structures, the wavelength of the light had to become constantly shorter. Nowadays, for example, routinely hard X-rays with wavelengths of less than 1 nm (billionths of a meter) are used to study matter. However, the smaller the objects to be examined, the more light is needed for a meaningful picture. As a result, applications have been limited due to insufficient light intensity from available X-ray sources.

In recent years "free electron laser" (FEL) technology has proven its ability to overcome the current limitations of X-ray diagnostics and thus provides a new basis for an advanced version of microscopy. Not only is the intensity of FEL light a billionfold higher than any previous X-ray experiment, but the light is also generated in ultra-short pulses so that even processes on extremely short time scales can be investigated. Similar to its predecessor, light microscopy, FEL technology will play a crucial role in the search for answers in a variety of disciplines.

The enormous potential of FEL technology has inspired the construction of numerous FEL facilities around the world. The most advanced and most powerful facility of its kind is the European X-ray free electron laser (XFEL) currently under construction in Hamburg. Starting in 2015, it will be the brightest man-made X-ray light source in the world, delivering extremely intense X-ray flashes on a femtosecond scale with a maximum repetition rate of 4.5 MHz. The light generated will have laser-like properties - it is fully coherent and highly focused. The European XFEL will provide technical capabilities for time-resolved 3D imaging of chemical and physical processes on an atomic level. For example, it will enable the "filming" of biochemical processes in individual cells, a technique that is an important basis for the development of new drugs. Equally important will be material investigations on an atomic scale, which will allow the study of catalytic processes in the chemicals industry or the development of new nanomaterials for energy storage. Apart from these examples, the European XFEL will also open new possibilities for scientific applications that have not even been considered yet.

The unprecedented properties of the European XFEL will require 2D imaging detector systems that will have to resolve the enormous contrasts occurring in FEL experiments and allow for frame rates in the MHz regime if they are to benefit from the high repetition rate of

#### CHAPTER 1. INTRODUCTION

the generated X-ray flashes. One of three 2D imaging and photon counting detector systems currently under development is the DSSC (DEPFET sensor with signal compression). It is based on a new DEPFET (depleted p-channel field effect transistor) active pixel sensor with nonlinear amplification, in other words, a high gain for small signals to obtain single-photon detection capability and a reduced gain for large signals to achieve a high dynamic range of several thousand photons per pixel and frame.

Within the framework of this thesis, first prototypes of the nonlinear DEPFET were developed and characterized in detail. The thesis contains comprehensive studies of the new device and the physical processes that occur during its operation. The newfound knowledge from measurements and simulations permits the improvement of the DEPFET and thus facilitates its optimization for application at the European XFEL.

The thesis is organized into four main chapters beginning with an introduction of free electron lasers and moving into a discussion of the special requirements for 2D photon counting detectors at the European XFEL. After a short overview of the DSSC detector system chapter three presents the basic DEPFET concept and its adaptation for FEL applications. Chapter four then represents the core of this thesis, which describes the first DEPFET prototypes with nonlinear amplification before moving on to an explanation of the test environment and the measurement procedures. After that the measurement results are presented and discussed together with device simulations. In chapter five the limitations of the prototypes are derived and the optimization potential for the next generation of nonlinear DEPFETs is evaluated.

# 2. The European X-ray free electron laser

The 4th and newest generation of accelerator-based X-ray sources is currently emerging on a worldwide level. With unprecedented beam intensity, these so-called free electron lasers (FELs) ring in a new era of atomic-scale X-ray diagnostics. The most powerful system of this kind is the European X-ray free electron laser (XFEL) in Hamburg and Schleswig-Holstein. It is currently under construction, but starting 2015 it will deliver ultra-short and extremely bright X-ray flashes for scientific operations. This chapter will briefly introduce the functional principle of the XFEL and give two examples of the new experimental possibilities for international and interdisciplinary researchers. We will then look at the requirements of the European XFEL for 2D imaging and photon counting detector systems before presenting the proposed DSSC detector system concept whose sensor development is the core of this thesis.

## 2.1. Working principle of free electron lasers

Radiation from a free electron laser (FEL) has much in common with radiation from conventional lasers: high output power, narrow bandwidth and spatial coherence. In a conventional laser, light is generated by the transition of exited electrons between bound atomic or molecular states in an active medium that is either a solid, a liquid or a gas.

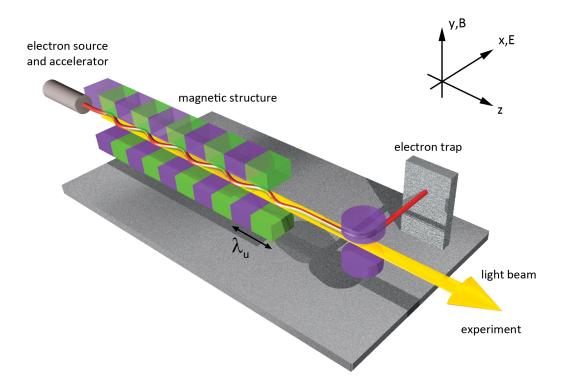

In a free electron laser, the function of the active medium is taken over by unbound electrons moving freely in a vacuum within a relativistic electron beam. Figure 2.1 shows the basic structure of a high-gain single-pass SASE (self-amplified spontaneous emission) FEL. Initially, an electron gun generates free electrons that are subsequently accelerated to relativistic velocities within a linear accelerator. The light generation takes place in a so-called undulator, which is a linear sequence of dipole magnets with alternating north-south orientation. While traveling through the undulator, the electrons are deflected by the Lorentz force transverse to their main propagation (z-direction) and to the magnetic field (y-direction). Due to the periodic structure of the undulator, the electrons are forced on a sinusoidal path in the x-z plane and the acceleration of the electrons leads to the emission of synchrotron radiation in a narrow, forward-directed cone.

Like for a bending magnet, the half opening angle  $\phi$  of the wavelength integrated radiation cone in small angle approximation is given by

$$\phi \approx \frac{1}{\gamma} = \frac{m_e c^2}{E_e} \tag{2.1}$$

**Figure 2.1:** Sketch of high-gain SASE FEL based on a single pass of the electron beam through a very long undulator. An electron bunch is accelerated to relativistic energies and passes the magnetic structure of the undulator where the radiation is generated. Afterward, the electron beam is dumped and the light beam goes to the experimental station [1].

with  $\gamma = \frac{1}{\sqrt{1-(\frac{v}{c})^2}}$  as the relativistic Lorentz factor,  $m_e$  as the electron mass, c as the speed of light, and  $E_e$  as the kinetic energy of the electrons [2].

To characterize the emission of the magnetic structure it is useful to introduce the dimensionless parameter K, which is given by the ratio between the maximum angular deviation of the electron beam from the forward direction  $\delta$  and the opening angle of the emission cone  $\phi$ . K can be expressed as

$$K = \frac{\delta}{\phi} = 0.934 \cdot B_0[T] \cdot \lambda_u[cm] \tag{2.2}$$

where  $\lambda_u$  is the length of the undulator period and B is the r.m.s. magnetic field strength in the undulator. While  $K \geq 1$  applies for Wigglers, in the case of an undulator the maximum angular deviation from the forward direction is smaller than the opening angle of the emission cone and thus K < 1 [3]. This basically means that the radiation generated by the electrons overlaps with the electron beam during propagation through the individual magnetic periods of the undulator. Due to their wave-like trajectory, the electrons have a velocity component in parallel to the electric field, enabling the interaction between the electromagnetic wave and the electrons. This interaction forms the basis for the functional principle of free electron lasers.

In the case of an existing light wave, the interaction allows the energy exchange between the electrons and the wave according to

$$\frac{dE_e}{dt} = -e\vec{v} \cdot \vec{F} = -e \cdot v_x \cdot F_x \tag{2.3}$$

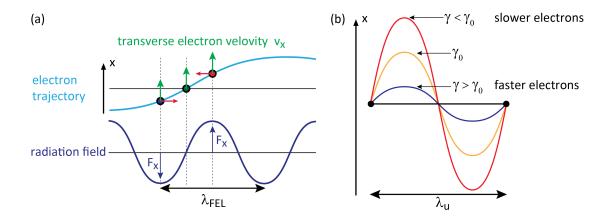

where  $E_e$  is the electron energy,  $\vec{v}$  is the velocity vector of the electron,  $\vec{F}$  is the electric field vector, and  $v_x$  and  $F_x$  are the respective components transverse to the main propagation and the magnetic field [4]. The equation indicates that electrons in phase with the electromagnetic wave are decelerated while electrons with a velocity anti-parallel to the electric field vector gain energy from the wave (compare Figure 2.2 (a)).

**Figure 2.2:** (a) Illustration of the interaction between the electromagnetic wave and electrons. Electrons that are in phase with the electric field are decelerated, while electrons out of phase are accelerated. The resulting energy spread leads to dispersion induced by the magnetic field of the undulator (b). Faster electrons move on a shorter trajectory than slower electrons.

As a result, the magnetic field of the undulator acts as a dispersive medium (b). The faster electrons that have been accelerated propagate on a shorter path due to their enhanced magnetic rigidity whereas the slower electrons are forced onto a longer path through the undulator. The energy exchange between the electron bunch and the electromagnetic wave combined with the dispersion due to the magnetic field results in the longitudinal modulation of the electron density within the bunch. This process is called 'microbunching': electrons are concentrated into slices located at the points where the electric field strength is zero. Since the slices are much shorter than the wavelength of the undulator radiation, they behave like a single particle with a high charge, which means they radiate coherently. In order to maintain the process of microbunching, a fixed phase relationship between the wave and the electron bunch is required. However, the light wave moves faster than the electrons since the electrons have a rest mass and move on a wiggly line. The only way out is that the light wave shifts exactly by one wavelength with respect to the electron bunch whenever the electrons move forward by a single undulator period.

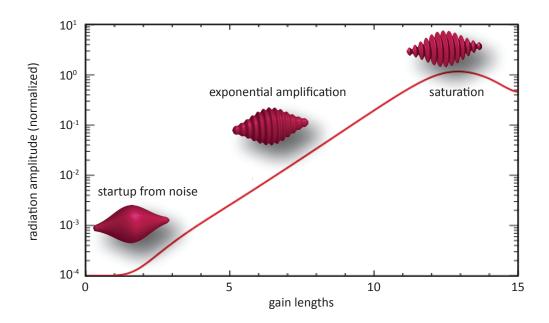

Figure 2.3: Amplification of FEL radiation as a function of the distance within the undulator. The red cartoon illustrates the electron bunch at various positions. The radiation amplitude starts out from noise emitted by a randomly distributed electron bunch. Through the interaction with the electromagnetic wave, the electron bunch is microbunched, which leads to increased radiation emission and to exponential amplification. When microbunching reaches its equilibrium, the radiation amplitude saturates. If the electron bunch continues propagating in the undulator the field starts to transfer energy back into the electron bunch and the radiation amplitude starts to oscillate [5].

On the undulator axis this so-called interference condition is only met for a radiation wavelength of

$$\lambda_{FEL} = \frac{\lambda_u}{2\gamma^2} \left( 1 + \frac{K^2}{2} \right). \tag{2.4}$$

with  $\lambda_u$  as the length of the undulator period,  $\gamma$  as the relativistic Lorentz factor, and K as the undulator parameter [4]. Although the emitted synchrotron radiation is white, the constructive interference is only given for  $\lambda_{FEL}$  and higher harmonics. If the interference condition is fulfilled, the electrons emit light at different points of the undulator in phase with the actual present light wave. One of the main advantages of this coherent radiation is the significantly higher brilliance compared to incoherent sources. The intensity for coherent emission scales quadratically with the number of electrons  $(N_e)$ , whereas for spontaneous radiation it scales only linearly with  $N_e$ . Therefore, the light emission strongly enhances the electric field strength in the undulator and in turn intensifies microbunching. This self-amplifying process leads to an exponential increase of the radiation amplitude with the undulator length, as it is shown in Figure 2.3.

At the beginning of the undulator there is no electromagnetic wave that can be amplified and the radiation power stays almost constant. The spontaneous emission of synchrotron radiation within the first section of the undulator acts as a seed radiation for the FEL process. Once an initial wave is present, the self-organizing process of the electrons in the undulator leads to an exponential growth of the pulse energy with the undulator length. When the electron distribution has reached its equilibrium and microbunching cannot become more pronounced due to the electrostatic repulsion of the electrons, the radiation amplitude reaches saturation. In the case of further propagation of the electron bunch in the undulator, the field starts to transfer energy back into the electron bunch and the radiation pulse energy starts to decrease again.

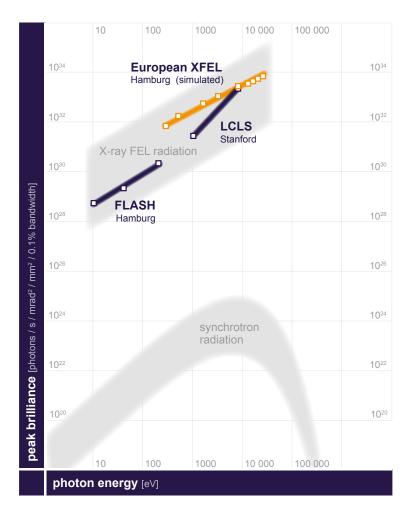

**Figure 2.4:** The peak brilliance of free electron lasers exceeds that of most modern synchrotron radiation by many orders of magnitude. Starting in 2015, the European XFEL will be the brightest X-ray light source in the world [1].

For a high-gain SASE FEL, saturation has to be achieved within a single pass. This demands not only very long undulators of several hundred meters but also a very high electron beam quality in order to maximize the overlap of the electrons with the emitted radiation and thus to achieve an increase in speed of microbunching. The required compression of the electrons into ultra-short bunches in the order of  $\mu$ m allows the generation of light pulses in the fs range.

The startup of the FEL process from noise without the need for any external seed radiation is called SASE (self-amplified spontaneous emission). It permits the startup at arbitrary wavelengths without the need for external seed radiation. Furthermore, an SASE FEL provides full amplification in a single pass and does not require an optical cavity with highly reflective mirrors. This extends the energy range of FELs into the X-ray realm and allows the radiation wavelength to be tuned by simply adjusting the energy of the electron beam (compare equation 2.4). As illustrated in Figure 2.4, the peak brilliance of FEL radiation is a billion times higher than for conventional synchrotron X-ray sources and the European XFEL will be the most powerful facility of its kind. It will provide ultra-short X-ray flashes with a typical duration of less than 100 fs with full lateral coherence. These unique and unprecedented properties of X-ray radiation will open up new experimental possibilities that will be briefly introduced in the following section.

## 2.2. New Opportunities at the FELs

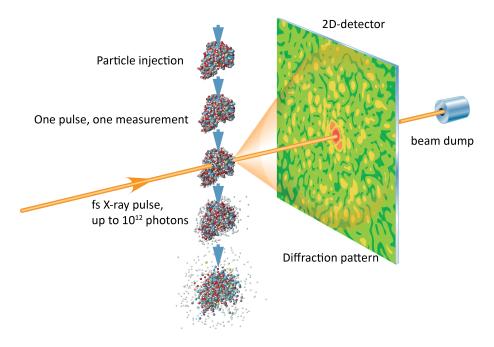

A typical experiment performed at FEL facilities is illustrated in a simplified sketch in Figure 2.5.

**Figure 2.5:** Simplified sketch of an X-ray scattering experiment. A scattering target is injected into the photon beam and the diffraction pattern is recorded by a 2D imaging detector [1].

The intense photon beam generated in the undulator is aligned to go through a central hole of a 2D imaging detector and is dumped by a beam stop behind. Whenever a target, like a molecule or a small nanocrystal, is brought into the photon beam, the X-rays are scattered and cause a diffraction pattern, which is recorded by the 2D detector. Using

dedicated analysis algorithms, the atomic structure of the target can then be calculated from the measured intensity distribution.

In principle, this is comparable to experiments performed for many years now at synchrotrons all around the world. However, the unprecedented properties of the FEL light open up a completely new class of experiments. In particular, it is the tremendous peak brilliance and the ultra-short, coherent light pulses that provide new opportunities previously inaccessible to accelerator based X-ray sources. Below, two experiments will be presented that convey an impression of the revolutionary potential of free electron lasers.

## 2.2.1. Imaging of biological samples

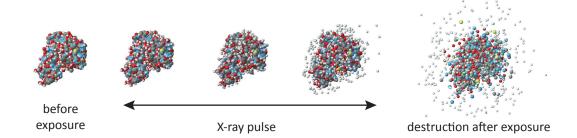

Analyzing the structure of molecules using scattering experiments is a standard application at conventional synchrotrons. In order to determine the molecular structure of the target, the recorded diffraction patterns need to provide sufficient statistics. This requires either long exposure time or crystalline samples that offer a large number of identical specimens. However, both approaches have significant limitations. On the one hand, many samples cannot be crystallized and thus only exist as an individual molecule. On the other hand, exposure times cannot be extended, especially for biological samples, because the radiation damage would lead to the degradation or even destruction of the target before the diffraction pattern is acquired. By using the ultra-short X-ray flashes of free electron lasers with a

**Figure 2.6:** Illustration of a molecule during a scattering experiment at a free electron laser facility. The molecule is injected and irradiated with an ultra-short X-ray flash. It hardly changes during exposure but is destroyed afterward due to the high energy deposition of the light pulse within the sample.

typical duration of less than 100 fs, the issue of radiation damage can be mitigated since the timescale for most damaging mechanisms is much longer [6,7]. As illustrated in Figure 2.6, the duration of the flashes is so short that the molecule hardly changes during the exposure. Only after the X-ray flash has passed, the target molecule does start to turn into plasma due to the enormous energy deposition of the intense light pulse [8]. Due to the extremely high peak brilliance of the FEL, each individual flash provides enough photons to record a full analyzable diffraction pattern. The coherence and the short wavelength further allow for holographic imaging with atomic resolution. The applicability of ultra-short X-ray flashes for structure analysis has already been shown for nanocrystals of Photosystem I,

one of the largest membrane protein complexes [8], as well as for a single mimivirus, one of the largest known viruses [9].

For these reasons, free electron lasers offer unique capabilities for the structural analysis of large and difficult-to-grow molecules that are sensitive to irradiation. This will surely open up new fields of research, one of which could be the human cell membrane proteins, one of the most important drug targets in the human body. The knowledge of their atomic structure would be a milestone for pharmaceutical research as the active substances in new medicines could be tailored to suit recipients, which would increase their effectiveness and reduce adverse effects.

## 2.2.2. Filming chemical reactions with atomic resolution

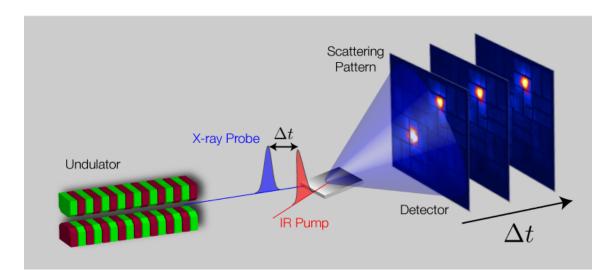

Besides the capability of taking snapshots of large molecules before they explode, the ultra-short light flashes of FELs will also enable researchers to resolve the transient behavior of molecules during chemical reactions by using pump-and-probe experiments.

Figure 2.7: Sketch of a typical pump-probe setup for ultra-fast measurements. An optical or IR pump excites a process and the dynamics of the sample are then observed by a time-delayed X-ray pulse of the FEL. The combination of measurements at varying delays  $\Delta t$  allows for the reconstruction of the dynamics in a stroboscopic fashion [10].

Such an experiment typically consists of two individual light pulses. Initially a reaction is started with an optical or an infrared laser pulse before it is probed by the femtosecond X-ray pulse of the FEL. Alternatively, the X-ray pulse is split in two to act as both pump and probe [11]. Even if the probe pulse of the FEL leads to the destruction of the target, repeating the experiment with different time intervals between the trigger and the probe pulse allows you to monitor the state of the system as a function of time after the reaction has been initiated. The temporal resolution of this technique is given by the duration of the X-ray pulse and the jitter between the pump and the probe. By using

pump-and-probe experiments, movies of molecular reactions can be recorded with atomic resolution allowing researchers to follow the motion of atoms within molecules as well as the progress of chemical reactions, all in real time. This will lead to a better understanding of the dynamics of chemical processes, which is essential for many fields of research, for example in chemistry, where it will help improve catalytic converters and thus develop more efficient industrial production processes, or in biology where the knowledge gained will provide an essential basis for the development of new medicines.

## 2.3. Detector requirements of the European XFEL

In order to benefit from the exceptional properties of the European XFEL, new detector systems are required. The key requirements for future detector systems will be discussed in the following section.

## 2.3.1. Single-photon resolution and high dynamic range

Free electron lasers, and in particular the European XFEL, are single-shot machines. The high brilliance of their light flashes enables researchers to decipher the atomic structure of molecules using diffraction patterns obtained from single flashes of light. This capability is directly connected with enormous contrast on the diffraction patterns. Depending on the target there will be areas on the detector that will be hit by several thousand photons, whereas other areas see only a few or none at all. The new detector systems therefore have to provide a very high dynamic range in order to resolve these extreme differences in brightness.

Apart from the high dynamic range, future detector systems should also provide single-photon detection capability up to some tens of photons. This allows the observation of higher scattering orders and thus increases the precision of the reconstruction algorithms. In addition, it allows us to precisely determine the X-ray background that results from scattering processes either on residual gas in the vacuum tank or on the liquid jet, which is used to bring the sample molecules into the photon beam. In pump-and-probe experiments, stray light from optical pump lasers can also cause additional background. The knowledge of this background is crucial for data analysis.

For higher numbers of photons per pixel and frame, the necessity of single-photon counting is only limited because both photon generation in the undulator as well as the scattering process underlie Poisson statistics. As a result, higher measurement accuracy does not contain more physical information. Natural Poisson noise is given by the square root of the number of photons. For example, if an experiment delivers on average N photons per pixel and it would be possible to repeat the experiment under exactly the same conditions,

then the statistical fluctuations of the measured photon number would be

$$\Delta N = \sqrt{N}.\tag{2.5}$$

Future detector systems need to provide a dynamic range of several thousand photons per pixel and frame. Independent of the number of registered photons the measurement accuracy should always be better than the statistical fluctuation due to the Poisson noise.

## 2.3.2. Readout speed

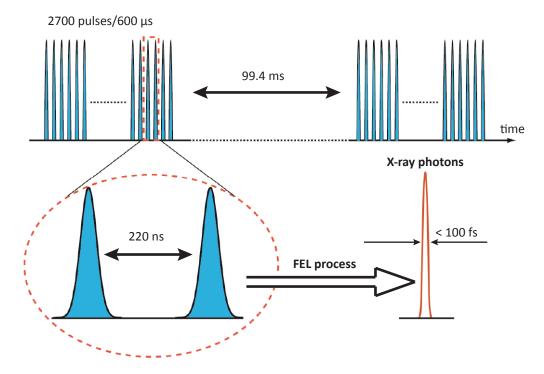

In contrast to the single-photon detection capability and the large dynamic range that are common requirements of all free electron laser facilities, the European XFEL has significantly higher demand in terms of readout speed. The focused beam will have such a high photon density that the sample under study will not survive a single shot. Thus, every X-ray flash has to be treated as a separate experiment and the complete X-ray diffraction pattern from each pulse has to be recorded separately. The European XFEL provides 27,000 light pulses per second, far more than any other FEL facility in the world. Due to the superconducting accelerator technology, the flashes are not equally distributed in time but in a time scheme as illustrated in Figure 2.8.

The X-ray flashes are generated in so-called bunch trains of 600  $\mu$ s length and a

Figure 2.8: X-ray bunch structure at the European XFEL. The XFEL machine generates bunch trains with a repetition rate of  $10~\mathrm{Hz}$ . Every bunch train is composed of  $2,700~\mathrm{X}$ -ray pulses with a temporal distance of  $220~\mathrm{ns}$  corresponding to a maximum repetition rate of  $4.5~\mathrm{MHz}$

repetition rate of 10 Hz. Each bunch train consists of 2,700 X-ray flashes with a temporal spacing of 220 ns. The 99.4 ms long gap between the bunch trains is required to cool the superconducting cavities in order to keep them below the superconducting transition temperature and thus to guarantee stable operation of the facility. To take advantage of the high repetition rate of the European XFEL within the bunch trains, detectors have to be able to process a full image within the 220 ns between two flashes. The only way to achieve the corresponding frame rate of 4.5 MHz for large-area 2D imaging detectors with one million pixels is to implement a full parallel readout of all pixels simultaneously.

#### 2.3.3. Radiation hardness

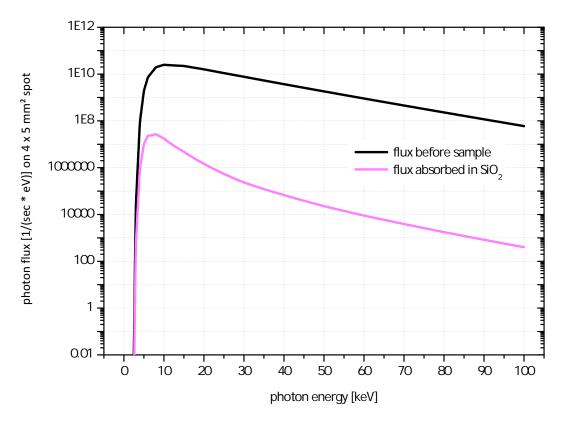

In the radiation environment of free electron lasers, radiation tolerance is another major challenge for silicon-based 2D imaging detector systems. At this point, the expected radiation dose at the European XFEL cannot be derived from experimental data since the facility is still under construction. However, based on the following assumptions, H. Graafsma [12] has set up a worst-case assessment of the expected radiation dose:

- Performing constantly, a very harmful experiment with  $5 \cdot 10^4$  photons per pulse and per 200 x 200  $\mu$ m<sup>2</sup> pixel

- 1,250 hours of data acquisition per year for a single detector system

- 15,000 X-ray pulses per second (less than 27,000 per second due to electron beam dump limitations)

This scenario delivers  $6.75 \cdot 10^{10}$  pulses and  $3.4 \cdot 10^{15}$  photons for the hottest pixels per year and thus roughly  $1 \cdot 10^{16}$  photons within a three-year operation. For 12 keV photons and a 500  $\mu$ m thick silicon sensor, this corresponds to a total absorbed dose of 1 Giga Gray. It has to be pointed out that, even for the billionfold higher peak brilliance of the FELs, the time-integrated photon flux is comparable to 3rd generation storage rings. The calculation is certainly the upper limit of any radiation dose that can be expected and the total integrated dose might well be much lower. However, because they are strongly dependent on the experiments performed and the energy of the photons, no precise values can be given. The detectors should therefore be designed as radiation hard as possible to mitigate the restriction of the detector systems for certain kinds of experiments.

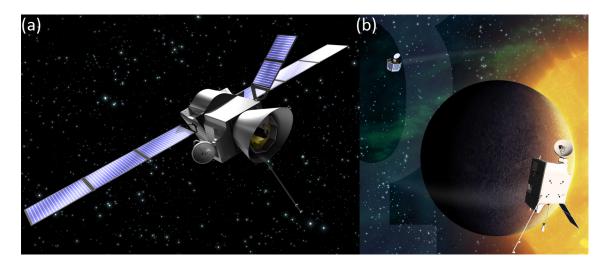

## 2.4. DSSC detector system

In addition to the LPD (Large Pixel Detector) [13] and the AGIPD (Adaptive Gain Integrating Pixel Detector) [14], the DSSC (DEPFET Sensor with Signal Compression) detector system is one of the three integrating and X-ray imaging detector systems currently under development for the use at the European XFEL. The DSSC will be a large-area detector system for high-speed photon counting with a focus on the low end of the XFEL's

energy range. Some of its main design parameters are listed in Table 2.1.

| Energy range                  | 0.525  keV (optimized for $0.56  keV$ )   |

|-------------------------------|-------------------------------------------|

| Number of pixels              | 1,024 x 1,024                             |

| Sensor pixel shape            | hexagonal                                 |

| Sensor pixel pitch            | $204~\mu\mathrm{m} \ge 236~\mu\mathrm{m}$ |

| Dynamic range                 | >10,000 photons/pixel/pulse               |

| Resolution                    | Single photon @ 1 keV (4.5 MHz)           |

| Frame rate                    | up to 4.5 MHz                             |

| Stored frames per bunch train | >640                                      |

| Operating sensor temperature  | -20°C optimum, RT possible                |

**Table 2.1:** Overview of design goals of DSSC detector system.

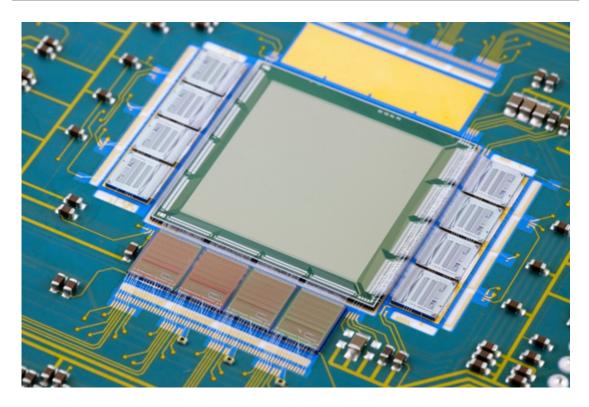

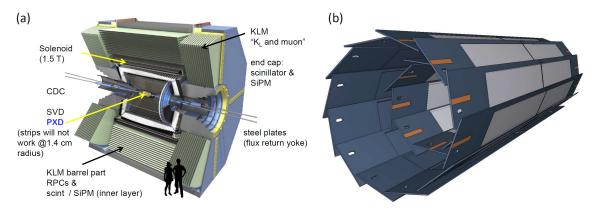

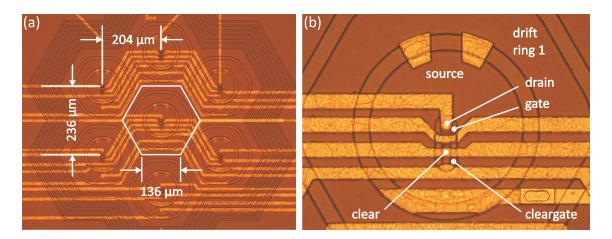

The full DSSC camera head [15,16] will be equipped with 1,024 x 1,024 hexagonal pixels covering a sensitive area of roughly 24 x 25 cm<sup>2</sup>. Yet these impressive dimensions should not obscure the high degree of integration and the complexity of the system.

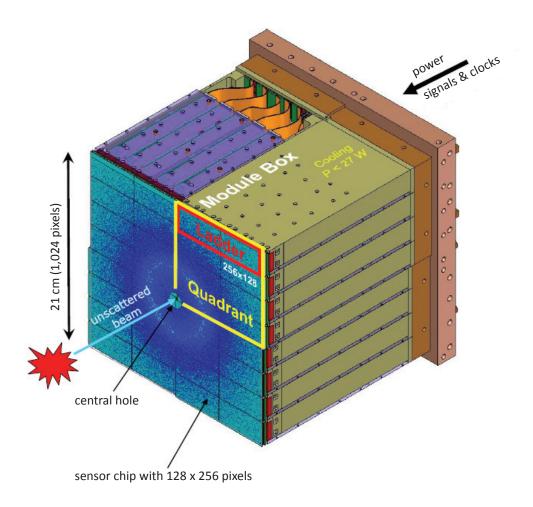

As indicated in Figure 2.9, the DSSC is subdivided into four equal, independent quadrants each having 512 x 512 pixels. The quadrants are arranged around a central hole, which is adjustable in size to let the direct, unscattered X-ray beam pass through. Each quadrant is again composed of four "ladder" modules, the smallest exchangeable detector unit, with a format of 128 x 512 pixels. A ladder comprises two identical sensor chips each with 128 x 256 pixels. To maintain the ladder module's four-side buttability, all mechanical, thermal, power and signal connections are implemented orthogonally to the sensor surface [17]. The dead area caused by sensor chip edges and gaps between ladders and quadrants is approximately 15%.

The modular design of the DSSC detector leads to a much higher yield of the sensor production and the module assembly process, which in turn guarantees the use of only flawless ladder modules. It also makes it possible to easily exchange individual ladders and thus replace certain regions of the detector that may be damaged or degraded due to the hostile radiation environment at the XFEL facility. In the future, this modular design will permit even further scalability of the detector area. That will enable either the registration of higher scattering orders or, in the case of greater distances between the detector and the interaction point, improved spatial resolution. Both options may even enhance the accuracy of structural analyses for irradiated targets, but a further enlargement of the detector system is not foreseen at the present time.

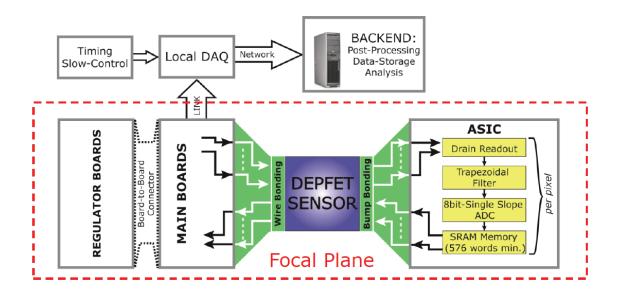

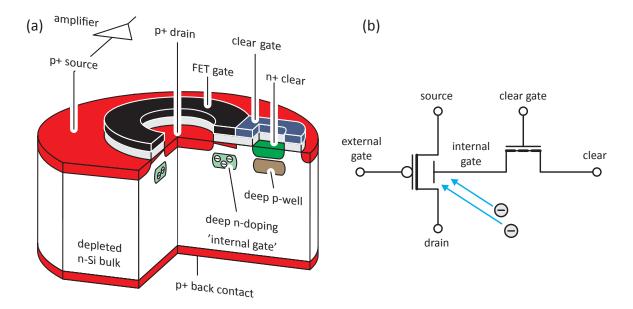

Figure 2.10 shows a simplified block diagram of the DSSC concept. It is based on a new DEPFET active pixel sensor that offers signal compression on the sensor level, fully parallel readout [18] and immediate digitization within the pixel footprint in order to achieve frame rates in the MHz range. Each DEPFET sensor chip (128 x 256 pixels) is connected by bump bonds to eight pixelated mixed-signal readout ASICs (application

**Figure 2.9:** 3D view of the full DSSC camera head  $(1,024 \times 1,024 \text{ pixels})$  composed of four quadrants. Each quadrant consists of four ladders and eight monolithic sensors of 128 x 256 pixels each. Due to the geometric arrangement of the quadrants, a central hole is maintained to let the unscattered beam pass through. All power and signal lines go to the rear of the camera head.

specific integrated circuit) with a format of 64 x 64 pixels. The bump bonding technology enables the 3D integration of DEPFETs and permits the connection of each sensor pixel with its own readout pixel due to the small pitch of only 200  $\mu$ m and the associated high bump density. For this purpose, a new 64 x 64 readout chip was developed as part of the DSSC project [19]. Each of its 4,096 readout pixels contains the full signal processing chain including a current-to-voltage conversion preamplifier, an analog filter with a trapezoidal weighting function [20], an 8-bit single-slope ADC [21,22] and an SRAM storage with a capacity of 640 frames per bunch train [23]. The memory should provide enough capacity to store all meaningful frames of a bunch train since the DSSC detector allows the system to overwrite frames in the SRAM that do not contain useful information. For this purpose, the XFEL machine will provide an external veto signal indicating frames that can be discarded. The digital data acquired in the memory is sent off the focal plane via optical links to

**Figure 2.10:** Simplified block diagram of the DSSC detector concept. The sensor is bump bonded to a set of readout ASICs. The ASICs provide analog signal filtering, 8-bit digitization and data storage for every individual pixel.

the local DAQ system [24] during the 99.4 ms between the bunch trains and temporarily stored there. Subsequently, the data is transferred over the network to powerful server farms for long-term storage and computation-intensive data analysis.

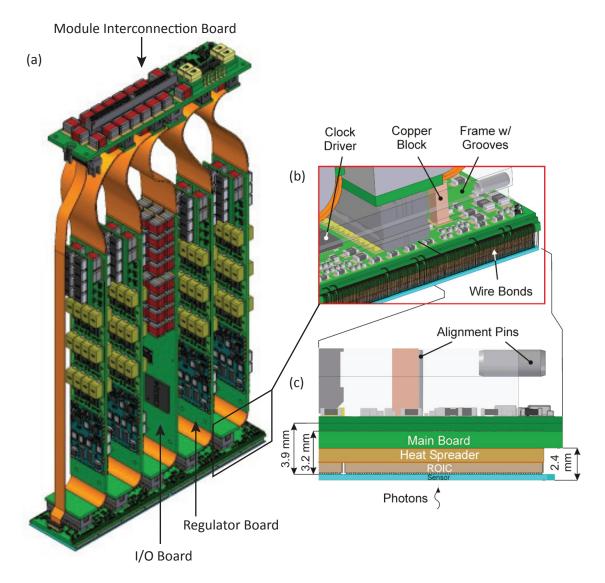

Figure 2.11 shows a drawing of one detector ladder module. Each module consists of a mainboard with two sensor readout chip stacks, four regulator boards and a single I/O board. On the bottom side there are two DEPFET sensor chips (128 x 256 pixels) each bump-bonded to eight readout ASICs. The backside of the ASICs is glued to a ceramic carrier, which in turn sits directly on the mainboard. The ceramic carrier acts as a heat spreader and allows for a temperature gradient over the sensors of a full ladder below 5 K at the foreseen sensor operation temperature of -20°C. All power and signal lines required for the chip stack are on the long side of the ladder by wire bonds between the mainboard and the sensor chip. In particular, this means that all ASIC connections go over the sensor chips.

The mainboard distributes the power and digital signals, and serves as a carrier for the four regulator boards and the I/O board, which are attached perpendicularly by board-to-board connectors.

The regulator boards generate the static and dynamic supply voltages for the DEPFET sensors as well as for the readout ASICs, and have additional electronic components that allow for a power cycling. The DEPFET and the readout ASICs are only active during the 600  $\mu$ s long bunch trains and switched off during the 99.4 ms long cooling phase of the XFEL machine (compare Figure 2.8). This way the total power consumption within the vacuum can be reduced from a peak power of 10.7 kW down to an average of 400 W. The regulator boards also accommodate big arrays of capacitors to stabilize the static voltages

Figure 2.11: Technical drawing of one "ladder", the smallest subunit of the DSSC detector system. Figure (a) shows the complete ladder with four regulator boards and one I/O board perpendicular to the mainboard. Figure (b) depicts a close-up side view of the mainboard with the wire bonds connecting the mainboard to the DEPFET sensor. Figure (c) illustrates the sandwich structure of the mainboard, the head spreader and the semiconductor chips.

and to enable fast rise times of a few nanoseconds and constant amplitudes for the clocked voltages over the entire bunch train.

All the digital timing and control signals for power cycling are generated on the I/O board and provided by the module interconnection board on the top in Figure 2.11 (a). Apart from generating the steering signals for regulator boards, the main task of the I/O board is to manage the data stream from the readout ASICs to the DAQ system. It is therefore equipped with a powerful FPGA (field programmable gate array) that receives the measurement data from all 16 readout ASICs of the entire ladder and merges the data

into a single serial output data stream. This can then be transferred via optical links to the DAQ system.

The key component of the detector system is the new DSSC-DEPFET, which features nonlinear amplification and thus provides intrinsic signal compression on sensor level. Besides the DSSC, the LPD and the AGIPD are also based on a fully parallel readout of all sensor pixels in order to achieve the required frame rate of 4.5 MHz. Similar to the DSSC, this is done using bump bonds that connect a sensor chip to a dedicated readout chip. The main difference between the systems is the place and the method of signal compression, which is required to combine the single-photon resolution and the very high dynamic range of several thousand photons per pixel and frame. Both the AGIPD and the LPD have arrays of conventional pin diodes as sensors, whose linear analog output signal is compressed in the readout chip. For the LPD, the analog signal path is fed into three individual amplifier stages which simultaneously process the analog signal with different gains. The AGIPD has indeed only a single amplifier stage, but its gain can be dynamically adjusted to the respective signal level during signal processing.

By contrast, for the DSSC, signal compression for high photon numbers is already implemented on sensor level by the intrinsic properties of the new DSSC-DEPFET. The input capacitance of the DEPFET representing the first amplifier stage is much smaller than in other systems. Consequently, the electronic noise at full speed can be reduced from several hundred electrons to less than 50 electrons r.m.s. for the DSSC. It is thus the only detector system featuring single-photon resolution of low-energy X-rays of 1 keV at the full frame rate of 4.5 MHz. For this reason, the DSSC is foreseen for low energy beamlines at the European XFEL, covering the energy range between 500 eV and 6 keV.

The following chapter will introduce the DEPFET amplifier and discuss the functional principle of the newly implemented signal compression mechanism.

# 3. DEPFET concept

This chapter presents the basic concept of active pixel sensors based on **de**pleted **p**-channel field effect transistors (DEPFETs). However, because all semiconductor radiation detectors are based on the energy deposition in the detector material, we will first discuss the possible interactions of ionizing radiation with matter before introducing the DEPFET in detail.

## 3.1. Interaction of radiation with matter

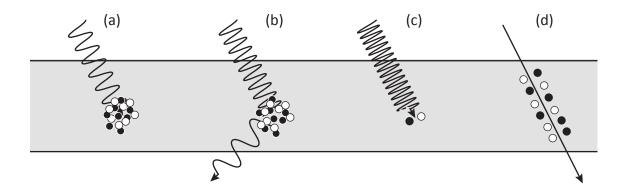

Semiconductor detectors are used for the detection of photons and charged particles like electrons, protons, myons and pions. In order to be detected, these particles have to interact with the detector material. The most important interaction mechanisms of ionizing radiation with a semiconductor are illustrated in Figure 3.1.

**Figure 3.1:** Most important interaction mechanisms of ionizing radiation with matter: (a) photoelectric absorption, (b) Compton scattering, (c) pair production, (d) Coulomb interaction of charged particle.

## 3.1.1. Electromagnetic radiation

In general, there are three different interactions for photons: photoelectric absorption, Compton scattering and pair production.

## Photoelectric absorption

Photoelectric absorption describes an interaction between a photon and an absorber atom where the photon completely disappears (a). In a semiconductor the photon excites an electron over the band gap and the remaining energy goes into the kinetic energy of the electron. The minimum required photon energy is therefore defined by the band gap of the material, which in the case of silicon is 1.12 eV corresponding to an optical photon with a maximum wavelength of 1100 nm. For higher primary photon energies, the excited electron dissipates its energy mainly by generating either phonons or additional electron-hole pairs via the Coulomb interaction with other electrons from the valence band (thermalization). Because part of the photon energy is dissipated to the crystal lattice, the average energy required to generate an additional electron-hole pair is 3.65 eV. This value can be considered as constant, but deviations occur for photon energies close to the band gap energy [25]. The statistical fluctuation of the mean number of electron-hole pairs generated is called Fano noise and limits the achievable energy resolution of semiconductor detectors.

## **Compton scattering**

The scattering process of a photon that only transfers a part of its energy is called Compton scattering (b). After the interaction, the scattered photon with less energy and therefore a longer wavelength will continue its path until another interaction process occurs or it leaves the material. The energy lost in the scattering process is transferred to an electron. According to photoelectric absorption this excited electron will thermalize and generate additional electron-hole pairs.

#### Pair production

For gamma radiation, so-called pair production can occur where the photon is converted into an electron-positron pair (c). Due to momentum conservation, this effect has to take place in the Coulomb field of an atomic nucleus that is absorbing the recoil. Therefore, the minimum required photon energy is the sum of the rest energies of the electron and the positron and the kinetic energy of the recoil nucleus

$$E_{\gamma} = 2m_e c^2 \left( 1 + \frac{m_e}{M_K} \right) \approx 1.022 \text{ MeV}$$

(3.1)

where  $m_e$  is the mass of the electron,  $M_K$  the mass of the recoiling nucleus and c the speed of light. Generally,  $m_e$  is much smaller than  $M_K$  and thus the second term can be neglected.

According to (a) and (b), additional energy will contribute to the kinetic energy of the electron-positron pair to create further electron-hole pairs during the thermalization process.

#### Cross sections

The cross sections for the discussed interaction mechanisms depend greatly on energy and materials and vary over several orders of magnitude. The following dependencies can be found in literature:

$$\Phi_{photo} \qquad \propto \quad \frac{Z^{4..5}}{E^{-3.5}} \tag{3.2}$$

$$\Phi_{compton} \propto Z$$

(3.3)

$$\Phi_{pair} \propto Z^2 \cdot lnE$$

(3.4)

where Z is the atomic number of the detector material and E is the photon energy [25, 26]. For silicon, photoelectric absorption dominates up to energies of roughly 50 keV. In the energy range from 50 keV up to 20 MeV it is Compton scattering and for higher energies than those, pair production is the most probable interaction.

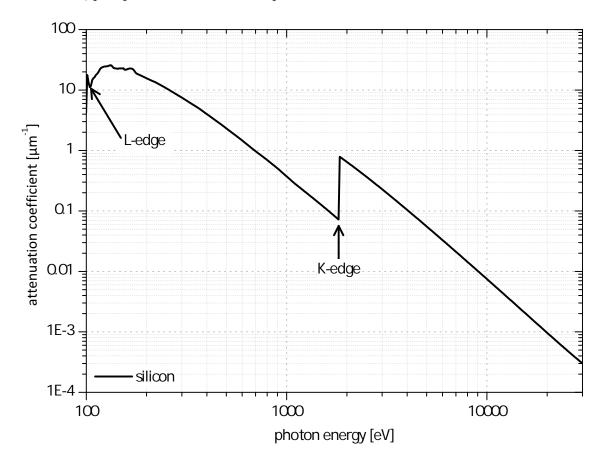

**Figure 3.2:** Energy dependence of the attenuation coefficient in silicon for photons in the energy range of 100 eV and 30 keV due to the photo effect [27].

Considering all of those mechanisms, the attenuation of electromagnetic radiation is described by the Beer-Lambert law

$$I(x) = I_0 \cdot e^{-\frac{x}{\mu}} = I_0 \cdot e^{-x \cdot \alpha}$$

(3.5)

where I(x) is the remaining intensity after the transition of an initial intensity  $I_0$  through an absorber material with an absorption length  $\mu$  and thickness x. The reciprocal value of  $\mu$ , called the attenuation coefficient  $\alpha$ , is shown in Figure 3.2 for silicon in the energy range between 100 eV and 30 keV. The attenuation coefficient decreases as it goes from lower to higher energies. Whenever the energy is higher than the excitation energy of an atomic shell, the attenuation coefficient immediately increases. This behavior can be observed in Figure 3.2 at an energy level of 1839 eV (K-shell of silicon) which is therefore termed the silicon K-edge. For photon energies above the K-edge,  $\alpha$  continues to decrease and hence limits the applicability of silicon detectors for the direct measurement of electromagnetic radiation since the detection probability becomes too small. For a wafer thickness of 450  $\mu$ m, which is the standard thickness of silicon detectors fabricated at the Max-Planck semiconductor laboratory, a detection probability of 99 % can be achieved up to energies of 8 keV.

## 3.1.2. Particle radiation

Uncharged particles like neutrons interact in direct collisions with the atomic nuclei of the absorber material. This scattering process can be either elastic or inelastic. For elastic scattering, the sum of the energies of the two collision partners before and after the interaction is constant, but atoms can be kicked out of their position and ionize other atoms in their vicinity. For inelastic scattering, part of the energy goes into the excitation of an atomic nucleus, which emits a gamma quantum to return to its ground state. The gamma quantum can again interact with the material by the mechanisms discussed in chapter 3.1.1 while another possibility is neutron capture, where the neutron is absorbed by an atomic nucleus causing radioactive decay. In semiconductors, the cross sections for the described interactions are very small and so other detector types are generally applied. By contrast, charged particles such as electrons, protons, myons and pions lose their energy mainly through inelastic Coulomb collisions with orbital electrons from the absorber

energy mainly through inelastic Coulomb collisions with orbital electrons from the absorber material. The maximum energy per interaction that can be transferred to an electron is generally limited to only a small fraction of the particle energy. Together with the high interaction probability, this leads to a continuous energy loss until the particle is stopped or leaves the detector material.

The mean energy loss in a wide energy range can be described by the Bethe-Bloch equation with additional corrections for low and high energies [26]:

$$-\frac{dE}{dx} = 2\pi N_a r_e^2 m_e c^2 \rho \frac{Z}{A} \frac{z^2}{\beta^2} \left[ ln \left( \frac{2m_e \gamma^2 v^2 W_{max}}{I^2} \right) - 2\beta^2 - \delta - 2\frac{C}{Z} \right],$$

(3.6)

where

• c light velocity

•  $r_e$  traditional electron radius =  $2.817 \cdot 10^{-13}$

•  $m_e$  electron mass

•  $N_a$  Avogadro's number =  $6.022 \cdot 10^{23} \text{ mol}^{-1}$

• I medium excitation potential

• Z atomic number of absorbing material

• A atomic weight of absorbing material

•  $\rho$  density of absorbing material

• z charge of incident particle in units of e

•  $\beta$  relativistic speed factor of incident particle  $\frac{\mathbf{v}}{c}$

•  $\gamma$   $\frac{1}{\sqrt{1-\beta^2}}$

•  $\delta$  density correction

• C shell correction

•  $W_{max}$  maximum energy transfer in a single collision

## 3.2. The DEPFET working principle

A DEPFET (depleted p-channel field effect transistor) is an electronic semiconductor device, that uses a special MOS field effect transistor on a fully depleted silicon substrate to detect light and particle radiation. The principle was proposed by J. Kemmer and G. Lutz in 1987 [28]. Like all other semiconductor radiation detectors, the DEPFET is based on charge generation in the detector material via the interactions discussed in the previous section. In order to be detected, the electron-hole pairs generated have to be separated within the detector by the presence of an electric field. For the DEPFET, the principle of sideward depletion, proposed by Gatti and Rehak [29], is used to achieve a full depletion of the silicon bulk and thus to maximize the sensitive detector volume. A schematic of this technique is shown in Figure 3.3.

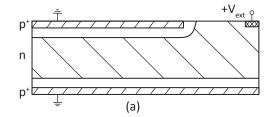

For the sideward depletion,  $p^+$  contacts are put on both sides of a highly resistive n-type silicon bulk resulting in a pn junction on every side of the wafer. In addition, a highly doped  $n^+$  contact (bulk contact) is placed outside the active area to make an ohmic bulk connection. Both intrinsic space charge regions (a) can be extended by applying a more negative voltage - relative to the bulk contact - to the  $p^+$  contact of the specific diode. For sufficiently high reverse biasing of both diodes the two space charge regions will join and the whole silicon bulk is fully depleted (b).

Figure 3.3: The basic principle of sideward depletion. On both sides of a highly resistive n-type silicon bulk there are  $p^+$  implantations forming two diodes. An  $n^+$  implantation outside of the active volume allows for a bulk contact. The intrinsic space charge regions (a) can be extended by higher reverse biasing of both diodes. For sufficiently positive  $V_{ext}$ , both depletion regions touch each other and the bulk is fully depleted (b) (pictures from [30]).

Taking into account the contact boundary conditions, the potential distribution within the device can be calculated according to the Poisson equation

$$\nabla^2 \Phi(\vec{r}) = -\frac{\rho(\vec{r})}{\epsilon_0 \epsilon_r} \tag{3.7}$$

where  $\Phi$  is the electrostatic potential,  $\rho$  is the current space charge density,  $\epsilon_0$  is the dielectric constant in vacuum, and  $\epsilon_r$  is the relative dielectric constant for silicon. In case of full depletion and identical reverse biasing of both diodes, it delivers a symmetric potential distribution and a potential minimum for electrons in the middle of the wafer.

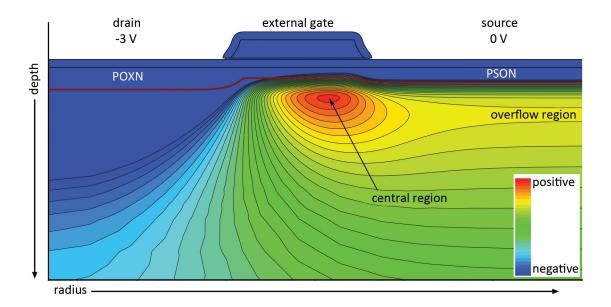

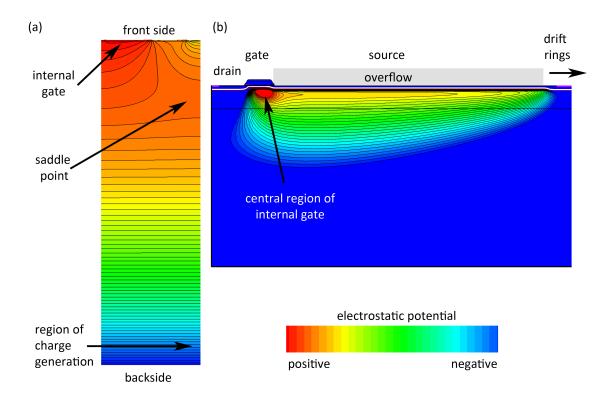

In the standard operation of a DEPFET sensor, the front side is kept at a fixed potential and the backside voltage is decreased until the two space charge regions touch each other and the so-called depletion voltage is reached. Figure 3.4 (a) shows the vertical potential distribution within the structure for various bias conditions, assuming a homogeneous n-doping concentration in the bulk. With decreasing backside voltage the space charge region of the backside diode is extended and bulk depletion voltage is reached at  $V_{dep}$ . For even more negative backside voltages, the formed potential minimum for electrons is shifted toward the front side but its depth is reduced. In order to compensate for this effect, an additional deep n implantation can be introduced at the front side as indicated in (b). The enhanced donor concentration, according to equation 3.7, results in a stronger bending of the potential and consequently allows for a pronounced and highly confined potential minimum for electrons close to the surface. By tuning the doping distribution you can also adjust the vertical and lateral position and the depth of the potential minimum for electrons.

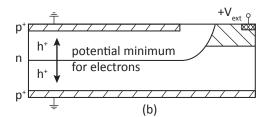

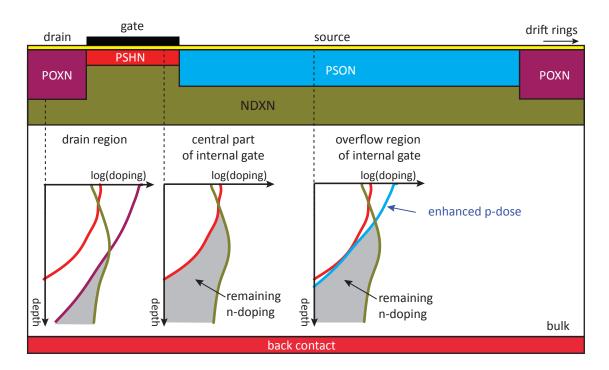

The basic structure of DEPFET sensor pixels is depicted in Figure 3.5. As necessary for the sideward depletion, the backside consists of a diode used for depletion of the full silicon bulk. Since in the standard operation of a DEPFET sensor the radiation enters the detector through the unstructured backside, the very thin diode is called the entrance window.

Figure 3.4: (a) Potential distribution inside a sideward depleted  $p^+n^-p^+$  semiconductor structure for asymmetric biasing of the front side and backside diode. After applying a backside voltage more negative than  $V_{dep}$  the substrate is fully depleted and a potential minimum for electrons is formed. Further decrease of  $V_{back}$  shifts the potential minimum toward the surface and lowers its depth. (b) An increased n-doping concentration close to the front side leads to an improved confinement and enhanced depth of the potential minimum (pictures from [31]).

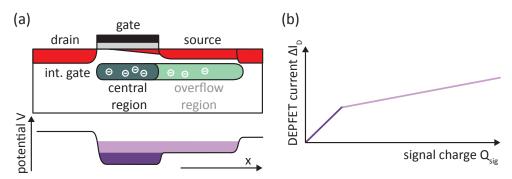

On the front side there are two field effect transistors. One is a p-channel field effect transistor comprising the source contact, an external MOS gate and the drain contact in the center. Appropriate biasing and a deep n implantation form a potential minimum for electrons, laterally constricted to the area below the transistor channel. Due to the potential gradient, all electrons generated thermally or by ionizing radiation somewhere in the depleted substrate will be collected in this potential minimum. The stored electrons will induce a mirror charge in the transistor channel and therefore increase the current density in the channel. By measuring the resulting change in the transistor current we can obtain information about the number of stored electrons and thus the energy of the absorbed radiation. Because of the capability to steer the transistor current like an external gate, the potential minimum for electron is called "internal gate". The sensitivity of the transistor current  $I_D$  to signal charges  $Q_{sig}$  in the internal gate can be calculated according to the analytical DEPFET model proposed by J. Kemmer et al. [32]

$$g_q = \frac{dI_D}{dQ_{sig}} = \sqrt{\frac{2\mu_p I_D}{WL^3 C_I}}$$

(3.8)

with  $\mu_p$  being the hole mobility in the transistor channel, W the width, L the length of the transistor channel and  $C_I$  the gate insulator capacitance per unit area. Hence, the  $g_q$  depends strongly on the geometry of the transistor - for a standard DEPFET it is in the order of 300 pA per electron. This high amplification can be achieved due to the very small input capacitance of the internal gate, which is in the range of only several tens of fF.

**Figure 3.5:** A DEPFET pixel cell (a) and its equivalent circuit (b). The transistor current between source and drain is controlled by the external and internal gates. The charge from the internal gate can be removed by the adjacent nMOS clear structure. The clear gate shields the bulk and the internal gate from the clear contact preventing electron injection as well as charge loss.

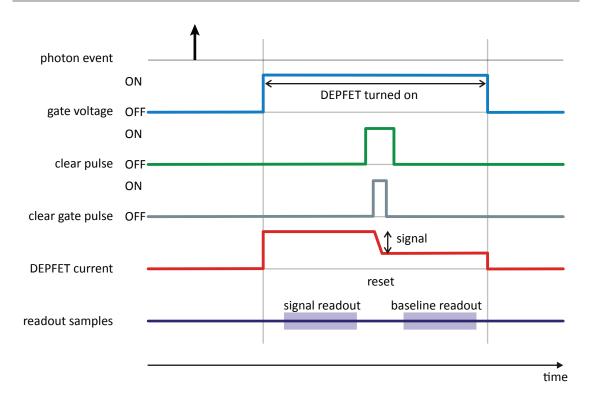

The readout is performed by a comparative measurement of the channel conductivity, once with and once without charge in the internal gate. This so-called correlated double sampling can be implemented either as source follower or as drain current readout. When using the source follower configuration, the source voltage change needed for a constant current through the transistor is measured, whereas for the drain readout the change of the transistor current is determined directly. For the low noise baseline measurement with an empty internal gate, the signal electrons have to be removed from the internal gate by an adjacent clear structure consisting of an  $n^+$ -doped "clear" contact and a second MOS gate called "clear gate". Together with the internal gate, the clear structure builds an n channel transistor allowing for the complete extraction of signal electrons from the internal gate if a positive voltage is applied to the clear and the clear gate. In order to avoid loss of signal charge into the clear contact as well as the emission of electrons from the clear contact into the internal gate, the clear contact is embedded into a p-doped well that forms a potential barrier for electrons in both directions.

The DEPFET combines detection and amplification within a single device, which provides several outstanding properties:

- Internal amplification without interference-prone connections between sensor and amplifier

- Minimum input capacitance for low noise

- High quantum efficiency for low energies because of irradiation through the homogeneous and thin entrance window on the backside

- High quantum efficiency for high energies because of a fully depleted substrate

- Analog storage in the internal gate allowing for "readout on demand"

- Nondestructive readout of stored information allowing for repetitive readout to reduce the low frequency noise

- Usage as unit cell for 2D active pixel sensors with fill factors of 100 % because of the unstructured, homogeneous, thin entrance window

In addition to its application as an active pixel sensor with an amplifier in each pixel, the DEPFET can also be used as readout node for other detector types like pn-CCDs and silicon drift detectors [33].

## 3.3. Noise considerations

The achievable energy resolution of a semiconductor radiation detector is limited by overall system noise. The following sections will discuss the physical causes of noise, their dependencies on detector materials and the various operating conditions.

#### 3.3.1. Fano noise

As already mentioned in section 3.1, energy deposition in a semiconductor by ionizing radiation leads to the generation of electron-hole pairs. For silicon, the mean pair generation energy (PGE) is w=3.65 eV, much higher than the band gap because the excitation of phonons transfers part of the energy to the crystal lattice. Since the PGE can be considered to be constant in a wide energy range, the average number of generated electron-hole pairs can be calculated by

$$\langle N \rangle = \frac{E_0}{w} \tag{3.9}$$

with  $E_0$  being the energy deposition in the semiconductor [34].

Due to statistical fluctuations of the generation process, N underlies certain deviations that are described by the Fano statistics. For this purpose, the Fano factor can be defined

as the mean square deviation (variance) of the number of generated electron-hole pairs divided by their mean number  $\langle N \rangle$ .

$$F = \frac{\langle N^2 \rangle - \langle N \rangle^2}{\langle N \rangle} = \frac{\sigma_{Fano}^2}{\langle N \rangle} = \frac{\sigma_{Fano}^2}{\sigma_{Poisson}^2}$$

(3.10)

The Fano factor can be interpreted as an adjustment factor to relate the observed variance to the variance predicted by the Poisson statistics. This is an intrinsic material parameter and has to be as small as possible in order to get low noise and thus good energy resolution. In literature, the value for silicon is commonly specified with  $F_{Si}$ =0.115 [35]. However, this value may increase for energies below 1 keV [36–38]. Combining equation 3.9 and 3.10 results in the so-called Fano noise:

$$\sigma_{Fano} = \sqrt{\frac{F \cdot E}{w}} \tag{3.11}$$

Fano noise is an intrinsic property of semiconductor materials and defines the physical limit of the achievable energy resolution of a semiconductor detector system.

#### 3.3.2. Thermal noise

Thermal noise is due to the thermal motion of charge carriers. In a semiconductor the electrons in the conduction band are unbound. Their movement is dominated by electric fields (drift) and gradients in the carrier density (diffusion). This straightened motion is overlaid by random and omnidirectional movement because of the Brownian motion from their thermal energy. Within a transistor, this causes statistically independent fluctuations of the current in the channel, which can be modeled by a noise current source at the drain. Quantum mechanical calculations allow for an analytical determination of its spectral noise-power density. In the typical approximation for a linear device it is given by

$$\frac{d\langle \overline{I^2} \rangle}{df} = \frac{4}{3} k_B \ T \ g_m \tag{3.12}$$

with  $k_B$  as the Boltzmann constant, T as the absolute temperature and  $g_m$  as the transconductance of the transistor defined as  $g_m = \frac{\partial I_{DS}}{\partial U_{GS}}$  [30]. In this approximation the spectral distribution of the thermal noise is independent of the frequency and for this reason generally termed white noise. The quantum mechanical solution includes a cutoff frequency where the spectral noise density drops exponentially and thus guarantees its integrability. Since the bandwidth of semiconductor radiation detectors is limited to frequencies far below the cutoff frequency, the cutoff can be neglected.

## 3.3.3. 1/f noise

The physical reasons for 1/f noise are myriad, many of them are caused by statistical fluctuations in the number of charge carriers and their changing mobility.

For a MOSFET, like the ones used for DEPFET sensors, it is strongly related to the Si-SiO<sub>2</sub> interface where the structure abruptly changes from the crystalline Si to the amorphous SiO<sub>2</sub>. This transition leads to unsaturated covalent bindings of silicon atoms called dangling bonds. Usually, dangling bonds are saturated by annealing in a hydrogen atmosphere during the production process - a few will remain, however. If charge carriers in the transistor channel pass a dangling bond they can be trapped, resulting in a reduction of channel conductivity. The probability of this depends on the capturing cross section and on carrier density in the vicinity of the trap. Due to its thermal energy, the trapped charge can be reemitted after a certain delay, thereby leaving the active trap behind. The probability for reemission depends on the energy level of the trap within the band gap, the device temperature, and the electric field conditions (Poole-Frenkel effect).

Similar to thermal noise, the 1/f noise can be modeled by a drain current noise with the spectral power density of

$$\frac{d\langle \overline{I^2} \rangle}{df} = \frac{K_F \ g_m^2}{W \ L \ C_{ox}^2} \frac{1}{f}.$$

(3.13)

The parameter  $K_F$  is characteristic for the technology of the production process and is correlated to the existing trap density in the vicinity of the channel. The transistor geometry consists of the gate length L, the gate width W and the capacitance of the gate insulator  $C_{ox}$  [30]. Frequency dependence in MOSFETs is approximately 1/f and can be derived by assuming various different traps with a continuous distribution of time constants for capturing and reemission.

#### 3.3.4. Shot noise

Shot noise in a semiconductor radiation detector is caused by leakage current in the sensor. Thermally generated leakage current refers to all electron-hole pairs that were not generated as a result of the radiation which should be detected. Generally, it is composed of gate, surface, and bulk leakage current, but for DEPFETs, the bulk leakage current is the most prevalent type.

The excitation probability p of charge carriers over a forbidden energy gap  $E_{gap}$  can be approximated by the Boltzmann statistic according to:

$$p \propto e^{-\frac{E_{gap}}{2k_BT}} \tag{3.14}$$

with  $k_B$  being the Boltzmann constant and T the device temperature. Generation probability increases exponentially by lowering the  $E_{gap}$ , which makes energy levels in the middle of the band gap (deep traps) the most efficient generation centers because they serve as an intermediate state for the excitation of electrons from valence into the conduction band. Deep traps in the silicon bulk contribute to the volume leakage current and can arise either from impurities in the crystal lattice, crystal defects caused by the production process or from irradiation with massive particles like protons (compare section 3.1.2). In addition,

dangling bonds at the Si-SiO<sub>2</sub> interface also possess energy levels roughly in the middle of the band gap and cause so-called surface leakage current. For a DEPFET sensor, this contribution is negligible because surface generated electrons are removed from the device by dedicated contacts. Taking into account only deep traps, the leakage current can be halved by a temperature reduction of roughly 7 K. To minimize the leakage current also high electric fields close to breakdown field strength have to be avoided in the sensor as they may lead to avalanche effects.

To model shot noise, we take an assumed current source to charge the internal gate with a constant leakage current  $I_l$

$$I_l = \frac{\Delta Q}{\Delta t} = \frac{\Delta N \cdot e}{\Delta t}.$$

(3.15)

Here e denotes the elementary charge and  $\Delta N$  the number of electrons arriving in the internal gate during the time interval  $\Delta t$ .

With statistical fluctuations of the number of arriving electrons  $\delta \Delta N = \sqrt{\Delta N}$  the standard deviation of the transistor current can be described by

$$\langle \delta I_l^2 \rangle = \frac{e^2 (\delta \Delta N)^2}{\Delta t^2} = \frac{e^2 (\Delta N)}{\Delta t^2} = \frac{I_l e}{\Delta t}.$$

(3.16)

Spectral noise density can be derived from this, assuming that potential distribution is not changed by any electron previously collected in the internal gate:

$$\frac{d\langle \overline{I_l^2} \rangle}{df} = 2I_l e. \tag{3.17}$$

It should be pointed out that shot noise especially affects sensor devices with large active volumes where the arriving leakage current in the internal gate is high. These devices have to be cooled in order to reduce shot noise and achieve good energy resolution. However, for large sensors with a lot of small pixels, shot noise will only play a minor role.

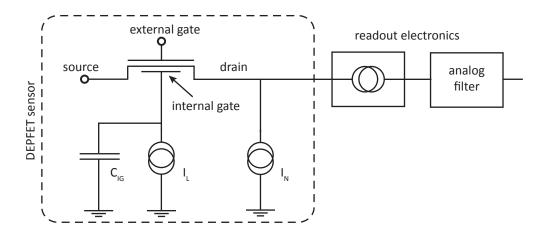

#### 3.3.5. Energy resolution

In order to calculate the achievable energy resolution of a semiconductor radiation detector, all noise sources have to be considered, as is done in Figure 3.6 for the drain readout concept. In this case, the information about energy deposition is obtained by measuring the change in the transistor current, which means all noise is modeled using two current noise sources:  $I_L$  and  $I_N$ . Thermal and 1/f noise are represented by  $I_N$  inducing a noise current parallel to the transistor. Leakage current and any involved fluctuations are represented by  $I_L$ .

For drain readout, all DEPFET voltages are kept at fixed potentials. For the drain, this is guaranteed by a current buffer that also ensures that the transistor current is not influenced by the electronics outside the sensor. Downstream of the current buffer, the analog current signal is filtered before it can be processed.

**Figure 3.6:** Noise model for drain current readout of a DEPFET sensor. Thermal and 1/f noise are modeled by the noise current source  $I_N$  and the leakage current and any involved fluctuations are represented by  $I_L$ .

To receive the r.m.s. noise value at the output point of the electronics, spectral densities (compare previous sections) have to be integrated over the full bandwidth of the system. According to [39], when applying this to the system shown in Figure 3.6, one gets an electronic noise of

$$ENC^{2} = a'A_{1}\frac{1}{\tau}\frac{1}{g_{q}^{2}} + 2\pi a'_{f}A_{2}\frac{1}{g_{q}^{2}} + bA_{3}\tau.$$

(3.18)

In this notation, noise is shown in terms of equivalent noise charge (ENC), i.e. the number of electrons that has to be collected in the internal gate in order to get a signal equivalent to the r.m.s. noise at the output. The constants  $A_1$ ,  $A_2$  and  $A_3$  are defined by the shape of the analog filter (weighting function) while  $\tau$  denotes its specific time constant (shaping time). In addition,  $g_q = \frac{\partial I_{DS}}{\partial Q_{IG}}$  represents the amplification of the internal gate and the spectral densities of the individual noise contributions are denoted by the constants

$$a' = \frac{4}{3}k_B T g_m$$

(thermal noise) (3.19)

$$a'_f = \frac{K_F g_m}{W L C_{ox}^2}$$

(1/f noise) (3.20)

$$b = 2I_l e$$

(shot noise) (3.21)

To optimize noise performance, the weighting function and the related shaping time have to be adjusted for every specific application. For example, if the detector has large pixels and is operated at high temperatures, the shaping time should be short in order to reduce shot noise. By contrast, thinking of a matrix with small pixels operated at very low temperatures, it may be better to have a longer shaping time to decrease thermal noise. Finally, the energy resolution  $\Delta E$  of a semiconductor radiation detector, usually expressed in the Full Width at Half Maximum (FWHM) of the Gaussian peak in the energy spectrum

for a constant energy deposition  $E_0$ , is given by

$$\Delta E \approx 2.355 \cdot w \cdot \sqrt{ENC^2 + \frac{F \cdot E_0}{w}}.$$

(3.22)

$ENC^2$  represents the electronics noise and  $\frac{F \cdot E_0}{w}$  is Fano noise with w being the pair generation energy and F the Fano factor of the detector material. The factor 2.355 is due to the conversion from standard deviation to the FWHM of a Gaussian peak.

Assuming perfectly noise-free electronics ( $ENC^2 = 0$ ), the achievable energy resolution is defined by the so-called Fano limit  $\Delta E_{Fano}$ .

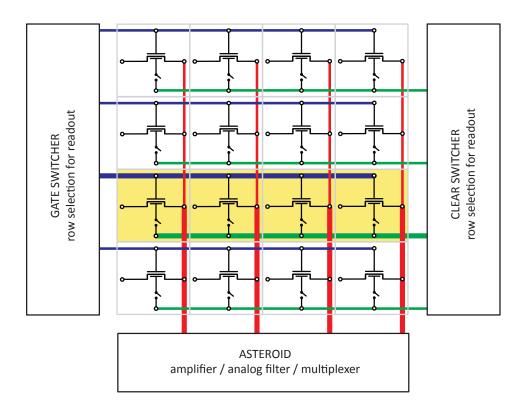

## 3.4. Matrix operation

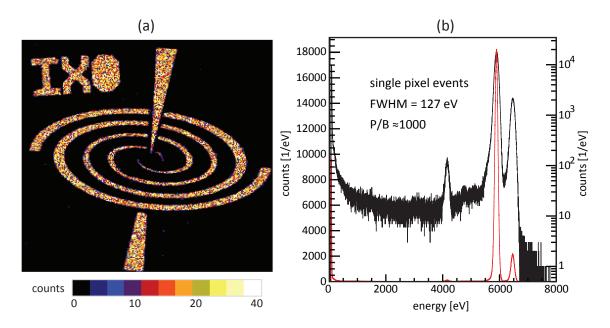

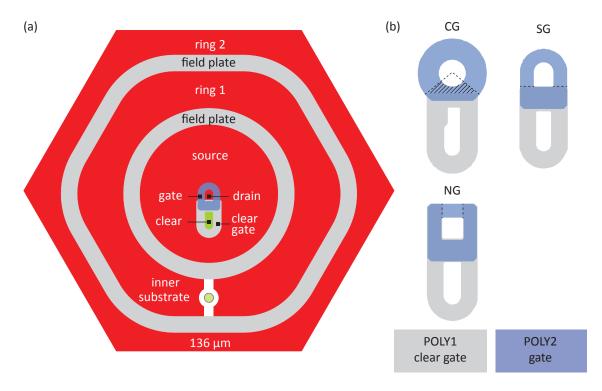

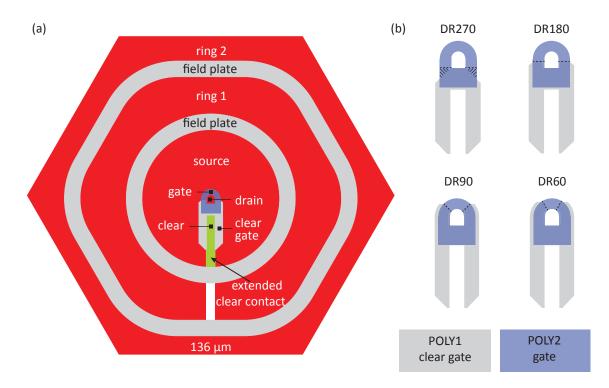

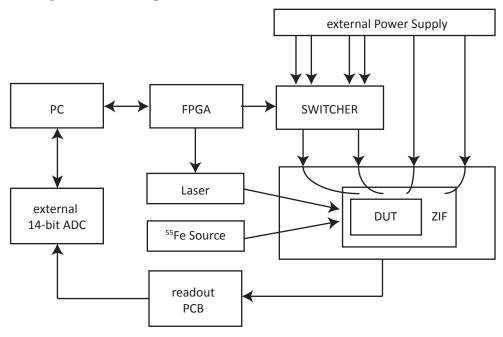

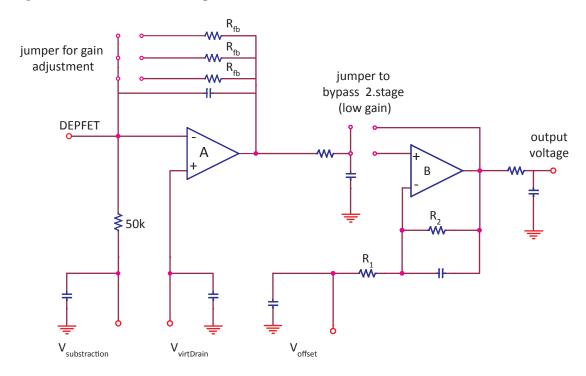

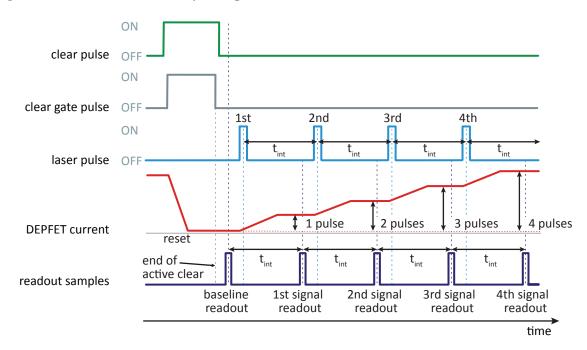

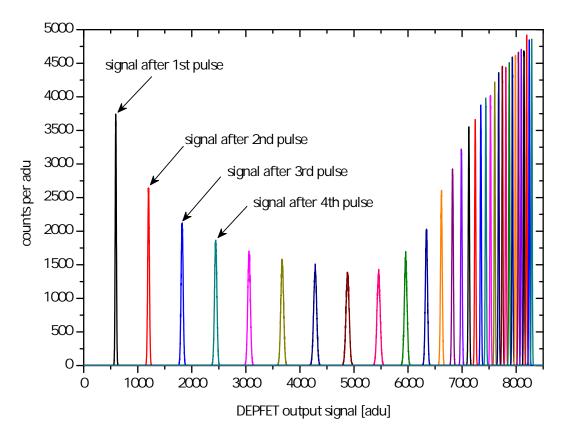

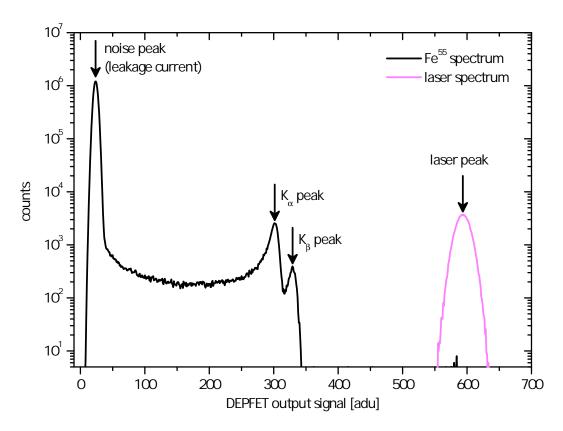

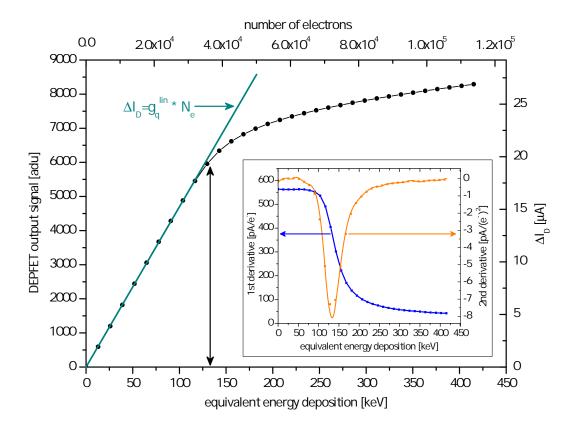

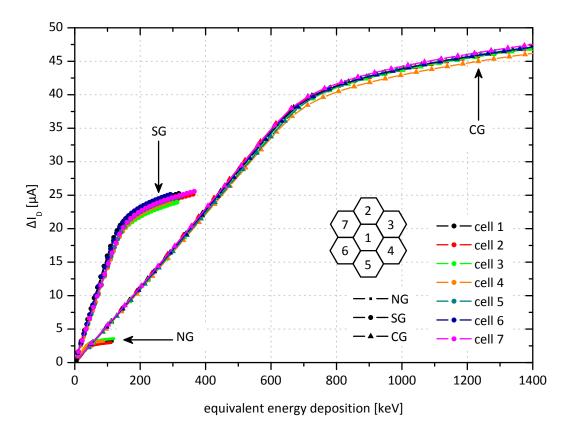

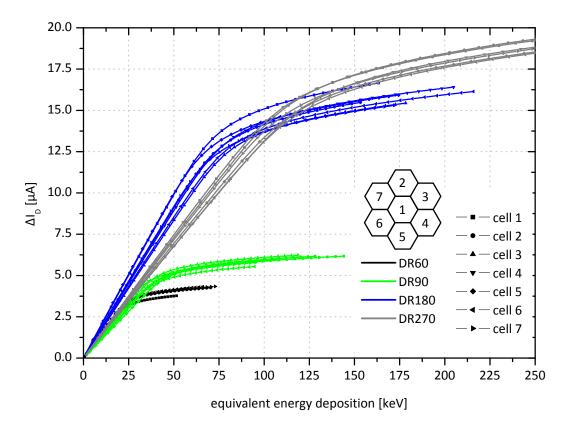

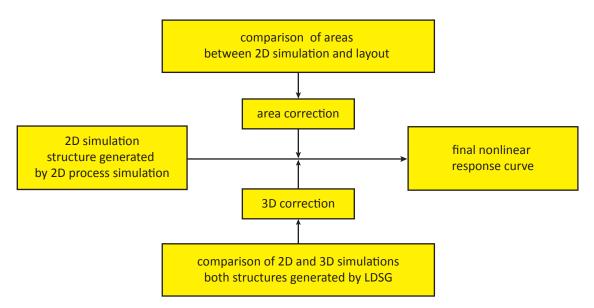

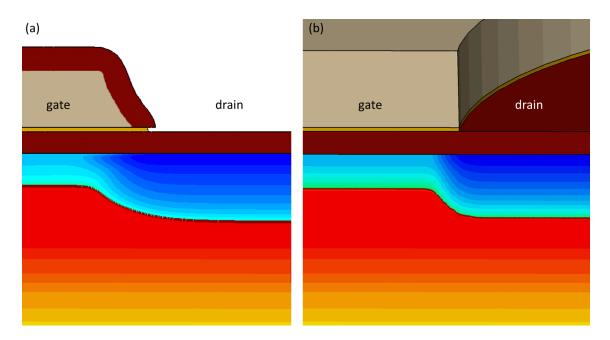

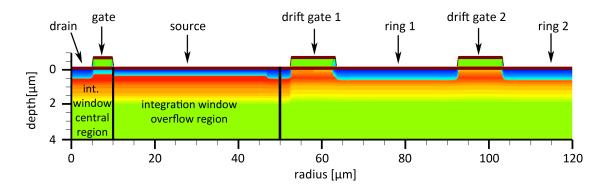

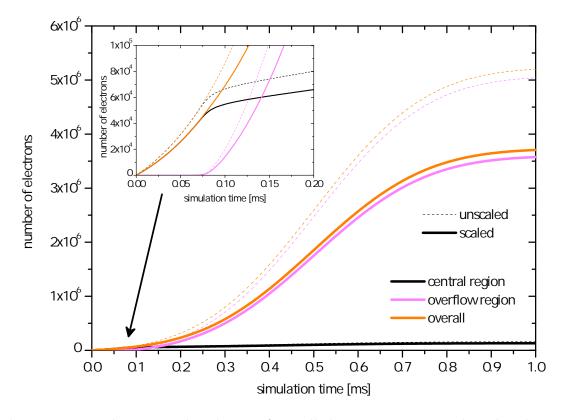

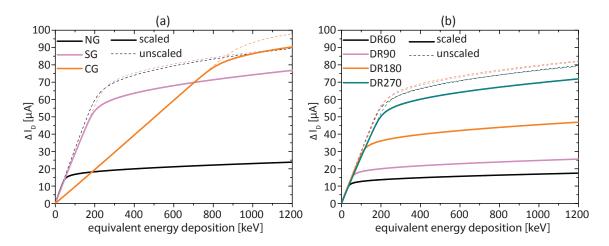

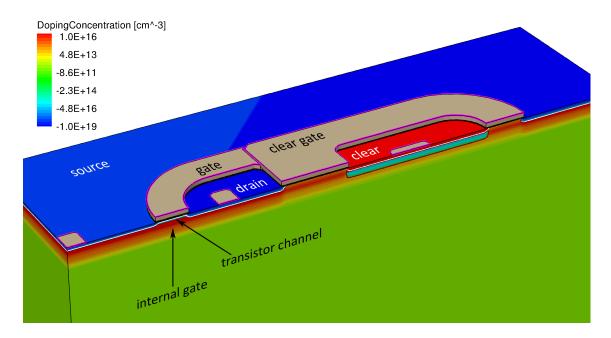

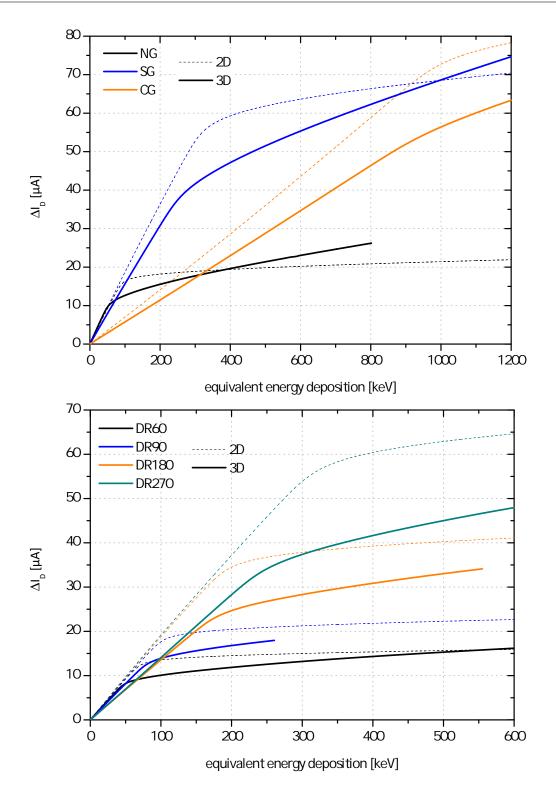

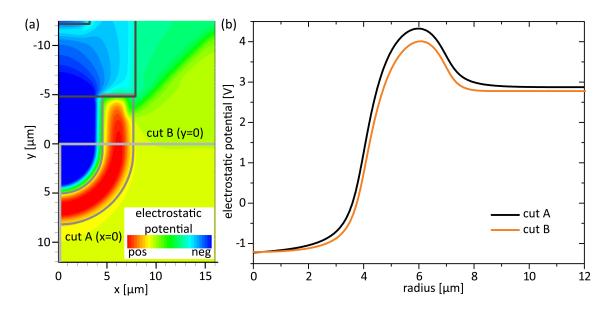

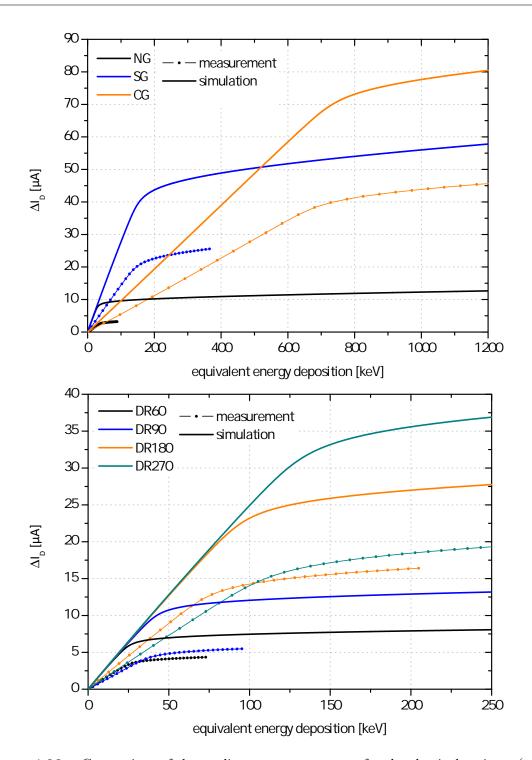

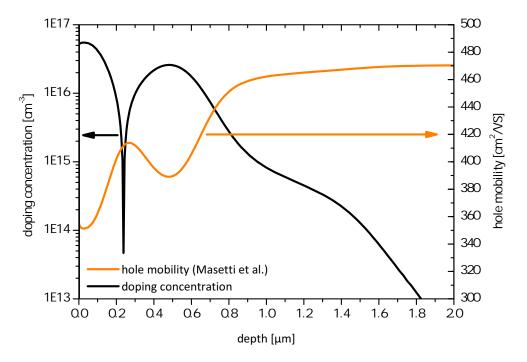

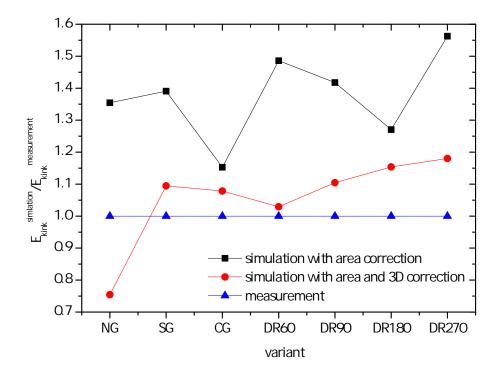

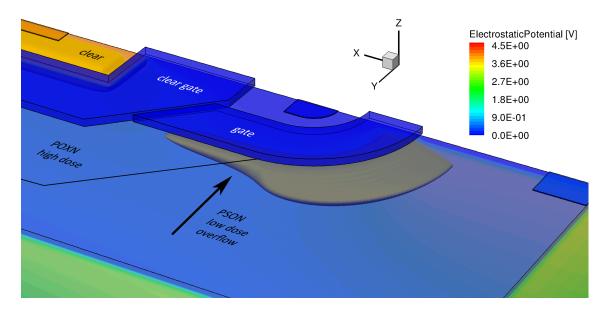

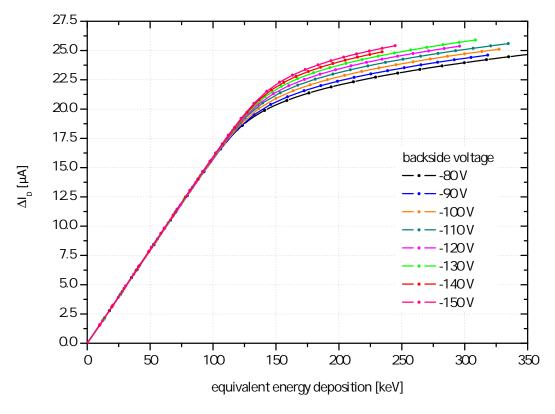

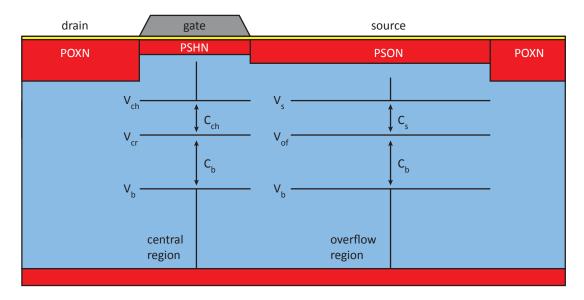

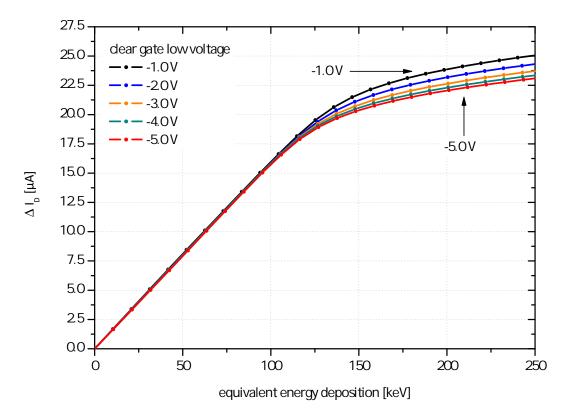

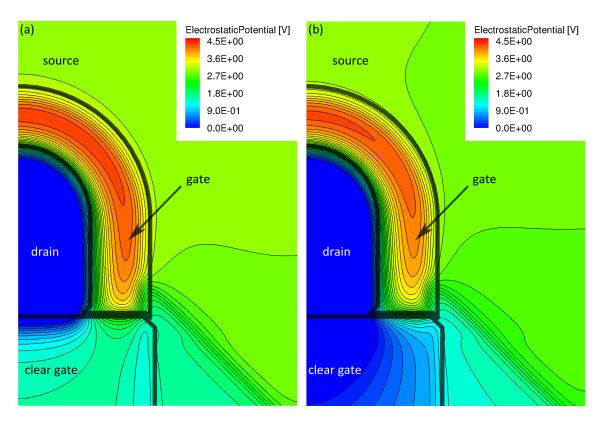

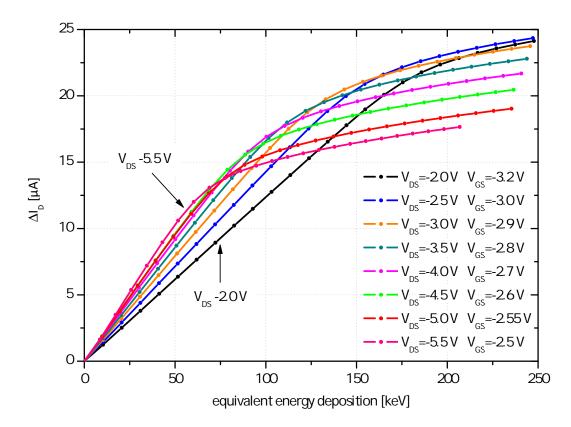

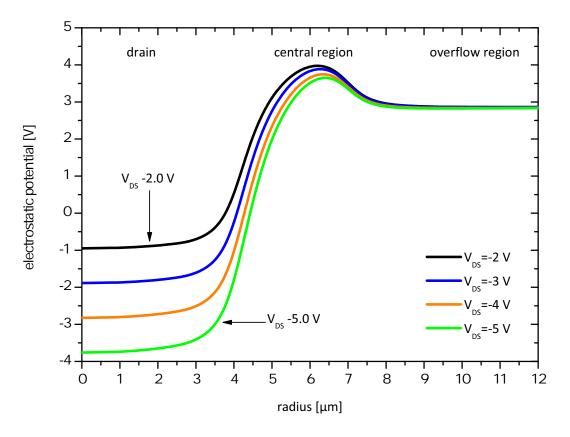

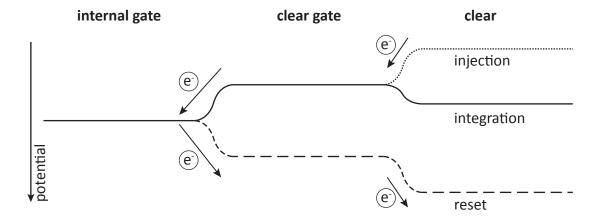

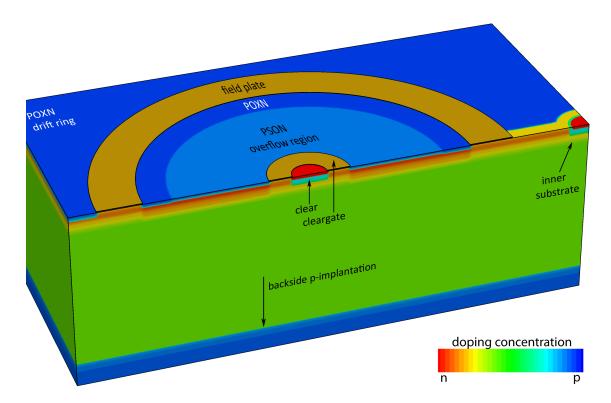

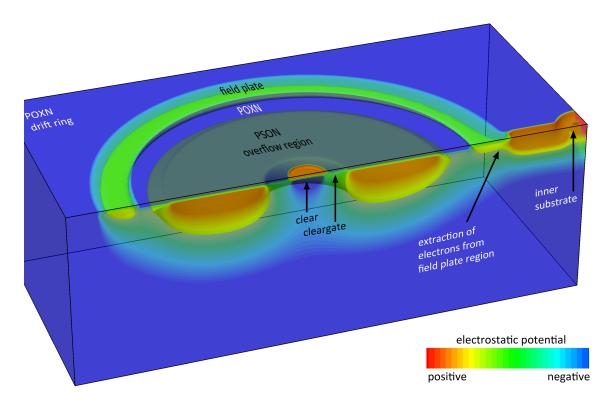

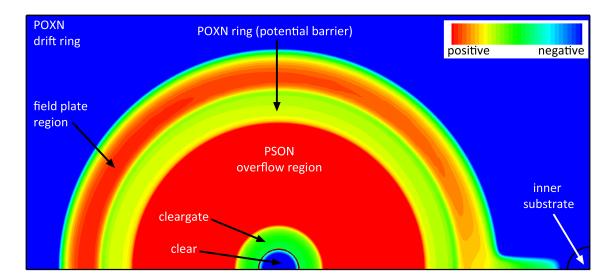

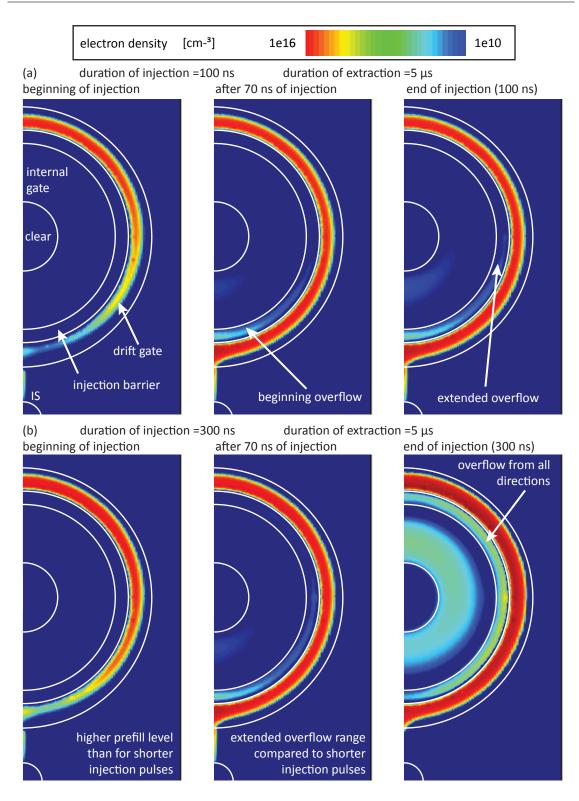

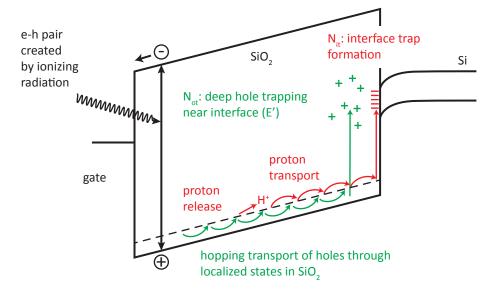

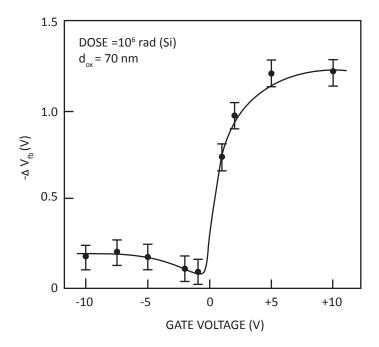

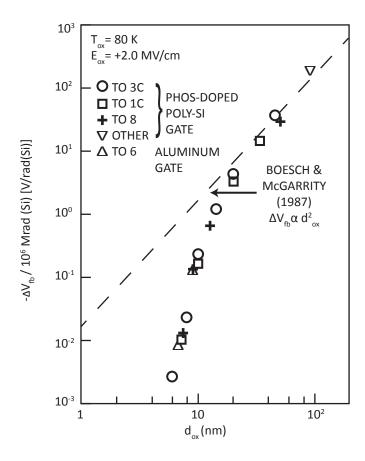

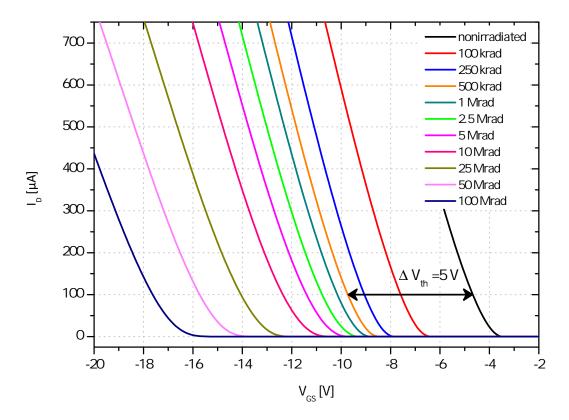

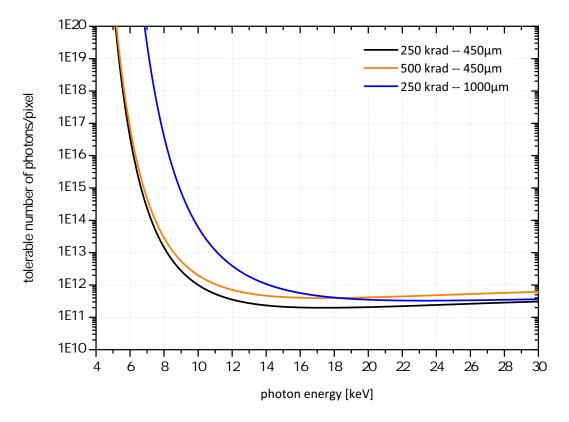

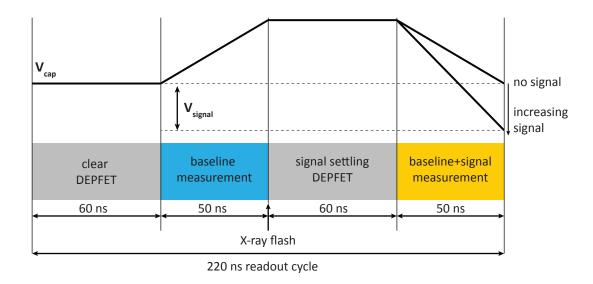

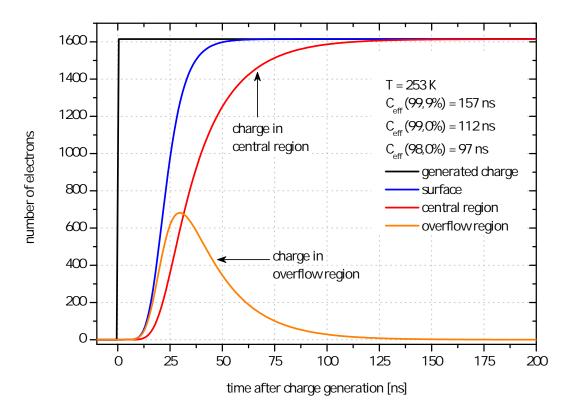

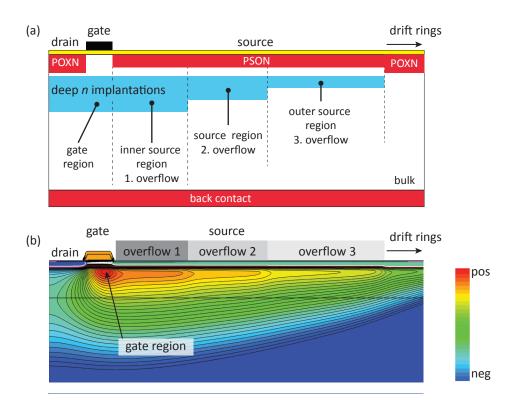

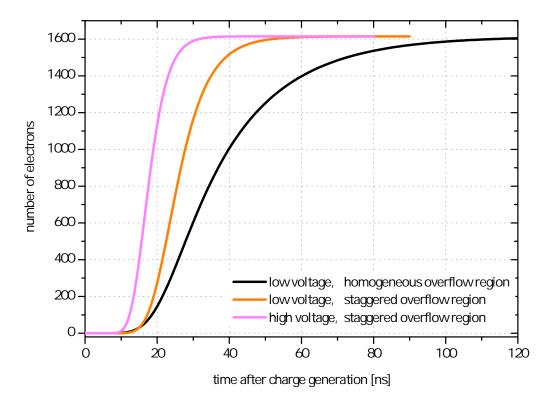

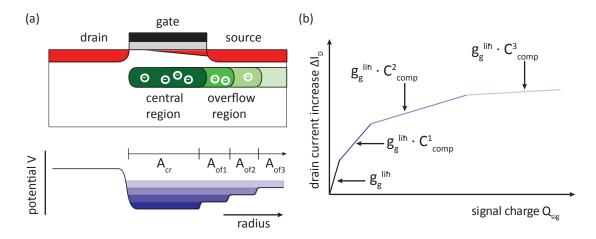

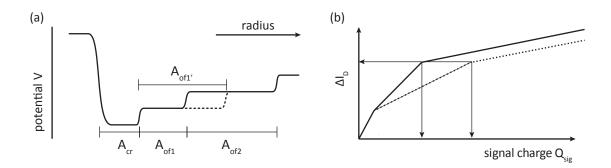

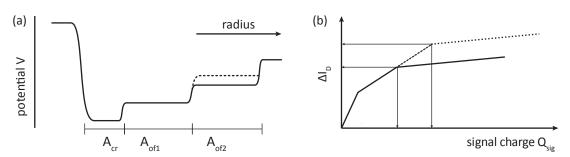

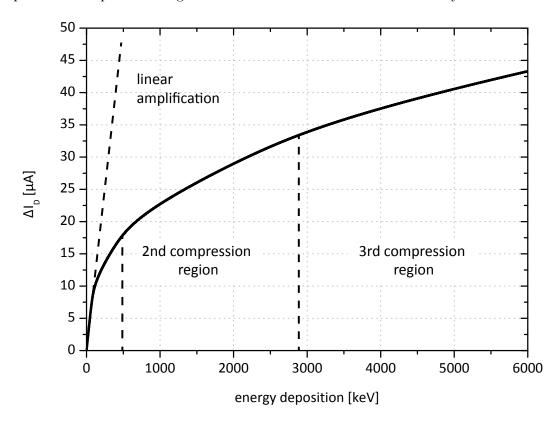

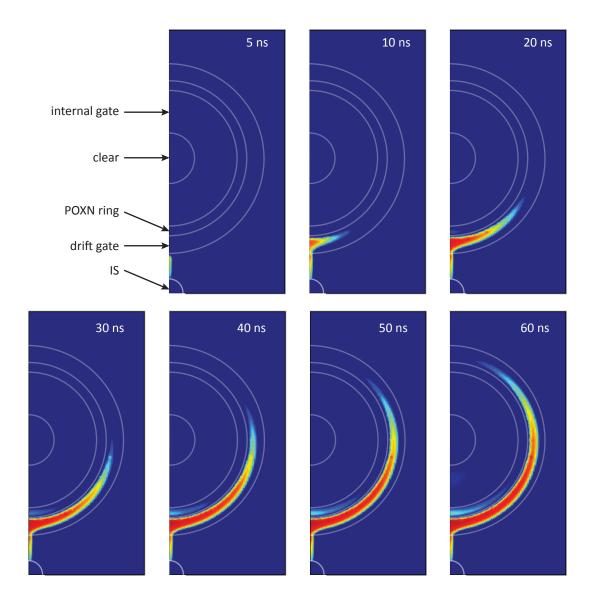

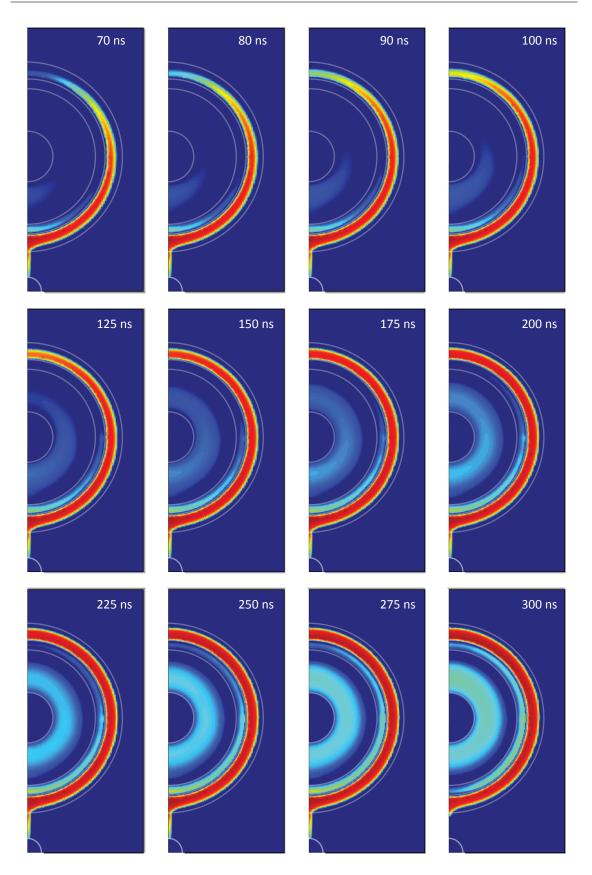

The DEPFET is often utilized as a unit cell for 2D imaging detectors. The readout of these 2D pixel matrices has been performed row by row until now. Figure 3.7 illustrates the standard interconnection scheme of a DEPFET pixel matrix in the source follower configuration.