#### TECHNISCHE UNIVERSITÄT MÜNCHEN

#### Lehrstuhl für Realzeit-Computersysteme

# Schedule Synthesis for Time-Triggered Automotive Architectures

Florian Richard Sagstetter

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

**Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. sc. techn. Andreas Herkersdorf

Prüfer der Dissertation: 1. Univ.-Prof. Dr. sc. Samarjit Chakraborty

2. Prof. Dr. Zebo Peng, Linköping University, Schweden

Die Dissertation wurde am 14.09.2015 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.05.2016 angenommen.

# Acknowledgements

This thesis is the result of four years of research at TUM CREATE in Singapore. It would not have been possible without the support of many people.

First, I would like to express my deepest gratitude to my supervisor Prof. Dr. Samarjit Chakraborty for his encouragement, guidance and support during this time. I very much appreciate all the fruitful discussions and his continuous interest in my work. I would also like to thank Prof. Dr. Zebo Peng for taking the time to act as a reviewer for this thesis.

I am also especially indebted to Prof. Dr. Martin Lukasiewycz for his patience when introducing me to research and paper writing from the beginning of my PhD. I am grateful for having had such a dedicated advisor.

I would also like to thank my colleagues from the Embedded Systems group at TUM CRE-ATE for all the pleasant coffee and lunch breaks, and all the technical and non-technical discussions. You made the work environment at TUM CREATE an enjoyable one.

Finally, I would like to thank my girlfriend Florence Chen, my parents Eva and Georg Sagstetter, my brother Michael Sagstetter and my uncle Rudolf Seeberger for supporting and believing in me.

### **Abstract**

Recent years have seen a strong increase in the functionality in vehicles based on software and electronics. A growing number of these functions like advanced driver assistance systems or the upcoming drive-by-wire have strict timing requirements. As a result, a clear trend towards time-triggered systems for safety-critical functionality can be seen in the automotive domain. Time-triggered communication buses such as FlexRay and Automotive Ethernet provide the necessary basis for these systems. Time-triggered systems increase the safety and control quality due to their deterministic behavior and minimal jitter. Moreover, simulation, integration, and testing efforts are significantly reduced due to the predictability of the system. However, determining a time-triggered schedule is a challenging task as various constraints have to be taken into account concurrently.

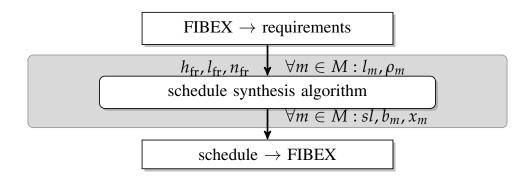

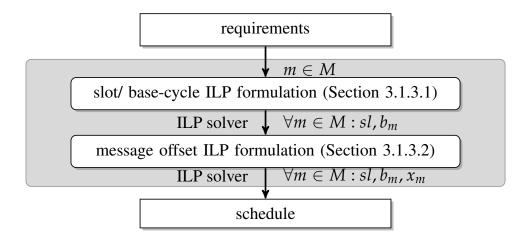

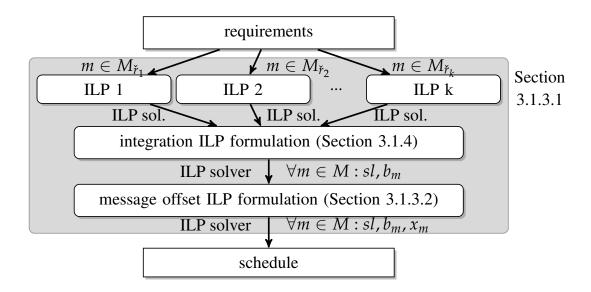

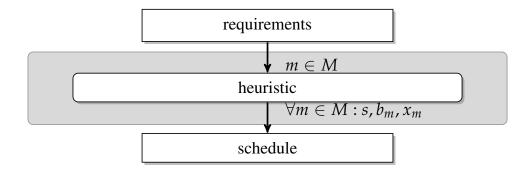

This thesis investigates various aspects of the schedule synthesis for time-triggered architectures in the automotive domain. It addresses the problems of (1) determining schedules for the automotive FlexRay bus, (2) modular schedule synthesis, addressing the problem of integrating independently developed functionality in a system and (3) concurrent schedule synthesis for various architecture variants. The contributions are as follows.

- (1) A schedule synthesis framework for the FlexRay bus is proposed. FlexRay is a latest-generation automotive bus supporting a high bandwidth and a time-triggered communication. The proposed approaches support the recently introduced FlexRay 3.0, while being compatible with the current industry standard version 2.1. Three schedule synthesis approaches are proposed. (a) An Integer Linear Programming approach determining an optimal solution, (b) a heuristic with good scalability, and (c) a schedule integration approach capable of combining previously generated subsystem schedules to a global schedule.

- (2) A schedule integration approach exploiting the predictability of time-triggered systems is proposed. It allows to generate individual application or subsystem schedules and integrates them into a global schedule in a second step. As the schedule integration does not change the general structure of the subsystem schedules, the previously defined constraints are not affected. Through this divide-and-conquer approach the complexity is significantly reduced while the system becomes highly composable. This approach allows to add or update applications in an iterative process, measurably reducing the integration efforts. During schedule synthesis, all tasks executed on distributed Electronic Control Units (ECUs) and messages sent on communication buses are taken into account. The proposed framework supports heteroge-

neous architectures based on FlexRay and Automotive Ethernet. Several metrics are presented to optimize subsystem schedules to improve the integration results.

(3) Finally, a multi-schedule synthesis is proposed which allows to generate individual system schedules for different vehicle variants while assigning identical schedules to common parts. It allows to clearly reduce testing and integration efforts as it only has to be done once for common parts. This variant-aware schedule synthesis first identifies commonality between different variants, before applying a schedule synthesis for common parts, and finally, integrating uncommon parts. As the complexity of multi-schedule synthesis is significantly increased compared to conventional approaches, we also propose a divide-and-conquer approach based on schedule integration to partition the problem, thus, clearly improving the scalability.

# Kurzfassung

In den letzten Jahren hat die Bedeutung von Software und Elektronik durch die Einführung neuer Funktionalität im Automobil stark zugenommen. Eine steigende Anzahl dieser Funktionen hat strikte Anforderungen an das Echtzeitverhalten des Systems. Hierzugehören etwa komplexe Fahrerassistenzsysteme oder zukünftige *Drive-by-wire* Systeme. Dies hat zu einem klaren Trend zu zeitgesteuerten Systemen für sicherheitskritische Anwendungen im Fahrzeug geführt. Zeitgesteuerte Bussysteme, wie FlexRay und Automotive Ethernet, bilden die Grundlage für die darunterliegende Architektur. Ein zeitgesteuertes System erhöht die Sicherheit und die Qualität von Regelungsalgorithmen durch sein deterministisches Verhalten und minimalen Laufzeitabweichungen. Außerdem ist der Aufwand für Simulationen, die Integration von Komponenten und das Testen durch das determistische Verhalten des Systems geringer. Allerdings ist die Bestimmung eines Ablaufplanes für zeitgesteuerte Systeme eine herausfordernde Aufgabe, da eine Vielzahl an Randbedingungen eingehalten werden müssen.

Die vorliegende Doktorarbeit beschäftigt sich mit verschiedenen Aspekten der Ablaufplansynthese für zeitgesteuerte Systeme im Automobilbereich. Die Arbeit befasst sich mit den folgenden Problemen: (1) Bestimmung von Ablaufplänen für den FlexRay Bus. (2) Untersuchung eines modularen Ansatzes für die Ablaufplansynthese, der sich mit der Integration unabhänging von einander entwickelter Funktionalität in ein gemeinsames System beschäftigt. (3) Untersuchung einer Ablaufplansynthese für verschiedene Varianten eines Systems. Die Arbeit leistet dabei die folgenden Beiträge:

- (1) Vorstellung einer Ablaufplansynthese für die Nachrichtenübertragung mit dem FlexRay Bus. FlexRay ermöglicht eine hohe Bandbreite und eine zeitgesteute Kommunikation. Die entwickelten Methoden unterstützen die kürzlich vorgestellte Version 3.0 von FlexRay, während sie gleichzeitig auch für den aktuellen Industriestandard 2.1 anwendbar sind. Drei Methoden mit verschiedenen Eigenschaften werden vorgestellt. (a) Ein Verfahren basierend auf Ganzzahliger linearer Optimierung das eine optimale Lösung findet. (b) Eine Heuristik mit hoher Skalierbarkeit. (c) Ein Verfahren zur Integration von Ablaufplänen, welches erlaubt zuvor erstellte Teilsystemablaufpläne in einen gemeinsamen Ablaufplan zu integrieren.

- (2) Vorstellung einer Methodik zur Integration von Ablaufplänen in einen gemeinsamen Ablaufplan. Sie erlaubt die unabhänginge Erstellung von Ablaufplänen für einzelne Anwendungen oder Teilsysteme und integriert diese in einen gemeinsamen globalen Ablaufplan zu einem späteren Zeitpunkt. Die Grundlage für diesen Ansatz bildet das deterministische Verhalten zeit-

gesteuerter Systeme. Da während der Integration die generelle Struktur des Teilsystemablaufplans nicht verändert wird, sind dabei alle zuvor definierten Randbedingungen gültig. Durch die Unterteilung der Ablaufplansynthese in mehrere Schritte wird die Komplexität und damit die Laufzeit reduziert, während das Systemdesign modular wird. Diese Methodik erleichtert es daher, Anwendungen zum System hinzuzufügen oder zu aktualisieren. Das vorgestellte Verfahren berücksichtigt sowohl Tasks auf Steuergeräten als auch Nachrichten, die auf den Kommunikationsbussen ausgetauscht werden. Es unterstützt sowohl FlexRay als auch Automotive Ethernet. Verschiedene Metriken werden vorgestellet, die es erlauben die Ablaufpläne von Teilsystem für die spätere Integration zu optimieren.

(3) Vorstellung einer Methodik zur Erstellung von Ablaufplänen für verschiedenen Varianten eines Systems. Bei der Ablaufplansynthese werden unabhängige Ablaufpläne für jede Variante erstellt, die für gemeinsame Tasks und Nachrichten einen identischen Ablaufplan definieren. Dies verringert den Aufwand für das Testen der Varianten und für die Integration gemeinsamer Komponenten in verschiedene Varianten. Die Methodik ermittelt zunächst Gemeinsamkeiten in verschiedenen Varianten, bevor für diese gemeinsamen Teile ein gemeinsamer Ablaufplan erstellt wird. Anschließend müssen Teile in denen sich die Varianten unterscheiden in den Ablaufplan jeder Variante integriert werden. Da die Komplexität der Ablaufplansynthese dadurch höher als bei konventionellen Ansätzen ist, beinhaltet die Methodik auch eine Partitionierungsheuristik, die es ermöglicht, die Ablaufplansynthese in kleinere Teilprobleme zu partitionieren. Die vorgestellte Integrationsmethodik erlaubt dann die einzelnen Teile in einen gemeinsamen Ablaufplan zu integrieren.

# Contents

| A  | cknow   | ledgem   | ents                                            | iii    |

|----|---------|----------|-------------------------------------------------|--------|

| A۱ | bstrac  | et .     |                                                 | v      |

| Kı | urzfas  | ssung    |                                                 | vii    |

| C  | ontent  | ts       |                                                 | ix     |

| Li | st of S | Symbols  | <b>;</b>                                        | xiii   |

|    | Nota    | ition    |                                                 | . xiii |

|    | Sym     | bols     |                                                 | . xiv  |

| 1  | Intr    | oduction | n and Background                                | 1      |

|    | 1.1     | E/E-arc  | chitecture                                      | . 4    |

|    |         | 1.1.1    | Event-Triggered Systems                         | . 4    |

|    |         | 1.1.2    | Time-Triggered Systems                          | . 5    |

|    |         | 1.1.3    | Comparison of Event- and Time-Triggered Systems | . 6    |

|    | 1.2     | Comm     | unication Buses                                 | . 7    |

|    |         | 1.2.1    | Controller Area Network                         | . 7    |

|    |         | 1.2.2    | Local Interconnect Network                      | . 8    |

|    |         | 1.2.3    | Media Oriented Systems Transport                | . 8    |

|    |         | 1.2.4    | FlexRay                                         | . 9    |

|    |         | 1.2.5    | Automotive Ethernet                             | . 9    |

|    |         | 1.2.6    | Comparison of Automotive Buses                  | . 10   |

|    | 1.3     | Electro  | onic Control Units                              | . 12   |

|    |         | 1.3.1    | OSEK/VDX                                        | . 13   |

|    |         | 1.3.2    | AUTOSAR                                         | . 13   |

|    | 1.4     | Design   | of Automotive E/E-architectures                 | . 14   |

|    | 1.5     | Challer  | nges                                            | . 15   |

|    | 1.6     | Thesis   | Contributions                                   | . 17   |

|    | 1.7     | Related  | d Work                                          | . 19   |

|    |         | 1.7.1    | Message Scheduling on the FlexRay Bus           | . 20   |

|   |      | 1.7.2    | Modular Schedule Synthesis                        | 21 |

|---|------|----------|---------------------------------------------------|----|

|   |      | 1.7.3    | Variant-aware Schedule Synthesis                  | 22 |

|   | 1.8  | Organi   | ization and Bibliographic Notes                   | 23 |

|   | 1.9  | Publica  | ations                                            | 24 |

| 2 | Syst | em Rep   | presentation                                      | 27 |

|   | 2.1  | System   | n Definition                                      | 27 |

|   | 2.2  | Time-7   | Triggered Scheduling                              | 29 |

|   |      | 2.2.1    | Asynchronous Time-Triggered Scheduling            | 31 |

|   |      | 2.2.2    | Synchronous Time-Triggered Scheduling             | 32 |

|   | 2.3  | Time-7   | Triggered Communication Buses                     | 34 |

|   |      | 2.3.1    | Time-Division Multiple Access                     | 34 |

|   |      | 2.3.2    | FlexRay                                           | 35 |

|   |      | 2.3.3    | Automotive Ethernet                               | 37 |

| 3 | Sche | edule Sy | enthesis for FlexRay                              | 41 |

|   | 3.1  | Async    | hronous Time-Triggered Scheduling                 | 42 |

|   |      | 3.1.1    | Related Work                                      | 45 |

|   |      | 3.1.2    | FlexRay Scheduling                                | 47 |

|   |      | 3.1.3    | ILP-based Optimal Schedule Synthesis              | 50 |

|   |      | 3.1.4    | Multi-stage ILP: ILP- based Heuristic Solution    | 54 |

|   |      | 3.1.5    | Greedy Heuristic                                  | 56 |

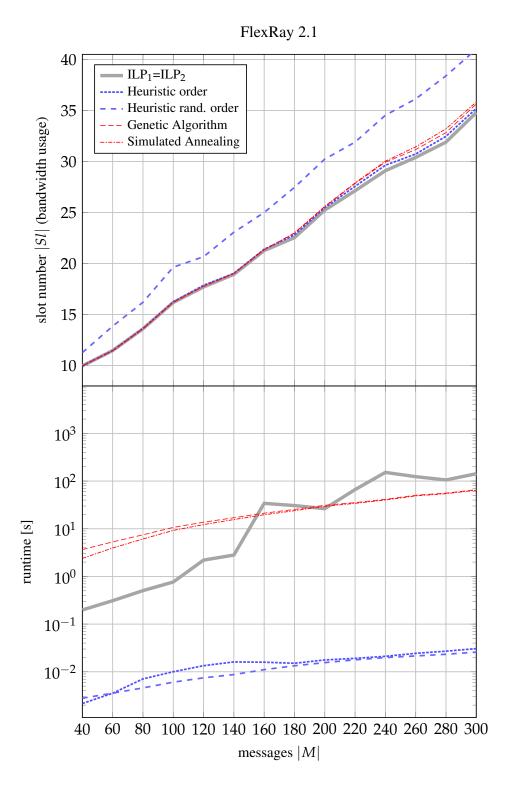

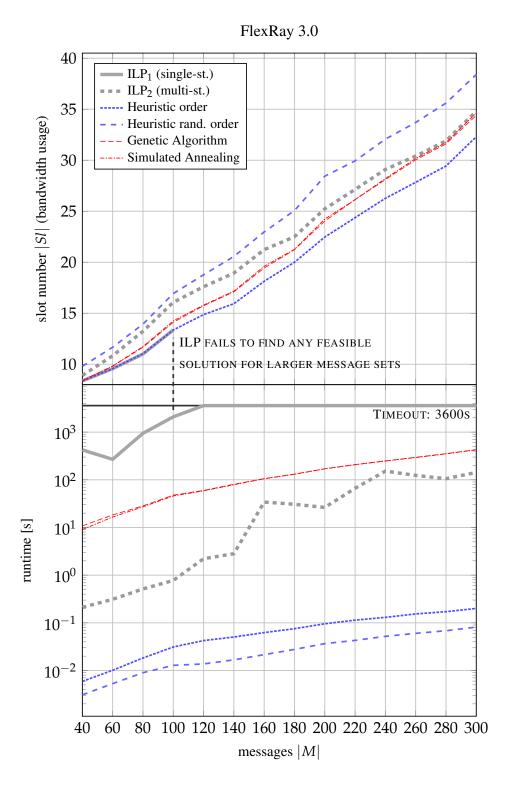

|   |      | 3.1.6    | Experimental Results                              | 62 |

|   |      | 3.1.7    | Summary                                           | 64 |

|   | 3.2  | Synchi   | ronous Time-Triggered Scheduling                  | 65 |

|   |      | 3.2.1    | Related work                                      | 66 |

|   |      | 3.2.2    | Schedule Synthesis                                | 66 |

|   |      | 3.2.3    | FlexRay Scheduling                                | 69 |

|   |      | 3.2.4    | Scheduling for Automotive Ethernet                | 70 |

|   |      | 3.2.5    | Summary                                           | 71 |

| 4 | Mod  | lular Sc | chedule Synthesis for Heterogeneous Architectures | 73 |

|   | 4.1  | Relate   | d Work                                            | 76 |

|   | 4.2  | Frame    | work                                              | 79 |

|   |      | 4.2.1    | Schedule Integration                              | 79 |

|   |      | 4.2.2    | Schedule Integration Framework                    | 82 |

|   | 4.3  | Integra  | ntion                                             | 83 |

|   |      | 4.3.1    | Schedule Integration                              | 83 |

|   |      | 4.3.2    | Conflict Refinement                               | 84 |

|   |      | 4.3.3    | Automotive Ethernet                               | 93 |

|   |      | 121      | FloyDoy                                           | 02 |

|    | 4.4                      | 4 Metrics for Subsystem Scheduling                                         |     |  |  |  |

|----|--------------------------|----------------------------------------------------------------------------|-----|--|--|--|

|    |                          | 4.4.1 Maximize Slack Usage                                                 | 97  |  |  |  |

|    |                          | 4.4.2 Evenly Distribute Processes                                          | 98  |  |  |  |

|    |                          | 4.4.3 Maximize Cumulative Idle Time in Schedule                            | 99  |  |  |  |

|    | 4.5 Experimental Results |                                                                            |     |  |  |  |

|    |                          | 4.5.1 Scalability Analysis for Schedule Integration                        | 100 |  |  |  |

|    |                          | 4.5.2 Feasibility Analysis for Schedule Integration                        | 102 |  |  |  |

|    |                          | 4.5.3 Feasibility Analysis for Integrability Metrics                       | 104 |  |  |  |

|    | 4.6                      | Design Flow: Enabling Highly Modular Architectures Based on Schedule Inte- |     |  |  |  |

|    |                          | gration                                                                    | 107 |  |  |  |

|    |                          | 4.6.1 Data-centric Design                                                  | 108 |  |  |  |

|    |                          | 4.6.2 Data-centric Design Flow                                             | 108 |  |  |  |

|    | 4.7                      | Summary                                                                    | 111 |  |  |  |

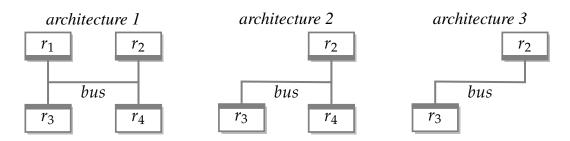

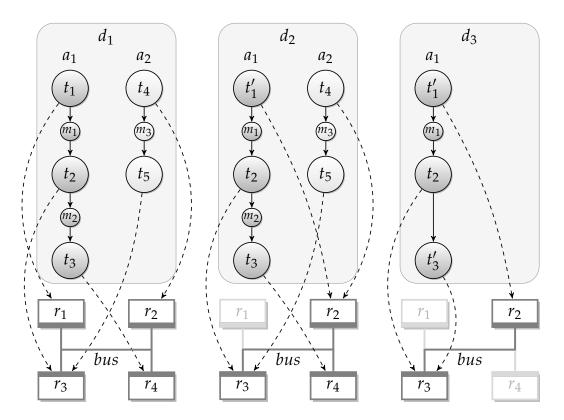

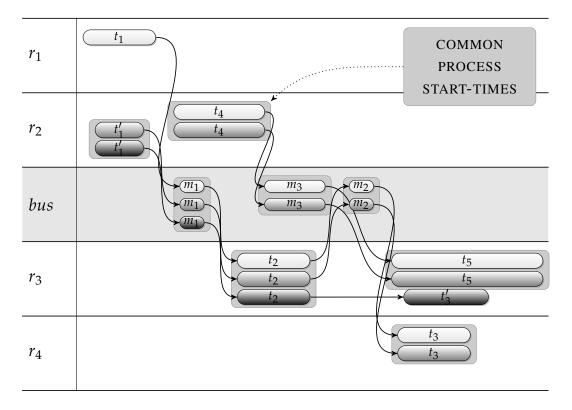

| 5  | Sche                     | edule Synthesis for Variant Management                                     | 113 |  |  |  |

|    | 5.1                      | ·                                                                          | 117 |  |  |  |

|    | 5.2                      | Framework                                                                  | 120 |  |  |  |

|    |                          | 5.2.1 Problem Description                                                  | 120 |  |  |  |

|    |                          | _                                                                          | 120 |  |  |  |

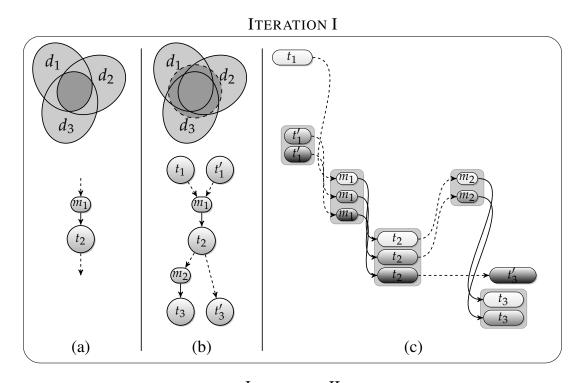

|    | 5.3                      | Multi-Schedule Synthesis                                                   | 123 |  |  |  |

|    |                          | 5.3.1 Methodology                                                          |     |  |  |  |

|    |                          | 5.3.2 Determine Comprehensive Task Graph                                   |     |  |  |  |

|    |                          | 5.3.3 Partitioning                                                         |     |  |  |  |

|    |                          | 5.3.4 Schedule Synthesis                                                   | 130 |  |  |  |

|    |                          | 5.3.5 Conflict Refinement                                                  | 133 |  |  |  |

|    | 5.4                      | Experimental Results                                                       | 133 |  |  |  |

|    |                          | 5.4.1 Resource Utilization                                                 | 134 |  |  |  |

|    |                          | 5.4.2 Analysis of Variant-Awareness                                        | 135 |  |  |  |

|    |                          | 5.4.3 Runtime Analysis                                                     | 137 |  |  |  |

|    |                          | 5.4.4 Automotive Case Study                                                | 138 |  |  |  |

|    | 5.5                      | Summary                                                                    | 142 |  |  |  |

| 6  | Con                      | cluding Remarks                                                            | 143 |  |  |  |

|    | 6.1                      | Summary                                                                    | 143 |  |  |  |

|    | 6.2                      |                                                                            | 144 |  |  |  |

| Bi | Bibliography 147         |                                                                            |     |  |  |  |

|    |                          |                                                                            | 161 |  |  |  |

| Ll | List of Tables           |                                                                            |     |  |  |  |

| Li | st of 1                  | Figures                                                                    | 163 |  |  |  |

List of Acronyms 167

# List of Symbols

## Notation

| $x, \tilde{x}, x_y, \tilde{x}_y$ | constant which might have an index y                                                                                                                            |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| X                                | set of constants $x \in X$                                                                                                                                      |  |  |

| $\mathcal{X}$                    | set of sets $X \in \mathcal{X}$                                                                                                                                 |  |  |

| x                                | variable                                                                                                                                                        |  |  |

| $\bar{\mathbf{x}}$               | binary variable                                                                                                                                                 |  |  |

| $x(\cdot)$                       | function returning constant x                                                                                                                                   |  |  |

| $X(\cdot)$                       | function returning set X                                                                                                                                        |  |  |

| $\delta_x$                       | interval $[\underline{\delta_x}, \overline{\delta_x}]$ where $\underline{\delta_x}$ denotes the lower and $\overline{\delta_x}$ the upper bound of the interval |  |  |

| $\Delta_{\chi}$                  | set of intervals                                                                                                                                                |  |  |

| $G_x=(Y_x,E_x)$                  | graph where $Y_x$ represents the set of nodes of type $y$ and $E_x$ the set of edges                                                                            |  |  |

| ž                                | predecessor of node $x$ in the path of a graph connecting $x$ with other nodes                                                                                  |  |  |

| $\hat{x}$                        | successor of $x$ in the path of a graph connecting $x$ with other nodes                                                                                         |  |  |

#### **Symbols**

а application set of applications in cluster cl  $A_{cl}$  $A_{Cl_{\lambda}}$ set of applications in set of clusters  $Cl_{\lambda}$ set of applications defined by specification d  $A_d$ set of applications defined in the comprehensive task  $A_{\lambda}$ graph  $\lambda$  $b_m$ base-cycle of a FlexRay message m cycle index for FlexRay schedule С  $C_f$ set of cycles occupied by frame f FlexRay parameter defining the number of communica- $C_{\mathsf{fr}}$ tion cycles cl cluster representing a subset of applications  $Cl_{\lambda}$ set of clusters of the comprehensive task graph  $\lambda$ cycles in slot sl suitable to transmit messages sent by  $\check{r}$  $C_{(sl,\check{r})}$ D set of specifications d specification  $D_{IIS}$ subset of clusters defining an Irreducible Inconsistent Set (IIS)  $\mathcal{D}_{IIS}$ set of all Irreducible Inconsistent Sets (ISSs) D(p)returns all specifications the process p is part of е edge  $E_a$ set of edges (data-dependencies) of application a  $E_{cl}$ set of edges (shared resources) between the applications in cluster cl  $E_{Cl_{\lambda}}$ set of edges (shared resources) between the applications in set of clusters  $Cl_{\lambda}$ set of edges (data-dependencies) of specification d  $E_d$

$E_{\text{IISs}}$  set of edges (data-dependencies) which are part of the

Irreducible Inconsistent Sets (IISs)

$E_{\lambda}$  set of edges (data-dependencies) in comprehensive task

graph  $\lambda$

$\check{E}(\phi, p)$  returns all edges (data-dependencies) connecting p with

the source process for the path  $\phi$

$\hat{E}(\phi, p)$  returns all edges (data-dependencies) connecting p with

the sink process for the path  $\phi$

*F* set of frames

f frame in FlexRay schedule

$f_p$  finish-time for process p

$\mathbf{f}_p$  variable for finish-time of process p

$G_a$  graph describing an application a

$G_{Cl_{\lambda}}$  graph describing the set of clusters  $Cl_{\lambda}$

$G_d$  graph describing specification d

$G_{\lambda}$  graph describing an comprehsive task graph  $\lambda$

$h_a$  period of application a

$h_d$  (hyper)-period of specification d

$h_{\rm fr}$  FlexRay parameter defining the period of a cycle

$h_m$  period of a FlexRay message m

$h_p$  period of a process p

$h(p, \tilde{p})$  returns the hyper-period of the two processes p and  $\tilde{p}$

$\mathbf{i}_m$  integer variable to indicate to which slot and base-cycle a

FlexRay message m is mapped

l<sub>fr</sub> FlexRay parameter defining the size of a static slot in

bytes

$l_m$  size of FlexRay message m in bytes

M set of messages

*m* FlexRay message

$M(\check{r})$ returns all messages sent by sender  $\check{r}$ theoretical number of static slots in a full FlexRay cycle  $n_{all}$  $n_{\rm fr}$ FlexRay parameter defining the number of static slots in a communication cycle variable for offset of application a  $\mathbf{o}_a$ variable for offset of cluster d  $\mathbf{o}_d$  $O_{(d,\tilde{d})}$ set with feasible values for which the two cluster d and  $\tilde{d}$ do not intersect variable for offset of FlexRay message m  $\mathbf{o}_m$ variable for offset of process p  $\mathbf{o}_{v}$ process (task or message) p  $P_a$ set of processes of application a  $P_d$ set of processes defined by specification d  $P_{\rm IISs}$ set of processes which are part of the Irreducible Inconsistent Sets (IISs) sink process  $p_{snk}$ source process  $p_{src}$  $P_{\lambda}$ set of processes in comprehensive task graph  $\lambda$ binary variable indicating if the finish-time  $\mathbf{f}_p$  exceeds the  $\bar{\mathbf{q}}_{\mathbf{f}_n}$ process period binary variable indicating if the waiting-time  $\mathbf{w}_{(p,\tilde{p})}$  ex- $\bar{\mathbf{q}}_{\mathbf{w}_{(p,\tilde{p})}}$ ceeds the process period resource r Ř set of resources sending FlexRay messages ř resource sending FlexRay messages R(d)returns all resources to which processes of specification d are mapped to set of all resources that are an Ethernet bus  $R_{eth}$ set of all resources that are a FlexRay bus  $R_{\rm fr}$

$\check{r}(m)$ returns resource message m is sent from r(p)returns the resource process p is mapped to Sl set of slot indexes slindex for FlexRay slot  $sl_m$ slot message m is transmitted in start-time of a FlexRay message m  $S_m$ variable for start-time of a FlexRay message m  $\mathbf{s}_m$  $\operatorname{snk}(\phi)$ returns the sink process for the path  $\phi$ start-time of process p $S_p$ variable for start-time of process p  $\mathbf{s}_{p}$  $src(\phi)$ returns the source process for the path  $\phi$ t time instant binary variable indicating if frame f is scheduled in slot  $\bar{\mathbf{u}}_{(f,sl,b)}$ sl with base-cycle b binary variable indicating ownership of resource  $\check{r}$  for slot  $ar{\mathbf{v}}_{(\check{r},sl)}$ slbinary variable indicating ownership of resource  $\check{r}$  for slot  $\bar{\mathbf{v}}_{(\check{r},sl,c)}$ sl in cycle c waiting-time between the finish-time of a process p and  $w_{(p,\tilde{p})}$ a data-dependent successor  $\tilde{p}$ variable for waiting-time between the two processes p $\mathbf{w}_{(p,\tilde{p})}$ and  $\tilde{p}$ x-offset of a FlexRay message within a slot  $x_m$ integer variable for the x-offset of message m in a  $\mathbf{x}_{m}$ FlexRay slot binary variable indicating if message m is placed before  $\bar{\mathbf{x}}_{(m,\tilde{m})}$ or after message  $\tilde{m}$  in a slot binary variable indicating if p is started before  $\tilde{p}$  $\bar{\mathbf{x}}_{(p,\tilde{p})}$ binary variable indicating if p is started before  $\tilde{p}$  for the  $\bar{\mathbf{x}}_{(p,\tilde{p},i,j)}$ indexes i and j

| $ar{\mathbf{y}}_{sl}$       | binary variable indicating if slot $sl$ is utilized                                              |

|-----------------------------|--------------------------------------------------------------------------------------------------|

| $ar{\mathbf{z}}_{(m,sl,b)}$ | binary variable indicating if message $m$ is sent in the slot $sl$ with the base-cycle $b$       |

| β                           | multi-schedule                                                                                   |

| $\Delta_{(d,	ilde{d})}$     | intervals for which the two cluster $d$ and $\tilde{d}$ do not intersect                         |

| $\delta_d^{	ext{fr}}$       | interval defining feasible cluster offset values for FlexRay communication                       |

| $\delta^{	ext{fr}}_{(d,m)}$ | interval defining feasible cluster offset values for FlexRay message $m$                         |

| $\delta_{\mathbf{o}_p}$     | interval defining boundaries for the process offset $\mathbf{o}_p$                               |

| $O_{(r,d,\tilde{d})}$       | set of intervals for which the two clusters $d$ and $\tilde{d}$ do not intersect on resource $r$ |

| $\eta(p, \mathbf{t})$       | function indicating if a process $p$ utilizes a resource at the time instant ${\bf t}$           |

| $\theta_a$                  | maximum end-to-end delay for application a                                                       |

| $\theta_a$                  | variable for the end-to-end delay of application a                                               |

| Λ                           | set of comprehensive task graphs                                                                 |

| λ                           | comprehensive task graph                                                                         |

| $\Pi_d$                     | describes the constraints of a time-triggered schedule for specification $d$                     |

| $ ho_f$                     | smallest repetition of messages in frame $f$                                                     |

| $ ho_m$                     | repetition of a FlexRay message                                                                  |

| $\sigma(M)$                 | returns a list containing a sorted message set                                                   |

| $	au_a$                     | variable for minimal waiting-time between processes of application $a$                           |

| $	au_{ m fr}$               | FlexRay parameter defining the temporal duration of a static slot in bytes                       |

| $	au_m$                     | transmission time of a message $m$                                                               |

| $	au_p$                     | execution-time of a process $p$                                                                  |

| $oldsymbol{	au}_{p_{	ext{idle}}}$ | variable for maximal idle time between processes on all resources               |

|-----------------------------------|---------------------------------------------------------------------------------|

| $	au_r$                           | variable for lower bound of minimal idle-time between processes on resource $r$ |

| $\Phi(E_a)$                       | returns all paths in the task graph of application a                            |

| $\phi$                            | path in task graph                                                              |

| $\psi(p)$                         | returns the routing for a process $p$ transmitted via an Ethernet bus           |

1

# Introduction and Background

Recent years have seen a strong increase in the number of advanced driver assistance functionality in modern vehicles. Functions like adaptive cruise control, lane departure warning, or pre-crash belt pretensioners make vehicles safer and driving more comfortable. These new functions are enabled by a radical change of automotive architectures from merely mechanical systems to strongly electronics and software-based architectures in the last 30 years. Today, innovation in the car industry is largely based on the software implemented on the Electrical/-Electronic (E/E)-architecture of a vehicle.

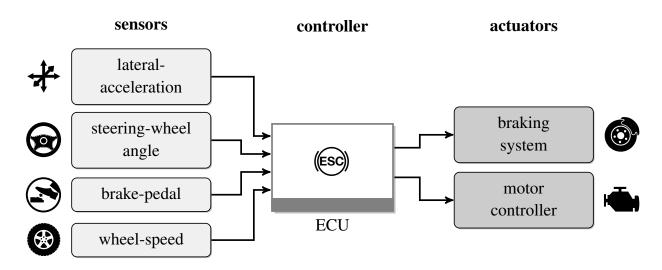

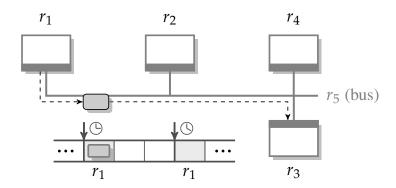

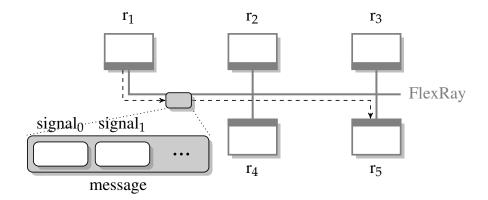

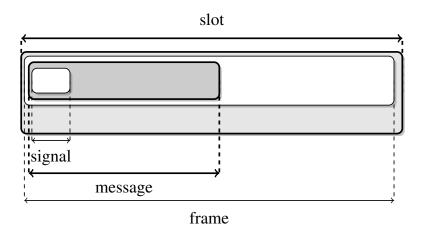

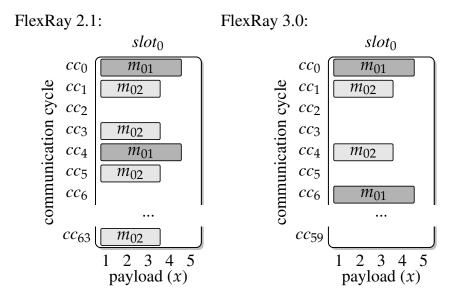

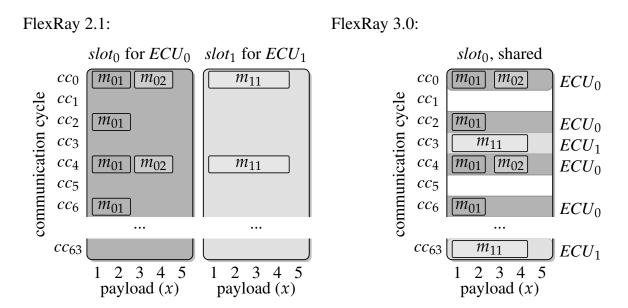

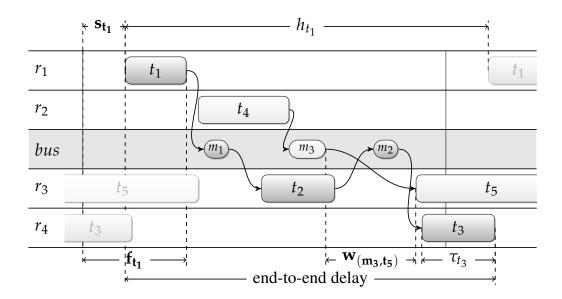

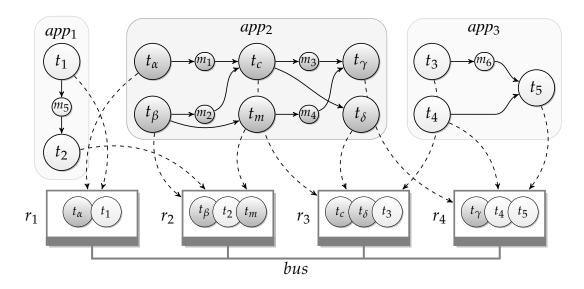

One of the first advanced driver assistance functions was the Electronic Stability Control (ESC). ESC is a safety function which adapts the behavior of the braking system and the drivetrain if necessary. It integrates the functionality of the Antilock Braking System (ABS), preventing the wheels from locking during braking, and Traction Control System (TCS), preventing the wheels from spinning. Both functions ensure that the wheels keep tractive contact with the road. In addition, ESC as a system improves the stability of a vehicle by preventing oversteer and understeer. This is achieved by braking or accelerating a single wheel to adjust the vehicle dynamics. Figure 1.1 illustrates the E/E-architecture of an ESC system. Several sensors provide data to the ESC controller which calculates the current vehicle dynamics and sends control signals to the braking system<sup>1</sup> or the motor control.

Based on the sensor data from the current vehicle speed (i.e. rotational wheel speed), the steering wheel input, and the brake activation, a control algorithm determines the intended vehicle behavior. A sensor measuring the side angle acceleration allows the controller to estimate the

<sup>&</sup>lt;sup>1</sup>The braking system today is commonly realized by an electronically controlled hydraulic power unit, but might be replaced by brake-by-wire technology in the near future.

**Figure 1.1:** Schematic illustration of the E/E-architecture of an Electronic Stability Control (ESC) system. The ESC controller is connected to multiple sensors and controls the braking system. The ESC controller also provides the motor controller with control instructions and data. The controller is implemented on an Electronic Control Unit (ECU). See [Rob14] for details.

slip angle deviating from the intended vehicle behavior. Based on this estimate, the controller determines suitable values for the speed of each individual wheel and instructs the brake system to slow down a certain wheel, or the motor controller to accelerate a wheel. ESC is a complex control function which not only has to accurately determine its control instructions but also has to do so in the time frame of a few milliseconds to efficiently stabilize the vehicle [Rob14].

Since the introduction of ESC in 1995, various additional advanced driver assistance functions based on software and electronics have been introduced, like Adaptive Cruise Control (ACC) or pedestrian detection. Today, the electrical and electronic parts of a vehicle already account for more than 30% of the production costs of a vehicle, despite the decreasing cost of electronic components in general [Cha09, Rob14]. This trend will continue, as most new advanced functions are electronics and software-based. All of these functions have in common that they are highly distributed systems, accessing various sensors and actuators. For instance, for ESC the location of senors and actuators, e.g., the rotational speed sensor at each wheel and the input senor for the steering wheel angle, require a distributed control system. For more advanced functions like ACC, allowing a semi-autonomous driving at low speeds, this effect is even increased, as additional location constraint sensors and actuators, e.g., a radar sensor, are required [BCG12].

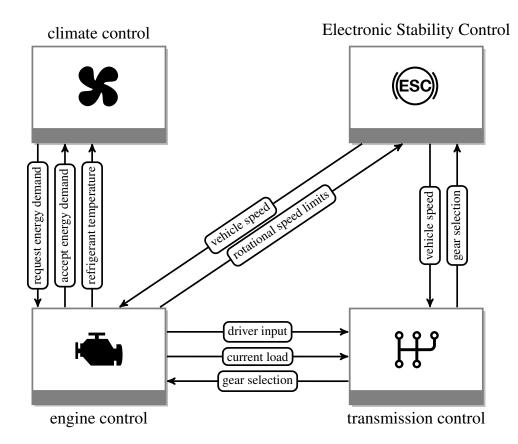

Control functions like ESC or ACC are implemented on Electronic Control Units (ECUs). While it would be generally feasible to connect ECUs with point-to-point connections, in reality this is not practical as many functions require common data or interact with each other. Figure 1.2 illustrates the data exchanged between four ECUs: The ESC, the engine control, the

**Figure 1.2:** Schematic illustration of data exchanged between 4 ECUs. In modern vehicles the communication of an ECU is not limited to the communication with sensors and actuators, but ECUs also exchange various data between each other, both in the form of control instructions as well as information.

transmission control and the climate control. As mentioned, the ESC controller sends instructions to the engine control, but it also provides the current vehicle speed, calculated from the wheel rotation speed. Hence, instead of having multiple controllers access the wheel rotation speed sensor individually, only the ESC-ECU has direct access to the sensor and provides the calculated vehicle speed to the other ECUs. The ESC also receives the rotational speed limits from the engine controller to ensure that the instructions sent to the engine controller do not stall the engine. Similarly, the engine controller communicates with various ECUs. To fulfill the strict emission requirements and to improve the performance, engine control units of modern vehicles employ highly complex algorithms to determine the optimal point in time and the right amount of fuel to inject [SCTQ09]. The control algorithm therefore not only relies on sensor data of the crankshaft position and the instructions from the gas pedal, but also on the current vehicle speed or the information of the current gear selection in the transmission. For instance, the engine control requires data from the transmission to maintain a minimal engine speed during idle mode, i.e., if no gear is currently selected. But also functionality like the

climate control interacts with the engine control, e.g., to request an increased energy demand, or to adjust the engine cooling [Bor14]. This small excerpt from the in-vehicle communication shows the strong connectivity between different functions. As a consequence, the point-to-point connections between individual ECUs have been replaced by a networked architecture in state-of-the-art vehicles. Communication buses connect multiple ECUs and allow them to exchange messages with each other.

#### 1.1 E/E-architecture

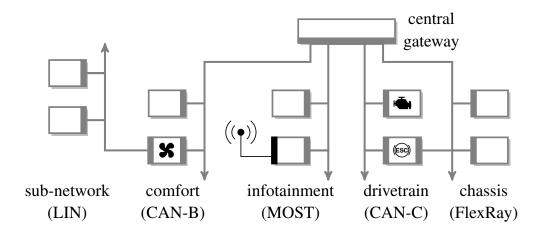

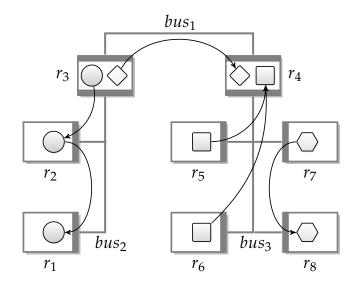

In Figure 1.3, the network structure of an automotive E/E-architecture is illustrated. A state-of-the-art in-vehicle network might consist of up to 100 ECUs connected through shared communication buses [Cha09]. To handle the complexity of more than 2000 individual functions [Bro06], the E/E-architecture is organized in domains. A domain groups functionality based on relations between functions, i.e., data dependencies, as well as safety and hardware requirements, e.g., predictability and reliability. Car manufacturers commonly group their domains in the following four groups: (1) The *comfort* domain containing body and cabin systems, e.g., the climate control. (2) The *infotainment* domain containing display and entertainment systems. (3) The *drivetrain* domain containing drivetrain and emission control systems, e.g., the engine control and transmission control. (4) The *chassis* domain containing vehicle motion, safety and driver assistance functions, e.g., the damper control [Rob14]. A central gateway connects the domains and allows communication between ECUs from different domains<sup>2</sup>.

Each domain has very different requirements. For the comfort domain, flexibility and seam-less integrability of various individual functions are required [Rob14, ZS14]. The infotainment domain has a high demand in bandwidth to transfer audio or video data [Bor14]. Finally, in the drivetrain and chassis domain the focus is on hard real-time functionality and reliability [Rob14, ZS14]. As a consequence, automotive E/E-architectures are highly heterogeneous systems with a mix of different communication buses, depending on the domain. Latest-generation in-vehicle networks therefore often implement both event-triggered as well as time-triggered systems in the E/E-architecture.

#### 1.1.1 Event-Triggered Systems

An event-triggered system reacts to an incoming event, e.g., the press of a button on the air-conditioning control field, or the motor speed dependent sensor reading for the current piston position of the engine controller [Rob14]. As event-triggered systems are not synchronized with each other, two ECUs might try to access a shared communication bus at the same instant. A collision avoidance in modern communication buses ensures that only one ECU is allowed

<sup>&</sup>lt;sup>2</sup>Note that the general structure of the network might differ between different car manufacturers, e.g., instead of having a central gateway, domain gateways might be connected by a backbone bus. However, most manufacturers follow a domain-based architecture with a fully connected in-vehicle network. See [Rei14, Rob14] for details.

**Figure 1.3:** Structure of the E/E-architecture of state-of-the-art vehicles. Sensors and actuators connected to ECUs have been omitted for readability. Modern in-vehicle networks consist of several different bus protocols such as CAN, MOST or FlexRay. See [BMW09] for details.

to transmit its data and other ECUs have to wait based on predefined priorities. Hence, high priority functionality is processed and transmitted with minimal delays, while functionality with a low priority might have to deal with significant delays if several ECUs with a high priority intend to transmit their data at the same time. Event-triggered systems are well-suited to react to asynchronous (i.e., unpredictable) events. The latency between the occurrence of an event and the reaction is ideally lower than for a time-triggered system. However, depending on the network traffic, the latency can vary strongly, leading to a non-deterministic system behavior [Kop91]. The flexibility of event-triggered systems makes them well-suited for the comfort domain where, depending on the customer's preferences, various different systems with low timing requirements need to be integrated.

#### **1.1.2** Time-Triggered Systems

A time-triggered system is governed by a global time and a schedule which exactly defines at which time instant each function sends its messages or starts software tasks. The deterministic behavior of time-triggered systems is of particular importance for the introduction of electronic *drive-by-wire* systems for steering and braking, replacing hydraulic components. Drive-by-wire systems have strict requirements on the safety, fault-tolerance and availability of the communication system. Time-triggered systems provide these properties. A time-triggered system partitions the time in time-slices during which a function can exclusively utilize a communication bus or an ECU. This provides an isolation between different functionality and guarantees a fixed latency. As messages are transmitted at predefined time instants, the system behavior is predictable and missing messages can be quickly detected. However, time-triggered systems also lead to an increased resource utilization and bandwidth demand, as resources that are

preallocated might not be required at all times. Consequently, communication buses for a time-triggered system should generally support a high bandwidth to ensure that all hard real-time requirements are met [Kop91, Rob14].

#### 1.1.3 Comparison of Event- and Time-Triggered Systems

Extending the discussion of event-triggered and time-triggered systems, in the following a short discussion of the advantages and disadvantages of each is given.

The main difference between event-triggered and time-triggered systems lies in the system scheduler. Event-triggered systems decide at runtime which task or message is released at the current time instant, while time-triggered systems follow a predefined schedule. To determine the system schedule, for time-triggered systems a periodic release is assumed. For the resource requirements pessimistic assumptions, i.e., the Worst Case Execution Time (WCET) for tasks, are made to always ensure the correct functionality of the system. This leads to an overestimation of resource requirements compared to an event-triggered system which only transmits messages when necessary. However, for safety-critical systems timing analysis methods are also applied for event-triggered systems to guarantee the correct system behavior also for worstcase scenarios. These timing analysis methods are also based on worst-case assumptions and a periodic execution. Thus, while event-triggered systems use resources more efficiently than time-triggered systems, to satisfy hard real-time requirements the estimated resource requirements are generally also pessimistic. Consequently, for safety-critical systems, event-triggered systems do not necessarily lead to a higher system utilization [Kop91]. However, as eventtriggered systems react to events, for functionality with a high priority in most cases they are able to react faster than a time-triggered system.

As time-triggered systems follow a predefined schedule, the system behavior is predictable and deterministic. Consequently, testing efforts are reduced as the system behavior is easier to reproduce, allowing a systematic testing approach. By contrast, for event-triggered systems a multitude of execution scenarios need to be tested, increasing the testing efforts [Kop91]. The predefined schedule also leads to minimal jitter and allows to design control functions based on a fixed and constant end-to-end delay. Event-triggered systems in contrast require the design of robust control functions which handle a varying end-to-end delay well. In addition, the time-triggered execution scheme of time-triggered systems provides a temporal isolation of functionality. This allows to extend existing schedules if additional messages do not affect previously scheduled ones. While event-triggered systems allow to easily add new functionality, to give timing guarantees as required for critical functions, a timing analysis of the whole system is generally necessary.

In summary, the suitability of event-triggered or time-triggered systems strongly depends on the function requirements. For instance, for non-critical functionality in the comfort domain which is generally highly asynchronous, event-triggered systems are clearly better suited to efficiently use the available resources and react to the user input. For critical applications on the other hand, the deterministic behavior of time-triggered systems helps to reduce the design and integration efforts.

#### 1.2 Communication Buses

Since the introduction of the Controller Area Network (CAN) bus in a series vehicle in 1991, various automotive communication buses have been introduced in series vehicles. While time-critical functionality in the power train and chassis domains require high bandwidths, e.g., for the ESC to react within a few milliseconds (ms) to a locked wheel, a reaction time of 100 ms is sufficient for the comfort domain, as delays of less than 100 ms cannot be perceived by a passenger. This allows the use of more economic low-speed buses. The infotainment domain on the other hand, requires a high bandwidth of up to 4 Mbit/s for audio data and 50 Mbit/s for video data [Bor14]. As a consequence, the communication protocols used in current vehicles have very different properties. In the following, an overview is given over these bus protocols.

#### 1.2.1 Controller Area Network

The CAN bus is the predominant bus protocol in current vehicles. The CAN protocol is event-triggered and supports messages up to a size of 8 byte, supporting bandwidths of up to 1 MBit/s. A Carrier Sense Multiple Access/Collision Avoidance (CSMA/CA) bus access protocol prevents collisions if multiple ECUs try to send their messages at the same time. Predefined priorities define which message is transmitted first in case of a conflict. To ensure a sufficiently short response time of all ECUs, the supported cable length is limited by the bandwidth, i.e., a longer cable supports a lower bandwidth [ZS14]. The CAN bus is used in multiple domains of the vehicle with strongly differing requirements on the network. For instance, in the drivetrain domain a significantly faster data exchange is required compared to the comfort domain where the different ECUs are distributed in the whole vehicle and the cable length of the bus needs to be long [Rob14]. As a consequence, two different CAN versions are currently in use, the High-speed-CAN (CAN-C) [CAN13], supporting data rates of 125 kBit/s to 1 MBit/s, and the Low-speed-CAN (CAN-B) [CAN06], supporting data rates of 5 kBit/s to 125 kBit/s. Typical applications for CAN-C are the engine control, the transmission control and ESC. Typical applications for CAN-B are the climate control and seat adjustment [Rob14]. The two CAN versions are not compatible.

Due to its limited bandwidth, the CAN bus has become a bottleneck for future functionality such as advanced driver assistance systems. As alternative bus protocols like FlexRay require a partial redesign of existing systems, for legacy reasons, many car manufacturers still rely on the CAN bus [ZS14]. Robert Bosch GmbH has therefore recently proposed CAN with Flexible Data-Rate (CAN FD) which increases the data rate up to 8x, compared to conventional CAN while being backwards compatible [Har12]. CAN FD supports message sizes of up to 64 byte. The bandwidth increase is achieved through increasing the bit rate after the arbitration phase

to transmit the message payload. Hence, legacy ECUs not supporting CAN FD transmit their messages with the bit rate of conventional CAN while CAN FD messages are transmitted at an increased bit rate on the same bus [Bor14, ZS14].

Due to the event-triggered transmission schemes of CAN, the latency of low priority messages can differ strongly. While approaches to determine the maximal latency exist [TBW95, DBBL07], in complex E/E-architectures all constraints are often not known in full detail or might quickly change during the design process [ZS14]. While this makes CAN still suitable for many real-time applications, this non-deterministic behavior makes CAN unsuitable for highly safety-critical applications, like brake-by-wire. As a consequence, Time-Triggered-CAN (TTCAN) was developed, extending the CAN protocol with time-triggered communication [TTC04]. Based on the Time Division Multiple Access (TDMA) scheme, the time is partitioned in time slots. While some time slots are exclusively assigned to an ECU to transmit messages using time-triggered communication, other slots are used for CSMA/CA-based event-triggered communication. A dedicated timing master sends cyclic reference messages to synchronize all ECUs. While TTCAN provides a deterministic communication for critical functionality, it is not compatible with conventional CAN and the low data rate of CAN remains. TTCAN has therefore not found wide acceptance in the automotive industry [Rei14, ZS14].

#### 1.2.2 Local Interconnect Network

The Local Interconnect Network (LIN) bus is a time-triggered low speed bus for simple sensor-actuator-functionality, like door- or seat-electronics [ZS14]. The LIN bus was developed as a low-cost alternative to Low-speed-CAN systems. The goal was to create a simple communication protocol that would not require an additional communication controller for low-end micro-controllers [Rob14]. The communication is triggered by a master ECU, sending cyclic requests to the slave ECUs which respond with the message transmission. The master also triggers the communication between slave ECUs, making the LIN bus a deterministic protocol [Bor14, ZS14]. LIN supports data-rates of 1 kbit/s to 20 kbit/s. It commonly realizes subsystems, e.g., for climate control, the air-conditioning controller uses the LIN bus to connect to temperature sensors and fans [Rob14].

The latest LIN version 2.2A [LINar] includes various new features such as support for sporadic frames and event-triggered communication, as well as plug-and-play functionality to ease the integration of functionality in different variants [Bor14, ZS14]. While these new features increase the flexibility of the LIN bus, the cost for a LIN controller has also increased and the intended goal to achieve a cost reduction of 50 % compared to a low speed CAN ECU is hard to meet [ZS14].

#### 1.2.3 Media Oriented Systems Transport

The Media Oriented Systems Transport (MOST) bus was specifically designed for multi media applications, providing a high data-rate. For a constant audio and video data transmis-

sion, MOST supports a time-triggered communication [Bor14]. The protocol also supports event-triggered communication for data without a fixed transmission rate, e.g., data of the navigation system [ZS14]. A dedicated master ECU creates the message frames in which the slave ECUs can send their messages. MOST is available in the three variants: *MOST25*, *MOST50* and *MOST150*, supporting data rates of 25 Mbit/s, 50 Mbit/s and 150 Mbit/s, respectively [Grz11]. MOST150 also supports the transmission of Ethernet frames to ease the integration of user devices like mobile phones that already support Ethernet protocols. MOST is currently mainly used in top-of-the-range and mid-range vehicles [ZS14].

#### 1.2.4 FlexRay

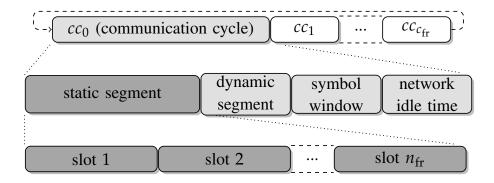

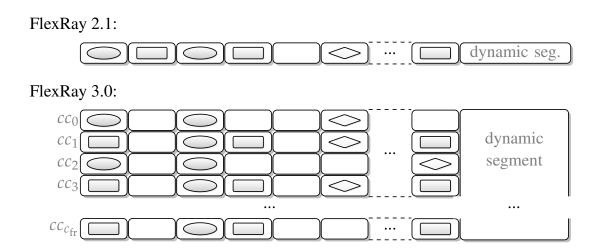

FlexRay [Fle13] is a hybrid communication protocol which supports both time- and event-triggered communication. It was developed with highly safety-critical drive-by-wire functionality in mind [ZS14]. FlexRay therefore combines a deterministic communication using a time-triggered protocol with fault-detection and reliability functionality. To provide a redundant message transmission, FlexRay supports two physical channels. In addition, optional bus guardians provide a monitoring unit in the ECU to deactivate faulty parts of the network if required [Rei14]. FlexRay provides data rates of 10 Mbit/s for each channel, clearly increasing the bandwidth compared to CAN networks. Like TTCAN, FlexRay uses TDMA for time-triggered communication. For event-triggered communication, a Flexible Time Division Multiple Access (FTDMA) scheme is used. Compared to CAN, the supported network topologies as well as the number of ECUs and cable length is increased through the support of active elements, i.e., a transceiver or repeater [ZS14]. With these properties, FlexRay is suitable for both the drivetrain as well as the chassis domain [Rob14]. For state-of-the-art vehicles, FlexRay is largely used in the chassis domain, for instance see [BMW09].

Despite these advantages, FlexRay is only gradually introduced in series vehicles. The main reasons are the late availability of FlexRay hardware and the slow introduction of drive-by-wire functionality, for which FlexRay is seen as a key enabler. Furthermore, a FlexRay bus configuration requires a set of partially dependent parameters, preventing an easy adoption [ZS14]. A more formal introduction to the FlexRay protocol is given in Section 2.3.2.

#### 1.2.5 Automotive Ethernet

While Ethernet has long been the predominant communication protocol for interconnecting computers, the lack of an implementation fulfilling automotive requirements, such as electromagnetic compatibility, made Ethernet an unsuitable candidate for automotive networks in the past. With the introduction of *BroadR-Reach* [Ope15], an unshielded twisted-pair implementation of the physical layer of Ethernet, these obstacles have been overcome [KCBQ14, ZS14]. As a consequence, all major car manufacturers are currently pursuing the integration of Automotive Ethernet in their in-vehicle networks [Ope15]. However, standard Ethernet does not provide any timing guarantees and is therefore unsuitable for real-time functionality. While several real-time

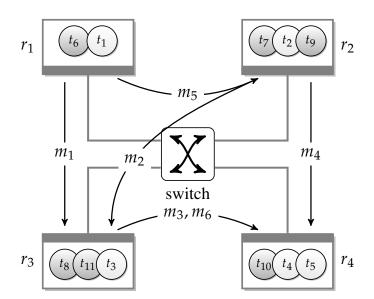

extensions to standard Ethernet exist, such as PROFINET [PRO] or TTEthernet [TTA08], no mutual standard was defined so far [ZS14]. Therefore, the Time Sensitive Networking (TSN) standards [IEE15], currently under development, define a real-time Ethernet which can also be deployed in the automotive domain. TSN will support time-triggered and event-triggered communication, providing end-to-end performance guarantees, while still supporting standard Ethernet best-effort message transmission [Ste14, IEE15]. Automotive Ethernet currently supports a bandwidth of 100 Mbit/s while a 1 Gbit/s version is under development. The communication is full-duplex, i.e., an ECU can send and receive messages at the same time. Instead of connecting ECUs directly to the Ethernet bus, a central switch is required, allowing the simultaneous communication of independent ECUs. Looking at the full network, Ethernet therefore supports much higher throughputs than the specified base rate [KCBQ14, ZS14].

Ethernet as a communication bus requires a very different design approach compared to existing automotive bus systems. For instance, Ethernet only supports point-to-point connections. Thus, messages between two ECUs are not visible to other network participants. In addition, to support full-duplex, BroadR-Reach employs sophisticated digital signal processing techniques, such as echo cancellation. This makes measuring and analyzing of bus data, as it is done with existing automotive bus systems, not feasible. Concepts for established analysis and diagnosis tools for automotive buses can therefore not be directly applied. Furthermore, the need for switches also increases the cost of an Ethernet network, as switch hardware and additional cabling are required [KCBQ14]. While the introduction of Ethernet might require a radical change in the design of automotive architectures, Ethernet also brings various advantages. As Automotive Ethernet makes a large number of established protocols such as the Internet Protocol (IP) available in the vehicle, the integration of internet and user device related functionality is strongly facilitated. At the same time, the switched network structure makes Ethernet wellsuited as a backbone bus, changing the structure of automotive architectures. Finally, the high bandwidths supported by Ethernet allow the introduction of new driver assistance functions, such as the 360-degree camera parking assist system [ABI14] based on Automotive Ethernet which was introduced by BMW in 2013 [KCBQ14, ZS14]. Analysts are projecting that 40 % of all new vehicles will ship with Ethernet by 2020 [ABI14]. A more formal introduction to Automotive Ethernet is given in Section 2.3.3.

#### 1.2.6 Comparison of Automotive Buses

Extending the introduction of automotive buses in the previous subsections, in the following, a short discussion is given, comparing the different buses. Table 1.1 gives an overview of the different properties of each protocol.

The bus systems deployed in vehicles today have been designed for specific purposes and none of the current bus systems is suitable to replace all other bus types. For instance, the LIN bus is well-suited for subsystems with simple ECUs and replacing LIN with a bus like Ethernet or FlexRay would not be reasonable for practical and economical reasons. Similarly, the CAN

**Table 1.1:** Overview of automotive communication buses. See [KCBQ14, Rob14, ZS14] for details.

| actaris.        | CAN-C<br>High-speed-CAN                                  | CAN-B<br>Low-speed-CAN | LIN                      |

|-----------------|----------------------------------------------------------|------------------------|--------------------------|

| protocol type   | event-triggered <sup>a</sup>                             | event-triggered        | time-triggered           |

| bit rate        | $\leq 1 \mathrm{Mbit/s}$<br>$(\leq 4 \mathrm{Mbit/s}^b)$ | $\leq$ 125 kbit/s      | $\leq 20  \text{kbit/s}$ |

| message size    | $\leq 8  \text{byte}$ $(\leq 64  \text{byte}^b)$         | ≤8 byte                | ≤8 byte                  |

| number of nodes | 10                                                       | 24                     | 16                       |

| network length  | 40 m                                                     | 320 m                  | 40 m                     |

| topologies      | bus                                                      | bus                    | bus                      |

| safety-critical | yes                                                      | no                     | no                       |

| domain          | drivetrain                                               | comfort                | comfort                  |

| cost            | low                                                      | low                    | very low                 |

<sup>&</sup>lt;sup>a</sup> for TTCAN also time-triggered

<sup>&</sup>lt;sup>b</sup> for upcoming CAN FD

|                 | MOST                                                        | FlexRay                     | Automotive<br>Ethernet    |

|-----------------|-------------------------------------------------------------|-----------------------------|---------------------------|

| protocol type   | time- and event-triggered                                   | time- and event-triggered   | time- and event-triggered |

| bit rate        | $\leq 150\mathrm{Mbit/s}$                                   | $\leq 10 \mathrm{Mbit/s^c}$ | $100\mathrm{Mbit/s}^d$    |

| message size    | $\leq$ 372 byte/ $\leq$ 1524 byte <sup><math>e</math></sup> | ≤ 256 byte                  | 42-1500 byte              |

| number of ECUs  | 64                                                          | $22^f$                      | -8                        |

| network length  | 20 m between nodes                                          | $24\mathrm{m}^f$            | 15 m per link             |

| topologies      | ring, star                                                  | bus, star, hybrid           | star, tree                |

| safety-critical | no                                                          | yes                         | yes                       |

| domain          | infotainment                                                | chassis                     | various                   |

| cost            | high                                                        | low                         | high                      |

$<sup>^{</sup>c}$  for single bus,  $\leq$  20 Mbit/s for dual channel, no redundancy

$<sup>^{\</sup>it d}$  per link, full-duplex, 1 Gbit/s in development

$<sup>^</sup>e$  time-triggered/event-triggered

$<sup>^</sup>f$  for passive bus, with active elements up to 2048 ECUs and longer cable

<sup>&</sup>lt;sup>g</sup> only limited by the number of ports on the switch

bus employed in the comfort domain provides a flexibility and clear cost advantage that is not matched by the other bus systems, making a replacement in the near future not reasonable. On the other hand, in the infotainment domain it is very likely that Ethernet will replace the MOST bus in the near future, as it supports all MOST functionality at similar cost while being also suitable for other domains. Finally, in the safety-critical drivetrain and chassis domains, developers have the choice between CAN FD, FlexRay, and Ethernet. While CAN will still persist as an important part of the automotive in-vehicle networks due to legacy reasons, the introduction of new functionality will require the use of other protocols. For drive-by-wire applications, FlexRay is well-suited and the time-triggered communication supported by TSN might also make Ethernet a suitable candidate for this class of applications. The introduction of advanced driver assistance functions also leads to a strong demand for an increased bandwidth, e.g., to transmit high resolution video data. Currently only Automotive Ethernet is able to provide the required bandwidths if the application is safety-critical. Consequently, we believe that in the near future an increasing number of in-vehicle networks will be using FlexRay and Ethernet. In general, a clear trend towards time-triggered communication for safety-critical systems is visible, while a mix of time- and event-triggered communication will prevail in future automotive E/E-architectures.

#### 1.3 Electronic Control Units

The previous section has discussed the different communication buses in state-of-the-art vehicles, connecting the different ECUs. In the following, the hardware and software of ECUs are introduced in more detail. The ECUs deployed in state-of-the-art automobiles are based on a micro-controller and interface circuits to connect to peripheral sensors and actuators. Depending on the sensors, a preprocessing, e.g., to reduce noise, or a transformation might be required, while an actuator might require power electronics to be controlled [Bor14, Rob14]. Depending on the functionality, the hardware properties of the micro-controllers in use in state-of-the-art vehicles strongly differ. For example, a low-end ECU might only have a 8 bit processor with 8 MHz, 4 kB flash memory, and 256 byte RAM while a top-end automotive ECU might have a 32 bit multi-core processor with 200 MHz, 6 MB flash memory, and 384 kB RAM<sup>3</sup>. An important part of an ECU is the monitoring unit which observes the system behavior and reacts to a fault. In the simplest cases, the monitoring unit might be a watchdog, initializing a reboot of the ECU if required [Bor14]. A state-of-the-art in-vehicle network consists of up to 100 ECUs depending on the car model [Cha09] with very different requirements and functionality.

Instead of implementing the software functionality directly on the micro-controller, ECUs today employ real-time operating systems to manage system resources and to allow the implementation of multiple independent functions on one ECU. For instance, a combustion engine

<sup>&</sup>lt;sup>3</sup>Data for FREESCALE automotive micro-controllers *S08QD* and *MPC5676R*, taken from http://cache.freescale.com/files/microcontrollers/doc/roadmap/BRAUTOPRDCTMAP.pdf.

controller implements various independent functions, such as the adjustment of the fuel injection while monitoring the rotational speed of the turbo charger [ZS14].

#### **1.3.1 OSEK/VDX**

The Offene Systeme und deren Schnittstellen für die Elektronik im Kraftfahrzeug/Vehicle Distributed Executive (OSEK/VDX) standard [OSE06] defines a Real-Time Operating System (RTOS) which has become the de facto standard for operating systems deployed on automotive ECUs [Bor14]. OSEK/VDX RTOSs are deployed in a wide range of ECUs, ranging from 8 bit to 32 bit processors, however, they are limited to single-core ECUs [Bor14]. OSEK/VDX was designed for distributed architectures, abstracting the communication between both internal and external tasks by messages transmitted using a communication layer. While the standard OSEK/VDX operating system is limited to event-triggered scheduling, a time-triggered version, OSEK time is available. There, a predefined dispatch table defines at which time instants a task is executed [Rei14]. An OSEK/VDX operating system is configured statically at design time using a configuration file. Dedicated configuration tools commonly allow to auto-generate the configured system [ZS14]. Various real-time operating systems that follow the OSEK/VDX standard are available, for instance see [ETAb, Vec]. However, most OSEK/VDX implementations are incompatible with each other, making a direct migration of software from one system to another a time-consuming task. This is largely due to the fact that, in particular, early versions of the OSEK/VDX specification did not specify all operating system parts in sufficient detail, leading to differing RTOS properties [Bor14, ZS14].

#### 1.3.2 AUTOSAR

To address the increasing complexity of automotive E/E-architectures and to account for the rising number of software-based functionality in vehicles, the AUTomotive Open System ARchitecture (AUTOSAR) initiative was established in 2003. AUTOSAR defines a set of standards [AUT14] for an automotive software architecture which abstracts the underlying ECU hardware to provide a uniform software platform for in-vehicle networks. The goal is to allow developing application software independent of the ECU it is later deployed on. Consequently, functionality could be easily added or updated [Lee09, Rob14].

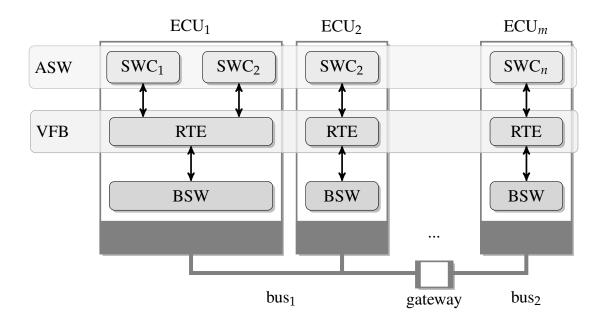

The AUTOSAR architecture consists of three layers: (1) The hardware specific Basic Software (BSW) layer abstracts the ECU hardware, providing hardware drivers and an RTOS. (2) In the Application Software (ASW) layer the actual system functionality is implemented, e.g., the control algorithm for an ESC system. (3) The VFB layer abstracts the internal, as well as the external communication between the Software Components (SWCs) implemented in the ASW layer [Rei11]. Figure 1.4 illustrates the AUTOSAR architecture. The underlying BSW layer is based on the OSEK/VDX standards [ZDGSV11] and implemented on the ECU by the supplier. The VFB layer is created statically during the design phase and abstracts the communication within an ECU as well as between ECUs connected by a bus. The communication paths are

**Figure 1.4:** Schematic illustration of AUTOSAR architecture. Each ECU runs a standardized RTOS providing the Basic Software (BSW) layer. The Virtual Function Bus (VFB) layer then abstracts the network structure with its different buses, taking care of all communication. The VFB is implemented by a Real-Time Environment (RTE) deployed on each ECU. Finally, in the Application Software (ASW) layer the actual functionality is implemented as Software Components (SWCs). The figure is reproduced from [Rei11].

defined in a configuration file from which tools can generate a Real-Time Environment (RTE) deployed on the ECU [ZS14]. For the application development, communication between SWCs is realized using *ports*, both for local as well as external communication. Based on these ports, the Real-Time Environment (RTE) then takes care of the actual data transmission [Rei14, ZS14]. Configuring the VFB is currently still a time consuming task as available configuration tools are unable to auto-generate most of the configuration parameters [ZS14]. AUTOSAR is supported by all major car manufacturers and first ECUs implementing AUTOSAR standards have been introduced into series vehicles since 2009 [Rei14].

#### 1.4 Design of Automotive E/E-architectures

Car manufacturers traditionally rely on suppliers to develop the individual components of a vehicle, such as brakes or seats. The car manufacturer focuses on competitive features such as the vehicle design and the development of the vehicle engine. For the E/E-architecture, most functionality is developed by suppliers and the car manufacturer is mainly concerned with the integration into the system [Lee09, SZ13].

While suppliers today commonly provide ECUs with pre-installed functionality, through AUTOSAR the suppliers might soon provide the functionality as software [ZS14]. The integration of different components in the E/E-architecture is a highly complex task, as a multitude of parameters need to be configured for each ECU and the correct timing behavior of the system needs to be guaranteed. Complex ECUs might have up to 10000 parameters of which several might have to be evaluated experimentally. While tools provide support in the parameter definition, several parameter decisions have to be made by the system designer, e.g., to optimally configure an engine controller [Bor14]. At an early design stage, timing analysis tools such as Symbolic Timing Analysis for Systems (SymTA/S) [Sym15] or methods using Real-Time Calculus (RTC) [TCN00] are commonly employed to determine maximum end-to-end delays. The timing analysis allows to evaluate the specified architecture and to determine conflicts [ST12, ZS14]. During the whole design process, each component, as well as the overall system are then tested to detect problems as early as possible, e.g., by simulating other ECUs in the system, using a residual bus simulation. Tools such as CANoe [Vec15] aid during this process [ZS14]. In recent years, model-based development tools such as Simulink [Mat15] or ASCET [ETAa] are used by most car manufacturers to evaluate their systems at an early design stage. Several of these tools also provide automated C-code generation. As the code generated by these tools currently suffers from being hard to read and being inefficient, it is rarely used in series vehicles [Bor14]. Despite the availability of various tools supporting the development process of the E/E-architecture, the integration of all components and testing of the system is still a time consuming and complex task. Systematic approaches are therefore required to aid this process [SN13, WLMC13].

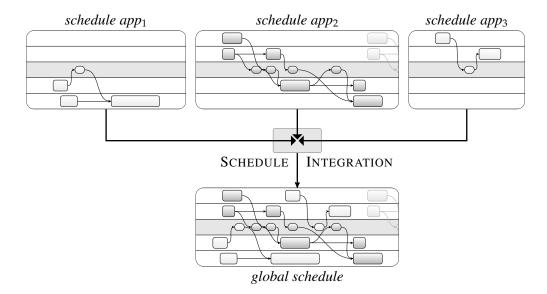

### 1.5 Challenges

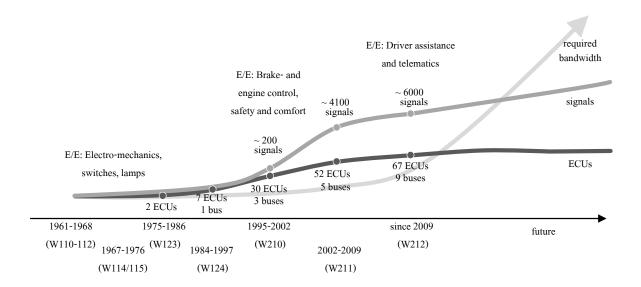

The number of electronics and software-based functionality in the automotive domain has been rapidly growing in the last years. Figure 1.5 illustrates how the number of ECUs and the number of transmitted signals has significantly increased for the Mercedes-Benz E-Class in the last decades. This trend will continue in the future, and in particular the introduction of advanced driver assistance functions based on video data will lead to a significant increase in bandwidth requirements [ZS14]. This growing number of functionality, but also the increasing interaction between highly distributed software components makes the integration of all components into a seamless working system a challenging task. In this context, in particular three challenges should be mentioned here: (1) Ensuring correct timing behavior of all components individually and in the interaction with other components. (2) The integration of independently developed components in a global system. (3) Efficient management of different variants of an E/E-architecture, e.g., a variant for a petrol and a diesel engine.

The recently introduced ISO 26262 standard [ISO12] for functional safety in the automotive domain requires *freedom of interference*. Hence, during the system design it has to be ensured that the correct execution of a critical software component can never be compromised by another

**Figure 1.5:** Evolution of the E/E-architecture of the Mercedes-Benz E-Class over the last decades. Figure reproduced from [ST12].

software component. Consequently, defining and guaranteeing a certain timing behavior becomes essential [SZ13]. AUTOSAR provides mechanisms such as *End-to-End-Communication Protection* to detect timing violations and to contain faults. However, these mechanisms require that the timing behavior of critical software components is clearly defined, making the timing analysis an important part of the software development process [SZ13, ZS14]. Consequently, the design process in the automotive industry is currently radically changing with time and timing behavior becoming an important design parameter. Single software components can no longer be regarded as independent modules that are later integrated in the system. Instead, starting from the specification of the system, the correct functionality in the interaction with other components needs to be evaluated during the whole design process to ensure a sufficient isolation between components.

In the last years, automotive E/E-architectures have seen a strong increase in the number of ECUs. However, this trend will not continue and it is expected that the number of ECUs will decrease from currently around 20-80 ECUs to only 10-20 powerful ECUs. At the same time, the overall number of software functions will continue to grow [Rob14]. As most functionality will then be provided as software components sharing few ECUs, the complexity of the integration process will continue to rapidly increase. The current approach is to apply timing analysis methods for event-triggered systems and define schedules for time-triggered systems already at the specification phase [BÖ7, ZS14]. While this is well-suited for legacy functionality, estimating the exact timing requirements or the communication demand of a software component before the implementation is challenging and might lead to an over- or underestimation of timing requirements. Consequently, during the design process the initial configurations and schedules have to be revised. Tools and methods that allow to efficiently integrate software components

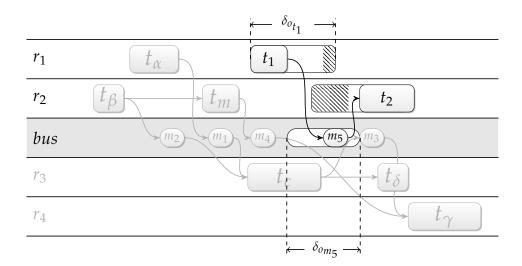

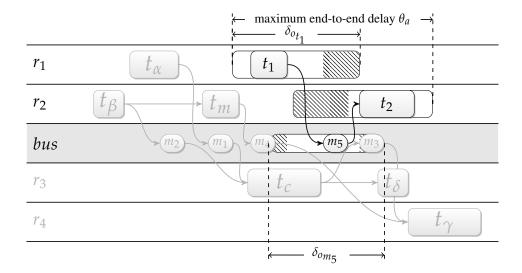

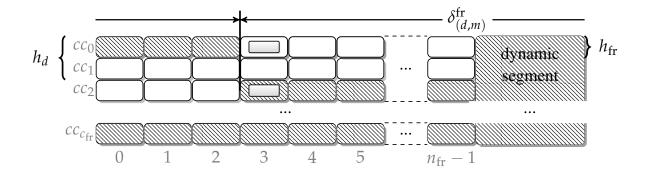

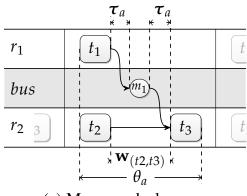

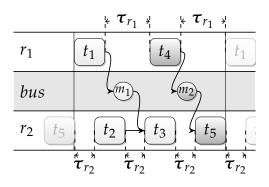

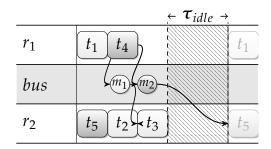

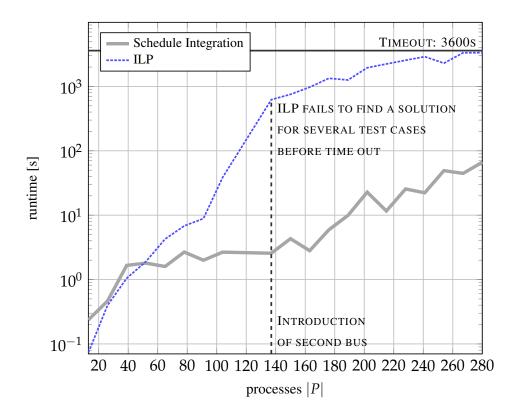

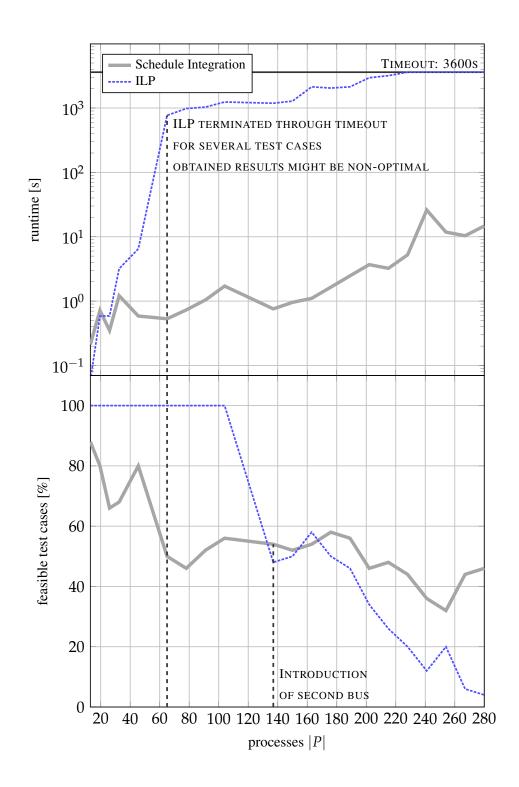

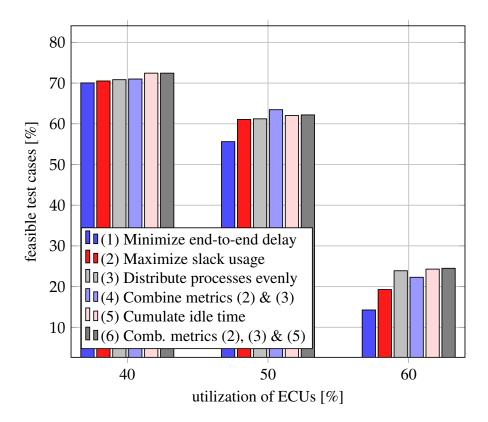

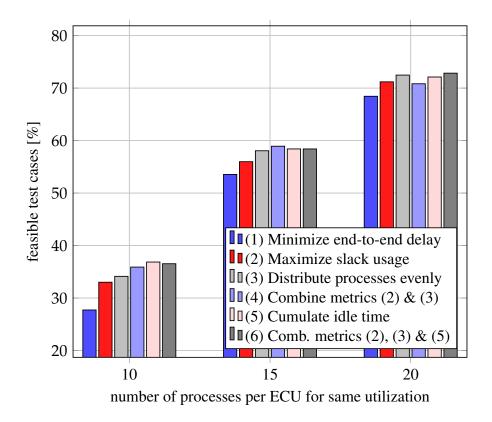

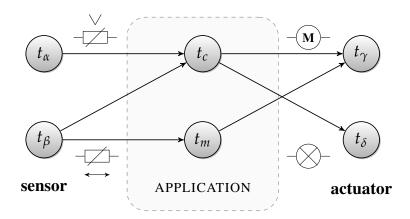

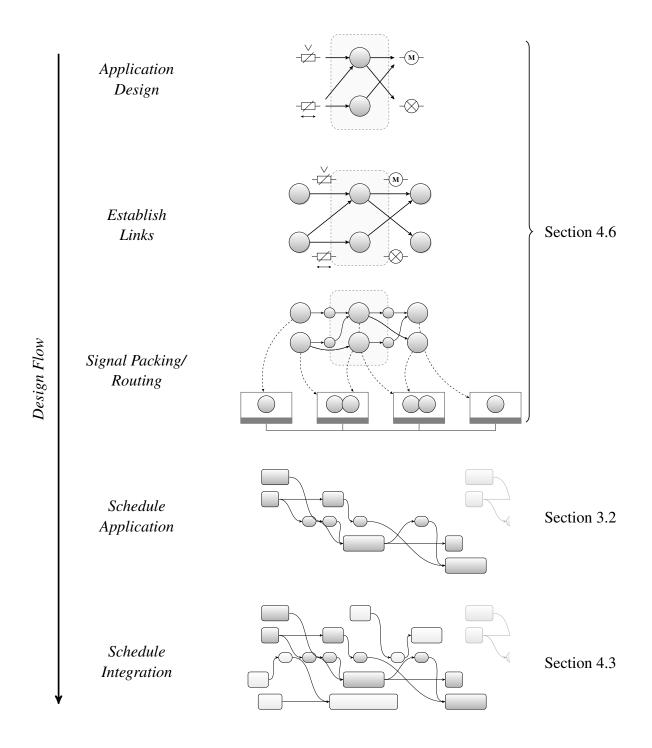

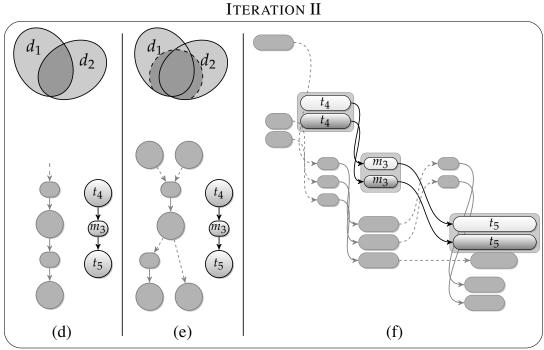

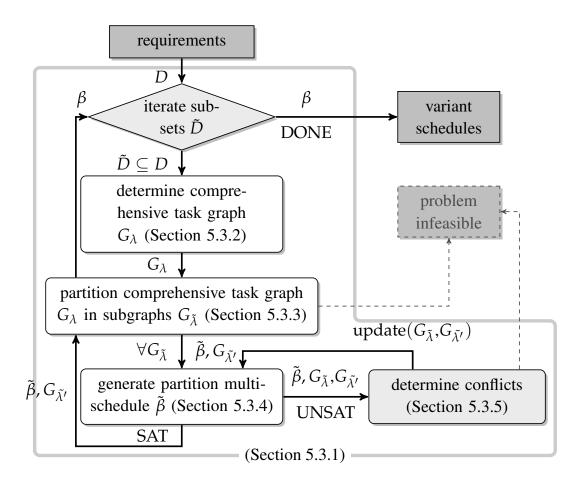

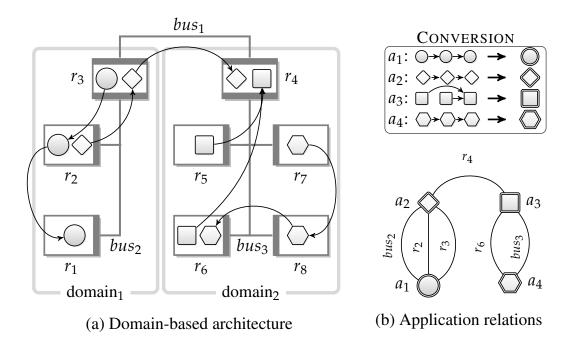

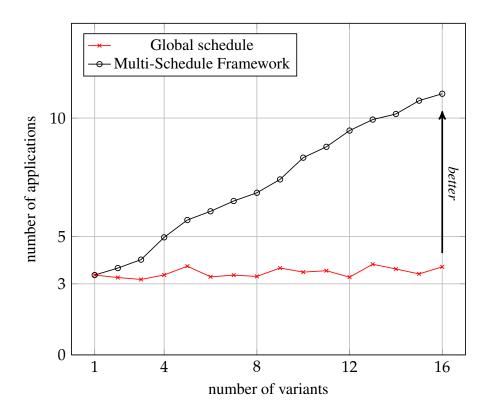

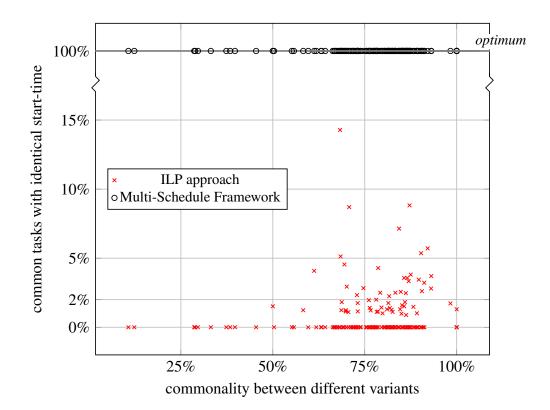

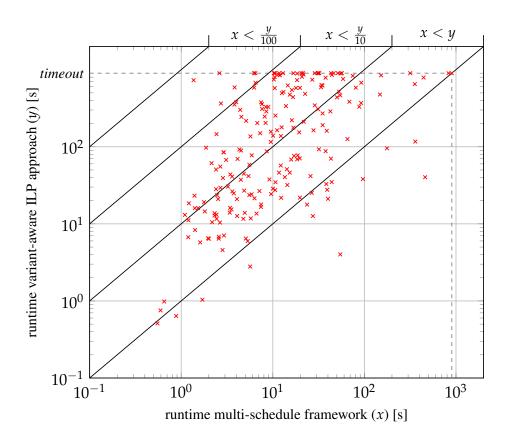

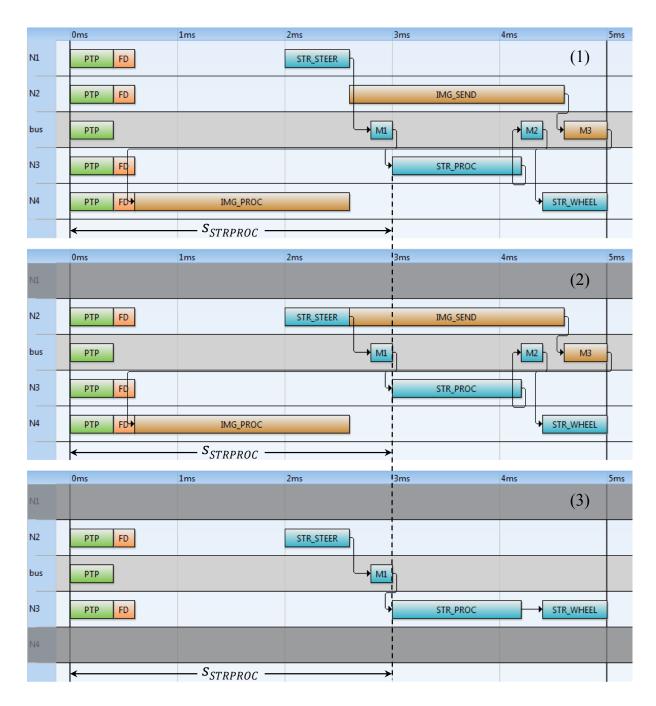

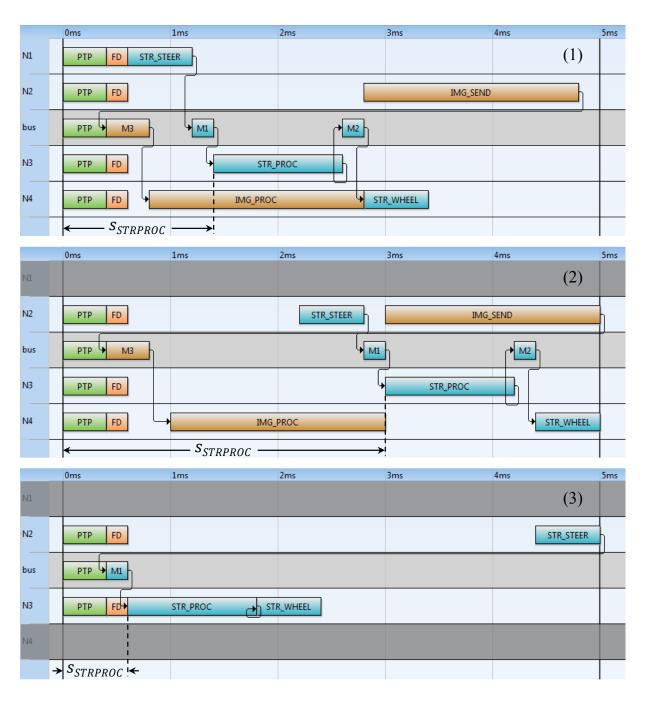

into the global system schedule are essential for the design of future E/E-architectures. While AUTOSAR simplifies the integration process of the software components into a common ECU, configuring the system and defining schedules is still a complex task and systematic methods for the integration are required.