## Automated Power Optimization of Sequential Integrated Circuits through Approximate Computing

David M. May

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

#### Vorsitzender:

Prof. Dr.-Ing. Ulf Schlichtmann

### Prüfer der Dissertation:

- 1. apl. Prof. Dr.-Ing. Walter Stechele

- 2. Prof. Lirida de Barros Naviner, Ph.D.

Die Dissertation wurde am 16.02.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 19.06.2017 angenommen.

# **Abstract**

Approximate Computing is a paradigm that has recently drawn interest due to its promise to substantially increase the power efficiency of integrated circuits by lowering the requirements on the precision of the calculations of a circuit. For a circuit in Approximate Computing, results that stay within a confidence interval can be sufficient as long as the power consumption can be reduced by tolerating this in-determinism. Not all applications are suitable for this approach. Especially applications from the signal and image processing domain are applicable, due to their intrinsic tolerance to imprecision. Approximate Computing proposes to reduce the power consumption for instance by removing, or switching off parts of a circuit that are only required for unnecessary high precision. The difficulty of applying the approach is to reliably and efficiently determine which parts of the circuit can be approximated, given the quality requirements of the application. Another approach in order to save power, is to over-scale the supply voltage and tolerate the appearance of timing faults. In this case it is not only necessary to determine which parts qualify for an approximation but also the degree of approximation that can be tolerated has to be determined.

In the prior art, approximations are mainly performed by a manual inspection and modification of the circuits. Only a few automated approaches exist, which limits the practical applicability of Approximate Computing. Lengthy simulations at gate-level are usually used to analyze the behavior of approximated circuits. Due to this limitation, often the proposed approximations are limited to combinational logic, i.e. sub-blocks of circuits, like arithmetic units.

In this work an approach is presented trying to overcome these limitations. Many steps of the approach are automated in order to simplify the process of the approximation. Approximations in this work are not limited to combinational sub-blocks, but can instead be applied to complex sequential logic. In order to overcome the lengthy gate-level simulations an intermediate approximation step, at register-transfer level, is used to analyze the behavior of the approximated circuits. In order to model a variety of approximation techniques, probabilistic fault injections are introduced. FPGA-based, accelerated, emulation is employed to perform the fault injections and to improve the runtime of the approximation. In order to apply voltage over-scaling without the need of lengthy simulations at transistor level, an analytical analysis approach is presented. This approach builds up on top of the results gained at the register-transfer level analysis and allows to efficiently and reliably apply voltage over-scaling to sequential circuits. With the help of a variety of case studies, the individual steps of the presented approach are demonstrated and validated.

# Zusammenfassung

Approximate Computing ist ein Paradigma, dass in letzter Zeit vermehrt Interesse in der Forschung geweckt hat, bedingt durch das Versprechen den Stromverbrauch von integrierten Schaltungen substantiell zu reduzieren. Für eine Schaltung in Approximate Computing ist es unter Umständen egal, ob das berechnete Ergebnis nur innerhalb eines Konfidenzintervalls bleibt, solange durch die Inkaufnahme dieser Ungenauigkeit der Stromverbrauch gesenkt werden kann. Nicht jeder Typ Schaltung ist geeignet für eine Approximierung. Besonders Schaltungen aus dem Bereich der Signal- und Bildverarbeitung scheinen geeignet zu sein, da diese eine natürliche Toleranz gegenüber Fehlern auszeichnet. Approximate Computing schlägt vor, den Stromverbrauch zum Beispiel durch das absichtliche Entfernen, bzw. Abschalten von Schaltungsteilen zu erreichen, die nur für unnötig hohe Präzision zuständig sind. Die Schwierigkeit dabei liegt darin, zuverlässig und effizient zu bestimmen, welche Teile approximiert werden, wenn gewisse Qualitätsanforderungen an die Anwendung nicht unterschritten werden dürfen. Ein anderer Ansatz den Stromverbrauch zu reduzieren, ist es, die Versorgungsspannung soweit zu skalieren, so dass unter Umständen Zeitverletzungen in sequenzieller Logik auftreten können. Bei diesem Ansatz ist es nicht nur notwendig zu bestimmen, welche Teile approximiert werden dürfen, sondern auch noch den Grad der Approximierung, der toleriert werden kann.

Im Stand der Technik werden Approximierungen meistens mit Hilfe manueller Analyse und Modifikation realisiert. Es sind nur wenige Ansätze bekannt, bei denen ein automatisierter Ansatz durchgeführt wird, was die praktische Anwendbarkeit vom Approximate Computing deutlich reduziert. Meistens sind zeitaufwendige Simulationen auf Gatterebene nötig um die Schaltung hinsichtlich der möglichen Approximierungen zu untersuchen. Durch diese Einschränkung sind approximierte Schaltungen oftmals auf kombinatorische Blöcke, kleine Teilschaltungen, wie zum Beispiel arithmetische Einheiten, limitiert.

In dieser Arbeit wird versucht, diese Einschränkungen zu überwinden. Viele Schritte des präsentierten Ansatzes sind automatisiert um den Prozess der Automatisierung zu erleichtern. Die Approximierungen sind nicht limitiert auf kombinatorische Unterblöcke, sondern können stattdessen auf gröse sequentielle Schaltungen angewandt werden. Um die zeitaufwendigen Simulationen auf Gatterebene zu umgehen, wird ein Zwischenschritt auf Registertransferebene eingeführt, um das Verhalten der approximierten Schaltung zu analysieren. Um eine Vielzahl von Approximierungstechniken zu modellieren, wird für die Analyse eine probabilistische Fehlerinjektion benutzt. Eine FPGA basierte, beschleunigte, Emulation um die Fehler in die Schaltung zu injizieren sorgt dafür, dass die Analyse schnellstmöglich durchgeführt werden kann. Um eine Approximierung durch Versorgungsspannungsüberskalierung, ohne den Einsatz von komplexen Simulationen auf

Transistorebene, zu bewerkstelligen, wird ein analytischer Ansatz vorgestellt. Dieser Ansatz baut auf den Ergebnissen aus der Registertransferebene auf, und erlaubt auf zuverlässige und effiziente Art und Weise die Approximierung von integrierten Schaltungen durch Versorgungsspannungsüberskalierung. Mit Hilfe einer Vielzahl von Fallstudien, werden die einzelnen Teilschritte des Ansatzes demonstriert und validiert.

# **Preface**

I want to thank Walter, Andreas and Thomas, not only for giving me the opportunity to write this thesis but also for their valuable input and support throughout my time working at the institute. I want to thank Stefan who helped me a lot with the netlist manipulation presented in this work. Without his help, this work would not have been possible. Special thanks go to my wife for always supporting me and for giving me the time to finish the thesis.

The Hague, December 2016 David May

# Contents

| C  | onten | ts       |                                                      | ix   |

|----|-------|----------|------------------------------------------------------|------|

| Li | st of | Figures  | 5                                                    | xi   |

| Li | st of | Tables   |                                                      | xv   |

| Αd | crony | ms       |                                                      | xvii |

| 1  | Mot   | ivation  |                                                      | 1    |

| 2  | Intr  | oductio  | on                                                   | 5    |

|    | 2.1   | Power    | Consumption Dilemma of Integrated Circuits           | . 5  |

|    |       | 2.1.1    | Dynamic Power Consumption                            | . 5  |

|    |       | 2.1.2    | Static Power Consumption                             | . 8  |

|    | 2.2   | Appro    | oximate Computing                                    | . 10 |

|    |       | 2.2.1    | Approximation Types                                  | . 12 |

|    |       | 2.2.2    | Suitable Applications                                | . 20 |

|    |       | 2.2.3    | Levels of Approximation                              | . 24 |

|    |       | 2.2.4    | Metrics of Approximation                             |      |

|    | 2.3   | Prior .  | Art                                                  | . 30 |

|    |       | 2.3.1    | Fault Analysis                                       |      |

|    |       | 2.3.2    | Confidence Intervals for Probabilistic Experiments   | . 35 |

|    |       | 2.3.3    | Circuit Approximation                                | . 36 |

| 3  | Pro   | babilist | ic Fault Emulation                                   | 45   |

|    | 3.1   | Proba    | bility-awareness                                     | . 47 |

|    | 3.2   | FPGA     | A-based probability-aware Fault Emulation - faultify |      |

|    |       | 3.2.1    | Software-side Emulation API                          | . 48 |

|    |       | 3.2.2    | Hardware Implementation                              | . 50 |

|    |       | 3.2.3    | Circuit Instrumentation                              | . 56 |

|    |       | 3.2.4    | Parallel Bit-error Generation                        | . 59 |

|    |       | 3.2.5    | Host vs. FPGA Generated Bit-Errors                   |      |

|    |       | 3.2.6    | Improved Bit-error Generation                        | . 63 |

|    |       | 3.2.7    | Island Concept                                       |      |

|    |       | 3.2.8    | Hardware Overhead                                    |      |

|    |       | 3.2.9    | Performance Analysis                                 | . 72 |

|    | 3.3   | Evalua   | ation                                                | . 78 |

### Contents

| 4  | Aut    | omated Functional Approximation of Sequential Circuits | 85  |

|----|--------|--------------------------------------------------------|-----|

|    | 4.1    | Datapath Separation                                    | 86  |

|    |        | 4.1.1 Netlist-based Separation Approach                | 89  |

|    |        | 4.1.2 Emulative Separation Approach                    | 91  |

|    |        | 4.1.3 High-Variance Register Exclusion                 | 95  |

|    |        | 4.1.4 Evaluation                                       | 95  |

|    | 4.2    | Result Significance                                    | 98  |

|    |        | 4.2.1 Variance-based Approach                          | 98  |

|    |        | 4.2.2 On-the-fly Approach                              | 99  |

|    |        | 4.2.3 Evaluation                                       | 101 |

|    | 4.3    | Application-reasoned Approximation                     | 103 |

|    | 4.4    | Coarse-grained Approximation                           | 107 |

|    | 4.5    | Fine-grained Approximation                             | 112 |

|    | 4.6    | Evaluation                                             | 115 |

|    | 4.7    | Summary                                                | 121 |

| 5  | Арр    | proximation at Gate Level for Voltage Scaling          | 125 |

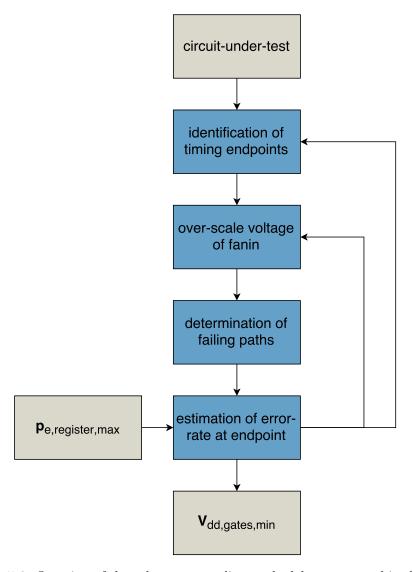

|    | 5.1    | Determination of Failing Timing Paths                  | 127 |

|    | 5.2    | Estimation of Error Probability at Timing Endpoint     | 131 |

|    | 5.3    | Shared Component Handling                              | 137 |

|    | 5.4    | Voltage Islands                                        | 137 |

|    | 5.5    | Applied voltage over-scaling                           | 137 |

|    | 5.6    | Summary                                                | 140 |

| 6  | Con    | clusion and Outlook                                    | 141 |

| Bi | bliog  | raphy                                                  | 149 |

| Sι | ıperv  | ised Student Research                                  | 161 |

| Pι | ıblica | ntions                                                 | 163 |

# List of Figures

| 1.1          | The extended "PPA" tradeoff of today's IC designs between power, per-                                                                             | 1   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | formance, area and reliability                                                                                                                    | 1   |

| 2.1          | Short circuit power of a CMOS inverter                                                                                                            | 6   |

| 2.2          | Capacitance switching power of a CMOS inverter                                                                                                    | 7   |

| 2.3          | The various forms of gate-leakage in CMOS devices                                                                                                 | 10  |

| $2.4 \\ 2.5$ | Approximate Computing: trading-off power consumption with precision . Bit-flip probability as the mean to model a variety of faults and approxi-  | 11  |

|              | mation techniques, respectively [23]                                                                                                              | 13  |

| 2.6          | Charge generation and collection phases in a reverse-biased junction and                                                                          | - 4 |

|              | the resultant current pulse caused by the passage of a high-energy ion. [28]                                                                      | 14  |

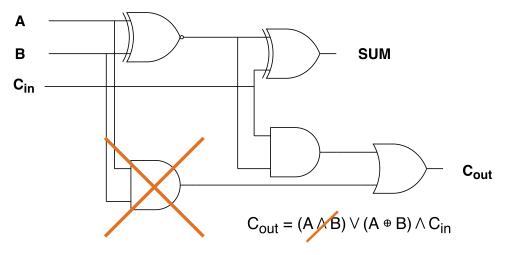

| 2.7          | Simple functional approximation at gate level of a 1-bit full adder                                                                               | 15  |

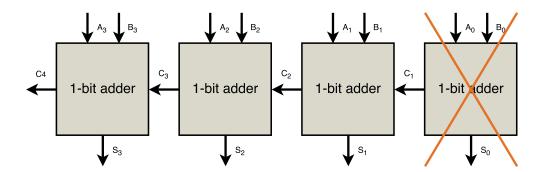

| 2.8          | Bit-width reduction of a 4-bit adder                                                                                                              | 16  |

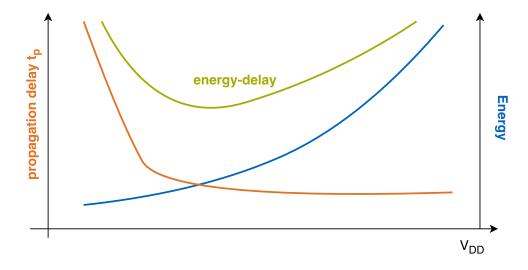

| 2.9          | Visualization of the Energy-Delay product (EDP) of CMOS circuits                                                                                  | 17  |

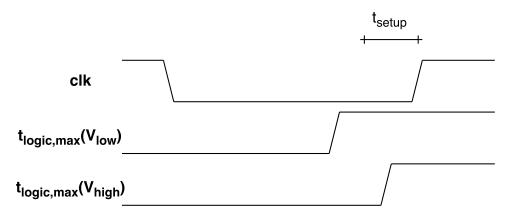

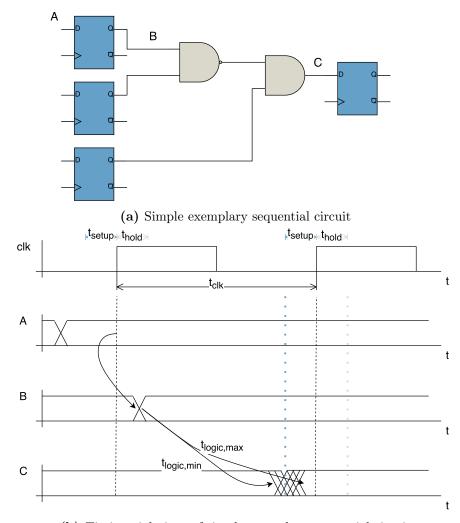

| 2.10         | Timing violation in sequential circuits. The signal transition is not arriving in time at the flip-flop                                           | 17  |

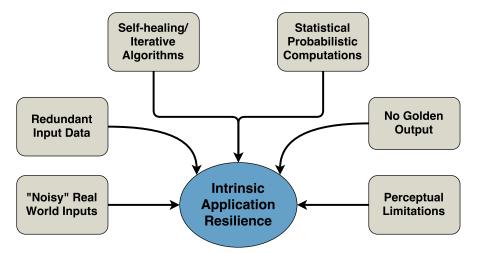

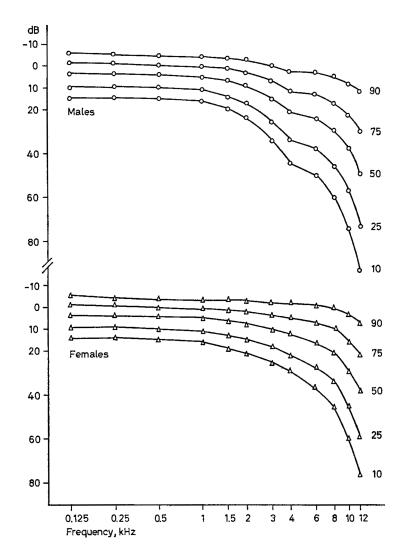

| 2 11         | Intrinsic application resilience [8]                                                                                                              | 20  |

|              | Change in hearing threshold level between age 18 and 55, for males and females, as a function of frequency, showing calculated medians, quartiles | 20  |

|              | and deciles [33]                                                                                                                                  | 22  |

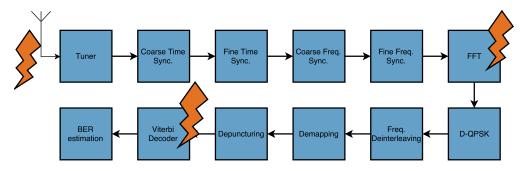

|              | Decoder chain of a "Digital Audio Broadcast" ETSI EN 300 401 receiver $$ .                                                                        | 23  |

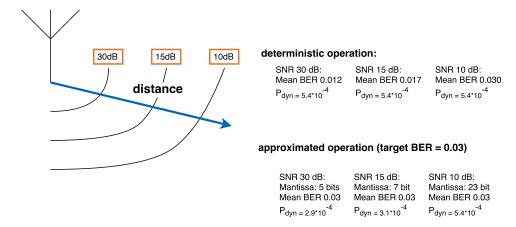

| 2.14         | Adaptive approximation of a DAB receiver based on signal-to-noise ratio of the received signal                                                    | 23  |

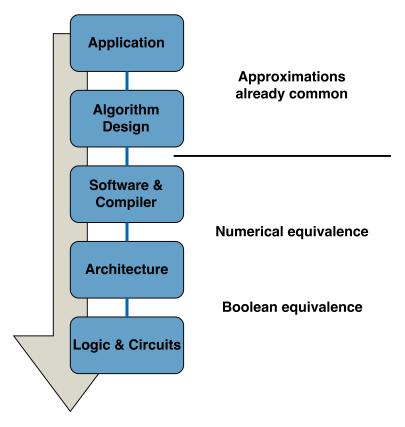

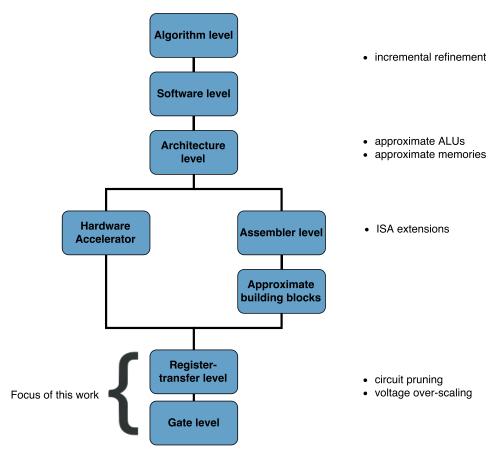

| 2.15         | Abstraction levels already used for approximations in today's applications                                                                        | 26  |

|              | Approximation techniques at various abstraction levels                                                                                            | 29  |

| 2.17         | Matrix operations used to combine individual probabilistic transfer matri-                                                                        |     |

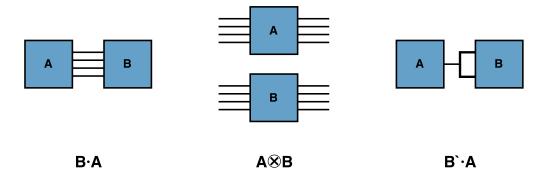

|              | ces (PTM) to describe whole combinational circuits [57]                                                                                           | 31  |

| 2.18         | Circuit Instrumentation                                                                                                                           | 34  |

| 2.19         | Quality degradation of test image due to an approximated DCT-IDCT transformation [29]                                                             | 38  |

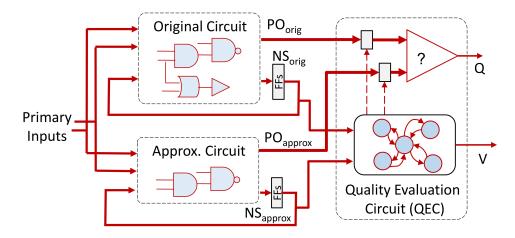

| 2.20         | Sequential quality constraint circuit [97]                                                                                                        | 39  |

|              | Annotated approximated circuit with timing information due to voltage                                                                             | 55  |

|              | over-scaling as proposed in [32]                                                                                                                  | 41  |

| 2.22         | Equivalent untimed circuit as proposed in [32]                                                                                                    | 42  |

|              | A                                                                                                                                                 |     |

## List of Figures

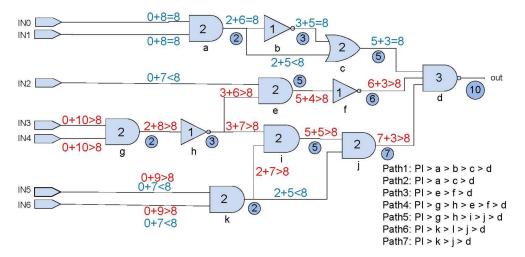

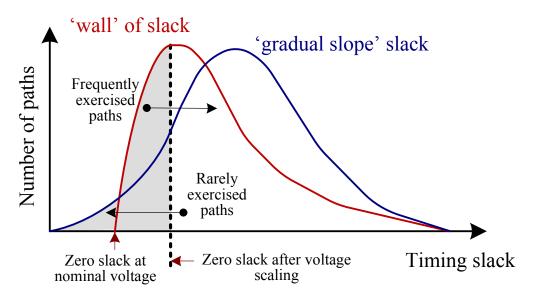

| 2.23          | The slack redistribution technique in order to move the slack distribution from a critical "wall" into one with a more gradual failure characteristic [107] | 43       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|               |                                                                                                                                                             |          |

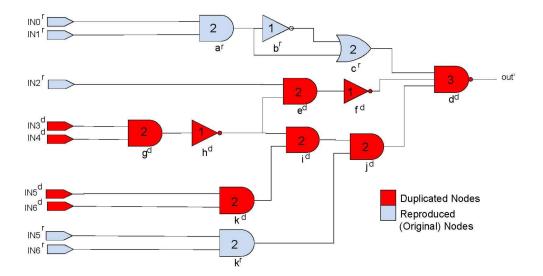

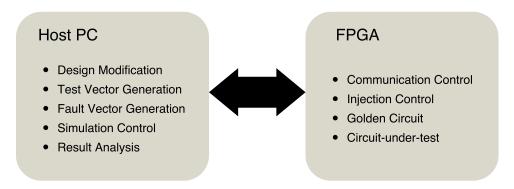

| 3.1           | The two main blocks of FPGA-based fault emulation                                                                                                           | 46       |

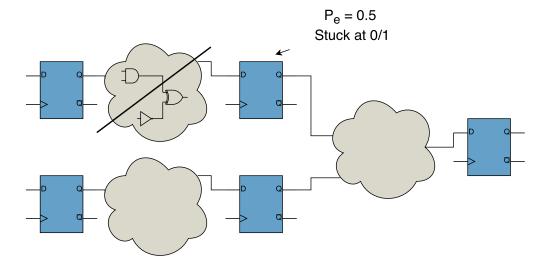

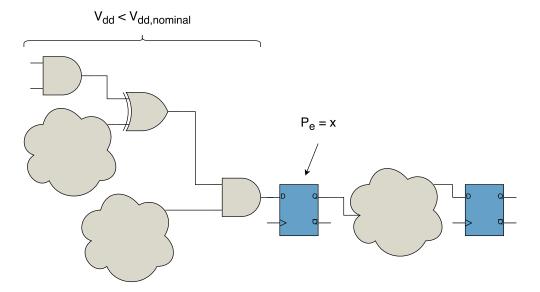

| 3.2           | Functional approximation of circuits with "circuit pruning" modeled as an                                                                                   | 4.0      |

| 0.0           | error rate at the input of the following flip-flop                                                                                                          | 48       |

| 3.3           | Voltage over-scaling as a further approximation technique that can be                                                                                       | 4.0      |

| 2.4           | modeled as error rates at the register inputs                                                                                                               | 49       |

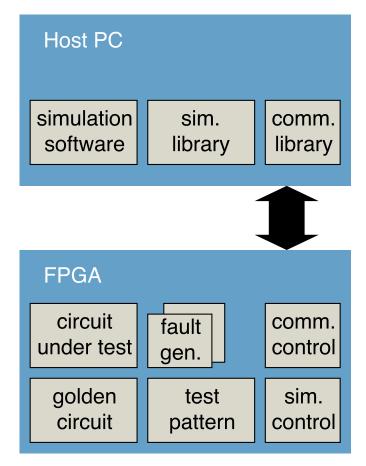

| 3.4           | The Synopsys "CHIP it" simulation system                                                                                                                    | 50       |

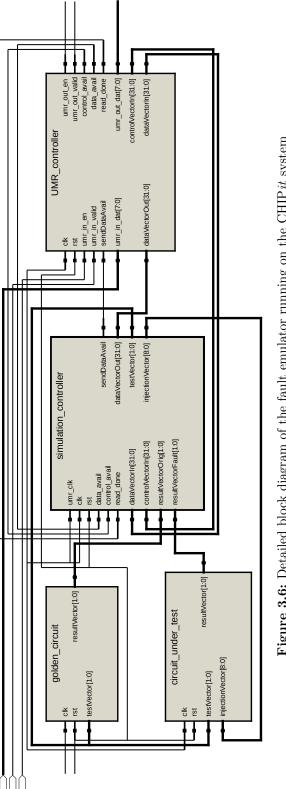

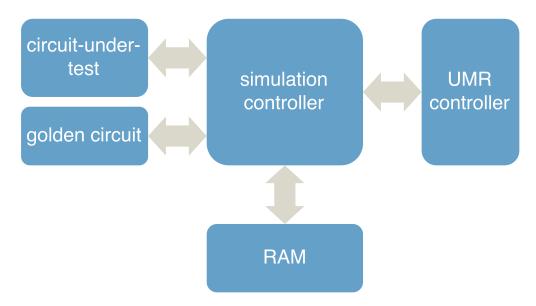

| 3.5           | Simple block diagram of the fault emulator running on the CHIP it system                                                                                    | 52<br>53 |

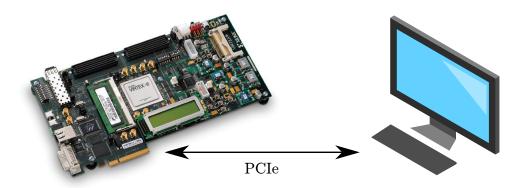

| 3.6<br>3.7    | Detailed block diagram of the fault emulator running on the CHIP it system Xilinx ML605 evaluation board connected via PCIe to a host PC                    | 55       |

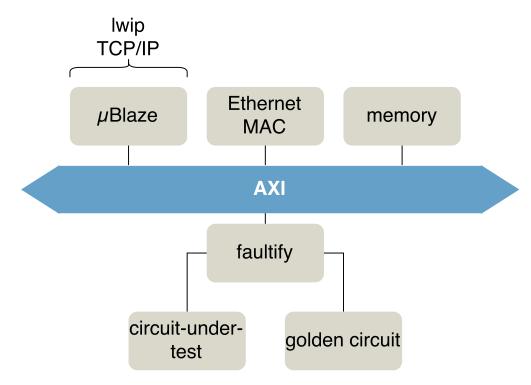

| 3.8           | A block diagram of the AXI-based emulator system with an Ethernet                                                                                           | 55       |

| 3.0           | control interface                                                                                                                                           | 56       |

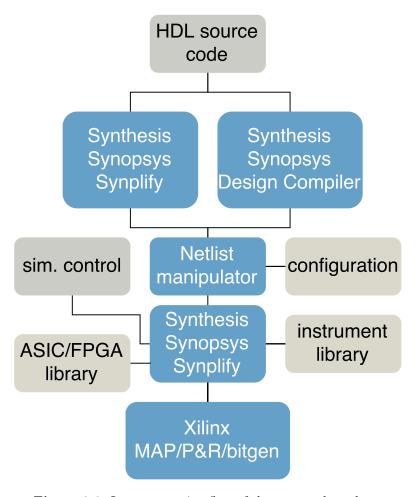

| 3.9           | Instrumentation flow of the proposed emulator                                                                                                               | 57       |

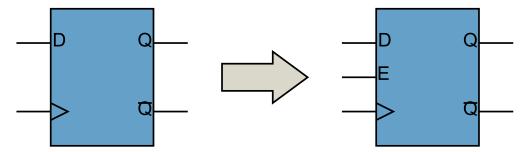

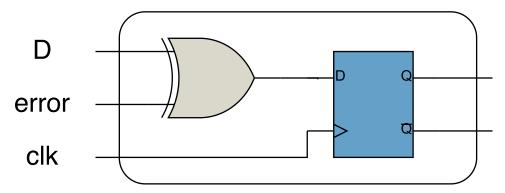

|               | Xilinx FD flip-flop instrument enabling fault injection                                                                                                     | 58       |

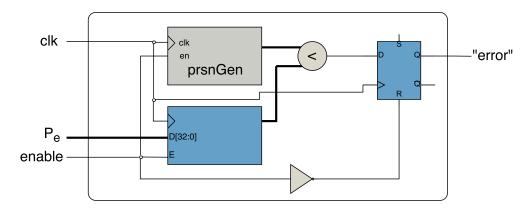

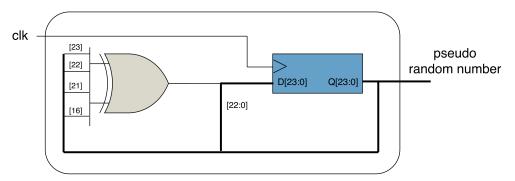

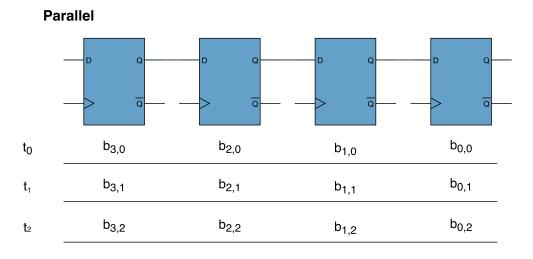

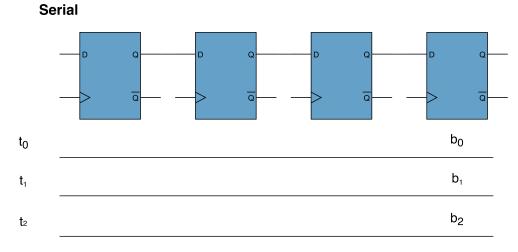

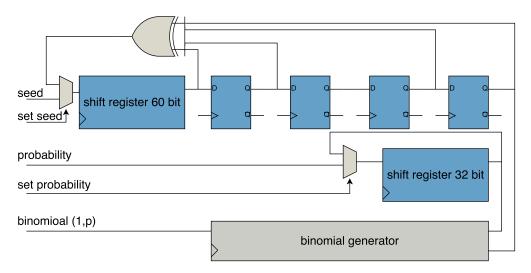

|               | Parallel 24-bit bit error generation                                                                                                                        | 60       |

|               | 24-bit LFSR with maximum length                                                                                                                             | 60       |

|               | Block diagram of the emulator, supporting on-the-fly injection of bit-errors                                                                                |          |

|               | generated on the host PC                                                                                                                                    | 62       |

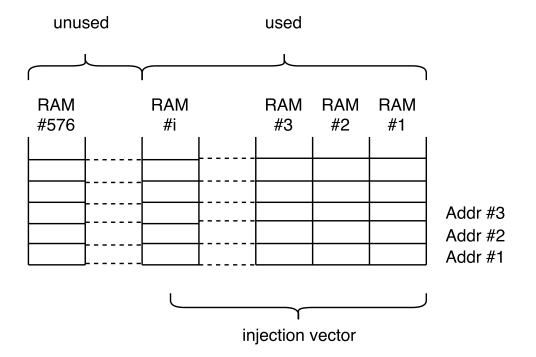

| 3.14          | Memory organization, storing injection location and time on Xilinx FP-                                                                                      |          |

|               | GAs when generated on host PC                                                                                                                               | 62       |

| 3.15          | Serial versus parallel random number generation                                                                                                             | 64       |

| 3.16          | Improved serial bit-error generation                                                                                                                        | 65       |

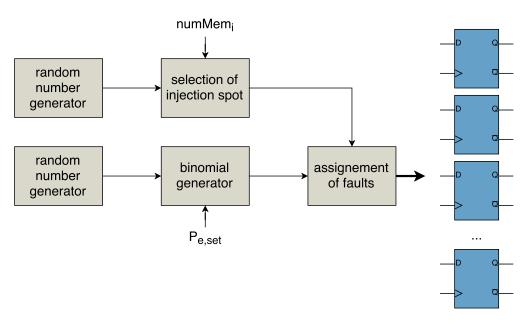

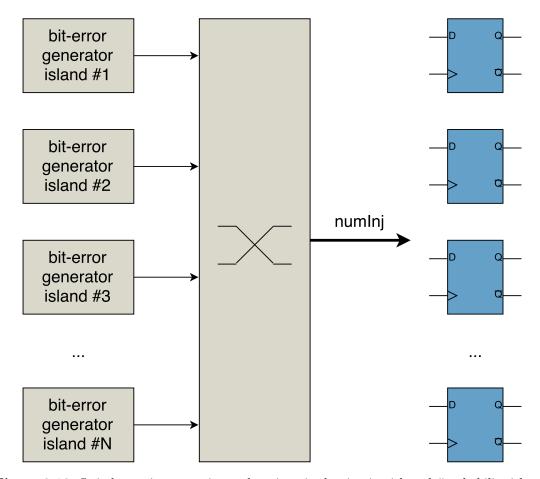

| 3.17          | Feeding a whole "probability island" with probabilistic bit-errors from a                                                                                   |          |

|               | single generator source                                                                                                                                     | 67       |

| 3.18          | Switch matrix connecting each register in the circuit with each "probability                                                                                |          |

|               | island"                                                                                                                                                     | 68       |

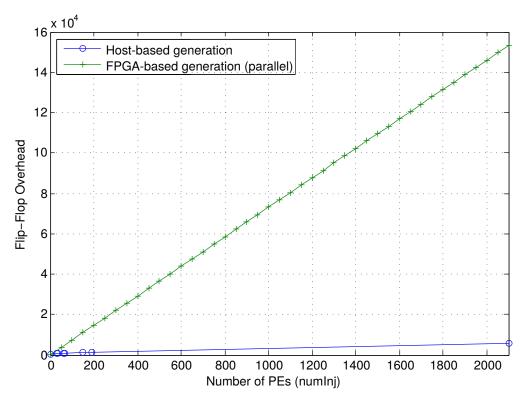

| 3.19          | Area overhead when generating faults on the FPGA compared to when                                                                                           |          |

|               | generating on the host PC                                                                                                                                   | 70       |

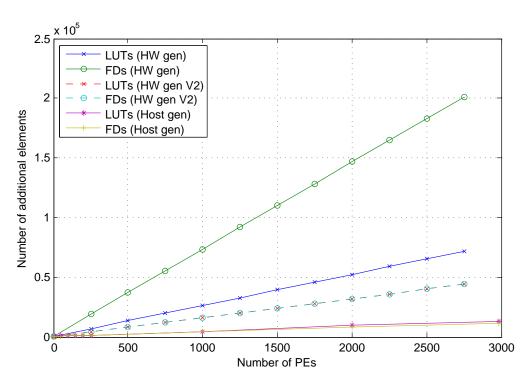

| 3.20          | Comparison of the area overhead of the probabilistic bit-error generators,                                                                                  |          |

| 0.04          | for serial, parallel and host-based generation.                                                                                                             | 72       |

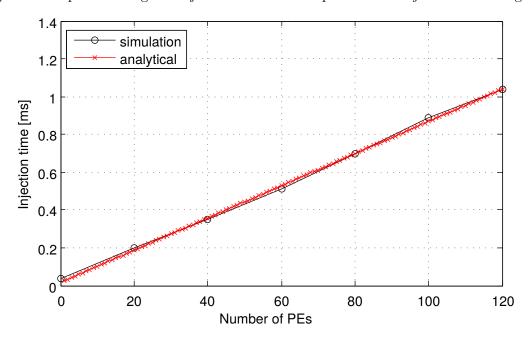

| 3.21          | Configuration time required to transfer desired error probabilities to the                                                                                  |          |

|               | emulator depending on the number of probabilistic elements (measured                                                                                        | 70       |

| 2 20          | and analytical)                                                                                                                                             | 73       |

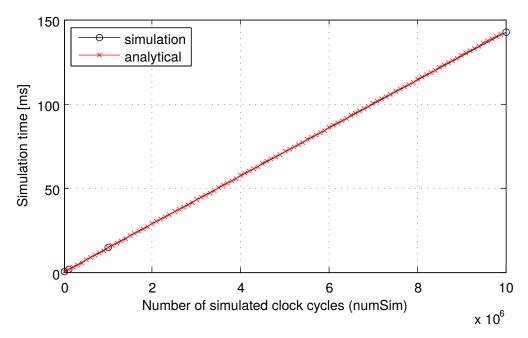

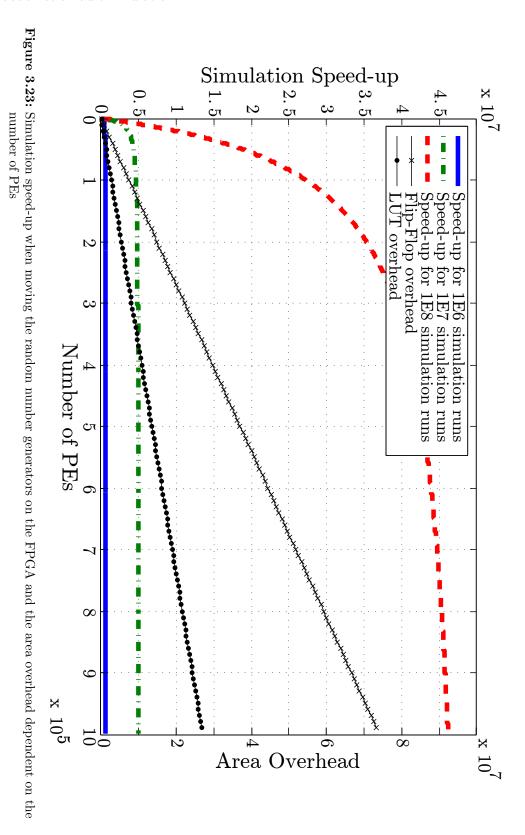

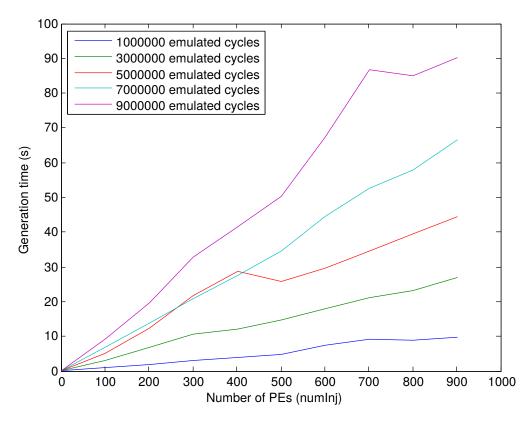

| 3.22          | Simulation time required to run an emulation depending on the number of emulated clock cycles (measured and analytical)                                     | 74       |

| 2 92          | Simulation speed-up when moving the random number generators on the                                                                                         | 14       |

| ა.∠ა          | FPGA and the area overhead dependent on the number of PEs                                                                                                   | 76       |

| 3 24          | Simulation time when generating faults on the host PC for some exemplary                                                                                    | 10       |

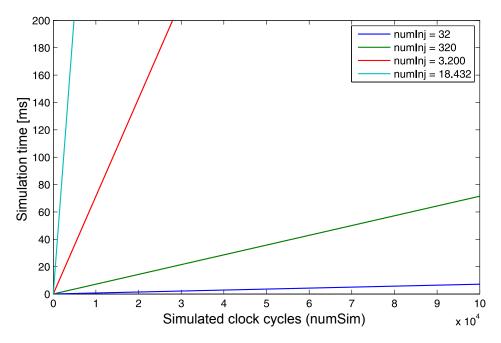

| 0.27          | circuit sizes [133]                                                                                                                                         | 77       |

| 3.25          | Time required to generate random numbers on a regular desktop PC de-                                                                                        | • •      |

| J. <b>2</b> 0 | pending on the circuit size                                                                                                                                 | 78       |

|               |                                                                                                                                                             |          |

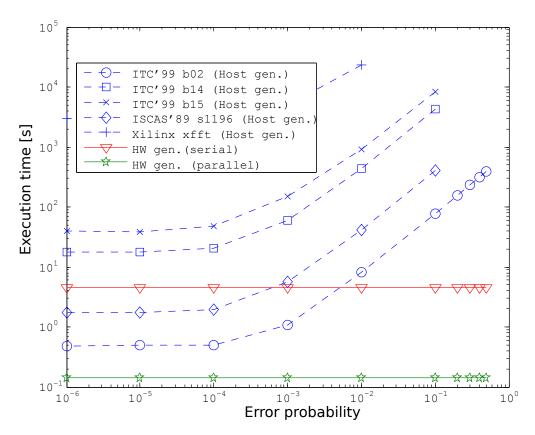

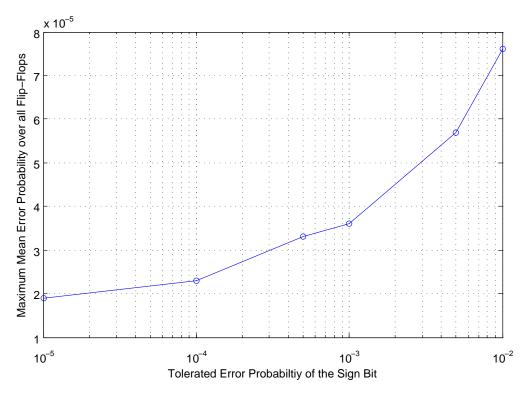

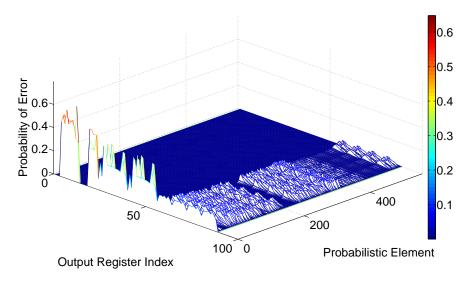

|      | Performance comparison of host-based, parallel and serial fault generation<br>Possible error distribution at the flip-flops of the time synchronization                                                                                                                                                                                                                                                                                                         | 79  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | block of a DAB receiver, still meeting an arbitrary set of constraints on the output pins [136]                                                                                                                                                                                                                                                                                                                                                                 | 81  |

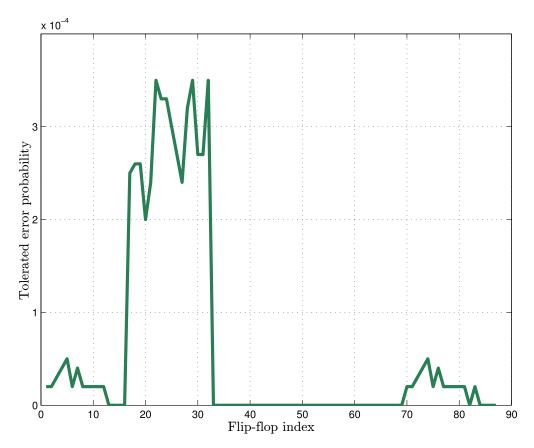

| 3.28 | Possible maximum mean error-probability over all flip-flops of the FFT block of a DAB receiver, still meeting an arbitrary set of constraints on                                                                                                                                                                                                                                                                                                                |     |

|      | the output pins [136]                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82  |

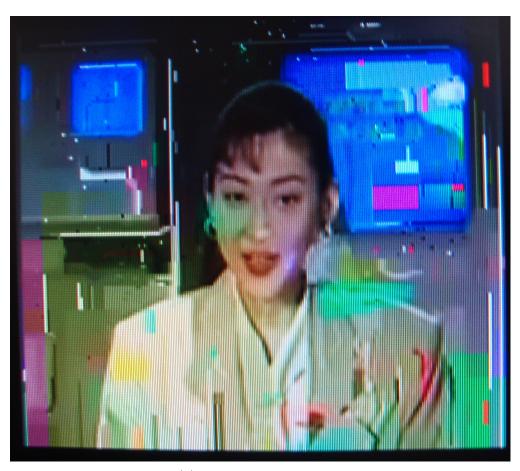

| 3.29 | Impact on fault injection into different functional parts of the h.264 video decoder [135]                                                                                                                                                                                                                                                                                                                                                                      | 83  |

| 3.30 | Relation of errors ( $p_e = 0.5$ ) injected at registers and resulting error rates at output pins of the intraprediction block of a h.264 video decoder [135] .                                                                                                                                                                                                                                                                                                 | 84  |

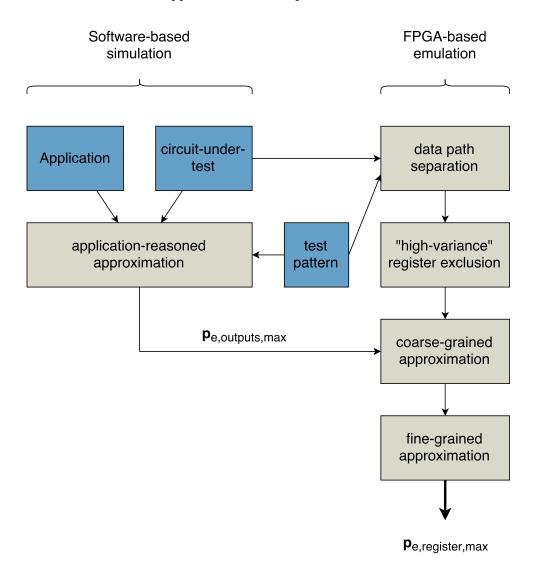

| 4.1  | An overview of the approximation tool-flow presented in this work $\dots$                                                                                                                                                                                                                                                                                                                                                                                       | 86  |

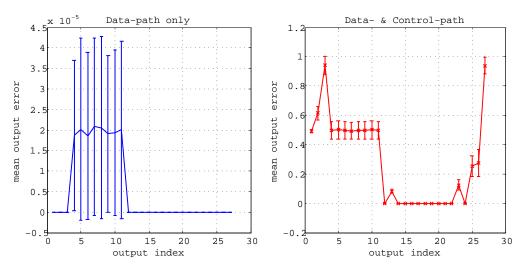

| 4.2  | Output error probability and variance of a "spacewire" implementation when injecting equally errors with a probability 0.0001 in both data- and                                                                                                                                                                                                                                                                                                                 |     |

|      | control path [143]                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87  |

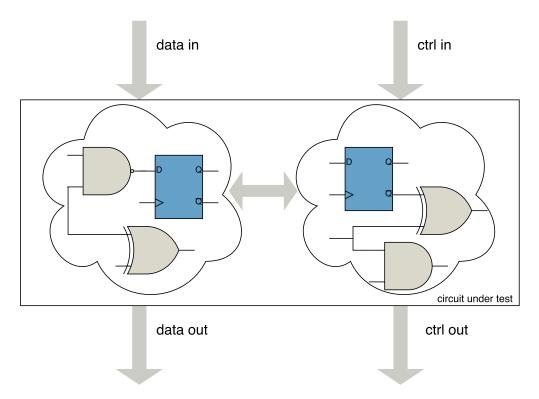

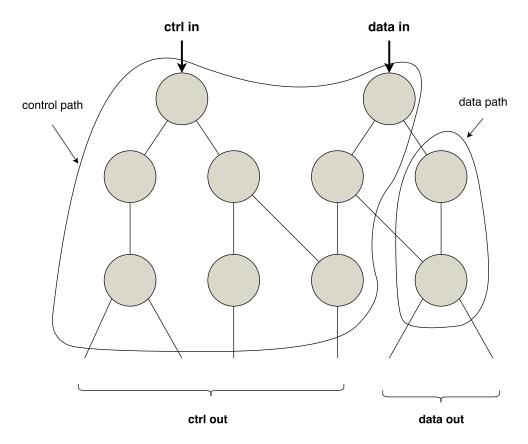

| 4.3  | Visualization of control and data flow of a generic circuit                                                                                                                                                                                                                                                                                                                                                                                                     | 89  |

| 4.4  | Data and control path separation based on analyzing the netlist of a circuit                                                                                                                                                                                                                                                                                                                                                                                    | 90  |

| 4.5  | Visual representation of the "Probability-Relation-Matrix" of benchmark circuit "QR Decomposition" [122]                                                                                                                                                                                                                                                                                                                                                        | 92  |

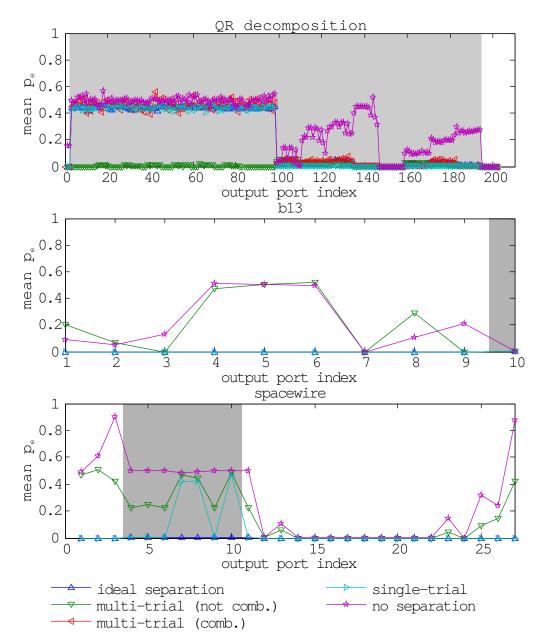

| 4.6  | Emulation results of different evaluation circuits when injecting errors with a probability of $p_e = 0.0001$ into registers based on different separation techniques as presented in Section 4.1, each emulating $50 \times 10^3$ clock cycles                                                                                                                                                                                                                 |     |

|      | $[143] \ldots \ldots$                                                                                                                                                                                                                                                                                                                                         | 97  |

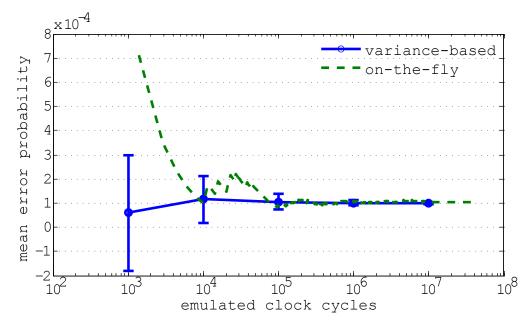

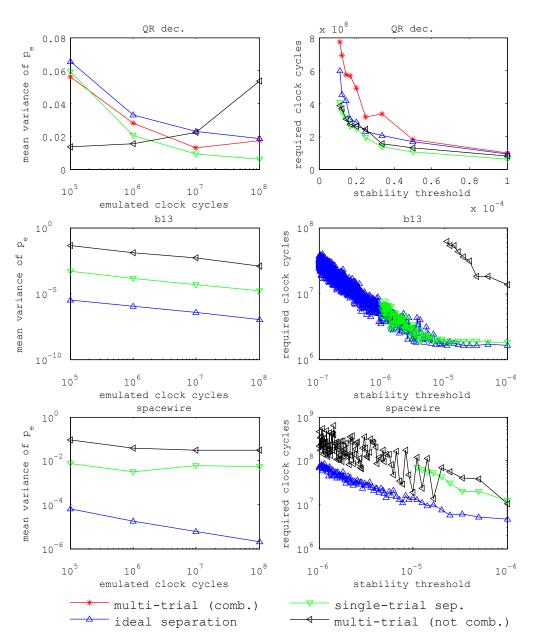

| 4.7  | Error probability mean and variance over 50 trials for variance-based and "on-the-fly" approach at the data output pin of benchmark circuit b13. Equal injection of errors with $p_e = 0.0001$ into the data path. [143]                                                                                                                                                                                                                                        | 99  |

| 4.8  | Figures in the left column are showing the mean variance of the measured output error probabilities for different benchmark circuits when injecting errors with a probability of $p_e = 0.0001$ into registers based on different separation techniques and for a different number of emulated clock cycles. The right column is showing the estimated required number of cycles for different stability thresholds using the method presented in Section 4.2.2 |     |

|      | [143]                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 102 |

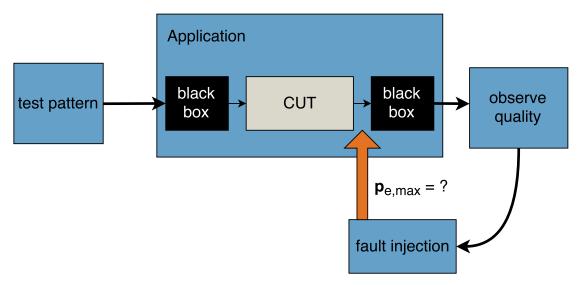

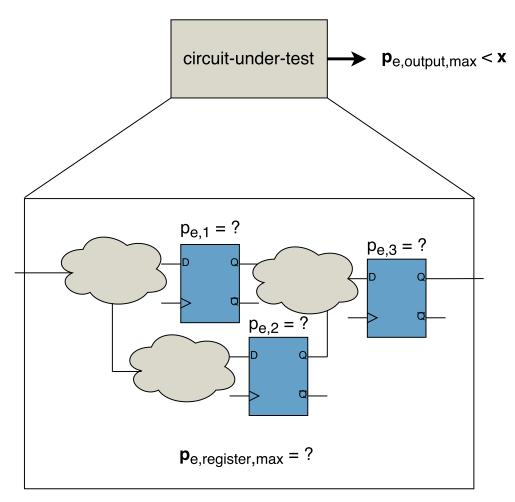

| 4.9  | Software-based fault injection at application-level to determine the possible approximations at register-level for the circuit under test                                                                                                                                                                                                                                                                                                                       | 103 |

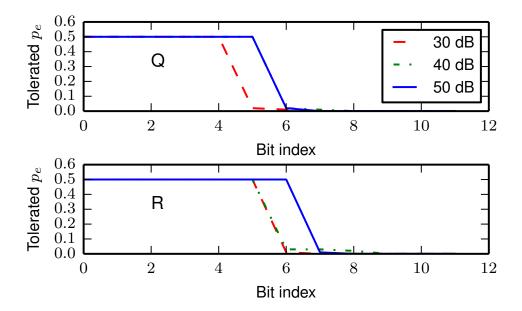

| 4.10 | Tolerable imprecision of a QR decomposition, part of a $8x8$ MIMO zero-forcing equalizer, for different signal qualities and a target BER=0.01 [144] I                                                                                                                                                                                                                                                                                                          | 106 |

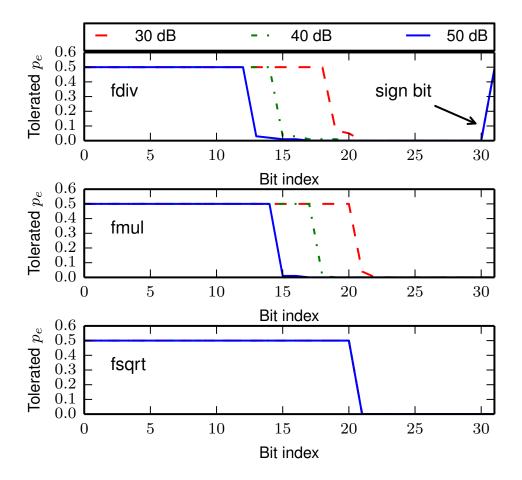

| 4.11 | Tolerable imprecision of floating-point operations in a <i>sobel</i> filter for different target qualities (PSNR) [144]                                                                                                                                                                                                                                                                                                                                         | 107 |

| 4.12 | The optimization problem of Approximate Computing - finding the largest approximations for a given quality constraint                                                                                                                                                                                                                                                                                                                                           |     |

|      | approximations for a Sixter dame? competenting                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

### List of Figures

| 4.13 | The coarse approximation is detecting all circuit elements that can be removed from the circuit as their influence on the quality of the application |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | is negligible                                                                                                                                        | 110 |

| 4.14 | Clock gating of coarse approximated circuit elements realized by replacing                                                                           |     |

|      | fault injection instruments by flip-flops with clock enable input                                                                                    | 111 |

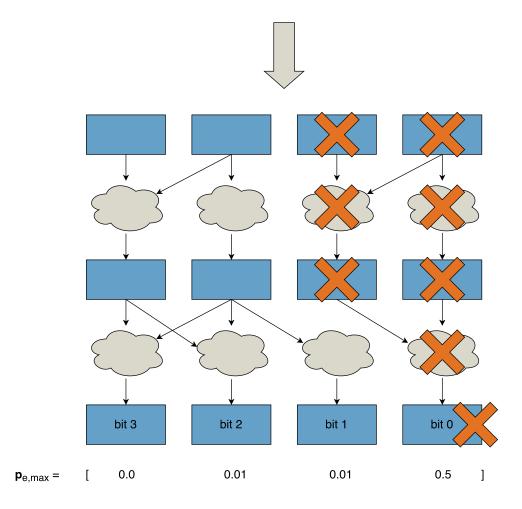

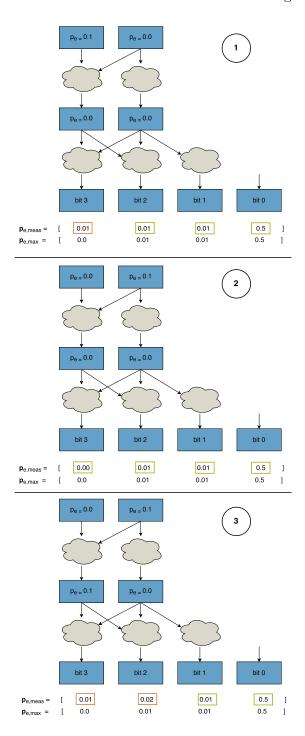

| 4.15 | Fine approximation algorithm - step-wise increment of error probabilities                                                                            |     |

|      | at the registers                                                                                                                                     | 113 |

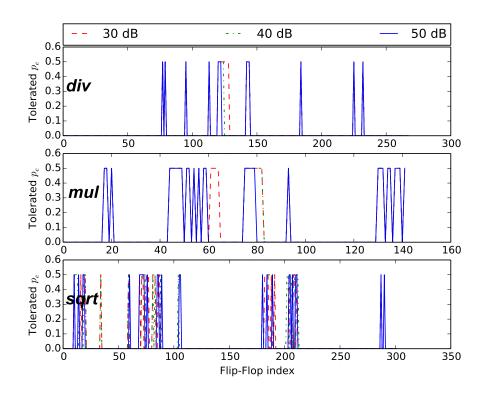

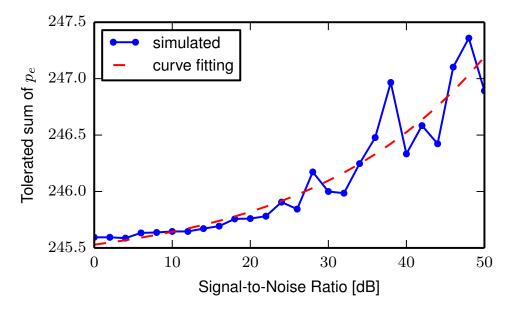

| 4.16 | 11 · · · · · · · · · · · · · · · · · ·                                                                                                               |     |

|      | tolerable error probability at each register                                                                                                         |     |

|      | Approximation result for benchmark circuit "fpu100"                                                                                                  | 118 |

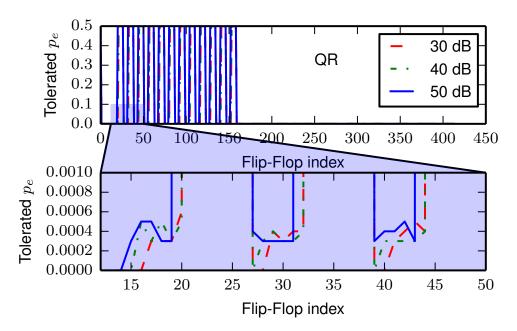

| 4.18 | Possible approximations in terms of tolerated error probabilities, for bench-                                                                        | 110 |

| 4 10 | mark circuit <i>viterbi</i> for varying signal qualities and a target BER=0.0                                                                        | 119 |

| 4.19 | Dynamic power consumption of benchmark circuit $QR$ for different approximations based on vowing signal qualities, when performing $8\times 8$ TE    |     |

|      | proximations based on varying signal qualities, when performing 8x8 ZF Equalization [143]                                                            | 120 |

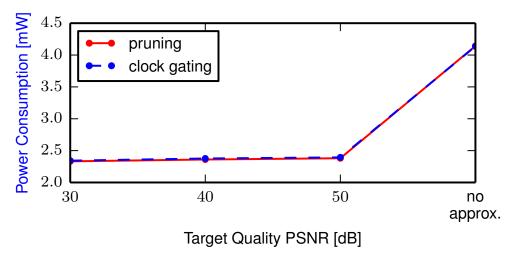

| 4 20 | Power consumption of benchmark circuit fpu100 (multiplication) for dif-                                                                              | 120 |

| 1.20 | ferent approximations based on varying target qualities, when performing                                                                             |     |

|      | a sobel filter                                                                                                                                       | 121 |

|      |                                                                                                                                                      |     |

| 5.2  | Overview of the voltage over-scaling methodology presented in this work.                                                                             | 128 |

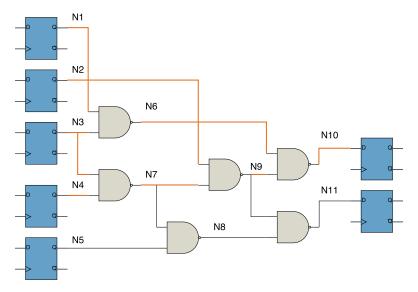

| 5.3  | Schematic of benchmark circuit "c17". Marked in orange the fanin of the                                                                              | 100 |

| F 1  | one output register                                                                                                                                  | 129 |

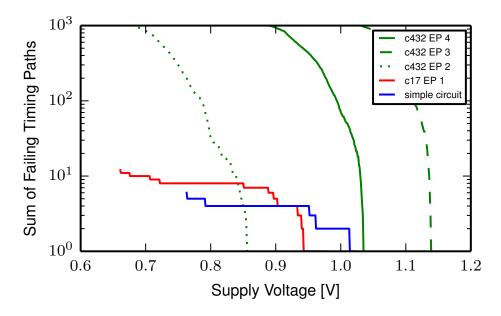

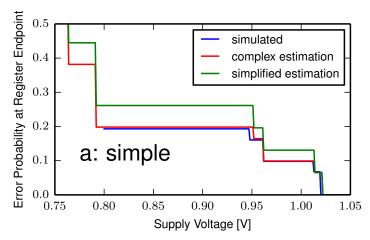

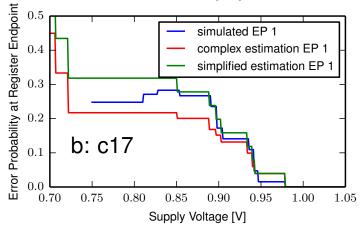

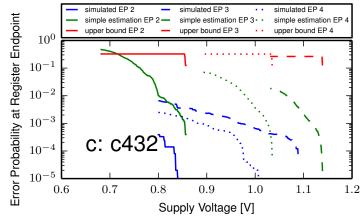

| 5.4  | Sum of failing paths (selected endpoints EP) depending on supply voltage for benchmark circuits: "simple", "c17" and "c432" [145]                    | 190 |

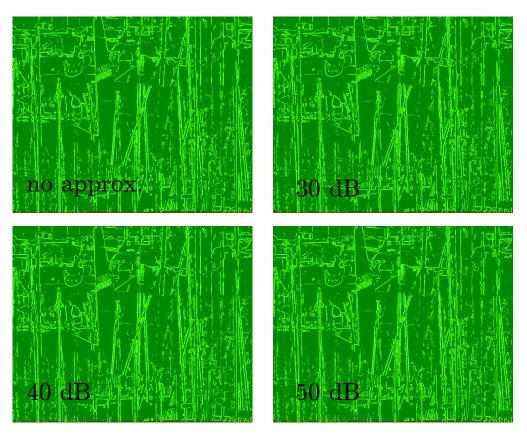

| 5.6  | Difference of the visual quality of a Sobel filtered still when applying no                                                                          | 190 |

| 5.0  | approximation and an approximation for target qualities 30, 40 and 50 dB                                                                             | 138 |

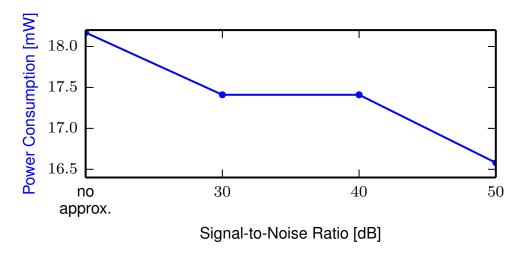

| 5.7  | Estimated power consumption of a floating point unit for different approxi-                                                                          | 100 |

| J.,  | mated operating points of a Sobel filter when applying voltage over-scaling                                                                          |     |

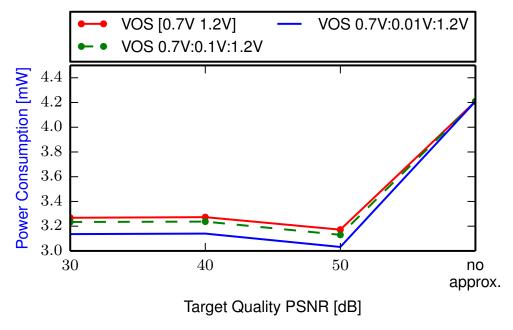

|      | [145]                                                                                                                                                | 139 |

|      |                                                                                                                                                      |     |

# List of Tables

| 2.1 2.2 | Truth table approximation of an adder [29]                                                              | 19<br>25 |

|---------|---------------------------------------------------------------------------------------------------------|----------|

| 3.1     | The resource utilization of the 24-bit wide pseudo random number generator and the injection scan chain | 61       |

| 3.2     | The overall resource utilization of the simulator for exemplary benchmark                               | 69       |

| 3.3     |                                                                                                         | 71       |

| 3.4     | Area overhead of complete simulator compared to circuit under test (pre                                 | ' 1      |

| 0.1     |                                                                                                         | 71       |

| 3.5     | Comparison of the HW overhead for probabilistic bit-error generation on                                 |          |

|         |                                                                                                         | 71       |

| 3.6     | Comparison of the overall simulator area overhead for ITC'99 b14 (post                                  |          |

|         | P&R)                                                                                                    | 73       |

| 4.1     | Evaluation of simulation-based data-path separation, by false-positive and                              | 0        |

| 1.0     | false-negative detected registers (each in total $50 \times 10^5$ emulated cycles) .                    | 94       |

| 4.2     | The benchmark circuits used for the evaluation of the approximation methodology                         | 1.5      |

| 4.3     | Possible Approximation for benchmark circuit $QR$ and $fpu100$ for different                            |          |

|         | quality goals                                                                                           | 17       |

| 5.1     | Transition possibilities of a NAND2 gate. Highlighted are the combina-                                  |          |

|         | tions that transfer an edge                                                                             | 33       |

# **Acronyms**

ALU Arithmetic Logic Unit.

ASIC Application Specific Integrated Circuit.

AST Abstract Syntax Tree.

AXI Advanced eXtensible Interface Bus.

BER Bit Error Rate.

CMOS Complementary Metal Oxide Semiconductor.

CPU Central Processing Unit.

DAB Digital Audio Broadcast.

DCT Discrete Cosine Transformation.

DSP Digital Signal Processing.

DVB Digital Video Broadcasting.

DVFS Dynamic Voltage Frequency Scaling.

EDP Energy Delay Product.

FFT Fast Fourier Transformation.

FIFO First-In First-Out.

FPGA Field Programmable Gate Array.

HDL Hardware Description Language.

ISA Instruction Set Architecture.

LDPC Low Density Parity Check.

LFSR Linear Feedback Shift Register.

LTE Long Term Evolution.

LUT Look-Up Table.

MBU Multi Bit Upset.

MIMO Multiple Input Multiple Output.

MOSFET Metal Oxide Semiconductor Field Effect Transistor.

NMOS N Channel Metal Oxide Semiconductor.

### Acronyms

P&R Place and Route.

PCI Peripheral Component Interconnect.

PCMOS Probabilistic CMOS.

PE Probabilistic Element.

PMOS P Channel Metal Oxide Semiconductor.

PPA Power Performance Area.

PPAR Power Performance Area Reliability.

PSNR Peak Signal to Noise Ratio. PTM Probabilistic Transfer Matrix.

QEC Quality Evaluation Circuit.

SEL Single Event Latchup.

SET Single Event Transient.

SEU Single Event Upset.

SPICE Simulation Program with Integrated Circuit Empha-

sis.

SQCC Sequential Quality Constraint Circuit.

UMR Universal Multi Resource.

VHDL Very High Speed Integrated Circuit Hardware De-

scription Language.

# 1 Motivation

Two main trends are dominating the development of integrated circuits over the last decades. The first one is the unabated tendency for shrinking CMOS feature sizes. The motivation for this is to realize more functionality on the same or even smaller chip size at faster clock frequencies. And the second one is the ever increasing demand for low-power applications, inevitable in our mobile society [1]. Both trends are closely connected to each other. Unfortunately, both of these trends don't come for free. They both have in common that they, if driven much further, negatively affect the overall performance of an integrated circuit. Scaled-down technology nodes result in a hard to manage manufacturing process which again results in complex process variations on the IC. That scale-down makes a circuit even more perceptible to the very same variations and to soft-errors due to smaller threshold voltages [2]. Furthermore, in today's designs the chip functionality is usually not limited by the area but often constrained by a limited power budget [3, 4]. With increasing chip density and, at the same time increasing operating frequencies, power dissipation is becoming a serious issue that has to be considered in the design phase. Similar problems can be observed when applying voltage scaling, the

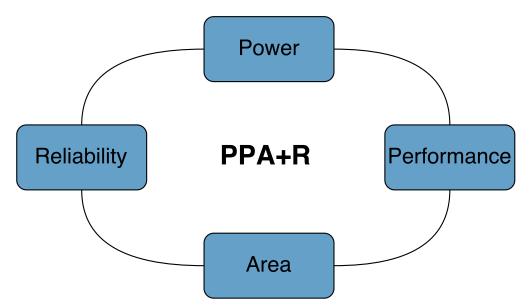

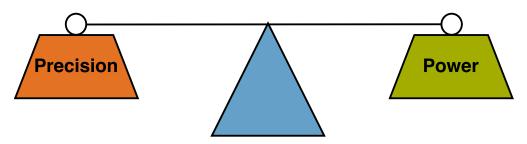

Figure 1.1: The extended "PPA" tradeoff of today's IC designs between power, performance, area and reliability

primary technique for saving power in CMOS circuits. Voltage scaling results in a degraded performance of the circuit due to the decreased speed of MOSFETs, operated at

a lower voltage. Usually, the performance loss is not acceptable for most applications as performance requirements are becoming constantly more and more demanding. However, even for those applications where voltage scaling can be applied, the gain is limited. The margin between supply voltage and threshold voltage is becoming so small to that logic gates are becoming more and more perceptible to small variations and noise in the circuit and in power supplies but also to soft-errors due to radiation. Hence, IC designers have to decide in which direction a circuit has to be optimized. The existing design trade-off between performance, power and area, sometimes referred to as the PPA trade-off, extends by the factor "reliability", as shown in Figure 1.1. It seems that a circuit cannot be fast, have a low power consumption, a small footprint and be reliable at the same time. A fast circuit needs, in order to operate reliable and correct, a sufficiently high supply voltage. And in reverse, a circuit operated at low power cannot be fast. Small circuits can usually not spend the area for redundancy mechanisms which would be required to provide sufficient reliability for circuits operated at near threshold or regular circuits e.g. in space applications. And finally, the reliability, as seen before, is depending on the power and area budget of a circuit. A reliable circuit can basically neither be small, nor power efficient.

However, recently one approach has appeared in the literature trying to tackle this problem, namely "Approximate Computing". The main idea of Approximate Computing is to relax the need for fully precise or completely deterministic operations [5], in order to substantially improve the energy efficiency. That means, Approximate Computing proposes to tolerate faults or imprecision in a circuit in order to save power. Various means on how the power can be saved exist and they vary a lot. The two most common approaches are aggressive voltage over-scaling and functional approximation. In the former case, the supply voltage is scaled down so far, so that timing violations occur in the critical paths of the circuit. When recalling the formula for the dynamic power consumption in CMOS devices, as shown in Equation 1.1, one can see that this method is ideal for saving power due to the quadratic relation of the supply voltage  $V_{dd}$  on the power consumption.

$$P_{dyn} = \alpha_{01} f_{clk} C_{load} V_{dd}^{2} \tag{1.1}$$

The latter method, functional approximation, instead proposes to switch off or remove those parts of the circuit that are not absolutely required for the operation, respectively the desired quality of the calculated result. The pruning can be performed either dynamically for instance by clock or power gating techniques or statically at synthesis time. Clearly, this method promises to save even more power, as the gates are completely switched off and therefore also the static power consumption is tackled.

Naturally, not all applications are suitable for Approximate Computing. Safety critical applications for instance, can never be approximated. There are mainly two types of applications that seem to suitable for such an approach. The first class of applications are those that have an *imprecision tolerance*. These are e.g. applications that somehow interfere with the human perception. For instance applications from the image, video or audio processing domain. The second class of applications are those that have an *intrinsic reliability*. These are applications that anyhow have to deal with noisy or imprecise data and know how to deal with it, like signal processing applications in wireless

communication systems. For such systems it might be irrelevant whether the imprecision in the processed data is coming from the communication channel or from the hardware. The full potential of Approximate Computing can be unlocked if the approximations are applied dynamically. Compared to state of the art optimization mechanisms, e.g. like fixed-point arithmetic, which is usually applied statically at design time or in the best case at synthesis time, Approximate Computing proposes to be applied at run-time. Based on actual conditions or the actual need, the precision of the computed result, and hence its power efficiency, can be scaled. In order to elaborate these relations more in detail, in the following two motivational examples are given. Consider any arbitrary wireless communication system. Such systems are usually working with the same precision independent of the quality of the received wireless signal. These systems are designed to deliver fault free data at the output of the decoding chain, no matter if the signalto-noise ratio is high, or if it is low. However, in case the channel quality is very good, the decoder would not be required to operate with the same high precision as in a bad channel environment in order to deliver the same output bit error rate. For instance, when looking at a convolutional decoder, such as a Viterbi decoder, it could be operated with less precision while consuming less power. Alternatively, an iterative decoder could be operated with less iterations. If the receiver is close to the transmitter, it could switch to a resource- and power-saving, but less precise state, as the signal quality itself is good enough to deliver a fault-free data output. However, if the receiver is moving away from the transmitter, and if the channel quality degrades, it could switch on the "precision" of the decoding chain, so that the output bit-error-rate remains constantly low.

The precision of an application could also be adapted based on the actual need in order to save power either preemptive or reactive. For instance in live video streaming the video feed is usually compressed in order to reduce the data rate. The compression is often done using dedicated hardware accelerators, due to its complexity. However, even hardware accelerated, this is a complex and power consuming task. For battery-powered mobile applications, it might be conceivable to reduce the precision of the compression, hence the resulting video quality, in order to increase the energy efficiency when running out of battery. With today's techniques it is already possible to reduce the resolution or quality (e.g. based on macroblocks per second) which can also be seen as an operation trading precision with power consumption. Originally however, these features are designed to reduce the data-rate. Again, Approximate Computing introduces the adaptivity into the field. Furthermore, resolution and quality profile can remain the same. If, e.g. during a live transmission, the mobile device is running out of battery, it could reduce the precision of the encoder. This in turn could allow to continue the stream, while accepting some artifacts in the stream, that are barely noticeable by the user. Clearly, some existing optimization techniques and Approximate Computing can go hand

Clearly, some existing optimization techniques and Approximate Computing can go hand in hand with each other, and can support each other. Some of them are closely related. Approximate Computing is a field that can, and has to be, applied on all levels of abstraction in order to get the most benefit of it. In Section 2.2, the various possibilities of approximation will be evaluated. However, the main focus of Approximate Computing up to now and its novelty is the approximation at hardware level. Approximate Computing tries to loosen the restriction on "Boolean equivalence" of the hardware, i.e.

#### 1 Motivation

the need for predictability of the hardware. This work focuses on the approximation of generic sequential integrated circuits. Previous works, operating on hardware level, as we will see in Section 2.3, either do not consider sequential hardware and do not propose a generic approach, but only application specific optimizations. Whereas this work researched the possibilities, difficulties and limitations to apply "Approximate Computing" to any existing circuit in a generic manner. The benefit of a generic approach is that most of the approximations can be automated, as much less specific knowledge about the circuit and its functionality is required. This is very important in order to make this paradigm widely applicable. The difficulty is to develop approximation algorithms that can be, on the one hand, generally applied to any kind of circuit and, on the other hand, are efficient in terms of approximation at the same time. Approximation algorithms have to determine the location where approximations can be made within a circuit and the degree of approximation that is possible for a desired quality constraint. Furthermore, as we will see later in detail, approximation speed, i.e. the time it takes to analyze and approximate a circuit, is also very important and hard to maintain. These considerations were influencing the decisions throughout most of the thesis.

# 2 Introduction

In order to perform the approximation of integrated circuits, one first has to understand the basic relations between imprecision in a circuit and its power consumption. In this chapter the fundamentals of CMOS power consumption and how approximations can be used to reduce it will be explained. A comprehensive introduction into the domain of Approximate Computing will be given. Furthermore, the different domains where Approximate Computing can be applied, the different types of approximation, circuit reliability in general, as well as metrics to measure approximation will be presented. Finally, a detailed overview about prior and related works will be given.

## 2.1 Power Consumption Dilemma of Integrated Circuits

The main goal of the techniques presented in this thesis is to reduce the overall power consumption of integrated CMOS circuits. Even though some approaches can be also used to reduce the area of an integrated circuit or increase the clock frequency, as we will see later, this can be seen more as a secondary optimization goal.

The total power consumption of CMOS circuits can simplified be expressed as:

$$P_{\text{total}} = P_{\text{dynamic}} + P_{\text{static}}, \tag{2.1}$$

the sum of the dynamic power consumption and the static power consumption, where the former consumes power only when actually "switching" and the latter at any time when connected to a supply voltage.

### 2.1.1 Dynamic Power Consumption

Dynamic power consumption is defined as the portion of the total power consumption that originates from switching the state of a circuit, e.g. a logic gate. It itself again consists of two portions.

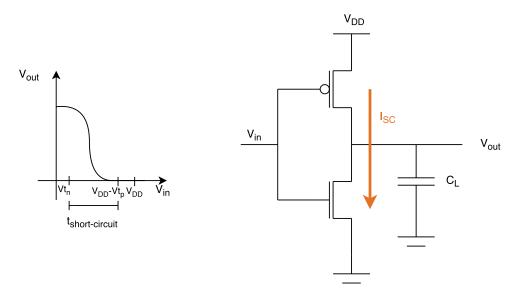

Short Circuit Power Dissipation The short circuit current is the current that flows from supply voltage via the pull-up path of a gate (PMOS) through the pull-down path (NMOS) to ground, in case both blocks, pull-up and pull-down are conducting at the same time. This can happen for instance when the input voltage  $V_{GS}$  is not using the full voltage hub between  $V_{DD}$  and GND, resulting in one MOSFET operating in saturation, and the other in the linear region. However as this effect is arising from miss-dimensioning of the circuit or variation of the fabrication it cannot be counted as a dynamic component. However, short circuit current does also arise, when regular

Figure 2.1: Short circuit power of a CMOS inverter

loading or unloading a load capacitance. This effect is shown in Figure 2.1. For instance in a CMOS inverter, when  $V_{IN} = V_{DD}/2$ , both NMOS and PMOS are operating in saturation. It hence depends on the slope of the input signal how long both transistors are in saturation. This interval is defined as  $t_{\rm short-circuit}$  in the Figure. Furthermore, it also depends on the ratio  $v = V_t/V_{DD}$ , where  $V_t$  corresponds to the threshold voltage. For values v > 0.5 short circuit current is eliminated, as NMOS and PMOS cannot be switched on at the same time. In today's technology generations  $V_t$  is in the range of 0.3V while the supply voltage  $V_{dd}$  is at about 1V [3]. Hence, short circuit current is negligible.

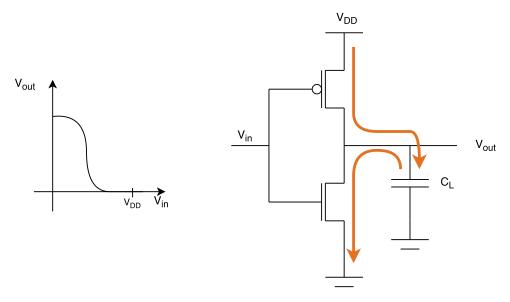

Capacitance Switching Power Dissipation The main factor of the dynamic power consumption is generated by loading and unloading the load capacitance of a gate. The load capacitance consists of the gate capacitance of all gates that are connected to the output of a gate (fanout). Additionally, the capacitance of the wires, as well as the intrinsic capacitance between source and drain are contributing as well. Every time the load capacitance is loaded and unloaded a charge of  $Q = C_L V_{DD}$  is transferred from  $V_{dd}$  to GND, as depicted in Figure 2.2. Hence the current that flows in each complete charge-discharge cycle can be calculated as:

$$I_{cap} = C_L V_{DD} f (2.2)$$

The resulting power consumption due to loading and unloading the load capacitance can hence be calculated as:

$$P_{cap} = \alpha_{01} C_L V_{DD}^2 f, \qquad (2.3)$$

where  $\alpha_{01}$  corresponds to the switching factor, as usually a gate is not switching in every clock cycle. As the short circuit power dissipation is negligible compared to the power

dissipation resulting from un-/loading the load capacitance, one usually focuses on the latter in order to minimize the power consumption of integrated circuits. In the following

Figure 2.2: Capacitance switching power of a CMOS inverter

we will see, how each of the factors of Equation 2.3 can be used to reduce the overall power consumption of integrated circuits. Starting from the left, the first term that could be reduced in order to minimize the dynamic power consumption is the switching factor  $\alpha_{01}$ . The switching factor is defined as the probability of a signal transition in one clock cycle. Reducing the switching factor by architectural changes is not simple and not intended, as this also correlates with the circuit efficiency. A circuit, by definition, cannot be efficient if it changes its state rarely. However, one very efficient technique in order to reduce the dynamic power consumption based on the switching factor is "Clock Gating". By disabling the clock of a circuit, the switching factor reduces to zero in sequential circuits. Applying this technique dynamically to sub-blocks of a circuit, that are not used all the time, can save a tremendous amount of power. Especially in the age of "Dark Silicon" this is a widely used technique. The second factor of Equation 2.3 is the capacitance  $C_L$ . Capacitance can be reduced by either reducing the gate capacitance  $C_g$  of a technology, or by reducing the wire capacitance of the circuit. The former can only reduced by introducing a new CMOS technology that usually results in a shorter gate length and hence a smaller gate capacitance  $C_L$ . However, a reduction of technology node sizes is a complex task that requires tremendous research effort. It is not a parameter the designer can choose. Additionally, today a reduction of the technology size is usually accompanied with an increase of parameter variations like threshold voltage, which requires a certain delta between  $V_{th}$  and  $V_{DD}$ , large enough to tolerate these variations. This in turn makes it difficult to save power by reducing the supply voltage. The third parameter is the supply voltage  $V_{DD}$ . Reducing the supply voltage in order to reduce the dynamic power consumption of an integrated circuit seems to be the primary choice due to the quadratic relationship. However, the most important drawback is that the by decreasing the supply voltage of CMOS gates, the propagation delay is increasing. The propagation delay can be approximated as follows:

$$t_p = \ln(2)C_L R,\tag{2.4}$$

where R corresponds to:

$$R = \frac{V_{DS,p}}{I_{DS,p}} \approx \frac{1}{\beta(|V_{GS,p}| - |V_{th,p}|)},$$

(2.5)

In CMOS circuits  $V_{GS,p}$  equals  $V_{DD}$ . Hence one can see that a reduction of the supply voltage increases the propagation delay. This again would require, in order to maintain the functionality of a circuit, to reduce the operating frequency of the circuit in order to meet the timing constraints. For most applications this performance loss is not acceptable. One approach to scale the supply voltage anyway is "Dynamic Voltage Frequency Scaling". This technique however is usually only applicable to CPUs. The idea of this technique is to scale the supply voltage in conjunction with the operating frequency depending on the actual work load. Hence, in case a CPU has a low workload, the operating voltage and frequency can be reduced in order to save power. When the workload increases, the voltage and operating frequency is increased as well in order to offer the performance required for the workload. This technique is widely applied in today's CPUs. In today's technologies where chip size is cheap, one can think of another method as well. Instead of dynamically adjusting the voltage-frequency operating point based on the workload, one could simply add another low-voltage CPU to the system. This slow, but power efficient CPU can then be used for simple computational tasks like background calculations, while the faster variant is used for peak workload. This technique is usually more power efficient than DVFS as the variants can be optimized exactly for their operating point. This heterogeneous technique is widely applied in today's mobile devices, where most of the workload can be seen as background tasks, and fast and responsive calculations are only required when the user interacts with the device.

Reducing the supply voltage close to the threshold voltage does not only impose a performance loss. Unfortunately, supply voltage noise is not scaling with the voltage. This effect is similar to the parameter variations as we have seen before. Usually, a certain "guard band" between  $V_{th}$  and  $V_{DD}$  is required in order to be robust against thermal noise and parameter variations. One possibility to overcome this problem could be to equally reduce the threshold voltage. However, this results in yet another problem. A reduced threshold voltage results in increased sub-threshold leakage, which in turn results in an increased, not negligible, static power dissipation, as we will see in following.

### 2.1.2 Static Power Consumption

The static power consumption is the power that is consumed even if no load capacitance is switched. It is therefore independent of the operating frequency f as well as the switching activity  $\alpha_{01}$  of a circuit. There are multiple sources for static power consumption from

which the two most important ones will be shortly explained here. Simplified, the leakage current can be described as:

$$I_{\text{leak}} = I_{\text{sub}} + I_{\text{ox}} \tag{2.6}$$

where  $I_{\text{sub}}$  is the "subthreshold leakage" component and  $I_{\text{ox}}$  is the "gate leakage" component.

Subthreshold Leakage Subthreshold leakage is defined as the current that flow between source and drain, when the MOSFET channel is supposed to be off. This can happen when the channel is in "weak inversion". Even if the gate-source voltage  $V_{GS}$  is below the threshold voltage  $V_{th}$  free charge carriers can be observed between source and drain. These carriers can create a current mainly due to diffusion. The intensity of the weak inversion is depending on two factors. On the one hand the current is depending on the channel width W. In a wide channel the current increases while in a narrow one it decreases. And on the other hand the intensity is depending on the threshold voltage  $V_{th}$ . A smaller threshold voltage is drastically increasing the weak inversion as even small noise on the gate voltage will have a large effect on the inversion. The relations are again shown simplified in Equation 2.7 [6].

$$I_{\text{sub}} = K_1 W e^{-V_{th}/nV_{\theta}} (1 - e^{V_{\text{dd}}/V_{\theta}}),$$

(2.7)

where  $K_1$  and n are experimentally derived values and  $V_{\theta}$  is a value depending on the temperature.

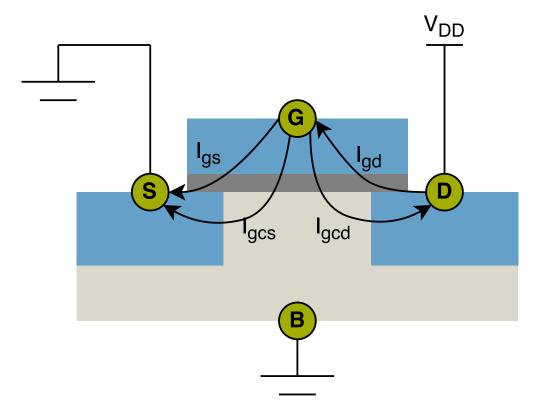

Gate Leakage During the last decade a new leakage source arose, the gate leakage. Gate leakage became the dominant factor of static power consumption for technology generations < 65nm [7]. Due to the fact that the oxide is becoming thinner every technology generation, more and more electrons can tunnel through the oxide. Gate leakage current can be observed between gate-source, gate-drain, gate-channel-source, gate-channel-drain and gate-bulk, as shown in Figure 2.3.

$$I_{\text{ox}} = I_{GS} + I_{GD} + I_{GCS} + I_{GCD} + I_{GB} \propto \frac{1}{t_{\text{ox}}}$$

(2.8)

The effects of gate leakage are much worse in NMOS than in PMOS.

We can see from Equations 2.7 and 2.8 that basically four possibilities to reduce  $I_{\text{leak}}$  exist. In order to reduce  $I_{\text{sub}}$  one can either reduce the supply voltage, the threshold voltage or the channel width. This, as we have seen before, results in a usually not acceptable performance loss. In order to reduce  $I_{\text{ox}}$  one can reduce the dielectric thickness. However, in order keep the influence of short-channel MOSFET effects low, the oxide thickness has to be scaled proportionally to the channel length. New techniques like high-k insulators are improving the situation due to their superior insulation capabilities. However, in general one can see that if MOSFETs shall be fast, the leakage current is inevitably increasing. The same can be seen for the switching current. A reduction of the power consumption results in a decreasing performance either resulting in a decreased operating frequency or in timing violations.

Therefore, the dilemma of integrated circuits built in their current technology is that they cannot be fast, reliable an energy efficient at the same time.

Figure 2.3: The various forms of gate-leakage in CMOS devices

## 2.2 Approximate Computing

Approximate Computing is a novel paradigm for energy-efficient digital systems that has considerably attracted interest over the last decade [5, 8, 9]. The core principle of Approximate Computing is to trade off power with precision, as visualized in Figure 2.4. It hereby relies on the ability of many applications and the end-user itself to tolerate a loss of quality or imprecise computational results. Clearly, the idea of computing results that are good enough for a certain application, instead of computing with unnecessary high precision is not new. For instance, any lossy compression system for video or audio data is applying the same principle, even though the motivation is slightly different. However, in the last years an increasing number of application fields, at various points in the design flow, have discovered the paradigm for themselves. A variety of techniques have been started capturing under the hood of Approximate Computing. Especially on the hardware level, tolerated non-determinism is a novelty.

There are two other noticeable research fields that are related to Approximate Computing. One is "Probabilistic Computing" and the other is "Near-Threshold Computing", which will be shortly explained in the following.

Figure 2.4: Approximate Computing: trading-off power consumption with precision

Near-Threshold Computing Near-threshold computing proposes to apply voltage-scaling in order to reduce the power consumption. Compared to regular voltage-scaling techniques it is trying to aggressively scale the voltage in the range of the CMOS threshold voltage. The concomitant performance loss is tried to be overcome by massive parallelism and modern design techniques like 3D integration. Near-threshold computing is also aware of functional failures. However, compared to Approximate Computing, it tries to completely avoid them by design changes or redundancy mechanisms. A comprehensive overview can be found in [10] and [11].

Probabilistic Computing Probabilistic computing proposes to exploit the probabilistic nature of circuit elements. Palem et al. developed the notion of probabilistic binary switches under the influence of thermal noise, i.e. operated at low-voltage [12]. Based on these switches probabilistic CMOS circuits (PCMOS) have been proposed, developed and the approach been evaluated [13, 14, 15, 16, 17, 18]. The principal idea of probabilistic computing is the same as of Approximate Computing, namely trading off power consumption with accuracy. The main difference however is, that Approximate Computing is usually using deterministic circuit elements to generate imprecise results. In contrast, probabilistic computing usually uses non-deterministic elements, and is hence considering another fault model. The methodology developed in this work is also not limited to deterministic CMOS elements. Due to the probability-awareness of the presented approach, hence assigning error probabilities to circuit elements, it can be applied as well in the domain of probabilistic computing. Indeed, techniques like circuit pruning, which can be applied for Approximate Computing, have their origin in probabilistic computing [19].

The consideration of imprecisions and non-determinism in digital circuits is going back to the origin of digital design using electromagnetic switches and vacuum tubes. Von Neumann himself, was searching for ways to build reliable circuits from unreliable elements [20]. With the rise of semiconductors and improving process technologies, the problems of unreliable building blocks seemed to disappear. For safety-critical or radiation-intense applications, reliability, of course, has always been an issues. However, means like error correction or redundancy could be exploited to guarantee a functional correctness, at least to a certain degree. However, now as it seems that the end of the classical Moore's

law has been reached [21], it looks like the problems are coming back. Increasing parameter variations, due to shrinking feature sizes, as well as ultra low-power operation tend to make the building blocks again unreliable. At least if the, so called, "happy scaling" continues. Approximate Computing is still assuming that the building block are working correctly. It is trying to directly tackle the power density problems of today's circuits. With the end of classical Dennard scaling [22] about 10 years ago, new technology generations do not lead to a constant frequency increase or a decrease of the power consumption, respectively. Even the shift to the multi-core era is not solving the problem of the high power density, which has led to dark silicon on the chip. In contrast to dark silicon management approaches, Approximate Computing is trying to reduce the power consumption on a chip, while preserving the speed and the functional density. This is achieved by tolerating imprecisions and non-determinisms in the circuit, for instance due to aggressive voltage-scaling or by removing parts of a circuit that are not required for an approximate, yet sufficiently correct, result. The main problem to be solved can be regarded as to find a distribution of approximations made within the circuit as large as possible, while at the same time meeting the constraint on the quality at the output of the circuit.

"Voltage over-scaling" and "circuit pruning" are the main approximation techniques considered in this work. While the former is going in the direction of probabilistic computing, the latter is going in the direction of Approximate Computing. However, as already mentioned, most methods developed to realize such approaches can be shared between these two fields. In the following the types of approximations and sources of imprecisions, hence the fault model, will be described more in detail.

### 2.2.1 Approximation Types

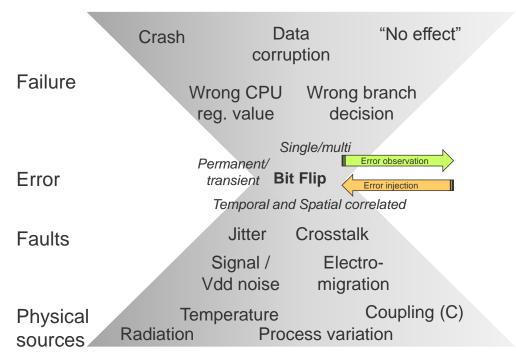

As already mentioned, Approximate Computing can be applied on multiple levels of abstraction. Hence, the actual point where a circuit is approximated can differ. For instance, in case the approximation is done for an application on algorithm-level, for instance by applying fixed point arithmetic instead of floating-point operations, the approximation is solely based on an algorithmic modification. No changes are made on the hardware level. However, for instance, when removing the least significant bit calculations of a floating-point unit at register-transfer level, hardware is indeed modified, while the initial algorithm of the application remains untouched. This work is focusing on approximations at hardware level. As it has been shown in previous work [23], bit-flips can be used to model a variety of physical sources of faults. Figure 2.5 illustrates this relation. All of these faults in the lower half of the hourglass concentrate in a potential error as bit-flips. As we will see in the following chapters in detail, the abstraction to RT-level, at least for an initial analysis of a circuit, gives a balanced trade-off between imprecision due to abstraction and analysis speed-up. When approximating an application one is not only interested in where approximations can be applied but also to what extent. Therefore, in this work bit-flip probabilities at register-transfer level have been introduced. This allows to model the probability of occurrence of the individual approximations, for instance due to masking effects.

Hence, the fault model for the initial analysis and approximation of a circuit in the presented methodology are bit-flips at registers that appear with a certain probability. For an exact analysis the information gained at RT-level has to be transferred down to gate-level, depending on the applied approximation techniques, in order to model the corresponding effects. In the following, the approximation techniques considered in this work will be presented in detail.

Figure 2.5: Bit-flip probability as the mean to model a variety of faults and approximation techniques, respectively [23]

Physically Unreliable Circuit Elements The first type of approximations considered in this work is the use of Unreliable Circuit Elements. Clearly, these are not approximations per se, but anyhow result in a non-deterministic behavior of a circuit. Unreliable circuit elements are the main source of imprecision in the domain of probabilistic computing. There are various reasons why circuit elements, usually logic gates, can be unreliable. The first category are unreliable circuit elements due to "noise-based" faults [24]. The ever increasing demand for fast and energy-saving, hence small, devices led to this problem. Due to the reduced supply voltage and the increasing integration density, noise immunity is becoming difficult to achieve. This results in very tight noise margins, leaving no room for further optimization. Thermal noise in the circuit or voltage regulators [25, 26] can therefore actually limit a further decrease of supply voltage. Similar behavior can be seen with parameter and process variations in the circuit [27]. For a further scale-down of the MOSFETs either the technology process has to be improved, or one has to deal with the resulting non-determinism.

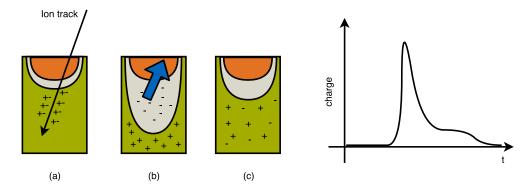

Another source of unreliable circuit elements are soft errors due to radiation. Alpha-

Figure 2.6: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion. [28]