Lehrstuhl für Sicherheit in der Informationstechnik an der Fakultät für Elektrotechnik und Informationstechnik

### New Techniques for Emulating Fault Attacks

### Ralph Heinz-Erik Nyberg

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines **Doktor-Ingenieurs** (**Dr.-Ing.**) genehmigten Dissertation.

Vorsitzender: apl. Prof. Dr.-Ing. Walter Stechele

Prüfer der Dissertation: 1. Prof. Dr.-Ing. Georg Sigl

2. Prof. Dr.-Ing. Ulf Schlichtmann

3. Prof. Dr.-Ing. Dirk Rabe

Die Dissertation wurde am 17.04.2018 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 04.09.2018 angenommen.

### Abstract

Integrated security circuits such as smart cards and security controllers protect sensitive data and protect its integrity with dedicated measures, which are often based on secured implementations of cryptographic algorithms. Besides the typical areas, identification, pay TV and ticketing, integrated security circuits are also deployed in automotive and industrial applications. Usually, countermeasures against so-called fault attacks are implemented in software and hardware to prevent attackers from compromising sensible data with fault attacks. These countermeasures have to be verified already during circuit design taking the specified security requirements into account, which is also known as security verification. For security verification of digital fault countermeasures, pre-silicon fault injection techniques are usually used to model complex physical effects of fault attacks during circuit design. Although abstract fault models are used, the huge variety of fault parameters in terms of spatial and temporal fault injection lead to a fault injection space infeasible to be analyzed completely. Therefore, analysis need to focus on subsets of the fault injection space, which have to be selected based on their relevance for the specified security level. These relevant faults have to be modeled with efficient tools that, on the one hand, provide the appropriate configurability and, on the other hand, provide high-performance to make security verification feasible in given time.

FPGA-based fault emulation, which basically constitutes a hardware accelerated fault simulation technique where the circuit under verification is synthesized onto an FPGA, features the highest possible pre-silicon verification performance. While a test sensitizes the circuit under verification, configurable faults are injected into it by additional hardware components synthesized onto the FPGA along with the actual circuit to be verified. Unfortunately, depending on the implementation, state-of-the-art fault emulation lacks either the configurability required to model arbitrary fault attacks or the performance is limited by a communication bottleneck between software and hardware components for fault configuration. The goal of my thesis is to close the gap between configurability and performance of FPGA-based

fault emulation and to achieve industrial applicability for security related designs.

First, I introduce a meta fault configuration model able to describe arbitrary fault configurations, which I use afterwards to describe the features of the implemented fault emulation techniques. The fault configuration model is defined at a meta level to make it independent of utilized tools, the circuits to be verified and their level of abstraction to be analyzed. This enables the description of fault models known from literature as well as new ones, and reuse for other applications is enabled.

Next, I present an FPGA-based fault emulation environment that supports the configurability required to mimic arbitrary fault attacks in combinational and sequential logic. My implementation supports fault configuration at runtime, which includes configurable fault model types, single and multiple faults and variable fault durations. Fault configurations can be applied at arbitrary discrete times during fault experiments. To allow the injection of time-displaced or time-overlapped faults, I propose a feature to reconfigure the fault settings during runtime in an efficient way, requiring a negligible amount of additional logic. This enables the emulation of sophisticated fault attacks such as exploiting multiple laser beams to inject faults with independent sources in a time-displaced or a time-overlapped fashion.

Further, I propose a hardware-efficient and performance-efficient concept for evaluating emulation results in hardware. This method is supported by a self-testing functional test software for processor-based security designs. A single fault-free emulation is used to generate a golden reference for following fault emulations. This way, the reference for result comparison has not to be generated by a second instance of the circuit to be verified. Moreover, the fault emulator is sensitive to events on dedicated observation points, which allows to judge the circuit behavior in a more flexible manner and reduces false positives in the emulation results. This feature also allows to configure temporal fault injection settings relatively to dedicated events on the defined observation points. For instance, time frames of varying length in which security-relevant operations are executed can be selected for fault injection without manually determining the absolute timing of them.

There are usually considerably more combinational cells than sequential cells in the designs to be verified. As a consequence, instrumenting circuits for fault injection in combinational logic consumes more of the limited hardware resources on the FPGA. Unfortunately, the entire combinational logic needs to be instrumented to support arbitrary multiple fault injection at runtime, which limits applicability compared to fault injection in sequential logic. Moreover, the performance is decreased since timing paths are increased with each instrumented combinational cell. To address these limi-

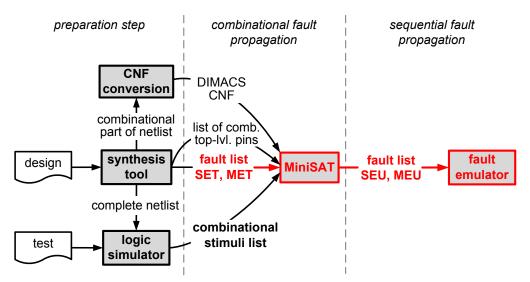

tations, I present a software-based pre-processor that maps faults in combinational logic to equivalent faults in sequential logic. These equivalent faults are then configured into the fault emulator for performance efficient analysis.

Once I achieved my goals w.r.t. configurability and applicability for industrial designs, I focus on performance optimization measures, which finally close the gap between performance and configurability. The presented optimizations address the communication bottleneck of FPGA-based fault emulation, reduce emulation runtime and cancel fault experiments when these exhibit fault effects equivalent to previous experiments.

To discuss the improvements of my work over the state-of-the-art, I applied the presented fault emulation techniques to two different microcontroller designs and configured hundreds of millions of fault attacks. With my results I demonstrate that the presented techniques enable to model arbitrary fault attacks in combinational and sequential logic of industrial designs without performance loss compared to fault-free emulations. As far as fault injection in combinational logic is concerned, I removed the limitation on applicability, I reduced the hardware requirements by 45% and I increased the performance by a factor of six at the same time. The proposed techniques allow to mimic more arbitrary fault attacks in given time and thus help to improve security devices by means of possibly finding more security flaws already during circuit design, i.e. before the manufactured devices are analyzed during post-silicon certification.

# Kurzfassung

Integrierte Sicherheits-Schaltungen – im Sinne des englischen Wortes security – schützen sensible Daten und ihre Integrität. Hierzu werden Sicherheitsmaßnahmen implementiert, die häufig auf abgesicherten Implementierungen kryptographischer Verfahren basieren. Zu integrierten Sicherheits-Schaltungen gehören Chipkarten und Sicherheitskontroller, die zum Beispiel bei elektronischen Reisepässen, Zugangskarten, elektrischen Tickets für öffentliche Verkehrsmittel, sowie für Automotive- und Industrieanwendungen eingesetzt werden. Um eine Kompromittierung sensibler Daten durch sogenannte Fehlerattacken auf integrierte Schaltungen zu verhindern, werden gewöhnlich dedizierter Gegenmaßnahmen in Hard- und Software implementiert. Während der Entwicklung von integrierten Sicherheits-Schaltungen müssen die implementierten Sicherheitsmaßnahmen unter Berücksichtigung der spezifizierten Sicherheitsanforderungen verifiziert werden. Zur Sicherheitsverifikation von digitalen Gegenmaßnahmen hinsichtlich Fehlerattacken werden hierzu üblicherweise Fehlerinjektionstechniken eingesetzt, welche die komplexen physikalischen Auswirkungen von Fehlerattacken bereits während der Entwicklung des Schaltungsdesigns modellieren. Trotz abstrakter Modelle ist es unmöglich, alle möglichen Fehlerattacken zu modellieren, da berücksichtigt werden muss, dass ein Angreifer örtliche und zeitliche Angriffspunkte beliebig variieren kann, was zu einem komplexen Fehlerraum führt. Daher müssen für das zu erzielende Schutzniveau relevante Submengen des Fehlerraums selektiert, anschließend modelliert und basierend auf der Modellierung analysiert werden. Dies erfordert Modellierungswerkzeuge, die zum einen die Konfiguration entsprechender Fehlerattacken ermöglichen und zum anderen sehr performant sind, um die Menge der analysierbaren Fehlerattacken in der verfügbaren Zeit für die Sicherheitsverifikation zu maximieren.

Die FPGA-basierte Fehleremulation, welche prinzipiell eine Hardwarebeschleunigte Fehlersimulation darstellt, ist das schnellste Werkzeug zur Modellierung von Fehlern. Hierzu wird die zu verifizierende Schaltung in ein FPGA konfiguriert. Während die Schaltung durch einen Test sensitiviert wird, werden konfigurierbare Fehler mittels zusätzlicher Hardware, die ebenfalls in das FPGA konfiguriert ist, in die zu verifizierende Schaltung injiziert.

Im Rahmen dieser Arbeit schließe ich mittels neuer Emulationstechniken die Lücke zwischen Konfigurierbarkeit und Geschwindigkeit der FPGA-basierten Fehleremulation und ermögliche die Anwendbarkeit für industrielle Sicherheitskontroller. Die präsentierten Emulationstechniken erlauben es beliebige Fehler zu konfigurieren, was in dieser Form mit bisherigen Ansätzen entweder nicht möglich ist, oder aufgrund eines Kommunikationsflaschenhalses zu erheblichen Geschwindigkeitsverlusten führt.

Zuerst führe ich ein Meta-Fehlerkonfigurationsmodell ein, welches ich verwende, um die Konfigurationsmöglichkeiten der implementierten Fehlerinjektionstechniken eindeutig zu beschreiben. Das Meta-Fehlerkonfigurationsmodell ist auf einem abstrakten Meta-Level verallgemeinert beschrieben, sodass es unabhängig von den eingesetzten Modellierungswerkzeugen, der zu verifizierenden Schaltung und dem zur Verifikation betrachteten Abstraktionslevels der Schaltung ist. So lassen sich bekannte Fehlermodelle aus der Literatur sowie neue Fehlermodelle beschreiben und die Wiederverwendbarkeit für andere Applikationen ist sichergestellt.

Anschließend präsentiere ich eine FPGA-basierte Fehleremulationsumgebung, die die erforderliche Konfigurierbarkeit zur Modellierung beliebiger Fehlerattacken in kombinatorischer und sequentieller Logik bietet. Meine Implementierung unterstützt zur Laufzeit konfigurierbare Fehlermodelle sowie Einzel- und Mehrfachfehler mit einer variablen Injektionsdauer. Eine Fehlerkonfiguration kann einmal pro Fehlerexperiment zu beliebigen diskreten Zeitpunkten aktiviert werden. Ich präsentiere ein zusätzliches Feature, welches die Aktivierung verschiedener Fehlerkonfigurationen zu mehreren beliebigen diskreten Zeitpunkten während eines Fehlerexperiments ermöglicht. So lassen sich aufwändige Fehlerattacken konfigurieren, die zum Beispiel mit mehreren Laserstrahlen von unabhängigen Quellen zeitlich überlagert oder zeitversetzt durchgeführt werden können.

Des Weiteren schlage ich ein Konzept zur Evaluation der Emulationsergebnisse in Hardware vor. Für Prozessor-basierte Schaltungsdesigns wird dieser Ansatz durch die Verwendung eines selbsttenstenden funktionalen Tests unterstützt. Mit Hilfe einer einzigen fehlerfreien Emulation wird eine Referenz für alle folgende Fehleremulationen generiert, wodurch die Referenz nicht durch eine Duplikation des zu verifizierenden Designs generiert werden muss. Dieser Ansatz ist effizient hinsichtlich des benötigten Hardwareaufwands sowie der erzielten Geschwindigkeit. Beobachtungspunkte, an welchen die Emulation auf bestimmte Ereignisse sensitiv ist, erlauben eine flexiblere Bewertung des Verhaltens des zu verifizierenden Schaltungsdesigns, wodurch falsch-positive Emulationsergebnisse reduziert werden. Außerdem können Zeitpunkte für die Fehlerinjektion relativ zu dedizierten Ereignis-

sen an den definierten Beobachtungspunkten konfiguriert werden. Dadurch wird es ermöglicht, Zeitbereiche variabler Länge für die Fehlerinjektion zu berücksichtigen, in denen sicherheitsrelevante Operationen durchgeführt werden, ohne die absoluten Zeitpunkte manuell zu bestimmen.

Die zu verifizierenden Schaltungen können als synchrone sequentielle Schaltung realisiert sein, welche aus kombinatorischen und sequentiellen Gattern bestehen, wobei der Anteil an kombinatorischen Gattern üblicherweise wesentlich höher ist. Um die Modellierung beliebiger Fehler innerhalb eines Schaltungsdesigns zu unterstützen, muss jedes Gatter für eine Fehlerinjektion instrumentiert werden. Für jedes Gatter wird zusätzliche Logik zur Steuerung der Fehlerinjektion benötigt, wodurch der Hardwareaufwand zur Realisierung der Fehlerinjektion entsprechend der Anzahl an kombinatorischen und sequentiellen Gattern des zu verifizierenden Schaltungsdesigns steigt. Verglichen mit der FPGA-basierten Fehleremulation für Fehler in ausschließlich sequentieller Logik, wird daher für die Fehlerinjektion in ausschließlich kombinatorischer Logik mehr der verfügbaren Hardware des verwendeten FPGAs benötigt. Dies hat zur Konsequenz, dass die maximale Schaltungsgröße des zu verifizierenden Schaltungsdesigns kleiner ist, wenn die FPGA-basierte Fehleremulation für Fehler in kombinatorischer Logik realisiert wird. Um die daraus resultierende Limitierung der Anwendbarkeit der FPGA-basierten Fehleremulation für die Fehlerinjektion in kombinatorischer Logik zu beseitigen, präsentiere ich einen Software-basierten Präprozessor, welcher Fehler in kombinatorischer Logik auf äquivalente Fehler in sequentieller Logik abbildet, die dann performant mit dem Fehleremulator untersucht werden können. Dieser Ansatz bietet weitere Vorteile, da äquivalente Fehler bestimmt und zur Geschwindigkeitsoptimierung von weiteren Untersuchungen ausgeschlossen werden können.

Da mittels der präsentierten Fehleremulationstechniken meine Ziele hinsichtlich Konfigurierbarkeit und Anwendbarkeit erfüllt sind, widme ich mich als nächstes Geschwindigkeitsoptimierungen, um die Lücke zwischen Konfigurierbarkeit und Geschwindigkeit der FPGA-basierten Fehleremulation zu schließen. Ich präsentiere Optimierungen, die den Kommunikationsflaschenhals zwischen Soft- und Hardwarekomponenten der Fehleremulationsumgebung beseitigen, die Laufzeit für Fehlerexperimente reduzieren und Fehlerexperimente abbrechen, wenn diese Fehlereffekte zeigen, die bereits in vorhergehenden Experimenten beobachtet wurden.

Um die Verbesserung gegenüber dem Stand der Technik zu diskutieren, analysierte ich die Schaltungsdesigns zweier Sicherheitskontroller, für welche ich einige hundert Millionen verschiedener Fehlerattacken emulierte. Die Ergebnisse meiner Experimente zeigen, dass die präsentierten Fehleremulationstechniken, im Gegensatz zum Stand der Technik, die Modellierung be-

liebiger Fehlerattacken in kombinatorischer und sequentieller Logik industrieller Schaltungsdesigns unter Verwendung repräsentativer Tests und im Vergleich zu einer fehlerfreien Schaltungsemulation ohne Geschwindigkeitseinbußen ermöglichen. Für die Fehlerinjektion in kombinatorischer Logik konnte ich, verglichen mit bisherigen Ansätzen, den benötigten Hardwareaufwand um 45% reduzieren und die Laufzeit um den Faktor sechs reduzieren. Durch die Reduktion des Hardwareaufwands können größere Schaltungen verifiziert werden. Mit Hilfe der präsentierten Fehleremulationstechniken lassen sich beliebige Fehlerattacken im Rahmen der Sicherheitsverifikation während der Schaltungsentwicklung analysieren, wobei zusätzlich mehr Fehlerattacken in gegebener und üblicherweise limitierter Zeit modelliert werden können. Diese Arbeit trägt daher dazu bei, die Sicherheit integrierter Schaltungsentwicklung, also bevor die gefertigte Schaltung Post-Silizium zertifiziert wird, ausgeschlossen werden können.

### Acknowledgements

I thank my adviser Prof. Dr.-Ing. Georg Sigl for his supervision, support and patience over the past years. I would also like to thank my examiners Prof. Dr.-Ing. Ulf Schlichtmann and Prof. Dr.-Ing. Dirk Rabe for their support.

I am sincerely grateful to Prof. Dr.-Ing. Dirk Rabe, who initiated the HaVerI project in which I started my scientific work and who motivated me to pursue a doctorate.

I am particularly grateful to Prof. Dr.-Ing. Georg Sigl and Prof. Dr. Claudia Eckert for giving me the opportunity to continue my scientific work at Fraunhofer AISEC.

I would also like to thank my colleagues from Infineon Technologies AG, Fraunhofer AISEC, Technische Universität München and Hochschule Emden/Leer for collaboration on scientific and industrial projects as well as scientific exchange. My special thanks goes to Dietmar Heinz, Prof. Dr.-Ing. Gerd von Cölln and Dr.-Ing. Johann Heyszl for giving me opportunities, to Jürgen Nolles for his support, to Robert Hesselbarth for inspiring discussions in the final phase of writing my dissertation and to Robert Specht for proof-reading my dissertation.

SPONSORED BY THE

Parts of this work originate from the project *HaVerI* (*FKZ* 17N1509), which was funded by the German Federal Ministry of Education and Research.

# List of Figures

| 1.1 | Concept of fault injection techniques                                               |

|-----|-------------------------------------------------------------------------------------|

| 2.1 | Fault-error-failure chain                                                           |

| 3.1 | Detailed fault injection concept                                                    |

| 3.2 | Fault classification                                                                |

| 3.3 | Configuration possibilities of fault models                                         |

| 3.4 | Sensitization, propagation and observation                                          |

| 3.5 | Detailed fault classification                                                       |

| 5.1 | Concept of FPGA-based fault emulation 82                                            |

| 6.1 | The fault emulation environment                                                     |

| 6.2 | Finite state machine                                                                |

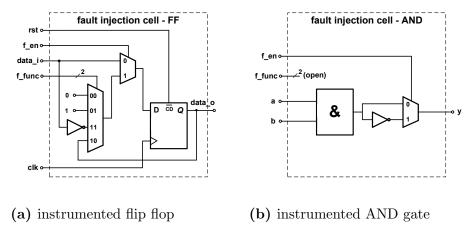

| 6.3 | Fault injection cells for flip flops and combinational cells 105                    |

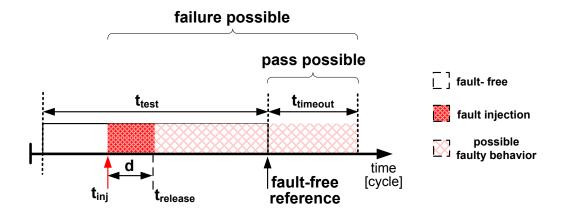

| 6.4 | Timing diagram for a particular fault experiment                                    |

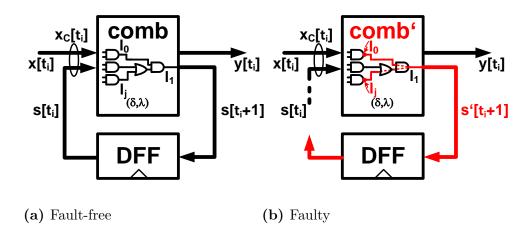

| 7.1 | Fault effect in sequential logic caused by a transient fault in combinational logic |

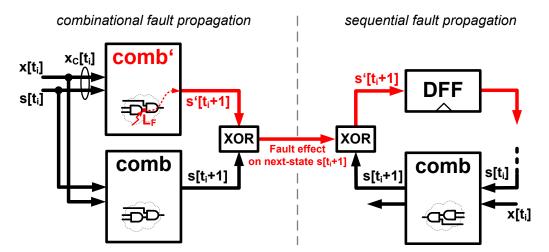

| 7.2 | Separating combinational and sequential fault propagation 130                       |

| 7.3 | Tool flow for enhanced combinational fault emulation 136                            |

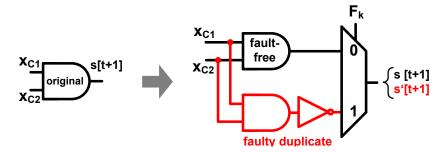

| 7.4 | Adding fault injection capability to an AND-gate                                    |

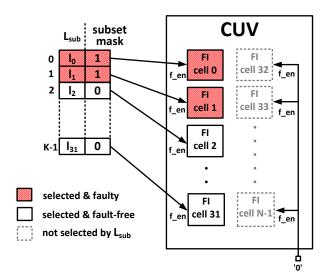

| 8.1 | Performance optimization: sub-selection of fault injection cells 147                |

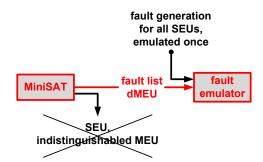

| 8.2 | Performance optimization: emulating distinguishable faults 150                      |

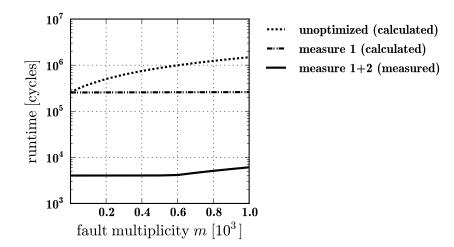

| 9.1 | Performance dependent on the spatial fault multiplicity 159                         |

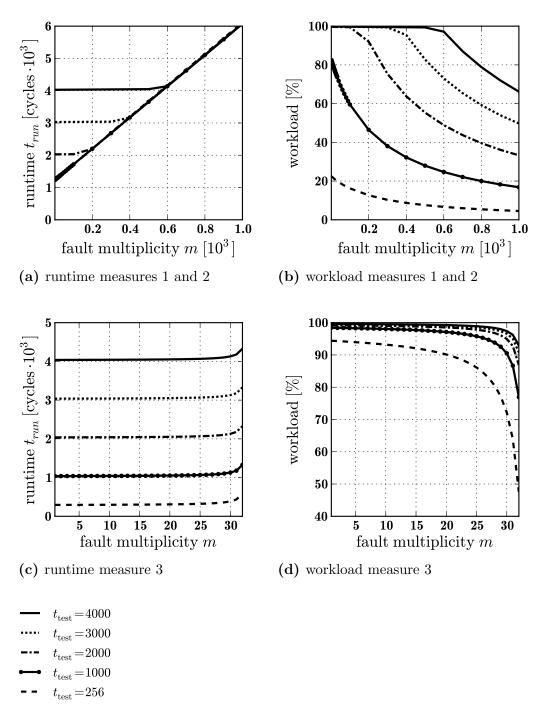

| 9.2 | Performance dependent on test duration and spatial fault mul-                       |

|     | tiplicity                                                                           |

# List of Tables

| 6.1 | Fault classification for security designs                    |

|-----|--------------------------------------------------------------|

| 9.1 | Hardware requirements of the fault emulation environment 158 |

| 9.2 | Fault propagation results                                    |

| 9.3 | Total runtime for fault injection campaigns 167              |

| 9.4 | Runtime for MiniSAT                                          |

# Contents

| A        | bstra  | net                                                       | i            |

|----------|--------|-----------------------------------------------------------|--------------|

| K        | urzfa  | assung                                                    | $\mathbf{v}$ |

| A        | ckno   | wledgements                                               | ix           |

| Li       | ist of | Figures                                                   | xi           |

| Li       | ist of | Tables                                                    | xiii         |

| 1        | Intr   | roduction                                                 | 1            |

|          | 1.1    | Problem Statement                                         | 4            |

|          | 1.2    | My Contribution                                           | 5            |

|          | 1.3    | Thesis Structure                                          | 6            |

| <b>2</b> | Att    | acks on Integrated Circuits                               | 11           |

|          | 2.1    | Taxonomy of Attacks                                       | 12           |

|          | 2.2    | Basics of Faults in Integrated Circuits                   | 13           |

|          |        | 2.2.1 A Historical Perspective                            | 13           |

|          |        | 2.2.2 Causality Relationship of Fault, Error and Failure  | 14           |

|          |        | 2.2.3 Persistence of Faults                               | 16           |

|          | 2.3    | Fault Attacks                                             | 18           |

|          |        | 2.3.1 Fault Analysis at Algorithm Level                   | 18           |

|          |        | 2.3.2 Methods for Physical Fault Injection                | 19           |

|          | 2.4    | Summary                                                   | 22           |

| 3        | Mo     | deling Fault Attacks during Security Verification of Faul | 5            |

|          | Cou    | ıntermeasures                                             | <b>23</b>    |

|          | 3.1    | Security Requirements and Countermeasures                 | 24           |

|          | 3.2    | Fault Injection Concept                                   | 26           |

|          | 3.3    | Abstracting Faults with Fault Models                      | 29           |

|          |        | 3.3.1 Abstraction Level of Fault Models                   | 30           |

xvi CONTENTS

|   |     | 3.3.2 Properties of Fault Models                         |

|---|-----|----------------------------------------------------------|

|   |     | 3.3.3 Fault Model Types                                  |

|   |     | 3.3.4 Transient Fault Models                             |

|   |     | 3.3.5 Permanent Fault Models                             |

|   |     | 3.3.6 Summary and Conclusion                             |

|   | 3.4 | Testing Concepts                                         |

|   |     | 3.4.1 Testability of Faults in Combinational Logic 3     |

|   |     | 3.4.2 Testing Concepts for Sequential Circuits           |

|   |     | 3.4.3 Tests and Test Generation                          |

|   | 3.5 | Propagation and Classification of Transient Faults 4     |

|   |     | 3.5.1 Masking Effects                                    |

|   |     | 3.5.2 Detailed Fault Classification 4                    |

|   | 3.6 | Pre-Silicon Fault Modeling Tools 4                       |

|   | 3.7 | Relevance for this Thesis                                |

|   | 3.6 |                                                          |

| 4 |     | Ta Fault Configuration Model                             |

|   | 4.1 | Fault Configuration Space                                |

|   |     | 4.1.1 Temporal Granularity                               |

|   |     | 4.1.2 Spatial Configuration Space                        |

|   |     | 4.1.3 Value Configuration Space                          |

|   |     | 4.1.4 Spatial-Value Configuration Space                  |

|   | 4.0 | 4.1.5 Total Configuration Space                          |

|   | 4.2 | Fault Multiplicities                                     |

|   |     | 4.2.1 Spatial Fault Multiplicity                         |

|   | 4.0 | 4.2.2 Temporal Fault Multiplicity                        |

|   | 4.3 | Practice-Oriented Interpretation                         |

|   |     | 4.3.1 Mapping Temporal Properties of Faults 6            |

|   |     | 4.3.2 Number of Fault Injection Times 6                  |

|   |     | 4.3.3 Permanent vs. Transient Faults 6                   |

|   |     | 4.3.4 Parametrized Fault                                 |

|   | 4.4 | Fault Injection Complexity                               |

|   |     | 4.4.1 Spatial Fault Injection Complexity 6               |

|   |     | 4.4.2 Spatial-Value Fault Injection Complexity           |

|   |     | 4.4.3 Total Fault Injection Complexity                   |

|   | 4.5 | Summary                                                  |

| 5 | Sta | te-of-the-Art of FPGA-based Fault Emulation 8            |

|   | 5.1 | Concept                                                  |

|   | 5.2 | Fault Injection Methodologies                            |

|   |     | 5.2.1 Partial FPGA-reconfiguration 8                     |

|   |     | 5.2.2 Mutant-based and Saboteur-based HDL Modification 8 |

| CONTENTS  | xvii    |

|-----------|---------|

| 001/1E/12 | 11 / 11 |

|   |     | 5.2.3 Circuit Instrumentation Technique                   | . 85  |

|---|-----|-----------------------------------------------------------|-------|

|   | 5.3 | Fault Generation and Upload                               |       |

|   | 5.4 | Test Generation, Upload and Execution                     |       |

|   |     | 5.4.1 Structural Test                                     |       |

|   |     | 5.4.2 Functional Test                                     | . 87  |

|   | 5.5 | Response Observation and Fault Classification             |       |

|   |     | 5.5.1 Comparison of Two Circuit Instances                 | . 89  |

|   |     | 5.5.2 Alternative Approaches                              |       |

|   |     | 5.5.3 Response Observation for Processor Designs          | . 90  |

|   | 5.6 | Summary and Discussion                                    | . 91  |

| 6 | Fau | lt Emulation Environment for Security Verification        | 95    |

| U | 6.1 | Fault Configuration Model at Gate Level                   |       |

|   | 0.1 | 6.1.1 Finite State Machine                                |       |

|   |     | 6.1.2 Fault Configuration Model at Gate Level             |       |

|   |     | 6.1.3 Multiple Transient and Multiple Permanent           | . 00  |

|   |     | Faults                                                    | . 101 |

|   |     | 6.1.4 Single Transient and Single Permanent Faults        |       |

|   | 6.2 | Hardware Implementation                                   |       |

|   |     | 6.2.1 Fault Injection Control Unit                        | . 104 |

|   |     | 6.2.2 Fault Injection Cells                               |       |

|   |     | 6.2.3 Concrete Fault Configuration Possibilities          |       |

|   | 6.3 | Circuit Instrumentation                                   |       |

|   | 6.4 | Fault Injection Campaign                                  | . 110 |

|   | 6.5 | Response Observation                                      | . 114 |

|   |     | 6.5.1 Using Adequate Observation Points                   | . 115 |

|   |     | 6.5.2 Determining the Fault-Free Reference                | . 116 |

|   |     | 6.5.3 Determining Fault Emulation Results                 | . 116 |

|   |     | 6.5.4 Observation of Processor Designs                    | . 117 |

|   |     | 6.5.5 Discussion of Advantages                            |       |

|   | 6.6 | Fault Classification for Security Designs                 | . 121 |

|   | 6.7 | Summary and Discussion                                    | . 122 |

| 7 | Enh | ancing Fault Injection in Combinational Logic             | 123   |

|   | 7.1 | Motivation                                                | . 124 |

|   | 7.2 | Related Work                                              | . 125 |

|   | 7.3 | A Pre-Processor for Combinational Faults                  | . 126 |

|   |     | 7.3.1 Fault Configuration Model for Combinational Cells . | . 127 |

|   |     | 7.3.2 Concept                                             |       |

|   |     | 7.3.3 Fault Equivalence                                   | . 130 |

|   |     | 7.3.4 Implementation                                      | . 134 |

xviii CONTENTS

|    | 7.4                                                        | Summary and Discussion                                  | 137 |  |  |

|----|------------------------------------------------------------|---------------------------------------------------------|-----|--|--|

| 8  | Performance Optimizations and a Feature for Multiple Fault |                                                         |     |  |  |

|    | Inje                                                       | ection Times                                            | 139 |  |  |

|    | 8.1                                                        | Performance Benchmarks                                  | 140 |  |  |

|    | 8.2                                                        | Fighting the Communication Bottleneck                   | 141 |  |  |

|    |                                                            | 8.2.1 Configuration Data Overhead Reduction             | 142 |  |  |

|    |                                                            | 8.2.2 Parallelizing Fault Experiments and Configuration |     |  |  |

|    |                                                            | Upload                                                  | 143 |  |  |

|    |                                                            | 8.2.3 Sub-Selection of Fault Injection Cells            | 144 |  |  |

|    |                                                            | 8.2.4 Summary                                           |     |  |  |

|    | 8.3                                                        | Reducing Emulation Runtime                              |     |  |  |

|    |                                                            | 8.3.1 Shorten Fault Experiments                         |     |  |  |

|    |                                                            | 8.3.2 Skipping Equivalent Fault Experiments             |     |  |  |

|    | 8.4                                                        | Multiple Fault Injection Times                          |     |  |  |

|    | 8.5                                                        | Summary and Discussion                                  |     |  |  |

| 9  | Exp                                                        | perimental Results                                      | 155 |  |  |

|    | 9.1                                                        | Verified Security Controllers                           | 156 |  |  |

|    | 9.2                                                        | Fault Injection in Sequential Logic                     |     |  |  |

|    | 9.3                                                        | Fault Injection in Combinational and Sequential Logic   |     |  |  |

|    |                                                            | 9.3.1 Combinational Fault Propagation Results           |     |  |  |

|    |                                                            | 9.3.2 Applicability for Industrial Circuits             |     |  |  |

|    |                                                            | 9.3.3 Performance                                       |     |  |  |

|    | 9.4                                                        | Summary and Conclusions                                 |     |  |  |

| 10 | Con                                                        | nclusions                                               | 173 |  |  |

| Bi | bliog                                                      | graphy                                                  | 177 |  |  |

## Chapter 1

### Introduction

Connected electronic devices are essential in our daily routines. To name just a few examples, we use smart phones, laptops and personal computers for checking daily news, writing emails or messages and managing the appointments of the upcoming day. Our favorite TV series are provided by streaming video on demand services, for which also TVs and Blue-Ray players are connected. Nowadays, we expect getting access to the Internet with our smart phones in public networks from, e.g., cafés and public transportation. The number of sold smart phones in 2016 is about 1,5 billion [Gar17b], which clearly indicates the strong impact of these devices on our daily live.

Hot topics in the information technology related research domains are today Internet of Things, 'Industrie 4.0', autonomous cars, smart homes and smart grid. In these emerging areas many different devices and machines are connected to exchange information, building a system that provides a service. In contrast to the listed devices above used by human beings to communicate or to enjoy media and multimedia, the incorporated devices work autonomously, i.e. without interaction with human beings. This is the reason for a heavy increase of connected devices in the last decade, which will still drive the market in the next decade. In 2015, the analysts of Gartner, Inc. [Gar15] predicted that 6.4 billion connected devices would be in use worldwide by end of 2016. These numbers are confirmed now and 8.4 billion connected devices are predicted to be in use by end of 2017 [Gar17a]. This corresponds to an increase of about 30 percent each year. Correspondingly 20.4 billion connected devices are expected in 2020 [Gar17a]. This tremendous amount of devices introduces huge potentials for adversaries to perform on-line attacks, exploited to break into systems and networks in order to violate privacy, confidentiality and integrity. In case of online attacks, the victim may realize that he is being attacked, enabling him to possibly counteract this threat before an adversary may cause any damage. Even more powerful are therefore off-line attacks, where attacks are repeated on isolated devices until its success without anyone noticing it. Successful attacks can then be replayed as on-line attacks, which increases the probability to compromise a system before respective attacks are detected by the victim. For example, secret information such as cryptographic keys and passwords can be extracted off-line, which then can be exploited to compromise systems by means of accessing their secured interfaces or breaking secured communication channels.

Systems are not appropriately secure by simply using encryption to protect sensible data. Even if the utilized encryption algorithm is theoretically secure, the hardware or software implementation of the cryptographic algorithm itself may introduce leakage of information about the processed secrets due to for example varying execution time, power consumption or electromagnetic emission of a circuit (also known as side channels). Basically, performing repeated passive measurements of these side channels a processed cryptographic key could be extracted. There is another class of attacks that exploits deliberately injecting faults into a system, where the fault may cause a malfunction or service failure, i.e. the circuit behavior deviates from the circuit's specification. This way, very critical behavior can be caused, e.g., disturbing the system such that its availability is violated, which would be critical in numerous safety applications. Especially critical for security applications would be to exploit faults to circumvent specific checks on, e.g., passwords to cause buffer overflows or to disrupt a cryptographic algorithm such that it outputs the processed key instead of the ciphertext.

Consequently, various attacks possibly mounted on systems and devices need to be considered when designing security circuits and security systems. Therefore, to protect sensitive data in terms of confidentiality as well as integrity and to enable secured authentication, it is not sufficient to rely solely on deploying cryptographic primitives. In addition, appropriate countermeasures need to be deployed that counteract passive side-channel attacks and active fault attacks. Basically, fault countermeasures introduce redundancy in hardware or software that enables to detect corrupted behavior caused by fault attacks and then actively prevents that an attack can be exploited. This is the purpose of security circuits, which include relatively complex processorbased circuits such as so-called secure elements, trusted platform modules (TPM), hardware security modules (HSM) and smart cards. These allow secured key storage, allow to perform cryptographic operations in untrusted environments and provide secured code execution, used to protect sensitive data and its integrity and to realize secured authentication. For this purpose, security circuits deploy cryptographic peripherals such as hardware accelerators for cryptographic algorithms and random number generators. These

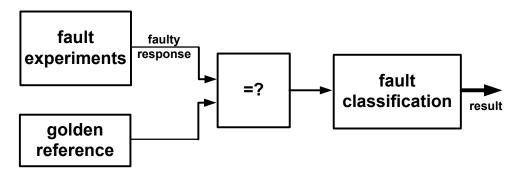

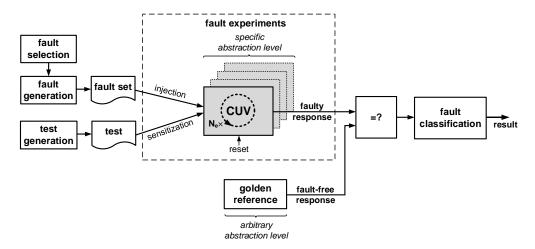

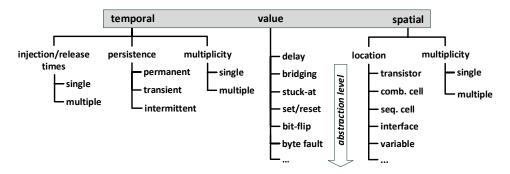

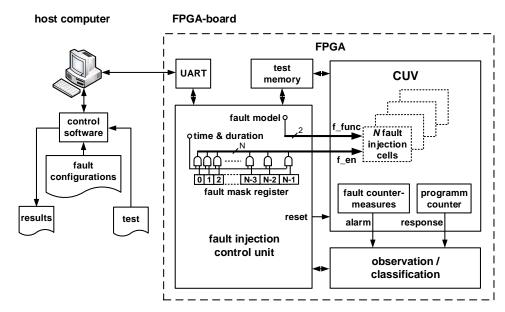

Figure 1.1: Concept of fault injection techniques.

are implemented and integrated into circuits in a secure way, for which it is necessary to deploy additional countermeasures dedicated to specific passive and active attacks. To create a secured system, any incorporated securitycritical device that is accessible to adversaries need to be designed in a secure way.

In this thesis the focus is on security verification, particularly on verification of the effectiveness of countermeasures that are dedicated to active fault attacks. In order to check the effectiveness of fault countermeasures, security verification is required to be performed in addition to common functional verification. Since fault countermeasures are only supposed to take any action in presence of faults, various fault attacks need to be mimicked during security verification by means of performing a huge number of fault experiments, during which faults with varying spatial and temporal properties are injected into the circuit under verification.

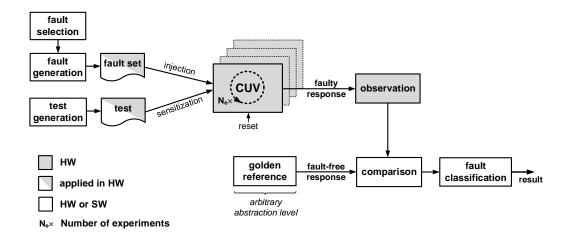

Figure 1.1 depicts the basic concept of fault injection techniques, which I am going to apply to security designs in this thesis. During fault experiments, the circuit to be verified needs to be sensitized by appropriate tests, i.e. input pattern or, in case of processor-based architectures, test software. The purpose is to represent relevant situations such as performing encryption and decryption using a cryptographic algorithm implemented in hardware or software, while attacks are being mimicked. In case of processor designs, usually relative extensive tests lasting thousands of clock cycles are applied since deployed software-based countermeasures need to be considered as well. Due to the fault injection, the circuit may output a faulty response, which is compared to the fault-free response generated by the golden reference. If a critical malfunction is observed that is not detected by fault countermeasures, faults are classified as critical. These are the cases of interest, which suit as starting point for further investigation with the goal to track the issue.

Important to note is that fault injection can be applied to any level of abstraction of the circuit under verification. This includes pre-silicon techniques that are already applicable during circuit design and post-silicon physical fault injection into the physical device. As for design bugs, it is important that vulnerabilities and security leaks are identified as early as possible during circuit design in order to save design costs and reduce time-to-market. Thus, pre-silicon fault injection tools are required that are applicable during circuit design.

#### 1.1 Problem Statement

Unfortunately, there is only a limited time frame for security verification during circuit design. Furthermore, due to the complexity of the verified circuits and applied tests and also due to the complexity of the fault injection space, it is impossible to consider all possible configurations for fault injection. In fact, only a very small subset of the total fault injection space can be considered within the given time frame for security verification. This motivates high speed tools for fault injection that are also required to provide the configurability required to mimic arbitrary fault attacks. Moreover, these tools are required to be applicable to relatively complex circuits and are required to handle extensive tests.

Pre-silicon fault injection tools based on software implementations including statistical, analytical, probabilistic and symbolic techniques as well as simulation-based, emulation-based and hardware-based (e.g. development boards) implementations are reported in literature (detailed in Section 3.6). All fault injection tools have application specific merits and strength. From these I choose the FPGA-based fault emulation technique, particularly the circuit instrumentation technique, which alters the design during security verification to add fault injection capability. The instrumented design is then synthesized into an FPGA. Additional software components are added to configure and control fault emulation. The biggest advantage over all other approaches is that FPGA-based fault emulation is the fastest method to perform fault propagation in a circuit after fault injection. Contrarily to post-silicon physical fault injection techniques, for which the circuit needs to be already manufactured, this technique can be applied early during circuit design. The performance of fault emulation is linear with the duration of the test that sensitizes the circuit under verification. Therefore, fault emulation provides high speed even for extensive tests, whereas software-based and simulation-based approaches would struggle.

Of course, fault emulation comes with some disadvantages. Compared

to software-based and simulation-based approaches, fault emulation is considered to provide less configurability and less observability. These two disadvantages have a considerable impact on applicability of fault emulation during security verification. High configurability is a requirement to mimic arbitrary fault attacks. So far, higher configurability comes with considerably reduced performance because of a communication bottleneck between controlling software components and hardware components. Observability is important to reliably identify vulnerabilities of security designs. For this purpose, not only the functional behavior of the circuit under verification needs to be checked, but also the effectiveness of deployed fault countermeasures, which is especially challenging when processor designs with limited top level interfaces are verified. Another drawback of FPGA-based emulation is that hardware resources available on FPGAs are limited. For mimicking arbitrary fault attacks fault injection capability needs to be added to every incorporated cell, for which additional logic is required. This limits the size of the circuit under verification (CUV), and therefore, applicability especially when considering fault injection in combinational cells.

### 1.2 My Contribution

The goal of this thesis is to eliminate the discussed disadvantages of FPGA-based fault emulation. I maximize the configurability for mimicking arbitrary fault attacks while the performance is maximized at the same time, which allows to benefit as much as possible from limited verification times. I decrease the hardware requirements for fault injection in combinational logic, and thus, increase the applicability in general. I increase observability for security controllers by introducing concepts for reliable response observation and fault classification, which at the same time save hardware and runtime overhead. In particular, I contribute the following improvements to the state-of-the-art, some of which have been partly or fully published in [NR11, NHN+14, NHRS15, NHS15, NHHS16]:

- I present an FPGA-based fault emulation environment that allows to configure arbitrary permanent and transient multiple faults at runtime without requiring to re-synthesize the fault emulator. This is a requirement for mimicking arbitrary fault attacks.

- I present a feature for fault emulation that allows to configure multiple fault injection times, where for every clock cycle of a test an arbitrary multiple fault can be injected without limitations. This feature completes fault configurability in sequential logic of FPGA-based fault

- emulation, for which I also propose a very hardware-efficient implementation (not published yet).

- I close the gap between speed and configurability of fault emulation environments by introducing performance optimization measures aiming on fighting the communication bottleneck between software and hardware components. These allow to support the high configurability requirements without performance loss compared to fault-free test runs.

- I propose additional performance optimization measures that aim on reducing the time required for fault experiments and skipping equivalent fault experiments entirely (not published yet).

- I present a generic concept for reliable response observation and fault classification, which is supported by software-based self-tests in case that the circuit under verification is a processor-based architecture. The proposed concept reduces false positives in emulation results, allows to monitor the state of the circuit under verification and supports defining test-related events used to control fault emulation. Thus, observability, controllability and applicability is improved.

- I introduce a new method enhancing fault injection in combinational logic by extending FPGA-based fault emulation by a software-based pre-processing that maps faults from combinational logic to equivalent faults in sequential logic. This method benefits from the high performance that FPGA-based fault emulation provides while limitations of conventional approaches with respect to applicability and performance are eliminated. Further performance optimizations based on skipping equivalent fault experiments are proposed for this method.

- I propose a meta fault configuration model that allows to describe all configuration possibilities required to mimic arbitrary fault attacks independently of the targeted circuit under verification, specific levels of abstraction and the technique used for fault injection. I use it to derive fault models for the considered level of abstraction to provide formal descriptions for all presented techniques and implementations.

#### 1.3 Thesis Structure

Next, in Chapter 2, I present the background to this thesis by means of reviewing the existing work related to physical fault effects, physical attacks and physical fault injection techniques.

In Chapter 3, I briefly outline security requirements and fault countermeasures and introduce fault injection concepts. Then I discuss along with the related work how physical faults are modeled using fault models and I review testability of faults and propagation of transient faults. My intention is to impart the basics of fault modeling, which is used to abstract complex physical behavior, and to impart that fault behavior depends on the sensitizing test. Finally, I review appropriate fault injection tools, where the focus lies on discussing the respective advantages and disadvantages in order to argue my decision to choose FPGA-based fault emulation for modeling fault attacks during security verification.

In Chapter 4 my goal is to create a comprehensive understanding of all possibilities for configuring fault properties during fault injection. Since fault modeling can be applied to any level of abstraction of a circuit under verification, I decided to formulate a fault configuration model at a meta level. It is based on a fault configuration space that covers all configuration possibilities independently of the targeted circuit under verification and its considered level of abstraction. It is independent of specific fault injection tools and techniques as well. This way, the proposed model constitutes a superset of specific fault models known from literature. This formal description is used to derive a fault configuration model at gate level later in Chapter 6, based on which formal descriptions of following concepts and implementations are provided. Moreover, I discuss in the context of the meta fault configuration model terms that are commonly used to describe properties of faults, fault models and fault experiments. I focus on terms that allow to describe specific practice-oriented subsets of the fault configuration space. Finally, equations are derived that allow to determine the complexity of the formulated fault injection space for practice-oriented subsets.

I decided to review the state-of-the-art of FPGA-based fault emulation in an own dedicated chapter, presented in Chapter 5. There I focus on how fault emulation realizes the concepts of fault injection and detail respective methodologies for fault injection, fault generation, test generation and response observation. I also discuss possibilities to implement components of fault emulation environments either in software or hardware, where I focus on respective advantages and disadvantages, based on which I make my design decisions.

Then, in Chapter 6, I present my hardware implementation for FPGA-based fault emulation that I have chosen to maximize configurability. My implementation provides configurability at runtime for arbitrary permanent and transient faults including single and multiple faults, at runtime configurable fault duration and at runtime configurable fault model types. After

this, the hardware implementation is embedded into a fault emulation environment, which adds software components to complete the concepts and methodologies of FPGA-based fault emulation discussed earlier when reviewing the state-of-the-art. To provide formal descriptions for the presented techniques and implementations, I apply the meta fault configuration model to gate level by means of refining its properties accordingly. Finally, I present advanced concepts for response observation and fault classification that suits security designs. These concepts are supported by software-based self-tests in case that the circuit under verification is a processor-based design.

Chapter 7 is dedicated to fault injection in combinational logic. There, I detail limitations w.r.t. applicability and performance that are encountered when using FPGA-based fault emulation for fault injection in combinational logic. In order to eliminate these limitations, I present a concept as well as an implementation that extends fault emulation by a software-based preprocessor for fault injection and fault propagation in combinational logic. Basically, I separate combinational and sequential fault propagation, where combinational fault propagation is performed in software in order to determine an equivalent fault in sequential logic. Then, the fault emulator presented earlier is used for further sequential fault propagation by means of injecting the determined equivalent fault into sequential logic. The concept is supported by reviewing the literature related to state equivalence and fault equivalence, based on which I derive the relation of equivalent transient faults.

In Chapter 8, I close the gap between speed and configurability of fault emulation environments by means of introducing performance optimization measures. These allow to reach optimal performance while supporting the ability to configure arbitrary faults at runtime. The presented performance optimization measures aim on fighting the communication bottleneck between software and hardware components of the fault emulation environment. Moreover concepts for shortening fault experiments and skipping equivalent fault experiments are proposed. Then, I propose a feature for enabling multiple fault injection times. This feature enables to configure any fault defined in the fault configuration space of the meta fault configuration model.

In Chapter 9, I provide experimental results for fault injection campaigns. First, I concentrate on fault injection in sequential logic to analyze the proposed performance optimizations for fighting the communication bottleneck of fault emulation environments. After this, I present results for fault injection in combinational and sequential logic. There, I focus on fault propagation results to discuss the efficiency and effectiveness of the performance optimizations proposed for the software-based pre-processing for enhancing fault injection in combinational logic. Then, I discuss respective performance

9

results and provide a comparison to the state-of-the-art. I am able to show that the proposed techniques provide a highly configurable and fast tool to perform fault injection in both combinational and sequential logic, which suits the purpose of security verification. Moreover, the presented techniques remove the limitations of state-of-the-art approaches w.r.t. speed, configurability, observability and applicability.

Finally, Chapter 10, summarizes and concludes this thesis.

# Chapter 2

# **Attacks on Integrated Circuits**

In the last decades, many efforts have been made on studying the reasons for fault occurrences, their impact on circuit behavior and modeling fault behavior. A lot of studies were motivated by manufacturing and quality testing whose goal is to find efficient tests, mainly used to detect permanent defects in integrated circuits. Advances in circuit design and semiconductor processes result in shrinking technology nodes and increasing operating frequencies. This leads to more frequent occurrence of transient faults and increases their impact on circuit behavior. As a consequence, reliability engineering emerged, who pushed research in the direction of transient faults with the goal of hardening circuits against random fault occurrences during in field operation. Nowadays, reliability engineering is considered to be an important design parameter in addition to the conventional power-area-performance trade-off, not only for application in very harsh environments like outer space and safety-critical application domains (e.g. automotive and avionics), but also for consumer products.

This work is dedicated to security engineering, which is another important application domain that is concerned with faults. In a security context, not only random fault occurrences have to be considered and countered by e.g. error detection and correction codes. Additionally, deliberately injected faults aiming on compromising security applications during in field operation, so called fault attacks, are one of the major concerns for concept, design and verification engineers of security circuits. Therefore, fault countermeasures dedicated to specific fault attacks are deployed, which need to be verified during circuit design.

Next, I outline the taxonomy of attacks on integrated circuits in Section 2.1 to define fault attacks, which is the class of attacks to which this thesis is dedicated. In order to draw a comprehensive picture, I briefly sketch the historical context on faults in integrated circuits in Section 2.2.1. In this

thesis, I make use of definitions and techniques that are mostly originated from application domains that are not dedicated to the security context, e.g. manufacturing testing and reliability engineering. I therefore discuss in the remainder of Section 2.2 fault effects in integrated circuits along with the related work from a general point of view and introduce related definitions. Various physical fault injection techniques that have been successfully exploited for fault attacks to break cryptographic algorithms as well as their respective physical effects are reviewed in Section 2.3.

In Chapter 3, I bridge the gap to fault countermeasures and fault injection concepts, including common fault models, testing concepts and fault classification. Additionally, I review pre-silicon methods capable of fault modeling.

### 2.1 Taxonomy of Attacks

Attackers try to compromise security circuits and cryptographic algorithms by means of conducting attacks in order to reveal secrets. In general, attacks are divided into active and passive attacks, as defined in [Shi00] and discussed by Skorobogatov et al. [Sko05] and Mangard et al. [MOP07].

Passive Attacks Passive attacks observe physical properties (side channels) of a circuit such as operating temperature, power consumption or execution time while the circuit is operated in its specification. In literature, these attacks are also referred to as side-channel attacks.

Active Attacks Active attacks manipulate a circuit or disrupt its function in order to prompt an abnormal circuit behavior that does not comply with the circuit's specification (service failure). For this, the circuit itself can be altered, an extra amount of energy can be induced or environmental and operating conditions that do not comply with the circuit's specification can be exploited. Injecting faults deliberately, also known as fault attack in literature, belongs to the class of active attacks.

Skorobogatov et al. [Sko05] and Mangard et al. [MOP07] subdivide passive and active attacks further into invasive, semi-invasive and non-invasive attacks, which indicates whether and how much a circuit is altered for conducting an attack. Although I focus on active attacks (fault attacks) in this thesis, the following description will also consult definitions for passive (side-channel) attacks.

Invasive Attacks Invasive attacks depackage a circuit to expose the die by grinding or by using laser cutters or acid in order to apply further modifications. For example, focused ion beam (FIB) and probing stations are often used to contact internal signals. According to Mangard et al., using probing to observe internal signals is a passive attack, whereas changing internal signals with this setup is an active attack.

Semi-invasive Attacks Semi-invasive attacks only depackage a circuit to expose the die but do not modify the die itself. This is required to conduct active attacks using e.g. a laser or light as well as optical passive side-channel attacks. It also improves precision of active attacks that use radiation sources (alpha particles, electromagnetic interference, etc.) and passive electromagnetic side-channel attacks, since the radiation source or probe can be put closer to the surface.

Non-invasive Attacks Non-invasive attacks do not alter a circuit and are conducted by exploiting directly accessible interfaces, environmental and operating conditions, radiation sources or side channels. Active non-invasive attacks can be induced by clock glitches (clock signal variation), power supply glitches (supply voltage variation), temperature variation of the environment and radiation sources such as alpha-particle and electromagnetic interference. Passive non-invasive attacks include timing, power, temperature, photonic and electromagnetic side-channel attacks.

### 2.2 Basics of Faults in Integrated Circuits

In this section I start with the historical background on faults in integrated circuits (IC). Then I give definitions related to faults, errors, failures and testing for faults, after which I bridge the gap to physical fault attacks.

### 2.2.1 A Historical Perspective

Faults in digital integrated circuits may occur because of different phenomena. For instance, manufacturing defects resulting from defective fabrication and process variation is one cause of fault occurrences. Rejecting defective devices to prevent that these are shipped to customers opened the oldest research area concerning faults, manufacturing testing, which includes disciplines such as test generation and fault simulation. In these research fields, relevant faults are usually assumed to be permanently present in circuits.

However, back in the 70's faults were discovered that exhibit transient characteristics. The relevant historical facts outlined in the following paragraph are inline with the book Soft Errors in Modern Electronic Systems [Nic10].

In 1975, Binder et al. [BSH75] reported on anomalies in space applications that triggered flip-flops. These effects were observed about one time in four years and were not caused by manufacturing defects. These could not be explained by known effects such as solar wind either. Instead, Binder et al. concluded that cosmic ray particles with high atomic numbers and high energy produce dense ionization tracks of electron-hole pairs, which charges base-emitter capacitance of transistors. In 1978, May and Woods [May78] reported that soft-errors also occur at sea-level. These were caused by alphaparticle hits emitted from radioactive decay of uranium and thorium used in package materials. May and Wood also introduced the term soft-error as random, nonrecurring single-bit error. In the same year, Ziegler suggested that cosmic radiation possibly may also cause soft-errors. In the 1990s, when package materials with low emission rates were already used, and therefore, could not be the reason for soft-errors, it was found that cosmic neutrons pose the main source for soft-errors [Zie96].

Nowadays, it is known that many sources are capable of inducing enough energy to cause a transient abnormal circuit behavior. These include, radiation sources, high-energetic particle hits and electromagnetic interaction, as will be detailed along with the literature in following sections. Because of shrinking technology nodes and growing device count per chip, particle hits occur more frequently [Bau05, MM07]. First studies focused on fault effects on sequential cells. However, reduction in operating voltage and increasing operating frequencies increase the probability that particle hits in combinational logic result in errors [Bau05, MM07]. As a consequence, the impact of faults in combinational logic could not be neglected anymore. Moreover, because of further advances in circuit design and manufacturing technologies, particle hits causing multiple faults are more likely to occur and it became important to study also these effects [MZM10].

# 2.2.2 Causality Relationship of Fault, Error and Failure

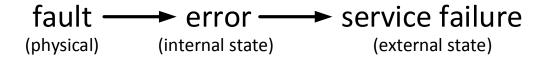

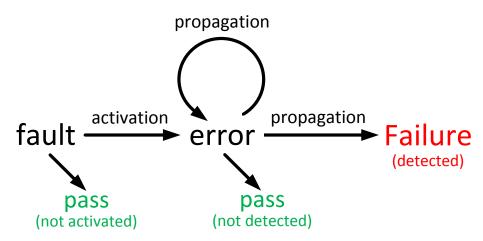

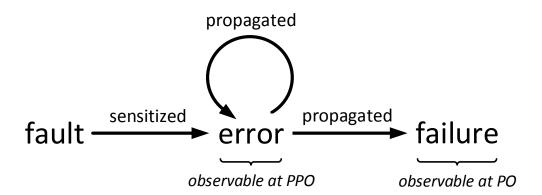

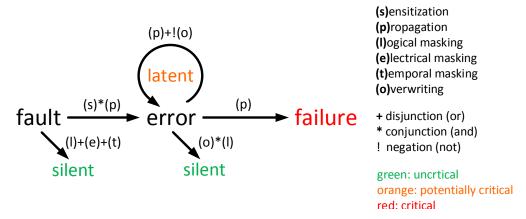

A fault has the potential to manifest as an error in an internal state of a system, which in turn may cause a service failure observable as corrupted external state, as discussed e.g. by Clark et al. [CP95] and later refined by Avizienis et al. [ALR01, ALRL04]. This causality relationship is often referred to as fault-error-failure chain [ALR01], which is depicted in Figure 2.1.

**Figure 2.1:** Fault-error-failure chain, illustrating the causality relationship of fault, error and failure.

The terms fault, error and failure are defined referring to the literature as follows:

**Fault** A fault is a physical defect, imperfection, flaw or abnormal event. Faults can occur in hardware or software at any level of abstraction and during the entire life cycle of a system [ALRL04] ranging from specification and design over manufacturing to in field operation.

In this thesis, I focus on modeling hardware faults and I use the term fault for abnormal circuit behavior caused by a physical effect or fault injection. The exhibited behavior of a hardware fault depends on its cause, the affected area and its temporal properties timing of occurrence, timing of dormancy relative to input or software execution, from which follows the fault duration.

**Error** An error is the deviation of correct and incorrect internal system states. Faults that manifest in at least one memory element result in an erroneous internal state, and hence, implicate an error [ALRL04].

In the literature, the two terms hard-error and soft-error commonly refer to permanent and transient errors, respectively. The term soft-error was originated by May et al. [May78] to described fault effects in dynamic memory cells.

Failure The term failure is often used as abbreviation of service failure and refers to the deviation of delivered incorrect service from correct service [ALRL04]. A system's service corresponds to the system's external state, i.e. the system's output, which is generated by a sequence of the system's internal states. Therefore, a service failure is the implication of at least one erroneous internal system state [ALRL04].

Note that, in a security context, a service failure occurs when assets or secrets such as sensible data or cryptographic keys are exposed to adversaries. This happens, for example, when fault countermeasures supposed to detect specific attacks in order to protect the defined assets and secrets actually fail. Fault attacks and countermeasures are further detailed in Sections 2.3 and 3.1.

**Soft-Error-Rate (SER)** In the domain of reliability engineering the Soft-Error-Rate (SER) is an important measurement for quantifying the vulnerability to random fault occurrence. It expresses the frequency of random soft error occurrence caused by e.g. particle hits [PHRB11], given in failure in time (FIT), which is the number of failures that can be expected in one billion device hours of operation.

#### 2.2.3 Persistence of Faults

Based on the duration faults exhibit, Clark et al. [CP95] divide faults into permanent, intermittent and transient faults. Avizienis et al. [ALR01, ALRL04] suggest to use the term persistence as hypernym for these properties.

Permanent Faults Permanent faults are irreversible device defects, which are permanently effective and are caused by e.g. damage (mechanical, overvoltage, etc.), fatigue or incorrect manufacture [CP95]. Permanent faults can be further subdivided into static and dynamic faults. Static faults include electrical shorts (stuck) to power supply. The fault behavior of static faults is independent of the operating clock frequency. Dynamic faults include delay faults, which are only effective with frequencies above a specific value.

Intermittent Faults Intermittent faults in integrated circuits are irreversible device defects which tend to oscillate between periods of erroneous activity and dormancy [CP95], i.e. these are temporarily present and a non-deterministic appearance is typical. Intermittent faults can be caused by e.g. erroneous design [CP95], irregular physical structure of components, critical circuit timing, stray capacitances, aging, fatigue, noise, loose connections [KP74], electromigration [KE15] and tunneling effects [Con03]. Faults often exhibit an intermittent characteristic before they turn into a permanent fault, caused by, e.g., a permanent oxide breakdown [Con03].

**Transient Faults** Transient faults are caused by reversible single or multiple event effects (SEE, MEE). These occur infrequently and temporarily when either an extra amount of energy is added into a circuit or when its environmental or operating condition are varied in a range that does not comply with the circuit's specification. Transient faults cause an abnormal

electrical behavior for a relatively short period of time (e.g. induced voltage pulse) and usually do not damage a circuit. Note, in rare cases when the energy is high enough, it may result in a latchup or burnout. Both latchups and burnouts may cause permanent damage [Bau05], i.e. single event effects may also result in permanent faults or permanent errors.

Sources for transient faults include radiation such as neutrons [Zie96, KHP04], alpha particles [May78, KHP04] and electromagnetic interaction [QS02, MLB+14]. Furthermore, environmental and operating conditions capable to influence electronic properties temporarily, e.g. variation of temperature [Sko09, KJP14], operating frequency [FT09] and operating voltage [ABH+02] may cause transient faults. The caused abnormal faulty behavior depends on the affected area (spatial property) and, in contrast to permanent faults, especially on the induced energy, the circuit's current state as well as the timing and duration of fault occurrence relative to the circuit's input or software execution (temporal properties). A very comprehensive work on transient fault effects is presented by Karnik et al. [KHP04].

Different terms are used in literature to describe transient fault effects based on single and multiple event effects, to distinguish between single and multiple fault occurrences and to distinguish whether combinational or sequential cells are affected. Unfortunately, theses terms are sometimes used inconsistently and interchangeable [PHRB11] in an ambiguous way. Moreover, these terms are used to name the physical fault effects, but are also used as synonym for related fault models. This makes it difficult to clearly distinguish between the actual physical effect and the describing fault model.

The following terms are used hereinafter to describe modeled transient fault effects.

- Single Event Upset (SEU) where a single transient fault is present in a sequential cell (single upset).

- Multiple Event Upset (MEU) where multiple transient faults are present in sequential cells (multiple upsets).

- Single Event Transient (SET) where a single transient fault is present in a combinational cell (single transient).

- Multiple Event Transient (MET) where multiple transient faults are present in combinational cells (multiple transients).

In the literature, the following synonyms are sometimes used. Multiple Cell Upset (MCU) or Multiple Bit Upset (MBU) are typically used as synonym for MEU, where MBU is then usually used to describe the case that multiple faults affect the same word. Single Bit Upset (SBU) is sometimes

used as synonym for SEU. SEU is often used as synonym for soft-errors in general and sometimes referred to as the superset of SBU, MCU, and MBU.

To distinguish between single and multiple event effects, sometimes terms were introduced that emphasize on that matter. For example, Kiddie et al. [KRL15] recently denoted fault effects stemming from single and multiple event effects as Single Event Single Transient (SEST) and Single Event Multiple Transient (SEMT), respectively. In contrast, Miskov-Zivanov et al. [MZM10] use the terms Single Event Multiple Transient Fault (SE-MTF) and Multiple Event Multiple Transient Fault (ME-MTF). In order to keep the nomenclature compact, I relinquish to distinguish between single and multiple event effects for the reminder of this work.

### 2.3 Fault Attacks

The objective of this work is modeling fault attacks using emulation techniques. Next, an introduction to fault analysis at algorithm level and methods for physical fault injection are given. I focus on techniques that have been successfully mounted at circuit level to break cryptographic algorithms.

## 2.3.1 Fault Analysis at Algorithm Level

Incorrect ciphertexts or signatures produced by a disturbed cryptographic algorithm in response to a fault attack may already pose a huge security weakness, which can be analyzed at algorithm level. By analyzing the deviation of correct and incorrect ciphertexts, for which Biham et al. [BS97] introduced the term differential fault analysis (DFA), a cryptographic key can be extracted. Boneh et al. [BDL97] were the first to present a theoretical model for exploiting fault attacks and were able to break a public-key cryptographic algorithm, namely Rivest Shamir Adleman (RSA). Similar attacks were deployed to private-key cryptographic algorithms. Biham et al. [BS97] deployed it to the Data Encryption Algorithm (DES), Biehl et al. [BMM00] to elliptic curves and Girau, Dusart et al., Blömer et al. and Piret et al. [Gir03, DLV03, BS03, PQ03] deployed it to the Advanced Encryption Standard (AES).

The above listed publications provide theoretical aspects of differential fault analysis, where the presence of faults is only assumed during the execution of cryptographic algorithms. To actually mount a successful fault attack onto a physical device, this fault needs to be injected into the physical device and information about the used secret is obtained from a corrupted output. In-depth knowledge about the theoretical background on differential fault

analysis helps to select the timing and location for an attack mounted on the physical device, i.e. at circuit level. Subsequently, methods for physical fault injection and related practical setups are discussed.

### 2.3.2 Methods for Physical Fault Injection

Note, methods for physical fault injection discussed in the remainder of this section are also used for post-silicon verification of security circuits.

Physical fault attacks are active attacks mounted at circuit level to prompt a fault in the circuit. The underlying physical effects of known methods for physical fault injection differ. Relatively prominent surveys on fault attacks providing a comprehensive overview and insight on techniques and physical effects are presented by Bar-El et al. [BCN<sup>+</sup>04] and Giraud et al. [GT04].

Injecting faults deliberately into a circuit may change circuit behavior in such a way that access to sensible data is granted or secrets are leaked. In the worst case, the attacked device outputs a secret key instead of the ciphertext, which was reported for example by Trichina et al. [TK10]. In general, the success of fault attacks increases by focusing on very small, local and specific regions of a circuit (e.g. only affecting transistors of a specific set of cells) and by controlling the timing precisely. Usually, it is desired to not damage the circuit with an fault attack, since fault attacks have to be repeated with varying parameters to succeed. Expertise in the circuit's layout and functionality helps to successfully conduct fault attacks.

Various methods for physically mounted fault attacks are reported in the literature. These differ mainly in precision w.r.t. temporal (timing) and spatial granularity (locality), acquisition cost, availability, replication ability and required expertise for their application. The most relevant methods for fault attacks are optical attacks, such as laser beams and intense light. Recently, electromagnetic (EM) glitch attacks gained increasing attention. Supply voltage, clock signal and temperature variations are also very prominent sources for fault attacks, since these were the first techniques reported in literature. X-rays and alpha-particle attacks are also reported in literature but these attacks are uncommon, and I concentrate subsequently on the other, more common fault attack methods. Fault effects of high energetic particles is a well studied topic in nuclear physics and reliability engineering, and therefore I refer to the related literature, e.g. [KHP04] and [Bau05].

In the following, I briefly review the most relevant physical fault attacks that have been successfully mounted on physical devices. I elaborate on the temporal and spatial precision of particular attacks, which I take up again in Section 3.3 while reviewing appropriate fault models.

**Optical Attacks** Optical attacks pose the most common method for physical fault injection, which include attacks utilizing intense light (e.g. flashgun) and laser-beams. Since the package of the chip has to be removed, so that the chip surface is exposed, optical attacks belong to the class of semi-invasive attacks.

Integrated circuits are sensitive to light due to photo-electric effects, which is exploited by optical attacks. Basically, based on photo-electric effects the generation of electron-hole pairs in the semiconductor is caused [LNF+14]. As discussed in detail by e.g. Wang et al. [WX11], electron hole pairs affected by an electric field result in a transient current pulse. The current pulse loads the gate's capacitance, which in turn generates a voltage pulse. At logical level, the voltage pulse transforms into a signal transition, which propagates through the combinational network. Optical fault attacks can be mounted on both surfaces of a chip, the frontside and the backside. Respective attacks are often referred to as frontside attacks and backside attacks. Castro et al. [CDR+16] recently compared both techniques w.r.t. exploitable errors induced into an AES hardware implementation. Due to the mirror effect of metal layers on the frontside, backside attacks can be (but do not necessarily have to be), more effective because of the freedom to target any desired location [CDR+16].