#### TECHNISCHE UNIVERSITÄT MÜNCHEN FAKULTÄT FÜR INFORMATIK

Lehrstuhl für Sprachen und Beschreibungsstrukturen

## **Binary Analysis using On-Demand Tabulation of Function Summaries**

Julian Kranz

#### TECHNISCHE UNIVERSITÄT MÜNCHEN FAKULTÄT FÜR INFORMATIK

Lehrstuhl für Sprachen und Beschreibungsstrukturen

### Binary Analysis using On-Demand Tabulation of Function Summaries

#### Julian Kranz

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender:

Prof. Tobias Nipkow, Ph.D.

Prüfer der Dissertation:

Prof. Dr. Helmut Seidl

Prof. Dr. Antoine Miné

Die Dissertation wurde am 16.01.2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 10.04.2019 angenommen.

#### **Abstract**

Program analysis tries to recover properties of software in order to find flaws or to understand the ideas behind a software system. Modern software is typically written in a high-level programming language and then translated into machine instructions by a compiler. An analysis can either work on the source code written by the programmer directly or use the compiled binary as input. Analyzing the source code has the advantage of being able to gather information from abstractions and control structures of the respective programming language. For example, the type of a variable constrains the set of operations that may modify its value. However, source code level analysis also has drawbacks. First and foremost, the source may not be available. This is the case, e.g., when analyzing proprietary systems or malware. In addition, source code analysis relies on the semantics specification of the programming language. This specification, however, may not be exact or may intentionally not cover all possible program constructs (as is the case for C and C++). Last but not least, the compiler itself may contain bugs resulting in a divergence between the language specification and the actual program behaviour. As a result, binary program analysis has recently gained attention.

This work addresses two main challenges of binary program analysis. Due to the complexity of modern processors (consider, e.g., the Intel x86 architecture) writing an analysis for a specific machine architecture is cumbersome and not portable. Thus, the binary has to be decoded and translated into an analysis-friendly architectureindependent intermediate representation (IR). Implementing a decoder is itself errorprone because general-purpose programming languages lack constructs required for an intuitive decoder specification. Therefore, we present a DSL that offers built-in syntax for instruction decoders. We also show how we compile our specifications into naturally-looking C code which can be easily understood and debugged by a human reader. The second challenge of binary analysis is scalability. Binary analysis has to deal with sized inputs resulting from code size increases by large factors during compilation and translation into an IR. A common means of dealing with the problem of analyzing a large program is breaking it up into smaller chunks – e.g. functions – and analyzing these in isolation. However, modularity may lead to a precision loss that is not acceptable. As a remedy, we present an analysis methodology that tabulates functions for certain properties of calling contexts on-demand. This approach allows us

to reach the necessary performance while not giving up contextual information where it is required.

We demonstrate our analysis algorithm using benchmarks gathered from an implementation that is based on our DSL for binary disassembly and that implements the modular analysis using on-demand tabulation of function summaries.

#### Zusammenfassung

Programmanalyse ist darum bemüht, Eigenschaften von Software zu rekonstruieren, um auf diese Weise Fehler zu entdecken oder die Ideen hinter einem Softwaresystem zu verstehen. Moderne Software wird üblicherweise in einer höheren Programmiersprache geschrieben und anschließend von einem Compiler in Maschinen-Instruktionen übersetzt. Eine Analyse kann entweder direkt mit dem Quelltext arbeiten, den der Programmierer verfasst hat, oder das kompilierte Binärprogramm als Eingabe verwenden. Den Quelltext zu analysieren hat den Vorteil, die Möglichkeit zu haben, Informationen aus den Abstraktionen und Kontrollstrukturen der jeweiligen Programmiersprache gewinnen zu können. Zum Beispiel beschränkt der Typ einer Variablen die Menge an Operationen, die ihren Wert verändern können. Allerdings hat die Analyse von Quelltext auch Nachteile. Zuallererst ist möglich, dass der Quelltext nicht verfügbar ist. Dies ist zum Beispiel der Fall, wenn ein proprietäres System oder Schadsoftware analysiert werden soll. Außerdem muss sich eine Analyse des Quelltextes auf die Spezifikation der Semantik der Programmiersprache verlassen. Diese Spezifikation kann allerdings ungenau sein oder sogar bewusst einige Programmkonstrukte nicht abdecken (dies ist bei C und C++ der Fall). Schließlich kann auch der Compiler selbst Fehler enthalten, was zu einer Divergenz zwischen der Spezifikation der Sprache und dem tatsächlichen Verhalten des Programms führt. Aus diesen Gründen hat die Analyse auf Binärebene an Wichtigkeit gewonnen.

Diese Arbeit beschäftigt sich mit zwei zentralen Herausforderungen von Binäranalyse. Wegen der Komplexität moderner Prozessoren (man bedenke, z.B., die x86-Achitektur von Intel) ist umständlich und nicht portabel, eine Analyse für eine spezifische Maschinen-Architektur zu entwerfen. Aus diesem Grund muss der Binärcode zunächst dekodiert und in eine analysefreundliche und nicht von der Architektur abhängige Zwischendarstellung (IR) übersetzt werden. Die Implementierung des Dekodierers selbst ist fehleranfällig, da Allzweck-Programmiersprachen keine passenden Konstrukte mitbringen, um Dekodierer intuitiv zu spezifizieren. Aus diesem Grund stellen wir eine domänenspezifische Sprache (DSL) vor, eine eingebaute Syntax für Instruktionsdekodierer anbietet. Wir erklären außerdem, wie wir die resultierenden Spezifikationen in natürlich aussehenden Quelltext der Programmiersprache C übersetzen, der von einem menschlichen Leser leicht verstanden und auf Fehler geprüft werden kann. Die zweite Herausforderung von Binäranalyse ist die Skalierbarkeit.

Binäranalyse muss mit umfangreichen Eingaben umgehen können, die sich aus starken Vergrößerungen des Codes während der Kompilierung bzw. der Übersetzung in eine IR ergeben. Eine übliche Herangehensweise, um mit dem Problem der Analyse großer Programme umgehen zu können, ist es, diese in kleinere Teile – z.B. Funktionen – herunterzubrechen und diese Teile in Isolation zu analysieren. Allerdings kann Modularität zu einem Präzisionsverlust führen, der nicht akzeptabel ist. Als Abhilfe hierfür stellen wir eine Analysemethodik vor, die Funktionen nach bestimmten Eigenschaften der Aufruf-Kontexte nach Bedarf tabelliert. Dieser Ansatz erlaubt es uns, die nötige Performanz zu erreichen, ohne dabei Informationen über den Kontext zu verlieren, wo ebendiese nötig sind.

Wir demonstrieren unseren Analyse-Algorithmus durch Messungen anhand einer Implementierung, die auf unserer DSL zur Disassemblierung von Binärcode aufbaut und die unsere modulare Analyse umsetzt, die bedarfsorientiert Funktionsabstraktionen tabelliert.

#### Acknowledgments

I would like to give thanks to Axel Simon. He officially was my supervisor until January 2015 and continued to assist me throughout my time as a doctoral candidate. This work would have not been possible without his constant support over the past years.

#### **Contents**

| 2.2. Decoding x86 Prefixes  2.3. Evaluation  2.3.1. Performance  2.3.2. Correctness  2.4. Related Work  3. Semantics Translation using RReil  3.1. RReil Intermediate Representation  3.2. The Generic Decoder Specification Language (GDSL)  3.3. Writing Semantics using GDSL  3.3.1. An Example Intel Instruction  3.3.2. Generating RReil Statements using GDSL Monadic Functions  3.3.3. The Translator  3.4. Optimizing the RReil Code                                                                                                                                                                                                                                                                            | Al  | ostrac | rt en                       | i  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----------------------------------------------------------------|----|

| I. Introduction  II. The GDSL Toolkit: An Architecture-Independent Framework for Machine Code Disassemblers  2. GDSL: The Generic Decoder Specification Language 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination    | Zι  | ısamı  | nenfassung                                                      | iv |

| 11. Introduction  II. The GDSL Toolkit: An Architecture-Independent Framework for Machine Code Disassemblers  22. GDSL: The Generic Decoder Specification Language 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  23. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination | A   | cknov  | vledgments                                                      | V  |

| II. The GDSL Toolkit: An Architecture-Independent Framework for Machine Code Disassemblers  2. GDSL: The Generic Decoder Specification Language 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                     | I.  | Int    | roduction                                                       | 1  |

| Machine Code Disassemblers  2. GDSL: The Generic Decoder Specification Language 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                     | 1.  | Intr   | oduction                                                        | 2  |

| 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                     | II. |        | <u>-</u>                                                        | g  |

| 2.1. General Language Overview 2.1.1. Endianness Configuration 2.2. Decoding x86 Prefixes 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                     | 2.  | GD     | SL: The Generic Decoder Specification Language                  | 1( |

| 2.1.1. Endianness Configuration  2.2. Decoding x86 Prefixes  2.3. Evaluation  2.3.1. Performance  2.3.2. Correctness  2.4. Related Work  3. Semantics Translation using RReil  3.1. RReil Intermediate Representation  3.2. The Generic Decoder Specification Language (GDSL)  3.3. Writing Semantics using GDSL  3.3.1. An Example Intel Instruction  3.3.2. Generating RReil Statements using GDSL Monadic Functions  3.3.3. The Translator  3.4. Optimizing the RReil Code  3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                       |     |        |                                                                 | 12 |

| 2.3. Evaluation 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                                                                                               |     |        | 2.1.1. Endianness Configuration                                 | 15 |

| 2.3.1. Performance 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                                                                                                               |     | 2.2.   | Decoding x86 Prefixes                                           | 16 |

| 2.3.2. Correctness 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                                                                                                                                  |     | 2.3.   | Evaluation                                                      | 18 |

| 2.4. Related Work  3. Semantics Translation using RReil 3.1. RReil Intermediate Representation 3.2. The Generic Decoder Specification Language (GDSL) 3.3. Writing Semantics using GDSL 3.3.1. An Example Intel Instruction 3.3.2. Generating RReil Statements using GDSL Monadic Functions 3.3.3. The Translator 3.4. Optimizing the RReil Code 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                                                                                                                                                     |     |        | 2.3.1. Performance                                              | 19 |

| 3.1. RReil Intermediate Representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |        | 2.3.2. Correctness                                              | 20 |

| <ul> <li>3.1. RReil Intermediate Representation</li> <li>3.2. The Generic Decoder Specification Language (GDSL)</li> <li>3.3. Writing Semantics using GDSL</li> <li>3.3.1. An Example Intel Instruction</li> <li>3.3.2. Generating RReil Statements using GDSL Monadic Functions</li> <li>3.3.3. The Translator</li> <li>3.4. Optimizing the RReil Code</li> <li>3.4.1. Liveness Analysis and Dead Code Elimination</li> </ul>                                                                                                                                                                                                                                                                                          |     | 2.4.   | Related Work                                                    | 20 |

| <ul> <li>3.2. The Generic Decoder Specification Language (GDSL)</li> <li>3.3. Writing Semantics using GDSL</li> <li>3.3.1. An Example Intel Instruction</li> <li>3.3.2. Generating RReil Statements using GDSL Monadic Functions</li> <li>3.3.3. The Translator</li> <li>3.4. Optimizing the RReil Code</li> <li>3.4.1. Liveness Analysis and Dead Code Elimination</li> </ul>                                                                                                                                                                                                                                                                                                                                          | 3.  | Sem    | antics Translation using RReil                                  | 24 |

| <ul> <li>3.3. Writing Semantics using GDSL</li> <li>3.3.1. An Example Intel Instruction</li> <li>3.3.2. Generating RReil Statements using GDSL Monadic Functions</li> <li>3.3.3. The Translator</li> <li>3.4. Optimizing the RReil Code</li> <li>3.4.1. Liveness Analysis and Dead Code Elimination</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |     | 3.1.   | RReil Intermediate Representation                               | 24 |

| <ul> <li>3.3.1. An Example Intel Instruction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 3.2.   | The Generic Decoder Specification Language (GDSL)               | 25 |

| <ul> <li>3.3.2. Generating RReil Statements using GDSL Monadic Functions .</li> <li>3.3.3. The Translator</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 3.3.   | Writing Semantics using GDSL                                    | 26 |

| 3.3.3. The Translator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |        | 3.3.1. An Example Intel Instruction                             | 26 |

| 3.4. Optimizing the RReil Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |        | 3.3.2. Generating RReil Statements using GDSL Monadic Functions | 27 |

| 3.4.1. Liveness Analysis and Dead Code Elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |        |                                                                 | 28 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 3.4.   | 1 0                                                             | 29 |

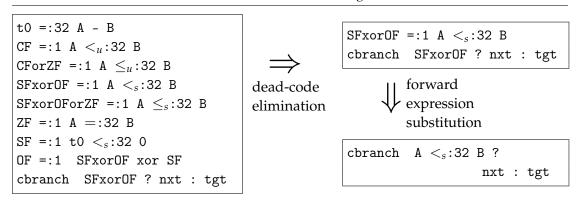

| 3.4.2. Forward Expression Substitution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |        | 3.4.1. Liveness Analysis and Dead Code Elimination              | 29 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |        | 3.4.2. Forward Expression Substitution                          | 30 |

#### Contents

|     |               | Empirical Evaluation                                             | 31<br>32   |

|-----|---------------|------------------------------------------------------------------|------------|

| 4.  | Veri          | fication of the Decoder and the Translator                       | 34         |

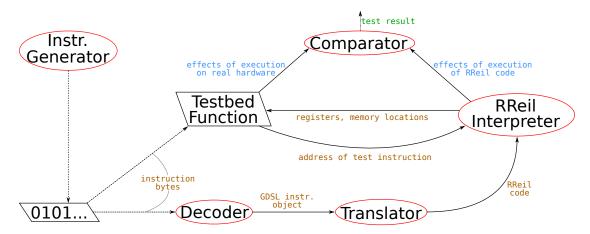

|     | 4.1.          | Automatic Generation of End-to-End Tests                         | 34         |

|     | 4.2.          | Generation of x86 Machine Instructions                           | 35         |

|     | 4.3.          | Execution of the Generated Instruction                           | 36         |

|     | 4.4.          | Test Results and Error Conditions                                | 38         |

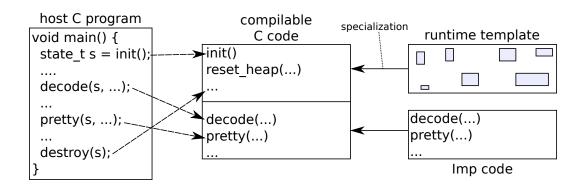

| 5.  | Con           | npiling GDSL to C                                                | 40         |

|     |               | 5.0.1. Heap-Allocation and Avoidance of Garbage Collection       | 40         |

|     |               | 5.0.2. Unboxing of Polymorphic Values and Closures               | 41         |

|     |               | 5.0.3. Transformation of Monadic Functions                       | 42         |

|     | 5.1.          | Lowering GDSL to Core                                            | 43         |

|     |               | Conversion to an Imperative Language                             | 48         |

|     |               | 5.2.1. Translating Monadic Sequences                             | 58         |

|     | 5.3.          | Optimizing the Intermediate Representation Imp                   | 60         |

|     |               | 5.3.1. Simplifying Imp                                           | 60         |

|     |               | 5.3.2. Removing Monadic Actions                                  | 62         |

|     |               | 5.3.3. Unboxing by Type Inference                                | 65         |

|     | 5.4.          | Implementation                                                   | 70         |

|     | 5.5.          | <del>-</del>                                                     | 71         |

|     | 5.6.          |                                                                  | 73         |

|     | 5.7.          | Conclusion                                                       | <b>7</b> 5 |

| TTI | ſ Sα          | alability Through Modular Analysis                               | 77         |

| 111 | ı. <i>5</i> 0 | alability Tillough Modulal Analysis                              | ,,         |

| 6.  |               | dular Analysis of Executables using On-Demand Heyting Completion | 78         |

|     | 6.1.          | Preliminary Definitions                                          | 81         |

|     |               | 6.1.1. Abstract Interpretation of the Collecting Semantics       | 83         |

|     | 6.2.          | Modular Program Semantics                                        | 86         |

|     |               | 6.2.1. Abstract Interpretation of the Relational Semantics       | 86         |

|     |               | 6.2.2. Abstract Semantics of Memory Accesses                     | 88         |

|     |               | 6.2.3. Application of Function Summaries                         | 90         |

|     |               | 6.2.4. Computing a Fixpoint of the Abstract Relational Semantics | 101        |

|     | 6.3.          | <i>y</i> 8 1                                                     | 103        |

|     |               | 6.3.1. Extracting Refinement Information using Herbrand Terms    | 103        |

|     |               | 6.3.2. Specializing Summaries with Herbrand Terms                | 106        |

|     |               | 6.3.3. Combining Specialized Function Summaries                  | 107        |

#### Contents

|     | 6.4.<br>6.5. | 6.3.4. Heyting Completion               | 109<br>110<br>112<br>113 |

|-----|--------------|-----------------------------------------|--------------------------|

| ΙV  | . An         | alysis Implementation and Evaluation    | 115                      |

| 7.  | The          | Summy Analysis Tool                     | 116                      |

|     |              | Getting Started                         | 116                      |

|     | 7.2.         |                                         | 117                      |

|     | 7.3.         |                                         | 118                      |

|     | 7.4.         |                                         | 122                      |

|     | 7.5.         |                                         | 125                      |

|     |              | 7.5.1. Additional Narrowing Iteration   | 129                      |

|     | 7.6.         |                                         | 130                      |

|     |              | 7.6.1. Handling of Conflicting Accesses | 130                      |

|     |              | 7.6.2. Further Ideas for Improvement    | 131                      |

|     | 7.7.         | Evaluation                              | 131                      |

| V.  | Co           | nclusion                                | 135                      |

| Lis | st of l      | Figures                                 | 138                      |

| Lis | st of [      | Tables                                  | 141                      |

| Bi  | bliog        | raphy                                   | 142                      |

# Part I. Introduction

#### 1. Introduction

Program analysis tries to recover properties of software programs in order to find flaws or understand the ideas behind a software system. The latter particularly applies to malware as there is no documentation available that describes its functionality. Finding flaws is particularly relevant for strengthening the security of systems since software nowadays is immensely important for every part of modern life and, thus, exposes a massive attack surface.

In general, an analysis can work with different input program representations: It can either analyze the source code of a program in some higher level programming language or it can analyze the machine instructions which were generated by a compiler from the source of a program. Generally, the task of the analyzer is significantly simpler when dealing with source code because programming languages are geared towards readability and understandability which can also be exploited by the analysis tool. For example, programming languages offer high-level control flow structures and help in componentization of large system, both of which help during program analysis. As a matter of fact, programming languages are sometimes designed with certain types of program analyses in mind (e.g. automatic lifetime deduction for references in Rust [58]) in order to allow for meaningful error messages and aid refactoring during development.

However, analyzing the source code also has drawbacks. First, the source code needs to be available which is not always the case. This may be because of software licensing or because the authors of the software are unwilling to allow the analysis of their software, e.g. in case of malware. Second, the analysis of source code needs to rely on the specified semantics of the programming language. However, the definition of the semantics may be vague, implementation defined, or even undefined for some language constructs (and, indeed, many C and C++ programs rely on undefined behaviour [62]). Here, the semantics implemented by the compiler needs to be approximated which can be a very laborious task, in particular in the presence of different compilers and optimization settings that can affect the behaviour of the generated program. As a result, binary program analysis is a necessity.

Binary program analysis uses the CPU-specific instructions of a program as an input. Thus, it directly processes the code as seen by the machine and only has to rely on the semantics specification of the silicon manufacturer. However, there is a multitude of

hardware architectures, some of which include hundreds of instructions with complex semantics. It is therefore desirable to separate the analysis algorithm itself from both the complexity of machine instructions and the concrete hardware architecture. A common approach for this is to first translate the input program into some intermediate representation (IR) that is common to all supported architectures. The analysis then only needs to implement transformers for the semantic statements of the IR. In such a design, new hardware can easily be supported by the analyzer by providing a suitable decoder and semantics translator. In this work, we use a refined version of the REIL IR [19] called RReil (Relational Reverse Engineering Intermediate Language) [48] which is geared towards binary analysis by having a very small and simple set of semantic statements while offering flexibility through, e.g., allowing accesses at arbitrary bit offsets into registers.

Decoding machine instructions and translating them into an IR seems to be a simple and straight forward software engineering problem at first sight. However, instruction sets are built for interpretation by machines and are – in some well-known cases such as Intel x86 – extended oftentimes during their lifespan. As a result, software implementations of decoders tend to contain a huge number of rules which makes them hard to understand and maintain. Even though a large number of decoding tools already existed [1], none of them seemed to be a perfect fit for our requirements: We needed a decoding tool that allows for an easy specification of machine decoders that closely follows the layout of the documentation of the chip manufacturer as we deem this to be the best way to keep the code readable and, thus, extensible and maintainable. We therefore developed the GDSL (Generic Disassembler Specification Language) toolkit that offers a functional ML-like DSL that is specifically designed for instruction decoder specifications. In this work, we present the current state of the GDSL project and future directions.

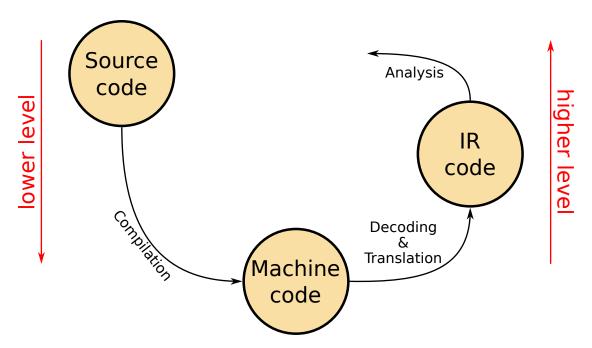

Figure 1.4 contains the software lifecycle from the viewpoint of binary program analysis. First, source code is written. This source code is then compiled to machine code. Later, the machine code is decoded and translated into an IR which is used by an analysis tool to recover properties of the software. As an example, consider the C++ code in Fig. 1.1. The code defines two structures A and B where B inherits from A. Line 15 uses dynamic function binding in order to invoke the function f() in structure B. Figure 1.2 shows the x86 assembly code that results from compiling the code with version 6 of clang from the LLVM project using the -01 optimization flag. The figure shows the assembly code for all relevant functions. Each line within a function begins with the address of the instruction in memory which is followed by the bytes that encode the instruction. Finally, each line contains a string representation of the instruction in AT&T assembly syntax. Note that mangled function names have been replaced by more readable identifiers. The main function commences by calling the

```

struct A {

1

virtual int f() {

2

return 99:

3

4

};

5

struct B : public A {

virtual int f() {

return 42;

}

10

};

11

12

int main(void) {

13

A *a = new B();

14

return a->f();

15

}

16

```

Figure 1.1.: Example code that uses dynamic function binding.

memory allocation function in line 4 which returns a pointer to the object in register %rax. Next, main() calls the constructor of structure B in line 8 which expects a pointer to the object it is constructing in register %rdi. The constructor of structure B, in turn, calls the constructor of structure A which initializes the virtual table pointer in line 23. The pointer to the virtual table is replaced by a pointer to the virtual table of the subclass, i.e. the virtual table of B, in line 18. This way, when tail-calling the first entry in the virtual table in line 12, control dispatches to the subclass version of f, namely B::f(). Note that the two lines of C++ code in main() translated to 11 assembly instructions. Further note that the instructions are encoded using a varying number of bytes. This is caused by the rather complex encoding rules of the Intel x86 architecture.

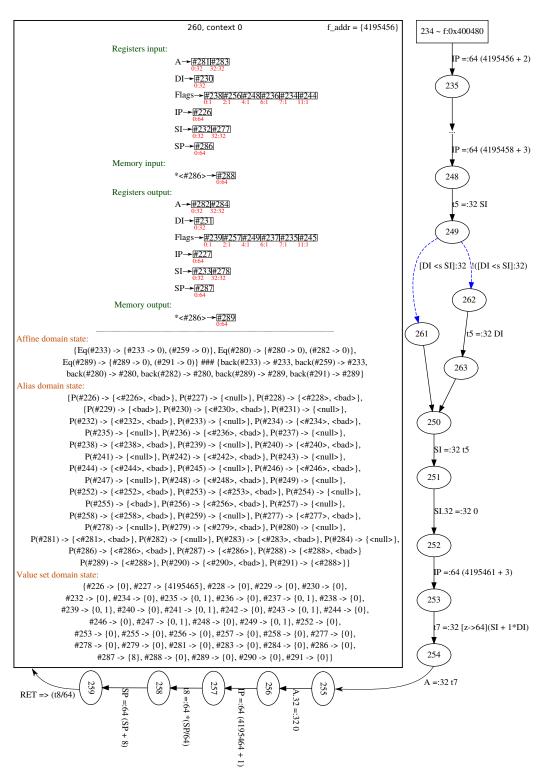

Figure 1.3 contains a string representation of the RReil code that is generated by the GDSL toolkit for the main function in Fig. 1.2. RReil allows for arbitrary bit sizes and offsets. For example, line 9 writes the 32 bit value 0 to DI at offset 32. Note that a single machine instruction is translated into a number of RReil statements, resulting in another increase in code size compared to the x86 machine code. Also note that the shown RReil code is not optimal; for example, the register IP is incremented multiple times without being read in between. Such updates could be merged together.

The increase in size of the source code becomes a challenge to the scalability of a

```

0000000000400600 <main>:

400600: 53

%rbx

push

2

400601: bf 08 00 00 00

$0x8, %edi

mov

3

400606: e8 f5 fe ff ff

callq 400500 <memory_alloc>

40060b: 48 89 c3

%rax, %rbx

mov

40060e: 48 c7 03 00 00 00 00

$0x0, (%rbx)

movq

400615: 48 89 df

mov

%rbx,%rdi

400618: e8 13 00 00 00

callq 400630 <B_constructor>

40061d: 48 8b 03

(%rbx), %rax

mov

400620: 48 89 df

%rbx, %rdi

mov

10

400623: 5b

%rbx

pop

11

400624: ff 20

*(%rax)

jmpq

12

13

000000000400630 <B_constructor>:

14

400630: 53

%rbx

push

15

400631: 48 89 fb

%rdi, %rbx

mov

16

400634: e8 17 00 00 00

callq

400650 <A_constructor>

17

400639: 48 c7 03 18 07 40 00

movq

$0x400718, (%rbx)

18

400640: 5b

%rbx

pop

19

400641: c3

20

retq

21

000000000400650 <A_constructor>:

22

400650: 48 c7 07 68 07 40 00 movq

$0x400768,(%rdi)

23

400657: c3

retq

24

25

0000000000400660 <B_f>:

26

400660: b8 2a 00 00 00

$0x2a, %eax

mov

27

400665: c3

retq

28

29

000000000400670 <A_f>:

30

400670: b8 63 00 00 00

$0x63, %eax

mov

31

400675: c3

retq

32

```

Figure 1.2.: Assembly code for the C++ program in Fig. 1.1

```

push %rbx

callq 400630

IP =: 64 (IP + 1)

IP =: 64 (IP + 5)

2

25

SP =:64 (SP - 8)

T0 =: 64 B

26

SP =: 64 (SP - 8)

*[64]SP =:64 IP

27

*[64]SP =:64 TO

goto [CALL] [64] (IP + 19)

28

mov $0x8, %edi

mov (%rbx), %rax

29

IP =: 64 (IP + 5)

IP = :64 (IP + 3)

30

DI =:32 8

T0 =: 64 * [64] B

31

DI.32 =:32 0

A = :64 T0

32

callq 400500

mov %rbx, %rdi

10

33

IP =: 64 (IP + 5)

IP = :64 (IP + 3)

11

34

SP =: 64 (SP - 8)

DI =:64 B

12

35

*[64]SP =:64 IP

pop %rbx

13

36

goto [CALL] [64](IP + -267)

IP = :64 (IP + 1)

14

T0 =: 64 * [64] SP

mov %rax, %rbx

15

38

IP =: 64 (IP + 3)

SP =: 64 (SP + 8)

16

39

B = :64 A

B =:64 TO

17

40

movq $0x0, (%rbx)

jmpq *(%rax)

18

41

IP =: 64 (IP + 7)

IP =: 64 (IP + 2)

19

42

*[64]B =: 64 0

T1 = :64 * [64] A

20

43

mov %rbx, %rdi

goto [JUMP] [64]T1

21

44

IP =: 64 (IP + 3)

22

DI =: 64 B

23

```

Figure 1.3.: Translated RReil code for the main function in Fig. 1.2.

Figure 1.4.: Software lifecycle from the viewpoint of binary analysis.

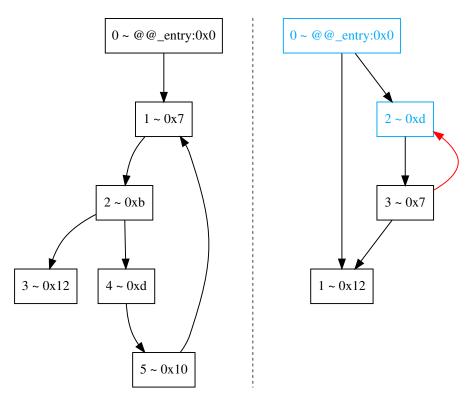

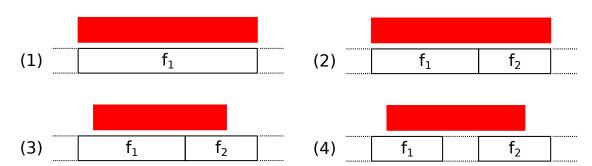

program analysis. Figure 1.3 illustrates this for our example code. In general, compiling a single line of C code results in around 10 x86 machine instructions on average. Each of these machine instructions is then translated into an IR program which requires around four IR statements (already taking optimizations into account) per instruction. As a result, scalability needs careful consideration during development of a binary analysis tool. In this work, we discuss an analysis algorithm that uses on-demand tabulation of function summaries. Here, the analyzer initially processes each function in isolation, thus keeping the analysis modular. However, this modularity may lead to a severe precision loss – consider, for example, a function that expects a pointer to a structure of type A as parameter and invokes the function f() on it. In this case, a fully modular analysis would need to make worst-case assumptions about the target of the call. Our analyzer recognizes such situations. It tabulates the function for each concrete function pointer value passed to the function and makes use of the now fixed target during summary computation. This way, we compromise on modularity in order to keep the analysis as precise as necessary, however without sacrificing scalability.

Again consider the code in Fig. 1.1 and Fig. 1.2. In the C++ code, the static type of the variable a constrains the set of possible targets of the virtual call in line 15 (the call can either dispatch to A::f() or B::f()). In the assembly code, on the other hand, line 12 alone gives no clue as to where the tail-call dispatches. Indeed, an analysis has to infer

the effects of the constructor calls and apply them to the state of the object pointed to by %rax in order to build the inter-procedural control flow graph. The analysis algorithm presented in this work is able to do that.

In summary, we make the following contributions:

- We describe a functional ML-like language called GDSL that is geared towards the implementation of instruction decoders and semantics translators. We provide a compiler from GDSL to C, but other back-end languages are possible.

- We evaluated the language design by implementing a decoder for all 897 (as of September 2012) instructions of the Intel x86 architecture and offering semantics translations for about half of those instructions.

- We show how we use GDSL to implement basic optimizations on the produced IR. This allows us to provide optimizations that are independent of both the machine architecture of the translated instructions and the target language of the DSL compiler.

- We present a structure preserving compilation of our functional language GDSL to C that results in code that resembles manually written C code. This enables the developer of the DSL program to use an off-the-shelf C debugger to debug the DSL code.

- We present an analysis framework for programs in executable format that makes use of on-demand tabulation of function summaries in order to achieve both scalability and sufficient precision. We demonstrate our framework using an analysis that reconstructs the control flow and call graph.

Parts of this work have been published in the following papers:

- 1. GDSL: A Generic Decoder Specification Language for Interpreting Machine Language [1]

- 2. GDSL: A Universal Toolkit for Giving Semantics to Machine Language [33]

- 3. The GDSL Toolkit: Generating Frontends for the Analysis of Machine Code [55]

- 4. Structure-Preserving Compilation: Efficient Integration of Functional DSLs into Legacy Systems [34]

- 5. Modular Analysis of Executables Using On-Demand Heyting Completion [36]

#### Part II.

# The GDSL Toolkit: An Architecture-Independent Framework for Machine Code Disassemblers

# 2. GDSL: The Generic Decoder Specification Language

The reconstruction of assembler instructions from an input (byte) sequence that comprises the program is the first step towards binary program analysis. The second step is to map each statement to a meaning which may be a value-, timing- or energy semantics, etc., depending on the goal of the analysis. Both aspects are commonly addressed by writing an architecture-specific decoder and a translator to some internal representation expressed in the implementation language of the analysis. The goal of our work is to build an infrastructure to specify decoders and translations to semantics using a domain specific language (DSL) that can be compiled into the programming language of the analysis tools. To this end, we present GDSL and motivate its design by the task of specifying decoders for Intel x86.

The incentive for creating a DSL to specify decoder and semantics of assembler instructions was a discussion at a Dagstuhl seminar on the analysis of executable code. Here, it was realized that many research groups implemented prototype analyses using an architecture-specific decoder and a hand-written semantics interpretation. Besides duplication of work, these approaches are usually incomplete, are bound to one architecture and are hard to maintain since their representation of instructions is geared towards a specific project. In the presence of steadily increasing instruction sets and the need to adapt an analysis to new targets such as virtual machines contained in malware, maintainability and simplicity of decoder specifications is of increasing importance.

To this end, it is desirable to group instructions logically or, when converting a manufacturer's manual, in alphabetical order; we call this mnemonic-centric specification. For the sake of efficiency, however, a decoder must make a decision based on the next value from the input sequence (opcode-centric dispatch) which precludes testing opcode patterns one after the other. While a classic scanner generator like lex can convert a mnemonic-centric specification to an opcode-centric decoder, it allows and encourages overlapping patterns. Consider the following lex scanner specification:

```

while|do|switch|case { printf("keyword %s", yytext); }

[a-zA-Z][a-zA-Z0-9]* { printf("ident %s", yytext); }

```

| Opcode | Instruction | Description            |

|--------|-------------|------------------------|

| 00 /r  | ADD r/m8,r8 | Add r8 to r/m8.        |

| 28 /r  | SUB r/m8,r8 | Subtract r8 from r/m8. |

Table 2.1.: Two typical instructions in the Intel x86 manual.

Here, the patterns for the keywords and the identifier are overlapping: the input while matches both rules. In this case, lex uses the rule that appears first in the specification file. Thus, a keyword is returned. Overlapping patterns are desirable in a scanner specification since they improve readability and conciseness. In an instruction decoder, however, overlapping patterns are undesirable since the sequence in which the rules are written starts to matter which, in turn, precludes a mnemonic-centric specification. Hence, a DSL for maintainable decoder specifications must provide a concise way of writing non-overlapping patterns to exactly match an instruction.

Another challenge is the processing of non-constant bits of an instruction that are used to specify parameters. Since parameter bits often follow recurring patterns, an abstraction mechanism is required to keep the specification concise. For example, the mod/rm-byte in Intel x86 instructions follows many opcodes and determines which register or memory addressing mode to use. Table 2.1 shows an excerpt of the Intel manual where the first column shows the two bytes that together form an instruction. The second byte /r is the mod/rm-byte that determines which 8-bit registers r8 and which pointer or register r/m8 stand for. Within our decoder specification language, we define functions  $r/m8^1$  and r8 to generate the arguments of an instruction. The contents of the mod/rm-byte are read by a sub-decoder named /r that stores the read byte in an internal decoder state. This sub-decoder can be re-used in the decoder for ADD and SUB:

```

val main [0x00 /r] = binop ADD r/m8 r8

val main [0x28 /r] = binop SUB r/m8 r8

```

Here, the decoder main is declared as reading 0x00 (resp. 0x28) from the input before running the sub-decoder /r. The binop function is a simple wrapper that executes functions r/m8 and r8 (which access the values stored by /r) and applies the results to the passed-in constructor (here ADD and SUB). By using sub-decoders such as /r that communicate via the internal state, our main decoder comes very close to the specification in Table 2.1 which is a simplified excerpt from the Intel manual.

<sup>&</sup>lt;sup>1</sup>We allow / as part of an identifier to accommodate the Intel nomenclature.

Since our DSL is an ML-like functional language, it is powerful enough to describe all parts of a decoder, even r/m8 and r8 that are often hand-coded primitives in other decoder frameworks. This comprehensive approach enables users to add instructions that have not been anticipated in the original design of /r. In summary, GDSL improves over existing approaches as follows:

- Its abstraction mechanisms enable the definition of instruction decoders that are very close to the syntax used in manufacturer's manuals, thereby ensuring maintainability even by the end users of the decoder framework.

- Our specification is type checked during compilation and overlapping patterns

are detected. This ensures high fidelity of the resulting decoder, especially in the

presence of mistakes in the manufacturer's manuals.

- The DSL is flexible enough to accommodate a variety of architectures. Due to its general nature, it is possible to add translations from native instructions to some abstract semantics, which will enable binary analysis tools to analyse code for any architecture that is described with our framework. In Chap. 3, we describe how we use GDSL for a translation to our IR called RReil.

- We provide a prototype compiler that generates C code which is competitive with other decoders. The specifications can be translated to other languages or used for other purposes (e.g. test generation) by writing a new backend.

After the next section presents the design of GDSL, Sect. 2.2 illustrates its expressiveness by detailing the decoding of Intel prefixes. Section 2.3 presents an evaluation of our implementation before Sect. 2.4 presents related work.

#### 2.1. General Language Overview

This section discusses the design of GDSL by illustrating the use of the various syntactic constructs. The general idea is that the decoder specification is an executable functional program that consumes the input sequence and produces a heap containing the abstract syntax tree (AST) that represents the recognized instruction. After the AST in the heap has been processed, the heap can be reused for decoding the next instruction, thereby avoiding the need for a garbage collector or for allocating memory with each instruction.

The grammar of GDSL is shown in Fig. 2.1 on page 22. In the following, we refer to single productions using their name in the right column of the table. A file consists of a sequence of definitions given by **Decl**.

Line *type decl*. shows the production for algebraic data types that introduce (or extend) the type t-id with constructors con. As in ML, each constructor takes zero or one argument, allowing the definition of enumerations such as type register = AX | BX | CX | DX or AST nodes such as type op = Reg of register | Mem of {size : int, reg : op} | Imm8 of [8]. Here, the argument to the Mem constructor is a record while Imm8 takes a bit vector of 8 bits, written [8]. Bit vectors and int are the only basic data types with singleton bit-vectors acting as Booleans. Abbreviations for complex types can be introduced using the syntactic construct in line *type abbrev*. Line *action type* contains the production for the type of a monadic action. A monadic action has a result type (first non-terminal **Type**) and transforms a state of type *t* to a state of type *t'*. The export keyword states which of the decoders, functions and constants are publicly visible to the client code. In line 1 of Fig. 2.2 on page 23, we export an action decode that produces a result of type instr. It requires a state of sub-type of {} and produces a new state which has a type that is a super-type of {}.

Productions function decl., decoder decl., and guarded decoder decl. introduce functions, decoders and decoders with guards, respectively. Functions and decoders differ in that functions take arguments and have exactly one definition whereas decoders read from the implicit input stream and definitions with the same name augment each other. Consider the decoder snipped in Fig. 2.2. Here, binop and r/m8 in lines 10 and 20 are functions taking three and no arguments, respectively. In contrast, lines 16, 18 and 25 define decoders whose right-hand-side is evaluated if the token sequence in the square brackets matches the current input. Tokens can be specified in three ways (Production single token in Fig. 2.1): either as a hexadecimal number (c.f. the first token of main), as a call to another decoder (c.f. the second token of main) or as a bit pattern (as used in the /r and /0 decoders). Bit patterns, in turn, are enclosed in ticks and are given by Productions bit patterns, pattern binding, and pattern var:

- strings of 0,1,. (c.f. 000 in /0); the dot acts as a wildcard; a set of bit strings can be specified by separating them using a vertical bar, e.g. 00|01|10.

- as above, with a leading variable separated by @; the variable is bound to the actual bits in the input; for instance, /0 could have been written as follows:

```

val /0 ['mod:2 reg@0000 rm:3'] =

update @{mod=mod, reg/opcode=reg, rm=rm}

```

• a variable with a width in bits; the notation v:3 is syntactic sugar for v@...; examples are mod, reg and rm in the decoders /r and /0.

The semantics of "calling" another decoder within a token sequence is that the pattern of the called decoder is substituted where it appears and that its body is

prepended to the right-hand-side of the decoder. For instance, main [0x80 / 0] is translated internally as follows:

```

val main [0x80 'mod:2 000 rm:3'] = do

update @{mod=mod, reg/opcode='000', rm=rm};

binop ADD r/m8 imm8

end

```

After inlining sub-decoders, an equivalent function without decoder syntax can easily be derived using a consume8 primitive that reads one byte from the input stream. Here, all patterns of the rules of main are transformed into the following combined function:

```

val main = do

1

byte1 <- consume8;</pre>

2

case byte1 of

3

'0x80' : do

byte2 <- consume8;</pre>

5

case byte2 of

'mod:2 000 rm:3' : do

update @{mod=mod, reg/opcode='000', rm=rm};

binop ADD r/m8 imm8

10

'0x00' : ...

11

```

During this translation, overlapping patterns are detected. For rules of varying lengths, a prefix length n is determined as the minimum number of bits that all rules read. Each rule is examined in turn by taking its prefix of size n and removing the matched patterns from an initial set of all patterns of size n. If this fails, i.e. the pattern to remove is no longer contained in the set, the rule is reported to overlap with a previous rule. Consider, for example, a prefix of size 2 which leads to the initial set  $\{'00', '01', '10', '11'\}$  and two overlapping rules '0.' and '00'. For the first rule, the patterns '00' and '01' are removed from the initial set, resulting in the set  $\{'10', '11'\}$ . For the second rule, the pattern '00' would need to be removed; however, '00' is not contained in the set of remaining patterns. As a result, the second rule is reported to overlap with a previous rule. Note that the actual implementation has to represent the set of remaining patterns more efficiently in order not to require an exponential amount of memory.

Once it is known that rules do not overlap, they can be re-arranged for more efficient pattern matching. Specifically, we repeatedly identify those bit positions that contain

the most constant bits (i.e. 0 or 1 but not wildcards) and generate a switch-statement for those bits. The results are nested switch-statements that mostly have consecutive cases and are therefore translated by the compiler into efficient tables.

The bodies of functions and decoders are given by the **Expr** productions. Here, productions *binding*, *bifurcation*, *conditional*, *function appl.*, *constants*, and *constructor/var* give the standard constructs found in a functional language with **Expr Expr** in line *function appl.* denoting function application. Our language allows the creation of compound values using records which are collections of field names bound to a value. Production *record constant* allows the construction of new records (used in line 13 of Fig. 2.2 on page 23). The value of a field foo is extracted using \$foo which itself is a function. Thus, \$foo {foo=7} evaluates to 7. Analogously, @{foo=x} is a function taking a record and setting the field foo to x. For instance, @{bar='110'} {foo=7} evaluates to {bar='110'}, foo=7}.

In order to allow for an internal state, each decoder is a monad, a concept borrowed from the pure functional language Haskell [44]. A monad is an abstract type containing a function from an input state to an output state and a result. The motivation for monads is to chain together computations that operate on a state without requiring side-effects in the language. Production *monadic seq.* details the do-statement which threads together monadic actions whose result can be bound to an identifier. A monadic action is a normal function that has a monadic type, i.e. expects the monadic state as parameter and produces a new, possibly modified state as result. The result of the do-statement is that of the last action. Production *basic actions* presents the three basic monadic actions of our language: update f applies f to the internal state (and is usually a record update); query f returns the result of applying f to the internal state (and is usually a record field selector); and return x that returns x as a result (this is a shorthand for let val f \_ = x in query f).

The internal state can also be accessed using guards. Guards allow an additional case distinction based on the global state after a matching decoder rule has been selected. An example of guards can be seen in Fig. 2.2. Here, the first guard of \$opndsz, \$rexw, and otherwise in lines 27f that evaluates to '1' determines which right-hand-side is evaluated. Guards are functions taking the internal state as argument. Thus, opndsz and rexw are record fields in the internal state and otherwise is a function always returning '1'.

#### 2.1.1. Endianness Configuration

When reading from the input stream, we have to take its instruction word size and endianness into account. For example, assume an architecture that uses 32 bit instruction words in big endian mode. Here, the first byte of an instruction at address i is not

found at address i, but at an offset of three, i.e. at i+3. We allow the configuration of the endianness through the endianness primitive as can be seen in line 6 of Fig. 2.2 on page 23. The primitive expects a bit vector as parameter. The integer value of this bit vector is XOR'ed with the offset when reading the instruction stream. For little endian architectures, we use the vector 0. For big endian architectures, we use a vector ending in n one bits for an architecture word size of 8\*(n+1). As an example, assume we want to read the second byte of the 4th instruction using the aforementioned 32-bit big endian architecture. The 4th instruction can be found at offset 3\*4=12 (3 preceding instructions of size 32 bits, i.e. 4 bytes, each). Thus, we want to access the 13th (counting from zero) byte of the instruction stream when not taking endianness into account. In order to find a proper endianness configuration vector for the architecture, we need to determine an n such that 8\*(n+1) equals the word size, i.e. 32. It follows that n is 3 and the respective vector is 0b11. XOR'ing the offset 13 with the vector 0b11 gives us  $13 \oplus 11_2 = 14$ . Indeed, given that the instruction spans 4 bytes starting from offset 12, this is the 2nd last byte, i.e. the byte we want to read.

#### 2.2. Decoding x86 Prefixes

One challenge in decoding x86 instructions is the correct handling of prefixes: they either serve to modify the following instruction or they are part of the following opcode (a so-called mandatory prefix). In the latter case, other prefixes are allowed between the mandatory prefix and the actual opcode. For example, both instruction sequences 67 f3 45 0f 7e d1 and f3 67 45 0f 7e d1 encode movq xmm10, xmm9 where 67 is an ADDRSZ prefix and f3 is a REPNE prefix, but used here as mandatory prefix to extend the opcode 0f 7e. Moreover, 45 is another "standard" REX prefix and d1 the mod/rm byte. Confusingly, the REX prefix must immediately precede the opcode, otherwise it is ignored.

Since the mandatory prefix extends the opcode, there may be multiple instructions with the same opcode but different mandatory prefixes. For example, the instructions mulss, mulsd, and mulpd share the same opcode, here 0f 59, but have different mandatory prefixes, namely f2, f3, and 66, respectively. If multiple mandatory prefixes are present, the order in which these prefixes occur and dominance rules become important. For example, while the last occurrence of f2 and f3 determines the mandatory prefix, an occurrence of 66 is only recognized as mandatory prefix if f2 and f3 cannot start an instruction. A correct decoder recognizes<sup>2</sup>:

<sup>&</sup>lt;sup>2</sup>Some of these instructions contain illegal prefixes; however, remember that we want our decoder to be able to decode all instructions accepted by Intel processors.

```

f3 f2 0f 59 ff mulsd xmm7, xmm7 Mandatory prefix: 0xf2

66 f3 f2 0f 59 ff mulsd xmm7, xmm7 Mandatory prefix: 0xf2

66 f2 f3 0f 59 ff mulss xmm7, xmm7 Mandatory prefix: 0xf3

66 0f 59 ff mulpd xmm7, xmm7 Mandatory prefix: 0x66

f2 66 0f 59 ff mulsd xmm7, xmm7 Mandatory prefix: 0xf2

```

Mandatory prefixes can easily be handled in GDSL by using different decoders, depending on the last relevant prefix. We decode prefixes using the following decoders that encode a state machine with start state "prefixes":

```

val prefixes [0x66] = p/66

val prefixes [0xf2] = p/f2

2

val prefixes [0xf3] = p/f3

val prefixes [] = main

val p/66 [0x66] = p/66

val p/66 [0xf2] = p/66/f2

val p/66 [0xf3] = p/66/f3

val p/66 [] = after /66 main

val p/f3 [0x66] = p/66/f3 #f3 dominates 66

val p/f3 [0xf2] = p/f3/f2

10

val p/f3 [0xf3] = p/f3

11

val p/f3 [] = after /f3 main

12

val p/f3/f2 [0x66] = p/66/f3/f2 #f3/f2 dominates 66

13

val p/f3/f2 [0xf2] = p/f3/f2

14

val p/f3/f2 [0xf3] = p/f2/f3

15

val p/f3/f2 [] = after /f2 (after /f3 main)

16

... #analogous for p/f2, p/66/f2, p/66/f3, p/f2/f3,

17

p/66/f3/f2, p/66/f2/f3

18

val /66 [] = continue #no match, continue with next decoder

19

val /f2 [] = continue #no match, continue with next decoder

20

val /f3 [] = continue #no match, continue with next decoder

21

val /66 [0x0f 0x59 /r] = binop MULPD xmm xmm/m128

22

val /f2 [0x0f 0x59 /r] = binop MULSD xmm xmm/m64

val /f3 [0x0f 0x59 /r] = binop MULSS xmm xmm/m32

val main [...] = ...

```

The entry point that is exported to the user is prefixes. When reading the sequence f3 f2 0f 59 ff, it dispatches to p/f3 which itself reads f2 and enters the decoder p/f3/f2. Since the next byte 0f has no match in p/f3/f2, the expression after /f2

(after /f3 main) is executed. The after function calls the decoder /f2 and, if it fails, continues with (after /f3 main). The latter expression runs f3 and, if this decoder fails, runs main. On our example byte sequence, the /f2 decoder succeeds in consuming the remaining bytes 0f 59 ff and returns the mulsd instruction. By construction of the prefix decoders, at most four decoder calls can fail to make progress, that is be unable to decode at least one further byte: one prefix decoder, plus one call to /66, /f2, and /f3, respectively. Thus, the adherence of the prefix rules only adds a small constant to the runtime complexity of the decoder.

Note that the example code does not contain the logic for recording which prefixes have been seen and are not mandarory, i.e. need to be taken into account to *configure* the decoded instruction. In pratice, this makes the rules a little harder to read:

```

val p/f2/f3 [] = after (with-f2 /f3) (

after (with-f3 /f2) (with-f2 (with-f3 /)))

```

Here, the with-XX calls encapsulate the calls to the decoders and set the respective prefix bits in the global state before calling the decoder passed as parameter. After the call to the decoder, the prefix bits are reset in the state so that they do not interfere with further decoder calls. Observe that after and continue can be defined directly within GDSL:

```

val after fst snd = do update @{cont=snd}; fst end

val continue = do decoder <- query $cont; decoder end</pre>

```

Here, after stores its argument snd in the decoder state and executes the decoder fst. The continue function retrieves the stored decoder and dispatches to it. Note that the main decoder has no default rule calling continue and, thus, fails in case no pattern matches. This completes the design of our prefix decoders.

#### 2.3. Evaluation

Our GDSL decoder handles all 897 (as of September 2012) instructions of the Intel x86 instruction set; we also offer decoders for AVR, MSP430, and a substantial subset of ARMv7. In this section we compare the performance and correctness of the Intel x86 decoder.

| Framework  | Time  | #Instrs | p/f2/f3   | p/66/f2/f3 | REX       |

|------------|-------|---------|-----------|------------|-----------|

| BeaEngine  | 238ms | 672207  | _         | _          | _         |

| distorm    | 204ms | 671991  | _         | _          | _         |

| GDSL       | 673ms | 671991  | $\sqrt{}$ | $\sqrt{}$  | $\sqrt{}$ |

| IDA Pro    | /     | /       | $\sqrt{}$ | _          | $\sqrt{}$ |

| libopcodes | 309ms | 671991  | _         | _          | _         |

| metasm     | 4m21s | /       | _         | _          | $\sqrt{}$ |

| udis86     | 705ms | 673965  | _         | _          | _         |

| xed2       | 338ms | 671991  | $\sqrt{}$ | $\sqrt{}$  |           |

Table 2.2.: Evaluation of different disassembler frameworks.

#### 2.3.1. Performance

We compare the performance of our generated code with several existing disassembler projects. Table 2.2 shows the running time for a linear sweep disassembly of a binary consisting of 671991 instructions in the .text segment. The size of the .text segment was 3032027 bytes. The binary is one of our earlier decoders and is a statically linked x86\_64 executable for Linux. Due to linking libc statically, it included several SSE and VEX instructions. We used BeaEngine [6], distorm [18], IDA Pro [28], libopcodes as shipped in a Debian package [38], metasm [41], udis86 [60], and the xed2 disassembler library that comes with the pintool [63] package. We ran all tests on an Intel Core i7 on Linux in 64-bit mode. The discrepancy in the number of decoded instructions for BeaEngine and udis86 is due to incorrectly decoded instructions which subsequently results in decoding further incorrect instructions due to different offsets.

We included the *metasm* package to complete the comparison with a disassembler not written in C. A possible reason for the results of the *metasm* package being slower is that it does not only do a linear sweep but also resolves symbols and does some control-flow analyses using the decoded instructions. Similarly, we were unable to run a linear-sweep disassembly using *IDA Pro*.

As can be seen from Table 2.2, the generated C code of GDSL is comparable in speed, being about 3 times slower than the fastest hand-written library. Since decoding is unlikely to be a bottleneck in program analysis, we deem the performance acceptable. However, Chapter 5 describes how we apply further optimizations during code generation that help us not only to improve the readability of the generated C code, but also allow us to leverage existing optimizations found in off-the-shelf C compilers.

#### 2.3.2. Correctness

Due to the complications of decoding byte sequences that contain prefix bytes, we compared the various disassemblers for correctness. Table 2.2 features three columns, labelled p/f2/f3, p/66/f2/f3, and REX, which test various prefix combinations as described in Sect. 2.2: p/f2/f3 states if the order of f2 and f3 is honoured, p/66/f2/f3 states if additionally 66 loses its mandatory prefix status once f2 or f3 was read, and REX states if this prefix is correctly ignored if not immediately preceding the opcode. A tick indicates a correct decoder.

According to the Intel manual, adding arbitrary prefixes may result in unpredictable behavior for certain instructions. We created byte sequences whose behaviour is unpredictable according to the manual and verified that an Core i7 processor executes them as if the superfluous prefixes were absent. While it could be argued that decoding sequences that are marked with unpredictable behavior is undesirable for program analysis, such sequences are routinely emitted by the *gcc* compiler which inserts prefixes in front of nop and ret instructions for alignment purposes. As an example, consider the following 14-byte padding sequence that occurred in our test binary:

```

66666662e0f1f840000000000:

nop WORD PTR cs:[rax+rax*1+0x0]

```

Here, four 66 prefixes precede a segment override prefix 2e before a nop opcode f1 f8 follows which takes an elaborate argument. Furthermore, malware may add spurious prefixes as additional code obfuscation technique. Thus, a decoder has to recognize more than what the manual recommends.

On the contrary, certain applications, such as the search for gadgets (byte sequences that form a specific instruction), require that a decoder only recognizes instructions common to all processors. Our GDSL language can use guards from barring certain instructions from being recognized. Certain aspects, such as the difference between 32-bit and 64-bit mode can be implemented using different prefix decoders (the REX prefix is a normal instruction in 32-bit mode). We believe that an open-source implementation of a decoder is likely to converge to a decoder that is correct under all such configurations.

#### 2.4. Related Work

Most decoder libraries for the Intel x86 instructions generate or use tables for mapping opcodes to instructions, however, the decoding of prefixes and arguments is usually hand-coded [38, 6, 18, 41]. One notable exception is *SLED* [45], a specification language

for encoding and decoding, which is a comprehensive specification language similar to GDSL. SLED specifies mnemonics using opcode-centric tables, thereby assigning fixed values to mnemonics. Besides mnemonics, it is possible to define pattern variables that associate names with sequences of bits. The mnemonics and pattern variables are then used to define an instruction. The fields of a pattern variable in such a definition can be specialized using constraints. Since these constraints are rather generic, it is not clear to which extent they can check if the resulting instruction definitions overlap (i.e. that the intersection of the constraint set of one rule with the constraint set of another rule is empty) and, thus, how often it can be avoided that constraints must be tested in sequence in order to find a matching pattern. Their approach is similar to regular expression matching, but without allowing repetition. Since the x86 instruction set allows for multiple and identical prefixes in many, but not arbitrary sequences, certain prefixed instructions are difficult to specify. In particular, the padding example using a nop in Sect. 2.3.2 is difficult to specify using SLED due to the inability to specify repetition. In fact, to our understanding, the specification given in [45] for x86 would not accept any instruction with superfluous prefixes. Even then, the ability of SLED to decode and encode instructions requires the specification to be bi-directional and therefore becomes relatively hard to understand and to maintain.

Another approach was taken by Fox et al. [23]. In their work they describe a formal model of the complete ARMv7 instruction set encoded in the HOL4 proof system [56]. The model directly operates on word sequences, as even the decoding logic is specified in the proof system. Besides mere decoding logic, a full semantics of the ARMv7 instruction set is also provided whose fidelity against an ARMv7 implementation was proved. Since the direct use of the decoder that is written in the HOL4 proof system is difficult, a provably correct translation to GDSL would be desirable.

The next chapter addresses the specification of semantics for which many intermediate representations have been suggested [11, 5, 48]. The expressed goal of GDSL is to also specify how a processor instruction can be translated to an intermediate representation that describes its semantics. Using a common framework can help to make the various intermediate representations comparable and usable in various analysis frameworks. Recently, Reps et al. have proposed to compile an abstract transformer for each processor instruction in order to obtain a more efficient analysis [39]. Future work will address how a different backend to our compiler can follow this setup.

Our implementation of GDSL is available at the website https://github.com/gdslang/gdsl-toolkit. It is written in SML/NJ v110.74 and released under a BSD license.

```

Decl

export <u>id</u>: Type

export decl.

type \underline{id} = \underline{con} (of \mathbf{Type})? (\underline{\perp} \underline{con} (of \mathbf{Type})?)^*

type decl.

type id = Type

type abbrev.

function decl.

\underline{val} \underline{id} \underline{id}^* = \mathbf{Expr}

\underline{val} \underline{id} [ \mathbf{TokPat}^* ] \underline{=} \mathbf{Expr}

decoder decl.

\underline{val} \underline{id} [ \mathbf{TokPat}^* ] ( | \mathbf{Expr} \underline{=} \mathbf{Expr} )^+

guarded dec.

::= <u>hex-num</u> | <u>id</u> | <u>'</u> BitPat * <u>'</u>

TokPat

single token

::= \underline{int} | \underline{l} \underline{num} \underline{l} | \underline{id}

Type

{ field : Type ( , field : Type )* }

( TypeList ) <u>-></u> Type

\underline{S} Type \underline{<} Type \underline{>} Type \underline{>}

action type