### Fakultät für Physik Lehrstuhl für experimentelle Physik E18

# The Neutron-Lifetime Experiment PENeLOPE and the Intelligent FPGA Data Acquisition Framework IF-DAQ

#### Dominic Maximilian Gaisbauer

Vollständiger Abdruck der von der Fakultät für Physik der Technischen Universität München zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigten Dissertation.

Vorsitzender: Prof. Dr. Andreas Weiler

Prüfer der Dissertation:

1. Prof. Dr. Stephan Paul

2. Prof. Dr. Lothar Oberauer

Die Dissertation wurde am 13. Mai 2019 bei der Technischen Universität München eingereicht und durch die Fakultät für Physik am 18. Juli 2019 angenommen.

## **Abstract**

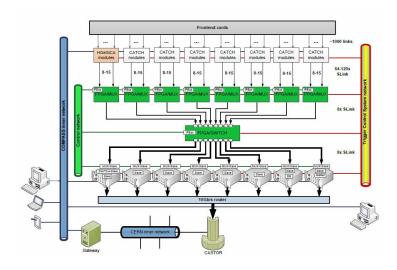

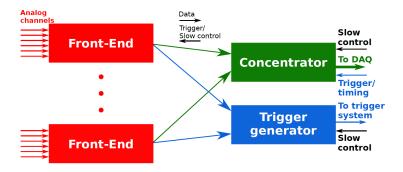

The neutron lifetime  $au_n=879.6\pm0.8$  s is an important parameter in the Standard Model of particle physics and in Big Bang cosmology. Several systematic corrections of previously published results reduced the PDG world average by several seconds in the last years together with a measurement difference of several seconds between the beam type experiments and the storage experiments call for a new experiment. At the Technische Universität München a new Precision Experiment on Neutron Lifetime Operating with Proton Extraction is currently under construction. It aims to determine the neutron lifetime with a precision of 0.1 s. It will confine ultra-cold neutrons in a magneto-gravitational trap using superconducting magnets and will measure their lifetime by both neutron counting and online detection of decay protons. In this thesis I will present the progress I have made on the experiment during this time. Recently, a lot of advances have been made to create a framework which enables an simplified construction of data acquisition systems for new and existing experiments. This framework, intelligent FPGA DAQ framework, is developed at the Technische Universität München and includes several FPGA cards for measuring times, digitize analog signals or process detector data digitally. Additionally, the framework includes an event builder and a newly developed communication framework for the communication between different FPGA modules. The second part of the thesis will introduce the iFDAQ framework and the progress which has been achieved there by myself in this area.

## Zusammenfassung

Die Neutronenlebensdauer  $au_n = 879.6 \pm 0.8$  s ist ein wichtiger Parameter im Standardmodell der Teilchenphysik und in der Untersuchung des Urknalls. Nachdem in den letzten Jahren einige Experimente ihre alten Daten korrigiert haben, reduzierte sich die Lebensdauer des Neutrons, veröffentlicht von der PDG, um einige Sekunden. Dies, zusammen mit der Diskrepanz zwischen Strahl- und Speicherexperimenten, verlangt nach einem neuen Experiment mit besserer Systematik. An der Technischen Universität München befindet sich das "Precision Experiment on Neutron Lifetime Operating with Proton Extraction Experiment" im Aufbau. Dieses benutzt eine Speicherflasche für ultrakalte Neutronen, bestehend aus supraleitenden Spulen. Das Besondere an diesem Experiment ist die Kombination der Neutronenzählung zusammen mit der Detektion der Zerfallsprotonen. Diese Kombination führt dazu, dass das Experiment eine Genauigkeit von 0.1 s erreichen will. Diese Dissertation erläutert die Arbeiten, die ich während meiner Promotion an diesem Experiment ausgeführt und den Fortschritt, den ich hierdurch bislang erreicht habe. In der letzten Zeit floß viel Arbeit in die Entwicklung einer Rahmenstruktur, die es ermöglichen soll neue und alte Datennahmesysteme zu errichten oder zu ersetzen. Diese Rahmenstruktur heißt intelligent FPGA DAQ und wird an der Technischen Universität München entwickelt. Dazu gehören FPGA Module um Zeiten zu messen, analoge Signale in digitale umzuwandeln oder digitale Daten weiter zu verarbeiten. Weiterhin wurde in diesem Zuge ein neues Datenübertragungsprotokoll entwickelt, welches die Kommunikation zwischen zwei FPGA Karten erleichtern soll. Der zweite Teil dieser Dissertation wird iFDAQ einführen und detailiert beschreiben, welche Entwicklungen ich während meiner Promotion dort erbracht habe.

## **Contents**

| I<br>Pr |                   |                                              | Experiment on Neutron Lifetime Operating action                                                                                        | with | 9                                            |

|---------|-------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------|

| 1       | 1.1<br>1.2<br>1.3 | Ultra-c                                      | eutron                                                                                                                                 |      | 10<br>10<br>11<br>13<br>14<br>14<br>15<br>17 |

| 2       | UCN               | l Prepa                                      | ration                                                                                                                                 |      | 22                                           |

| _       | 2.1               | Polariz<br>2.1.1<br>2.1.2                    |                                                                                                                                        |      | 22<br>22<br>23                               |

|         | 2.2               | Spin F<br>2.2.1<br>2.2.2                     |                                                                                                                                        | <br> | 25<br>25<br>25                               |

|         | 2.3               | Qualific<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | cation Measurements                                                                                                                    |      | 26<br>26<br>27<br>29<br>29                   |

| 3       | Mag               | neto-G                                       | ravitational Trap                                                                                                                      |      | 32                                           |

|         | 3.1<br>3.2        | Superd                                       | conductor VSF-SSCI et Training  Quench Protection  Coil Test Experiment  Prototype Coil  Triple Coil Stack  Inner Coil  PENeLOPE Light |      | 32<br>34<br>34<br>36<br>38<br>39<br>40<br>42 |

| 4       | Cen               | tral Coi                                     | il                                                                                                                                     |      | 46                                           |

| 5       | Abs               | orber                                        |                                                                                                                                        |      | 50                                           |

| 6  | Prot | on Det  | ector                                                    | 53 |

|----|------|---------|----------------------------------------------------------|----|

|    | 6.1  | Detect  | or Architecture                                          | 54 |

|    | 6.2  | Large   | Area Avalanche Photodiodes                               | 55 |

|    | 6.3  | Analog  | g Electronics                                            | 58 |

|    |      | 6.3.1   | Bias Voltage Supply Board                                | 59 |

|    |      | 6.3.2   | Preamplifier Board                                       | 60 |

|    |      | 6.3.3   | Shaper Board                                             | 62 |

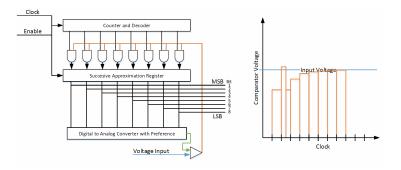

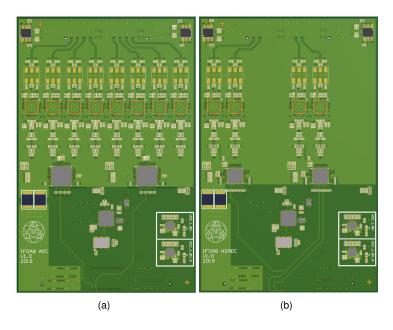

|    |      | 6.3.4   | Analog-To-Digital Converter Board                        | 63 |

|    | 6.4  | Digital | Electronics                                              | 67 |

|    |      | 6.4.1   | Voltage Distribution Board                               | 67 |

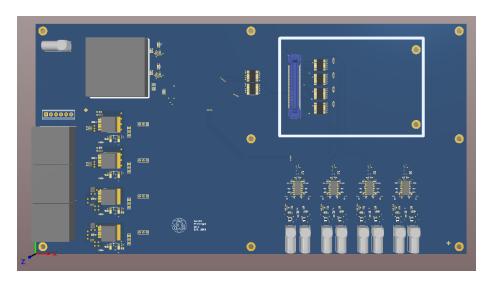

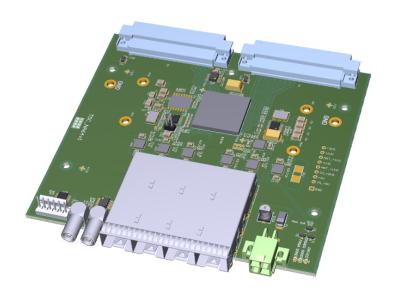

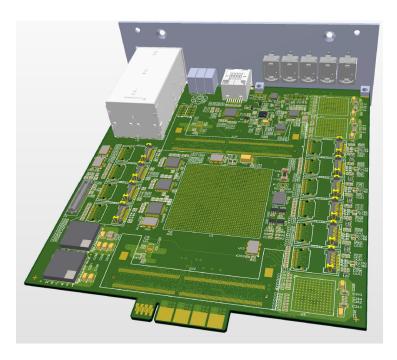

|    |      | 6.4.2   | Signal Detection Unit                                    | 70 |

|    |      | 6.4.3   | Network Access Controller                                | 75 |

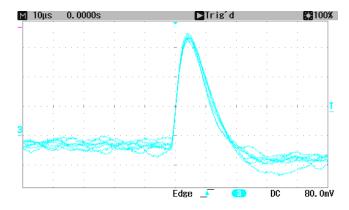

|    | 6.5  | Qualifi | cation Measurements                                      | 75 |

|    |      | 6.5.1   | Simulation                                               | 76 |

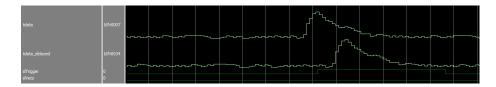

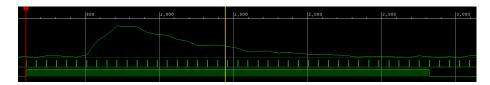

|    |      | 6.5.2   | Signal Generator                                         | 78 |

|    |      | 6.5.3   | Conclusion                                               |    |

|    |      |         |                                                          |    |

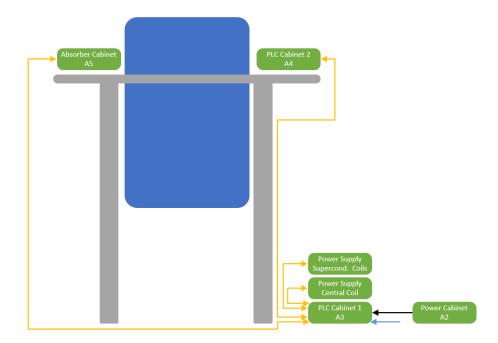

| 7  | Exp  | erimen  | t Control                                                | 79 |

|    | 7.1  | Overvi  | ew                                                       | 79 |

|    | 7.2  | Power   | Cabinet - A2                                             | 79 |

|    | 7.3  | PLC C   | Cabinet - A3                                             | 81 |

|    |      | 7.3.1   | Power Supply                                             | 81 |

|    |      | 7.3.2   | Network Connections                                      | 82 |

|    |      | 7.3.3   | Industry PC                                              | 82 |

|    |      | 7.3.4   | UCN Infrastructure                                       | 83 |

|    |      | 7.3.5   | Vacuum Infrastructure                                    | 84 |

|    |      | 7.3.6   | PLC                                                      | 84 |

|    |      | 7.3.7   | PLC Module List                                          | 85 |

|    | 7.4  | PLC C   | Cabinet - A4                                             | 85 |

|    |      | 7.4.1   | Power Supply                                             | 88 |

|    |      | 7.4.2   | Network Connections                                      | 88 |

|    |      | 7.4.3   | Vacuum Infrastructure                                    | 88 |

|    |      | 7.4.4   | Temperature Infrastructure                               | 88 |

|    |      | 7.4.5   | Cryogenic Infrastructure                                 |    |

|    |      | 7.4.6   | High-Voltage Infrastructure                              |    |

|    |      | 7.4.7   | Safety Infrastructure                                    | 89 |

|    |      | 7.4.8   | PLC Module List                                          | 90 |

|    | 7.5  |         | per Cabinet - A5                                         |    |

|    |      |         |                                                          |    |

|    |      | - 112   | of EDOA Data Association E                               | ٠. |

| II | Into | ellige  | nt FPGA Data Acquisition Framework                       | 94 |

| 8  | On 1 | Γhe Wa  | y Towards an Intelligent FPGA Data Acquisition Framework | 95 |

| ۵  | Time | -to Di  | nital Convertor                                          | 97 |

| 9  |      | -       | gital Converter                                          | _  |

|    | ع. I | ⊓aruw   | are                                                      | 97 |

| 10 | Ana  | log-to- | Digital Converter                                        | 99 |

| -  |      |         | C 40/80 MSPS                                             |    |

|    | 10.2 MSADC 80 MSPS                                                                                                                                                            |                                        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

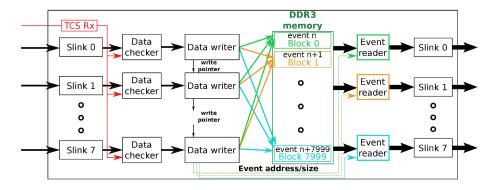

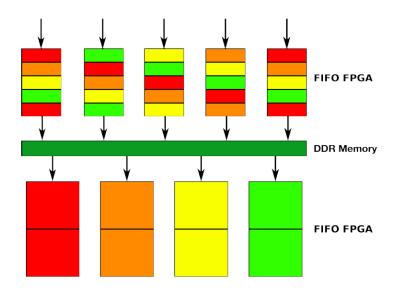

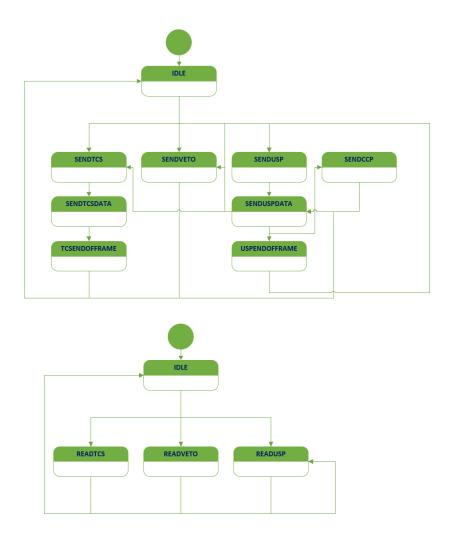

| 11 | Event Builder                                                                                                                                                                 | 101                                    |

| 12 | Multi-purpose FPGA card  12.1 Architecture  12.1.1 FPGA  12.1.2 Power Supply  12.1.3 Clocking  12.1.4 Flash  12.1.5 Memory  12.1.6 High-Speed Serial Links  12.2 Carrier Card | 104<br>104<br>105<br>106<br>106<br>106 |

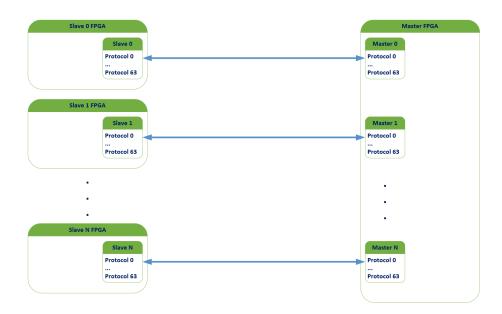

| 13 | Unified Communication Framework  13.1 Introduction                                                                                                                            | 111                                    |

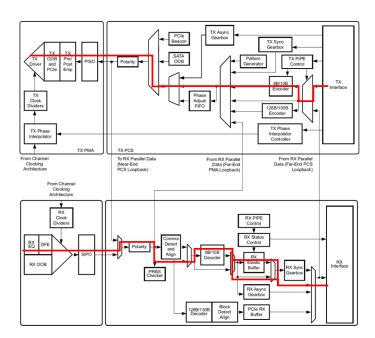

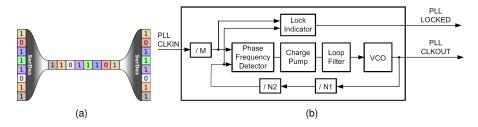

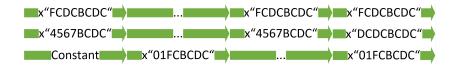

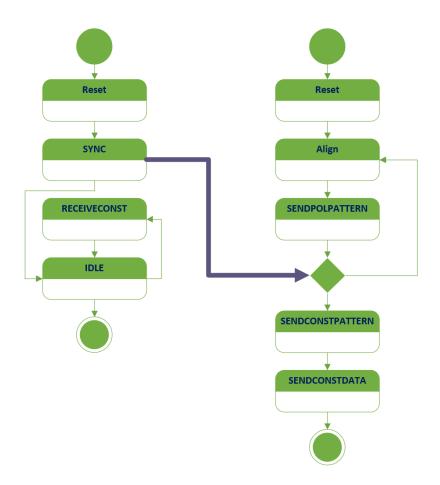

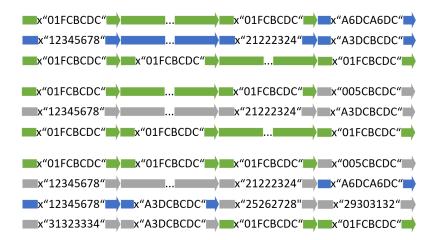

|    | 13.2 Transport Layer Protocol  13.2.1 High-Speed Transceiver  13.2.2 Initialization  13.2.3 Frame Transmission and Priority Handling  13.2.4 Veto  13.2.5 Clock Correction    | 112<br>118<br>118<br>120               |

|    | 13.3 Configuration  13.3.1 Instantiation  13.3.2 Reference Clocking  13.3.3 User Interface Clocking  13.3.4 Reset Structure                                                   | 122<br>122<br>124<br>126               |

|    | 13.4 Simulation                                                                                                                                                               | 127<br>128<br>129                      |

|    | 13.7 References                                                                                                                                                               | 129                                    |

| 14 | Conclusions and Outlook  14.1 Conclusion of PENeLOPE  14.2 Outlook  14.3 Conclusion of iFDAQ  14.4 Outlook of iFDAQ  14.5 Own Contributions                                   | 131<br>132<br>132                      |

## Part I

## Precision Experiment on Neutron Lifetime Operating with Proton Extraction

## **Chapter 1**

## Introduction

#### 1.1 The Neutron

In the year 1930 Walter Bothe and Herbert Becker [5] shot alpha particles from the radioactive decay of polonium onto beryllium and observed an untypical neutral radiation. By mistake, they took it as gamma radiation despite the fact that it showed strange behavior like accelerating of light particles which would lead to gamma energies way to high. One year after, the Curies used the radiation in an ionization chamber without any significant current flow [8]. The experiments of the Curies motivated Chadwick in 1932 [7] to prove, in a series of experiments, that the radiation consists of particles with a mass very close to that of a proton. His discovery led to the Nobel prize in 1935.

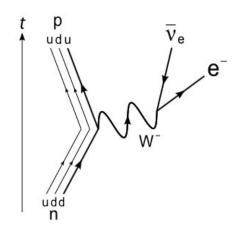

Figure 1.1: Feynman diagram of the neutron decay.

Nowadays, we know that a neutron is an electrically neutral baryon with a mass of 1.00866491588~u [52] where u is the atomic mass unit. The neutron consists of one up quark and two down quarks as shown in fig. 1.1. If it is bound within a

nucleus, the neutron is stable but when unbound, the neutron decays through weak interaction with a decay energy of  $0.782343~{\rm MeV}$  [52].

$$n^0 \to p^+ + W^- \to p^+ + e^- + \bar{v}_e$$

(1.1)

This involves the changing of one down into an up quark by emitting a short lived  $W^-$  boson, which by itself decays into an electron and electron anti-neutrino. Most of the decay energy is transferred to the electron which has a maximum kinetic energy of  $0.782\pm13~$  MeV [52].

#### 1.2 Ultra-cold Neutrons

Free neutrons are typically produced in spallation sources or fission reactors. In spallation sources typically a tungsten or tantalum target is shot with an accelerated particle beam. The beam produces free neutrons by the spallation process within the target. Fission reactors commonly use uranium 235 which is bombarded by free neutrons and, by this, decays then into fission products with a mass around 95 and 135 u plus some additional neutrons which by themselves can induce more fission of uranium. This chain reaction leads to a continuous operation of nuclear fission reactors. Neutrons produced in both spallation source and fission reactor are typically in the energy range of several MeV. A classification of the neutron by velocity and energy range can be found in table 1.1.

| Class      | Energy [eV] Velocity [m/s        |      |

|------------|----------------------------------|------|

| Fast       | $10\cdot 10^3$ to $20\cdot 10^6$ | >    |

| Thermal    | $\approx 10 \cdot 10^{-3}$       | 2200 |

| Cold       | $10^{-3}$                        | 400  |

| Very Cold  | $10^{-6}$                        | 100  |

| Ultra-cold | $100 \cdot 10^{-9}$              | 5    |

Table 1.1: Classification of neutrons in energy and velocity regimes according to Golub [21].

Fast neutrons produced in neutron sources are moderated to the thermal energy regime by elastic scattering. Due to their long wavelength (several angstroms) thermal neutrons can be described as a material wave and are reflected by material walls under very small glancing angles. The total reflection of such a neutron beam can be enhanced by multilayer coating of the glass guides with nickel and titanium . In order to obtain even slower neutrons they first have to be moderated further by e.g. liquid deuterium at  $25~\rm K$  to reach the cold and very cold energy regime. To get to even lower energies of less than  $300~\rm neV$  several methods have been implemented in ultra-cold neutron (UCN) sources around the world. At the Institut Laue-Langevin (ILL) in Grenoble very cold neutrons with an average speed of  $50~\rm m/s$  are extracted by a curved vertical guide from the reactor core and guided towards a turbine rotating at  $25~\rm m/s$ . The neutrons are reflected on the turbine wheels

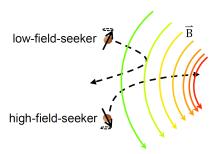

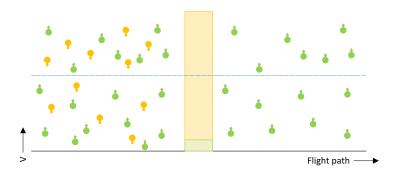

and are Doppler-shifted towards lower energies [50]. Another form of UCN source uses the super-thermal conversion process ([20]) where pre-moderated neutrons excite solid state excitations - mainly phonons - within the lattice of a solid state converter. If an incoming neutron scatters of the lattice and excites such a phonon, it can loose nearly all of its energy and reach the ultra-cold energy regime. This process is called down-scattering. Also the inverse process - up-scattering - is possible, where an excited phonon transfers its energy onto an ultra-cold neutron and by this accelerates it. In order to reduce such an up-scattering process the moderators are cooled to cryogenic temperatures. Examples for these sources are [16], [28] and [34] which either use super-fluid helium or frozen deuterium as a moderator. Ultra-cold neutrons interact with gravitation, magnetic fields, the weak force and the strong force. In interaction with gravitation UCN can gain or loose depending on the direction of movement 102.51945556(64) neV/m [21]. Magnetic fields interact with the magnetic moment of the neutron with 60.307740(15) neV/T [21]. Depending on the orientation of their magnetic moments in a magnetic field the neutrons are either attracted by large gradients - high-field-seekers (HFS) - or repelled by large gradients - low-field-seekers (LFS) - as can be seen in fig. 1.2.

Figure 1.2: Flight path of high-field and low-field-seekers in a magnetic field [39].

The wavelength of UCN can be calculated with the De-Broglie equation  $\lambda=\frac{h}{m_nv_n}$  where  $m_n$  is the mass of the neutron,  $v_n$  the velocity and h the Planck's constant. UCN thus have large wavelengths of more than 50 nm. If a UCN scatters on a material it will only see the combination of the nucleon interaction potentials since it has only a very short range in the order of 2 fm. Fermi [14] introduced an effective Fermi-Potential

$$V = \frac{2\pi\hbar^2}{m} N_A \tag{1.2}$$

describing the interaction of UCN with material. In the calculation of the effective wall potential in the equation above m is the mass of the neutron and  $N_A$  is the Avogrado's constant. UCN with energies less than this effective potential will be reflected under any angle of incidence. Table 1.2 lists the Fermi-Potential of some materials. Elements with a negative potential are very effective UCN absorbers. The critical velocity - below which the UCN are totally reflected from a material -

can be calculated from the Fermi-Potential via the equation  $v_c=\sqrt{\frac{2V}{m_n}}$  where  $m_n$  is the mass of the neutron.

| Material         | Fermi-Potential [neV] |

|------------------|-----------------------|

| <sup>58</sup> Ni | 335                   |

| $^{nat}Ni$       | 252                   |

| Fe               | 210                   |

| Cu               | 168                   |

| Al               | 54                    |

| Ti               | -48                   |

Table 1.2: List of Fermi-Potential values of different materials from Golub [21].

#### 1.3 Neutron Lifetime

Free unbound neutrons decay due to the weak interaction with a decay time of  $879.6 \pm 0.8~s$  [52]. Since they interact with all forces except for electric ones the neutrons are a perfect tool for manifesting the Standard Model of physics and for investigating the Big Bang nucleosynthesis.

#### 1.3.1 Standard Model of Particle Physics

Within the Standard Model of particle physics the unitarity of the Cabibbo-Kobayashi-Maskawa (CKM) matrix is predicted. The CKM matrix describes the mixing of quarks of three flavor generations when interacting via the weak interaction. Thus the mixing of the mass eigenstates d, s and b into the weak eigenstates d', s' and b' can be described with the following equation.

$$\begin{pmatrix} d' \\ s' \\ b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix}.$$

(1.3)

The neutron lifetime  $\tau_n$  is inversely dependent on the squared matrix element  $V_{ud}$  since it is dependent on the conversion of a down quark into a up quark.

$$|V_{ud}|^2 = \frac{(4908.7 \pm 1.9)s}{\tau_n (1 + \lambda^2)} \tag{1.4}$$

In the equation above the numerator is a collection of radiative corrections and constants and  $\lambda=\frac{g_A}{g_V}$  is the ratio of the axial vector and vector coupling. The latter can be calculated precisely with results of experiments like PERKEO I-III ([10], [42], [36]). Currently, the most precise value for  $V_{ud}$  is  $0.97420\pm0.00021$  [52] but new experiments like PENeLOPE and PERC [33] will improve the error down by one order of magnitude if they meet their claimed precision.

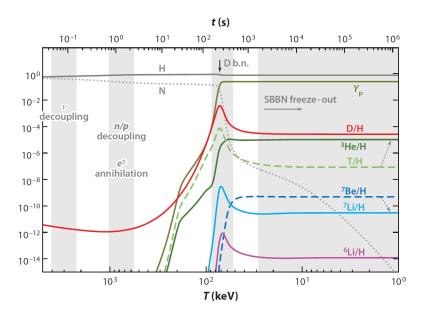

#### 1.3.2 Big Bang Nucleosynthesis

The Big Bang Nucleosynthesis (BBN) describes the formation and abundances of light elements at a very early stage of the universe with the help of Standard Model physics. When the energy of the universe was much higher than 1 MeV the reactions

$$n + \nu_e \to p + e^- \tag{1.5}$$

$$p + \bar{\nu}_e \to n + e^+ \tag{1.6}$$

were in a thermal equilibrium leading to a neutron to proton ratio of  $\frac{n}{p}=e^{\frac{Q}{T}}=1.$  Here n and p are the amount of neutrons and protons, Q is the mass difference between the n and the p and T the temperature. At an energy of about  $1~{\rm MeV}$  the reactions above where no longer in an equilibrium and the ratio was dominated by the neutron decay (compare fig. 1.3). Starting from the freeze-out until nuclear reactions began the neutron to proton rate shifted from 1:6 to 1:7 by the decay. Approximately 100 seconds after the Big Bang or at an energy of below 0.1 MeV the threshold of photo-dissociation for the deuterium was undershot and deuterium started to form by the reaction

$$n + p \to d + \gamma. \tag{1.7}$$

From the deuteron heavier elements could form and mostly ended up in  $^4{\rm He}$  which is the most stable light element in the early universe at that time. The abundance of the  $^4{\rm He}$  can be described by the equation

$$Y_p = \frac{2n/p}{1 + n/p}. (1.8)$$

The neutron lifetime in fact has an impact on the BBN in two ways. Firstly, it describes the time of the freeze out ( $t\approx 1~{\rm s}$ ) by changing the weak interaction rates and secondly, it defines the rate of neutron decays between the freeze out and the light element formation ( $t\approx 100~{\rm s}$ ) and by this has an impact on the equation above.

#### 1.3.3 Lifetime Measurements

The measurement of the neutron lifetime can be divided into two kinds of experiments - beam experiments and storage experiments.

Figure 1.3: Time and temperature evolution of all standard big bang nucleosynthesis (SBBN)-relevant nuclear abundances [41]

#### **Beam Experiments**

In beam experiments the neutron lifetime is determined from the rate of the neutron decay products (protons and electrons) extracted from a neutron beam. A sketch of the experiment of Nico et al. ([37]) is shown as an example of this kind of experiment in fig. 1.4 a. Typically, the electrons and protons are guided via magnetic fields outside of the beam onto the detectors whereas the remaining neutrons can be stopped in a beam dump. For a precise measurement the decay volume, the neutron intensity and the proton and electron extraction and detection efficiency must be known precisely. Examples for this type of experiment are listed in table 1.3. Currently, the average of these most recent and precise experiments is  $886.9\pm1.2\pm2.8\ s.$

| Year | Group            | Lifetime [s]                 |

|------|------------------|------------------------------|

| 2013 | Yue et al. [58]  | $887.7 \pm 1.2 \pm 1.9 \ s$  |

| 2005 | Nico et al. [37] | $886.3 \pm 1.2 \pm 3.2 \; s$ |

| 2003 | Dewey et al. [9] | $886.8 \pm 1.2 \pm 3.2 \ s$  |

Table 1.3: Neutron lifetime experiments using neutron beams. The lifetimes are given with systematic error in the first place and a statistical in the second.

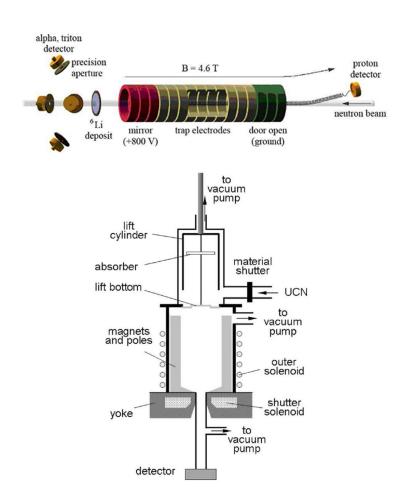

#### Storage Experiments

Storage experiments fill e.g. ultra-cold neutrons into a gravitational, magnetic, material or combined trap and store them there for a specific time. After different storage times the remaining neutrons are extracted and counted. Together with the precise knowledge of the incoming neutron density or a constant neutron flux over the different storage times the lifetime can be determined precisely. Examples for this type of experiment are shown in table 1.4 and as an example sketch the experiment of Ezhov et al. ([13]) is shown in fig. 1.4 b. Currently, the average of these most recent and precise experiments is  $879.9 \pm 0.87^{+0.83}_{-0.8}$  s.

| Year | Group                  | Lifetime [s]                    |

|------|------------------------|---------------------------------|

| 2018 | Ezhov et al. [12]      | $878.3 \pm 1.6 \pm 1.0 \ s$     |

| 2018 | Pattie et al. [38]     | $877.7 \pm 0.7^{+0.4}_{-0.2} s$ |

| 2018 | Serebov et al. [48]    | $881.5 \pm 0.7 \pm 0.6 \ s$     |

| 2012 | Steyerl et al. [51]    | $882.5 \pm 1.4 \pm 1.5 \ s$     |

| 2010 | Pichlmaier et al. [40] | $880.7 \pm 1.3^{\pm}1.2 \ s$    |

| 2005 | Serebov et al. [47]    | $878.5 \pm 0.7 \pm 0.3 \ s$     |

Table 1.4: Neutron lifetime experiments using neutron beams. The lifetimes are given with systematic error in the first place and a statistical in the second.

#### Conclusion

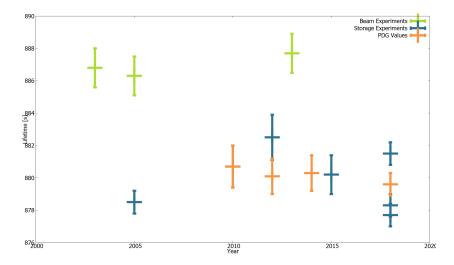

As can be seen from fig. 1.5 there is a clear difference between the results of beam and storage experiments. Together with an error of nearly one second on the most recent PDG value of  $\tau_n=879.6\pm0.8~s$  this is a reasonable motivation for a new precise neutron lifetime experiment. Currently, the PDG mean lifetime is mostly determined by storage experiments.

#### 1.4 PENeLOPE

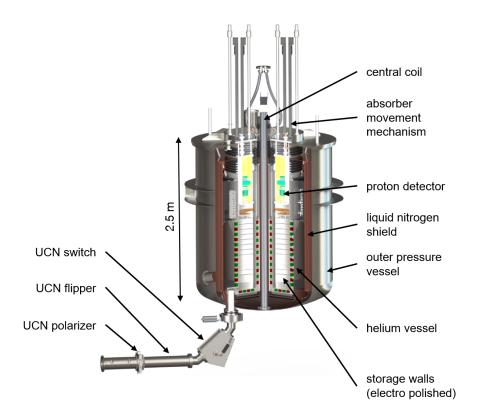

The Precision Experiment on **Ne**utron Lifetime **O**perating with **P**roton Extraction (PENeLOPE) combines the advantages of a storage experiment and that of a beam experiment (especially monitoring of the decay particles) into one measurement aiming for a precision of less than  $0.1~\rm s$ . Fig. 1.6 shows a CAD model of the experiment. The center of the experiment is a magneto-gravitational trap for UCN consisting of twenty-four superconducting coils with an overall height of one meter and an equal diameter. The principle of magnetic storage is more favorable than storing neutrons in a material bottle due to better storage times and easier error handling. Due to the large alternating current directions within the different coils and the gravitation, a storage potential for UCN of up to  $115~\rm neV$  is created which follows the equation  $V = m_n gz + \mu_n B$  in a height z above the bottom of the trap. The UCN have to be polarized and spin flipped before entering the trap as low-field-seekers which can be stored nearly without losses. In some areas of the storage volume the

Figure 1.4: (a) Neutron lifetime beam experiment of Nico et al. ([37]). (b) Neutron lifetime storage experiment of Ezhov et al. ([13]).

topology of the coils can lead to zero field areas. These zero field areas can turn the LFS into HFS, which in turn can lead to losses of UCN and by this to a distortion of the measurement. To overcome this, a large central current is running vertically through the middle of PENeLOPE creating an azimuthal field overlaying the zero field areas. Due to the fact that the coils have a defined time for ramping to nominal current the LFS can turn into HFS by hitting the walls. These marginally trapped neutrons can shift the measurement to an effective lifetime which is lower than the real lifetime by hitting the wall during the measurement and leaving the trap. To clean up the high-field-seekers from the spectrum an absorber mechanism is also installed in the cryostat. The storage volume itself is covered by a proton detector counting the protons from the decay. It is placed on a high electrical potential in order to guarantee a sufficient extraction of protons out of the trap.

A typical experimental cycle of PENeLOPE can be found in table 1.5 and starts with the filling of the UCN from the source. When the UCN are filled, the magnets start to ramp up to generate the storage potential. This phase is then followed by the movement of the absorber removing the remaining HFS. Afterwards, the

Figure 1.5: Most recent and precise neutron lifetime experiments with beam experiments marked in green and storage experiments in blue. All experiments plotted here are included in the PDG averages marked in orange.

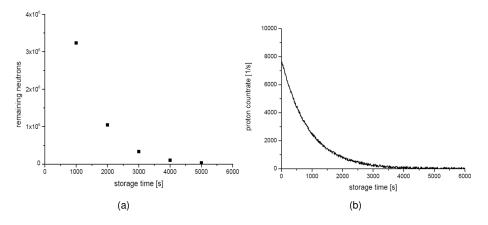

UCN will be stored for different storage times. The ramping down of the magnets after the storage time is followed by the counting of the remaining neutrons. If this cycle is repeated several times and the count values are inserted into a graph plotting storage time versus the number of remaining neutrons, the decay curve of the neutron can be seen (compare fig. 1.7). For each point in this graph the proton count rate can be monitored over time and also here the decay curve is clearly visible following the equation  $N(t) = N_o \cdot e^{-\frac{t}{\tau_n}}$ . The following chapters will describe all parts of PENeLOPE in more detail. Starting with the UCN preparation in chapter 2, followed by the magneto-gravitational trap and all superconducting coil tests in chapter 3, the central coil in chapter 4, the absorber in chapter 5, the proton detector in chapter 6 and the experiment control in chapter 7. Error corrections for the lifetime measurement and impact assessments of different error sources have been done and can be found in [45]. They are not part of this thesis.

|   | Stage        | Duration [s]          |

|---|--------------|-----------------------|

| 1 | filling      | $\sim 200$            |

| 2 | ramping up   | 100                   |

| 3 | cleaning     | 150                   |

| 4 | storage      | variable up to $5000$ |

| 5 | ramping down | 100                   |

| 6 | emptying     | $\sim 200$            |

Table 1.5: Experimental stages of PENeLOPE

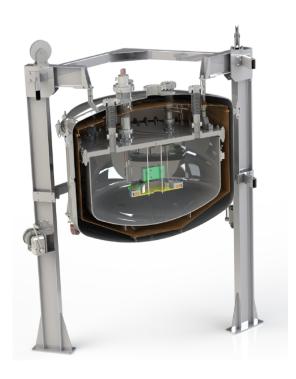

Figure 1.6: CAD model of the PENeLOPE cryostat. On the lower left all parts concerning the UCN guiding like the polarizer, flipper and switch are depicted. In the center of the picture is the LHe cryostat with the superconducting coils surrounded by the thermal radiation shield and the vacuum tank. In the upper part of the picture the absorber and additional instrumentation is shown.

Figure 1.7: Decay curve of the neutron with storage measurements (a) and proton measurements (b). The error bars are hidden within the simulated points.

## **Chapter 2**

## **UCN Preparation**

Due to the design of the PENeLOPE experiment a precision of less than  $0.1~\rm s$  in the neutron lifetime measurement is only possible if the UCN from the source are polarized and turned into low-field-seekers by a spin flipper before being stored in the trap. According to [45] the polarization has to be approximately  $90~\rm \%$ . If the polarization is less and too many high-field-seekers enter the trap they could introduce a large systematic effect (about  $0.7~\rm s$  [45]) on the measurement. The following sections will describe the theory and the hardware of the polarizer and the spin flipper and end with the results of the beam measurement in the TRIGA reactor in Mainz.

#### 2.1 Polarization

#### 2.1.1 Theory

Depending on the direction of the magnetic moment of the UCN mentioned in 1.2 they will observe a potential of

$$V = \pm \mu_n |B| \tag{2.1}$$

in a strong magnetic field. If UCN pass through a magnetically saturated iron foil they are exposed to a potential of

$$V = V_{Fermi} \pm \mu_n B \tag{2.2}$$

again depending on the orientation of the magnetic moment with respect to the field. It can be seen that the low-field-seeker will see a potential barrier of  $V=V_{Fermi}+\mu_n B$  and high-field-seeker will observe a potential well of  $V=V_{Fermi}-V_{Fermi}$

$\mu_n B$ . In order to achieve a high transmission for the high-field-seeker and a low transmission for the low-field-seeker - which will then result in a large degree of polarization - the potential well should ideally vanish. Fig. 2.1 illustrates the potential barrier and well. [23] and [30] showed that a certain mixture of iron and cobalt ( $Fe_{0.5}Co_{0.5}$ ) would have a polarization of more than 90 %. With the iron and cobalt mixture the potential well would be  $V=135-60.3\cdot 2.4=9.72$  neV and the potential barrier would be  $V=135+60.3\cdot 2.4=279.72$  neV.

Figure 2.1: The potential barrier seen by LFS in orange and the potential well seen by HFS in green. The dashed blue line is the Fermi potential of the polarizer foil.

#### 2.1.2 Hardware

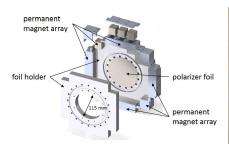

The polarizer designed by [45] is shown in fig. 2.2 as a picture and a CAD model. On both sides it has the possibility to either connect a standard stainless steel UCN guide or a Replika UCN guide which is a rolled sheet of a nickel vanadium mixture  $(Ni_0.93V_0.07)$  within a stainless steel vacuum tube. The centerpiece of the polarizer are two stainless steel blocks (1.4401 /EN10088-2 - non magnetizing stainless steel) which press the polarizer foil within their center. The foil itself is made from aluminum and is coated with  $150~\rm nm$  of the iron mixture mentioned in section 2.1.1. Aside from being the backing material the aluminum foil separates the vacua before and after the polarizer which is crucial for PENeLOPE where the UCN guide system will have a vacuum of about  $10^{-4}~\rm mbar$  whereas the experimental vacuum is in the region of  $10^{-8}~\rm mbar$ . [45] calculated a minimum transverse magnetic field of  $10~\rm mT$  in order to saturate the iron foil. A minimum field of  $13.4~\rm mT$  is produced by a Halbach array of eight permanent NdFeB magnets oriented around the polarizer holder.

For holding the polarity and preventing undesired spin flips behind the polarizer a holding field must be generated surrounding the guide until the neutrons enter the storage volume. The holding field is generated by three pairs of Helmholtz coils shown in fig. 2.3. They generate a minimum field of 1 mT which is sufficient according to [45] to hold the polarity.

Figure 2.2: (a) CAD model of the polarizer. (b) Picture of the polarizer (size  $40 \text{ cm} \times 40 \text{ cm}$ ).

Figure 2.3: Picture of the Helmholtz coils designed by [45].

#### 2.2 Spin Flipper

#### 2.2.1 Theory

A combination of both - static and dynamic - magnetic fields for changing the spins is the fundamental principle of the nuclear magnetic resonance. A device from this technology is the adiabatic fast passage (AFP) spin flipper used for UCN spin changes. The AFP consists of a static field perpendicular to the direction of motion of the UCN and a rotating field oscillating around the direction of motion ([23],[19]). Another version of the AFP has a static field parallel to the direction of motion of the UCN and the oscillating field is perpendicular to it ([25]). For PENeLOPE the first version is preferable since it is easier to implement. The effective field seen by the neutron is described by

$$B_{\text{effective}} = \left(B_0 - \frac{\omega}{\gamma_n}\right) \cdot \mathbf{z} + B_1 \cdot \mathbf{x}$$

(2.3)

where  $\gamma_n=1.83247172\frac{1}{sT}$  ([52]) is the gyro-magnetic ratio of the neutron. If the

oscillation frequency of the magnetic field  $B_1$  is in the order of the Lamor frequency, the equation above will change to  $B_0=\frac{\omega}{\gamma_n}$  and the neutron is in a resonance point which will lead to a inversion of its spin with respect to the field  $B_0$ .

#### 2.2.2 Hardware

The AFP spin flipper is enclosed by the Helmholtz coils described in section 2.1.2 which, according to [45], have a static field  $B_0$  of 1 mT in their center. This field leads to a resonance frequency of

$$B_0 = \frac{\omega}{\gamma_n} \to f = \frac{\gamma_n B_0}{2\pi} = 29.165 \ kHz.$$

(2.4)

The oscillating coil is a cylindrical solenoid wound onto a coated glass tube which is used as an UCN guide. It is coated with nickel and molybdenum ( ${

m Ni}_{0.85}{

m Mo}_{0.15}$ ). According to [45] the flipper coil must produce a peak magnetic field of at least 0.05 mT. Following the equation

$$B = \mu_0 \frac{\text{IN}}{\text{L}} \tag{2.5}$$

for air filled cylinder coils the coil consists of 20 windings N on a length L of 160 mm. Together with a current I of 2.5 A this leads to a minimum field of 0.39 mT. The impedance of this coil which is wound with some distance between the windings is  $38~\mu{\rm H}$  leading to an impedance of  $2\pi fL = 6.96~\Omega$ . This perfectly matches the impedance of the commercial Reloop Dominance 702 audio amplifier ([2]) used by [45] in the previous spin flipper design. Together with a standard sine frequency generator this completes the AFP spin flipper design.

#### 2.3 Qualification Measurements

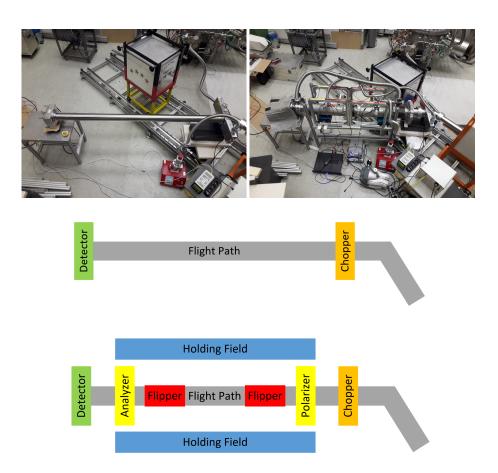

In order to test the polarizer and spin flipper system an experiment at the TRIGA reactor in Mainz was performed in 2018. The two setups used there are shown in fig. 2.4. The following section will give an overview of the different measurements and the spectrum of the UCN source.

#### 2.3.1 UCN Source Spectrum

In order to get the spectrum of the UCN source in Mainz, the setup shown on the left side of fig. 2.4 was used. It consists of a chopper, a two meter UCN guide and a CASCADE-U ([1]) UCN detector. A chopper is a device containing two linear motors driving two titanium grids coated with gadolinium in opposite directions. By

Figure 2.4: (a + c) Characterization setup for the UCN source spectrum. (b + d) Characterization setup for the spin flipper efficiency.

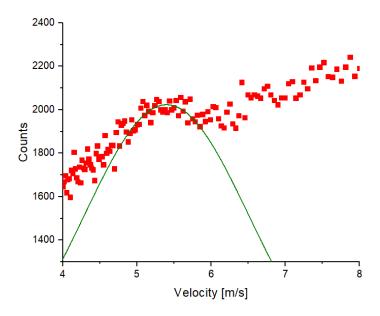

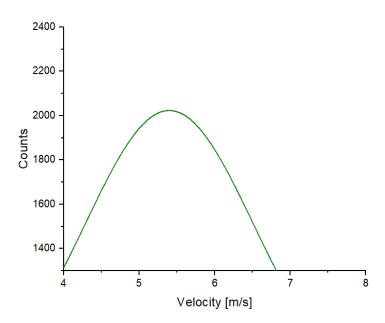

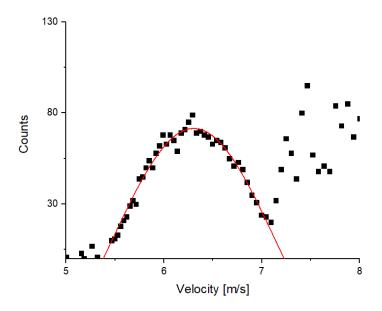

defining opening and closing times, the grids can either overlap in a way that they open half of the guide or they can overlap in a way that they completely close the guide and all UCN are absorbed in the titanium. For this setup the opening time was  $100~\rm ms$  followed by a closing time of  $1000~\rm ms$ . The CASCADE-U detector is made up of one  $^{10}\rm B$  layer on an aluminum foil with GEM foils and the readout PCB in between. UCN are absorbed in the boron and charges which are then multiplied in the GEMs and readout via a pixel detector. The measurement principle used is the time-of-flight (TOF) measurement which will give a velocity dependent spectrum of the UCN. Fig. 2.5 and 2.6 show the raw and cleaned velocity spectrum collected during a two hour measurement time. One can identify the UCN peak at a velocity of  $5.4~\rm m/s$ . The right side of the graph is the VCN shoulder which is known to be quite significant in Mainz. In the second graph the UCN peak was fitted with a Gaussian and shows the actual UCN spectrum of the source.

Figure 2.5: Velocity spectrum of the source in Mainz.

Figure 2.6: Cleaned UCN spectrum of the source in Mainz showing only the fit.

#### 2.3.2 Background Measurement

For testing the background at the reactor in Mainz the shutter to the UCN source was kept close and all flipper devices in the setup shown in fig. 2.4 (b) where turned off. The setup consists of the chopper (same type as in the measurement before),

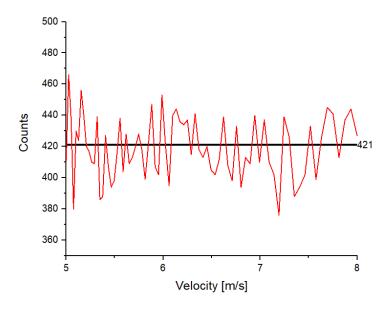

a polarizer as described in section 2.1.2, a  $1.4\,\mathrm{m}$  flight path equipped with two spin flippers as described in section 2.2.2, an analyzer (same as the polarizer) and the CASCADE-U UCN detector. In fig. 2.7 the background collected in a two and a half hour period is shown. All following graphs in the other sections will be background subtracted with the mean background value of  $421\,\mathrm{counts}$ .

Figure 2.7: Background of the source in Mainz. The mean value was taken.

#### 2.3.3 Reference Measurement

In order to determine the efficiency of the spin flipper there has to be a reference measurement on how the velocity spectrum looks like when both flippers are turned off and the UCN will only see the polarizer and analyzer in their flight path. Additionally, the holding field is turned on. This spectrum cleaned of the background is shown in fig. 2.8 and is the reference for  $100\,\%$  transmission.

#### 2.3.4 Flipper Measurements

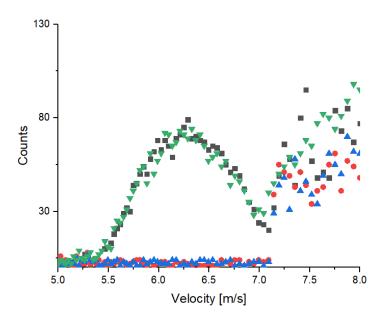

In order to determine the efficiency of the spin flipper design, three more measurements were executed. All measurements are shown together with the reference in fig. 2.9. In the first measurement only one spin flipper was turned on which should result in almost no counts in the detector since the HFS from the polarizer are turned into LFS which cannot pass the analyzer. The second measurement repeated the same thing with the other flipper turned on. Finally both flippers were turned on and the transmission now should be close to  $100\,\%$  again since now the HFS are turned into LFS by the first flipper and turn from LFS to HFS again in the second flipper.

Figure 2.8: Reference measurement for the spin flipper efficiency.

Figure 2.9: Neutron spectrum between 8 and 5 meter per second velocity. Grey is the reference, green the measurement with both flippers on, blue the one with flipper one on and red the one with flipper two on.

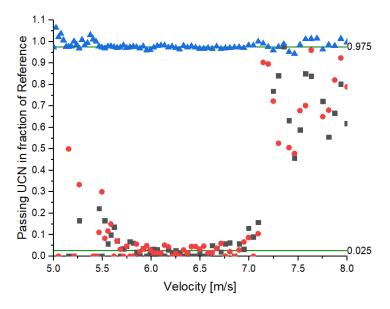

To determine the efficiency the UCN counted in the detector in the different bins was divided by the reference count in the respective bin. This is plotted in fig. 2.10 where additionally between the region of interest the mean value was calculated

for the measurements with one flipper and the one with two flippers. It can be seen that in the latter case only  $2.5\,\%$  of the UCN still pass the setup and in the first case  $97.5\,\%$  of the UCN reach the detector. Thus the overall efficiency of the spin flipper is  $98.7\,\%$  which is according to [45] enough to reach the precision PENeLOPE is aiming for.

Figure 2.10: Efficiency of the measurements. Blue shows the two flipper measurement and red and grey the one flipper measurements. Additionally the mean is shown for the blue points and the red and grey together.

## **Chapter 3**

## **Magneto-Gravitational Trap**

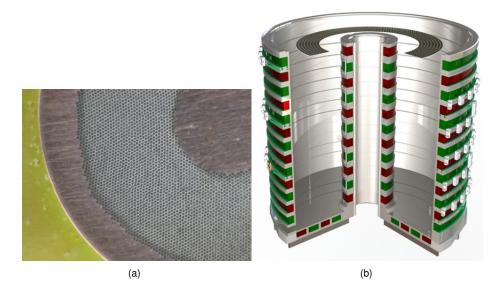

The magneto-gravitational trap of the PENeLOPE experiment consists of twenty-four individual superconducting coils. All coils are wound onto a carrier made of stainless steel (1.4409; EN 1088-2), suitable for applications with high magnetic fields. The NbTi wire used for the coils is the Supercon VSF-SSCI. It is made of a copper core surrounded by 7400 superconducting filaments and has a bare diameter of 0.9 mm, a total diameter of 0.95 mm and a copper to superconductor volume ratio of 1.5:1 [26]. Each of the coils has between 1520 and 1940 windings depending on the position and size in the coil stack. Due to the winding force of 105 N the superconducting wire even sticks to the coil former when there are thermal or magnetic forces. The "air gaps" within the winding package are filled with an epoxy resin. A cut through the superconductor and a CAD model the coils can be found in figure 3.1.

#### 3.1 Superconductor VSF-SSCI

The NbTi wire used for PENeLOPE becomes superconducting if the temperature falls below  $9.2~\rm K$  [26]. To guarantee a sufficient cooling of the magnet system it is embedded into a liquid helium tank cooling it to about  $4.2~\rm K$ . As every superconductor, the NbTi has a critical current density, a critical temperature and critical magnetic field above which it will become normal conducting again. According to [35] and [6] the critical current density and with it the critical current can be calculated via

$$J_c = \frac{C_0}{B} \cdot \left(\frac{B}{B_0}\right)^{\alpha} \cdot \left(1 - \frac{B}{B_0}\right)^{\beta} \cdot \left(1 - \left(\frac{T}{T_{c0}}\right)^{1.7}\right)^{\gamma} \tag{3.1}$$

$$I_c = J_c \cdot J_{Ref} \cdot A_{Eff} \tag{3.2}$$

Figure 3.1: (a) A cut through the superconductor used with a diameter of 0.95 mm. (b) A CAD model of coil stack with a height of 1 m.

with

$$B_0 = B_{c0} \cdot \left( 1 - \left( \frac{T}{T_{c0}} \right)^{1.7} \right). \tag{3.3}$$

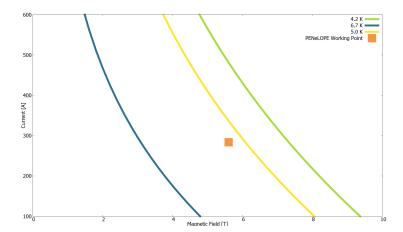

In these equations  $T_{c0}=9.2~{\rm K}$  is the critical temperature of NbTi at  $B=0~{\rm T}$ ,  $B_{c0}=14.5~{\rm T}$  is the critical magnetic field of NbTi at  $T=0~{\rm K},\,J_{Ref}=2122~{\rm A/mm^2}$ is the reference current density of NbTi at  $T=4.2~{

m K}$  and  $B=5~{

m T}$  and  $A_{Eff}=$  $0.254~\mathrm{mm}^2$  the effective superconductor area within the diameter of the VSF-SSCI wire. The parameters for the equations were determined with the help of Supercon by testing to  $C_0=28$  T,  $\alpha=0.6,\,\beta=1$  and  $\gamma=2.$  With these parameters the superconductor of PENeLOPE is underestimated meaning that the resulting calculated critical current is always below the effective real current density. The dependence of the current on the field, the temperature and the working point of PENeLOPE is shown in figure 3.2. It can be seen that at the operating point of PENeLOPE a nominal current of 283.5 A, necessary to create the storage potential of up to 115 neV, is 25 % below the critical line of the NbTi superconductor material. Nevertheless, superconducting coils need to be trained in order to reach the nominal current. During this training current is ramped through the coil and at some point the windings within the coil windings will move into a energetically more favorable position. These small movements introduce heat into the superconductor leading to a loss of superconductivity within the coil which is rapidly spreading over the whole coil. This process is called a guench. In the next ramping cycle the coil will sustain a bigger current until finally the nominal current is reached.

Figure 3.2: Critical current of the VSF-SSCI superconductor at different temperatures and the working point of PENeLOPE.

#### 3.2 Magnet Training

As mentioned in the previous section superconducting coils have to be trained before they can reach their nominal current. This section will describe the quench training of individual coils and coil stacks of the PENeLOPE experiment, the coil testing facility and the quench protection needed.

#### 3.2.1 Quench Protection

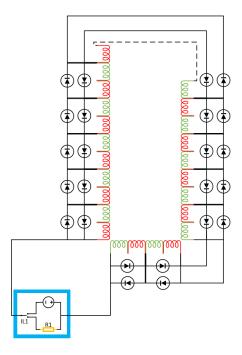

Figure 3.3 shows the electrical scheme of the magnet system. In the case of a quench the power supply tries to maintain the current flow and due to Ohm's law the voltage increases. The voltage over each coil pair and the power supply in general is monitored and if a sudden rise in any of these voltages is detected the interlock IL1 is released by the quench protection software. The energy still stored within the quenched coils has to be dissipated in the water-cooled dump resistor R1 within the power supply. According to Lenz's law high voltages are induced within the coils in order to maintain the current flow. These large voltages can damage the coil and have to be limited. Therefore, two coils are always bridged with DS502ST14 diodes from DYNEX. In the training set-ups described in the following sections only fractions of the quench protection system shown in figure 3.3 are used. Coils with alternating current directions are paired because according to [49] the overall forces within the whole system during a quench are the lowest with this set-up. The tensions reach up to a maximum of  $62 \, \mathrm{MPa}$ .

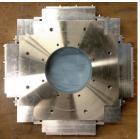

#### 3.2.2 Coil Test Experiment

In order to test and train the coils for PENeLOPE the Coil Test Experiment (CoTEx) facility was used ([35], [46], [45] and [17]) and figure 3.4 shows a CAD cut through

Figure 3.3: Electrical scheme of the PENeLOPE quench protection. The green and red symbolize the alternating directions of the current within the coils. The blue enclosed area is the power supply.

it. It consists of an inner liquid helium tank with a volume of roughly  $1000\ \rm I$  and a diameter of  $1.7\ \rm m$ . The  $4\ \rm K$  inner tank is surrounded by a copper shield with pipes soldered onto it which are cooled with liquid nitrogen to  $77\ \rm K$ . Both tanks are then surrounded with a vacuum tank of  $3\ \rm m^3$  which is able to hold a vacuum of up to  $10^{-6}\ \rm mbar$  at  $4\ \rm K$ . The lids of the different tanks are equipped with multiple feed-throughs which assure space for a proper experimental control and monitoring. To fill the cryostat, a helium liquefier with a liquefaction rate of up to  $15\ \rm I/h$  was used. In order to control, monitor and protect the experiment a CompactRIO system from National Instruments ([27]) was embedded in an electrical cabinet. It is a modular system consisting of a central CPU with a real-time operating system and a FPGA in the backplane of the CompactRIO shelf holding all I/O modules.

#### Monitoring

The CoTEx experiment monitors and stores several different parameters which are useful for the quench analysis and the control of the experiment to a Citadel database. Pressure is measured via two WIKA A10 sensors capable of a pressure region of 0 to 250 bar connected to the 4...20 mA modules of the CompactRIO. The vacuum is read out via a RS232 connection to the CenterThree from Leybold which is itself connected to two PTR90 ultra high vacuum sensors from Leybold. For temperature measures, there are PT100 sensors for the liquid nitrogen shield and the outside of the cryostat and CERNOX sensors for the inside of the cryostat and the

monitoring of the coil(s). PT100 sensors are directly connected to the CompactRIO whereas the CERNOX are connected to LakeShore LS218 temperature monitors having the calibration curve of each sensor stored inside. The latter are then read out via RS232. In order to have a measure of the liquid helium level within the cryostat, a helium level sensor from American Magnetics is used which is connected to an American Magnetics Model 135 helium level monitor which is then read out via RS232. The helium level sensor consists of a superconducting filament shielded in a metal pipe. Depending on the fill level the residual resistance of the filament is monitored. All data stored to the database are marked with a global time stamp for post analysis of quenches.

#### Control

For control purposes there are several relays and RS232 connections. Via RS232 connections the liquid nitrogen flow through the copper shield is controlled and via Ethernet the superconducting coil power supply is regulated. Several different digital I/Os are used for activating and deactivating the vacuum pumps and controlling their high and low speed modes. Furthermore, the vacuum shutter is controlled hereby.

#### **Protection**

Since CoTEx holds several hundred liters of cryo-liquids there are active and passive protection systems mounted onto the experiment. The nitrogen and helium systems are both protected with over pressure valves. If the pressure within the helium tank still gets too big or the over pressure valves fail, the gas is relieved via a burst disk opening at an overpressure of 1 bar. Additionally to the pressure protection system the experimental area of CoTEx also has an oxygen monitoring system in order to warn and protect the working personnel. As mentioned in section 3.1 the superconducting coils need a special quench protection and monitoring system. For this purpose, a floating differential voltages measurement module is connected to the CompactRIO. This measures the voltages across the bridged coils and triggers the interlock in the power supply if any differential voltage is above a set threshold. The NI9229 module is capable of voltages of  $\pm 60$  V and therefore too small for the PENeLOPE light system in section 3.2.6 which will generate differential voltages of more than  $100~\mathrm{V}$ . For this purpose, the system was adapted and an additional isolation amplifier module was connected in front of the existing one. The new module is the WAGO 2857 isolation amplifier capable of differential voltages of  $\pm 200~\text{V}$  at the input. It transfers these voltages to a scale of  $\pm 10~\text{V}$  at the output and is thus compatible with the existing system.

#### 3.2.3 Prototype Coil

In order to verify and test the design and performance of the superconducting coils produced by Babcock Noell GmbH (BNG) the prototype coil was build. It equals in

Figure 3.4: CAD cut trough CoTEx. The experiment has a height of 3 meters.

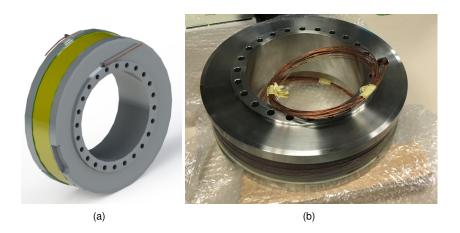

dimension the innermost bottom coil of the trap which was expected to be the most critical one due to its large winding package height-to-width ratio. Figure 3.5 shows a CAD and real image of the prototype coil. For the training procedure the coil was equipped with seven CERNOX sensors which should help to evaluate the position of the quench.

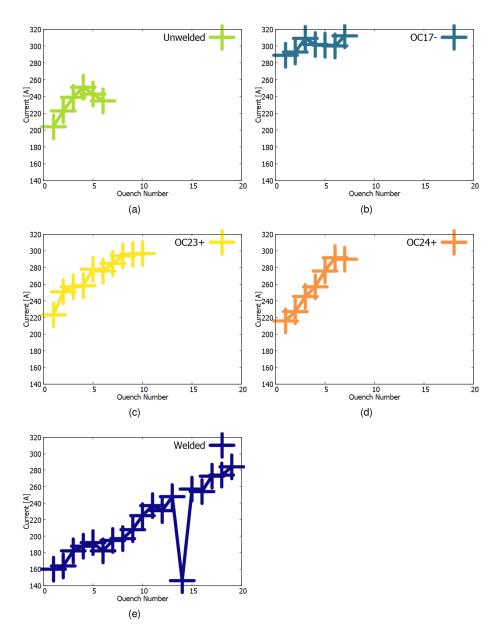

The prototype coil was the most extensively tested coil which, in addition to the training, went through mechanical and thermal stress introduced by welding and transportation. This was done to investigate the consequences of stress on the training achievements. Furthermore this coil was ramped with larger rate than actually required and it was mounted and dismounted several times. Figure 3.6 shows the quenching diagram of the coil with quench current versus quench number. It can be seen that eight different training cycles have been performed, indicated by different colors. In between the runs, the coil was either only warmed up for some time or the coil was mechanically or thermally treated. Overall the coil needs at least one guench after mechanical load (up to  $7000 \text{ m/s}^2$  [45]) or a temperature cycle of warming up and cooling down before being operated stably. The mechanical load might be transportation or disassembly and reassembly. A bigger thermal load on the coil like welding will result in a complete loss of the achieved training. In addition to the quench training the triple stack went through several ramping cycles with different ramp rates up to 3 A/s and the nominal current was held for several hours. In total this means that the complete coil system of PENeLOPE needs to be retrained no matter what achievements have been done already before welding. Nevertheless, the prototype coil fulfilled the design requirements and reached

Figure 3.5: (a) Prototype coil (diameter of 40 cm) as a CAD image. (b) Prototype coil picture.

much more than the necessary current of  $283.5~\mathrm{A}.$

Figure 3.6: Quench history of the prototype coil

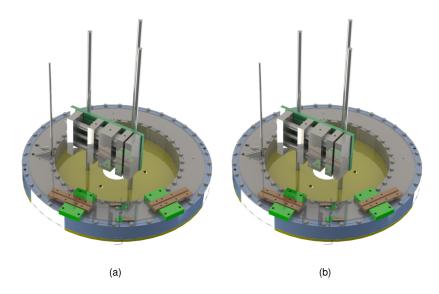

### 3.2.4 Triple Coil Stack

After the successful commissioning of the prototype coil, BNG started the production of the first outer coils in a stack of three coils (compare figure 3.7). Due to some qualification problems of the welding procedure of the coils they were delivered late and in a clamped state. As can be seen from figure 3.8 the unwelded stack reached at most  $251\,\mathrm{A}$  and even went down in current again. After this behavior it was decided to test all coils individually in order to confirm that all coils

were manufactured properly. Figure 3.8 shows that all coils behaved as expected and reached the nominal current easily. The welding of the triple stack erased all training of the individual coils but, as can be seen, however, the nominal current was reached after nineteen quenches. Additionally to the quench training the triple stack went through several ramping cycles with different ramp rates up to 3~A/s and the nominal current was held for several hours.

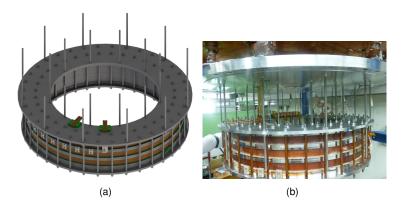

Figure 3.7: Triple coil stack with a diameter of 1 meter as a CAD image (a) and as a picture (b).

#### 3.2.5 Inner Coil

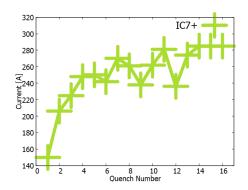

The next coil in the training procedure was the first inner coil of the final coil production. A picture and CAD model of the coil can be found in figure 3.9. During the training procedure the inner coil showed a very fluctuating quench behavior and eventually did not reach the nominal current of  $283.5\,$  A. After sixteen quenches the inner coil reached the nominal current (compare figure 3.10). The last three quenches happened all on the same current while holding the current for some minutes. After calculating the forces on the coil, the definition of the nominal current on this coil was lowered to  $270\,$  A. This current represents the forces which are acting on the coil in the PENeLOPE trapping system. With the current of  $270\,$  A several ramping sessions were conducted successfully.

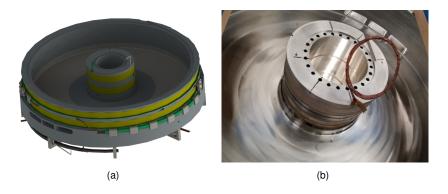

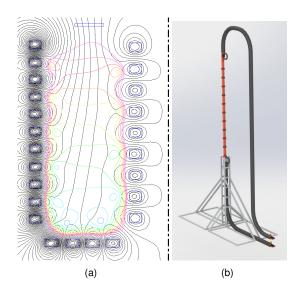

### 3.2.6 PENeLOPE Light

The next step in the buildup of PENeLOPE was to produce a first bottle shaped magnet assembly which can be seen in figure 3.11. It consists of the four bottom, two outer and two inner coils. This assembly also worked as a technology demonstrator of the complete magnet system since the most critical forces of the PENeLOPE system are impacting on the joints of bottom, outer and inner coils. Furthermore, a topology like this has never been built before with superconducting magnets operating under these conditions. Due to the large forces on the coils while being operated, the inner part of the trap would lift up several millimeters. This

Figure 3.8: Quench history of the unwelded (a) and welded stack (e) and the three individual coils (b-d).

effect would distort the trapping potential and could potentially lead to quenches of the whole system. To overcome this, fins were welded to the bottom of the trap which can be seen in the CAD image in figure 3.11.

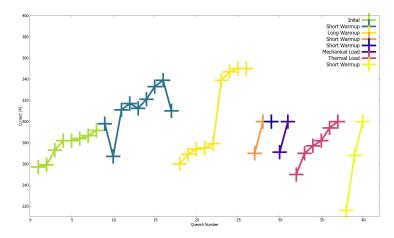

The training history of the PENeLOPE Light system consisting of eight coils (two inner, two outer and four bottom) can be found in figure 3.12 and shows, just like the inner coil, a very fluctuating quenching behavior. Several different approaches

Figure 3.9: Inner coil with a diameter of 330 cm as a CAD image (a) and as a picture (b).

Figure 3.10: Quench history of the inner coil.

Figure 3.11: PENeLOPE light with a diameter of 1 meter as a CAD image (a) and as a picture (b).

have been made to clarify this behavior of the system. At first, the magnetic field simulations done with the Opera tool have been checked by placing cryogenic Lake

Shore 3D hall sensors at different positions around the coils and comparing the measurements with the simulations. Table 3.1 shows the results and clearly both values agree very well.

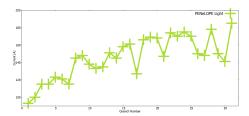

Figure 3.12: Quench history of PENeLOPE Light

Another suspicion was that one or more  $\operatorname{coil}(s)$  in the system is/are somewhat damaged and degrade(s) the performance of the whole system. In order to check this, the voltage curves of each quench were analyzed and the quenching coil pair was determined. Table 3.2 lists the amount of quenches per responsible coil pair. It can be seen that the quenching source varies quite a lot and no pair can be properly identified as being damaged or primarily responsible for the quenches. Since after thirty one quenches only a current of 185~A was reached, calculations have been made on which storage potential will still serve the precision goal of PENeLOPE within a feasible time and effort. The minimum current was determined by [44] to 180~A. Due to the fact that this current was already reached and the trend line of the quench training is still rising it was decided to continue the building of PENeLOPE and to stop the training session of PENeLOPE Light. Moreover all further training would just have been time and resource consuming and nevertheless been lost again after welding the whole system.

| Current [A] | Field Measured [mT] | Field Simulated [mT] |

|-------------|---------------------|----------------------|

| 0           | 0.01                | 0.00                 |

| 50          | 56.50               | 55.00                |

| 75          | 82.50               | 83.00                |

| 100         | 115.00              | 110.00               |

| 0           | 0.012               | 0.00                 |

| 50          | -412.00             | -411.00              |

| 75          | -615.00             | -617.00              |

| 100         | -830.00             | -822.50              |

| 0           | 0.01                | 0.00                 |

| 50          | -414.00             | -411.00              |

| 75          | -615.00             | -617.00              |

| 100         | -823.00             | -822.50              |

Table 3.1: Measured and simulated magnetic field at three different sensor positions within the PENeLOPE Light system.

| Responsible Coil Pair | Amount of Quenches |

|-----------------------|--------------------|

| BC1/3                 | 7                  |

| BC2/4                 | 6                  |

| IC5/10                | 9                  |

| OC22/16               | 8                  |

Table 3.2: Lits of coil pairs producing the different quenches in the PENeLOPE Light system (8 coils in total).

# **Chapter 4**

## **Central Coil**

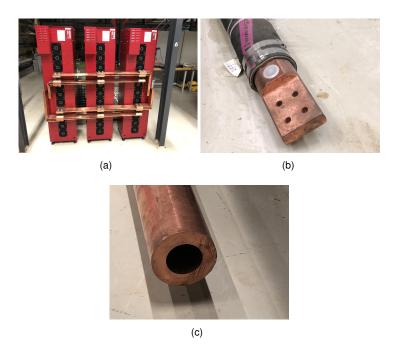

The magneto-gravitational trap mentioned in chapter 3 forms a storage volume with a potential barrier of 115 neV. One half of the trap with the equipotential lines of the storage potential is shown in fig. 4.1. The small closed circles within the volume point to areas where the magnetic field is vanishing. As mentioned in chapter 2 zero field areas can lead to undesired spin flips of the pre-polarized low-field-seeking neutrons into high-field-seeking ones. The latter will then disturb the lifetime measurement with systematic errors [45]. In order to overcome this problem, a central conductor is inserted into the warm bore in the center of PENeLOPE which will overlay the trapping potential with an azimuthal field around the central symmetry axis of the trap. According to [45] a field of at least 5 mT is necessary to maintain the spin orientation of the UCN - with a single central conductor this equals a current of at least 12500 A. In fig. 4.1 the central coil and symmetry axis is indicated by the dashed line. The central coil consists of a copper tube with a diameter of eight centimeters and a wall thickness of two centimeters, cooled with water flowing through the inside of the tube. A CAD image of the set up can be found in fig. 4.1 where water-cooled cables from Druseidt can be seen on the bottom and top side of the conductor. To separate the conductor from the PENeLOPE vacuum tank, small plastic spacers have to be mounted on the bare conductor tube. A stack of three 5000 A power supplies from RGB Heytekker with a total current of 15000 A at a maximal voltage of  $10~{\rm V}$  is used as a power supply. An image of the power supply, the conductor and the cable can be found in fig. 4.2.

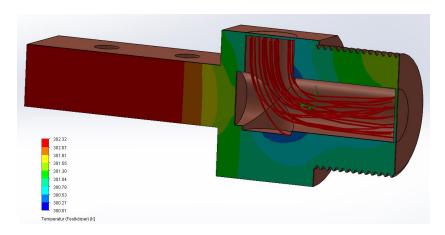

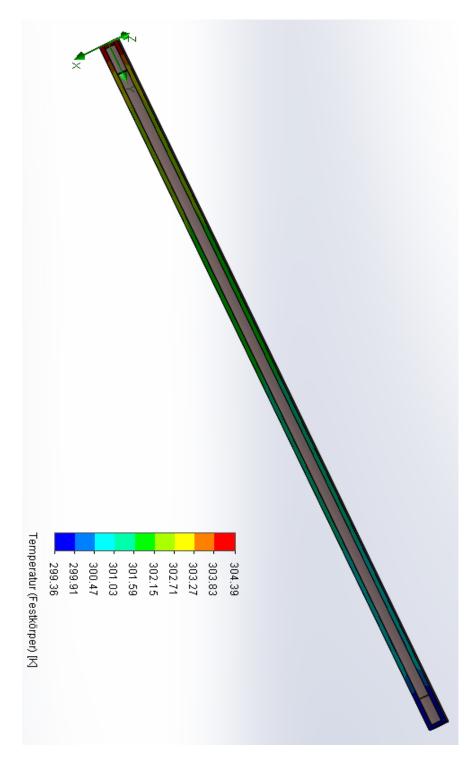

In order to verify the design of the central coil, several simulations have been made for different currents and different water flows with the Solidworks Flow Simulation tool. Fig. 4.3 and 4.4 show the results of the simulations with a current of  $15000~\rm A$  and a water flow of  $0.25~\rm kg/s$ . The simulation goal was set to a saturating maximum temperature of the solid. It can be seen in the figures that the conductor itself and the mating for the cables at each end of the conductor will not increase beyond a temperature of  $305~\rm K$ . The starting temperature of the conductor and the cooling water was  $293.5~\rm K$ , so it merely increased by roughly  $12~\rm K$ .

Figure 4.1: (a) Magnetic field lines in an axially symmetric cut of the storage volume of PENeLOPE. The 115 neV potential line is the most outer closed line (pink). (b) CAD image of the central conductor in its stand and connected to water-cooled cables.

Figure 4.2: (a) Image of the power supply system of the central coil (Height of 1.8 meters). (b) Image of the mating of the Druseidt water-cooled cable. (c) Image of the central conductor before the assembly (diameter of 8 cm).

Figure 4.3: Maximum temperature in the mating adapter at 15000 A and a water flow of 0.25 kg/s.

Figure 4.4: Maximum temperature in the conductor at 15000 A and a water flow of  $0.25\ kg/s$ .

## **Chapter 5**

# **Absorber**

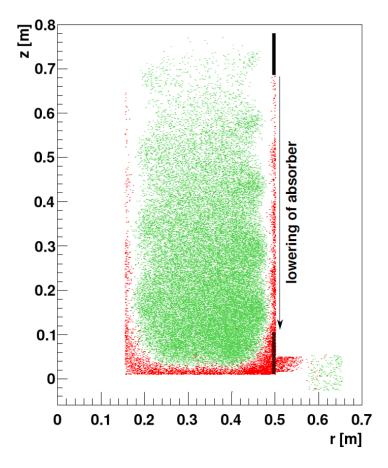

When the superconducting coils of the experiment are ramped up to the nominal current, the low-field-seekers and the high-field-seekers are separated by their different properties in an outer magnetic field. The distribution of the LFS and HFS after ramping is shown in fig. 5.1. As already mentioned in previous chapters the HFS can introduce systematic errors to the neutron lifetime measurement and therefore have to be removed.

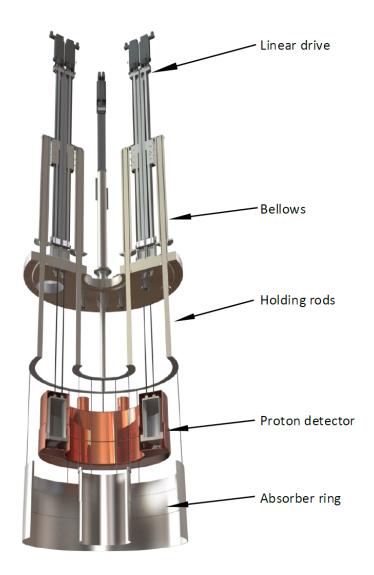

For PENeLOPE, it was decided to build an inner and outer neutron absorbing ring which can be lowered into the trap. Due to the design of the trap, there are several tight constraints on the design of such an absorber mechanism. First of all, the system is operating in a high magnetic field and an ultra-high vacuum area. Furthermore the system has to withstand a large temperature gradient from  $4\ K$  in the inside of the experiment to room temperature. Additionally, the space between the walls and the storage potential is only in the millimeter regime and only 5 mm in the most narrow spot.

A CAD image of the absorber and the necessary components can be found in fig. 5.2. The set-up consists of six linear servo drives from Bosch Rexroth with a very precise positioning in the micrometer range, six bellow feedthroughs which hold the rods for the absorber rings and the inner and outer absorber rings themselves [45]. The servo drives are all connected via the EtherCAT protocol to the experiment control described in chapter 7. Due to the very tight space constraints the rings of the absorber are made of a light weight plastic honeycomb structure where a neutron absorbing foil is wrapped around. In addition to the high-field-seeker cleaning, the absorber could also be used as a spectrum shaper when the absorber is lowered into the trap during the filling procedure and by this cuts off neutron energies above a certain level.

Figure 5.1: Distribution of LFS (green) and HFS (red) in the magneto-gravitational trap of PENeLOPE.

Figure 5.2: CAD image of the neutron absorber of PENeLOPE.

# **Chapter 6**

## **Proton Detector**

Within the PENeLOPE experiment the proton detector is another challenging part due to environmental conditions. The key facts of the proton detector are listed below.

- Electrostatic potential of −30 kV

- Detector temperature 77 K

- Electronics at room temperature within a tank in the cryostat

- Cryostat at 4 K

- $\bullet\,$  Large magnetic field of  $0.6\ {\rm T}$

- Total of 700 events/s

- Sensitive area of  $0.23~\mathrm{m}^2$

- 1344 large area avalanche photodiodes (LAAPDs)

There have been several studies on the proton detector architecture and the detector which shall be used. [35] evaluated the use of caesium iodid crystals or plastic as scintillators, [35] evaluated micro-channel-plates and finally [54] tested LAAPDs for the proton detection. A crucial trade off led to the decision to use the LAAPDs for the PENeLOPE readout due to signal quality, easiness of the setup and cost. The following sections will describe the architecture and electronics of the final detector concept.

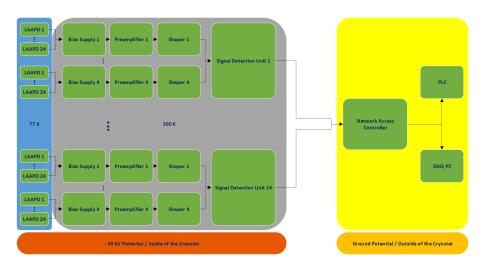

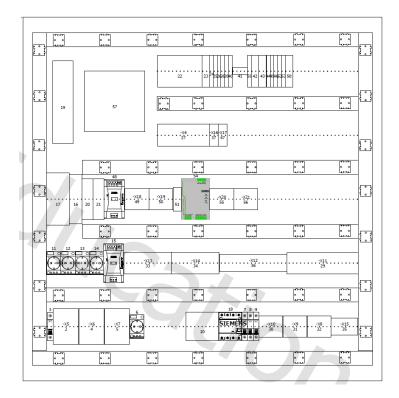

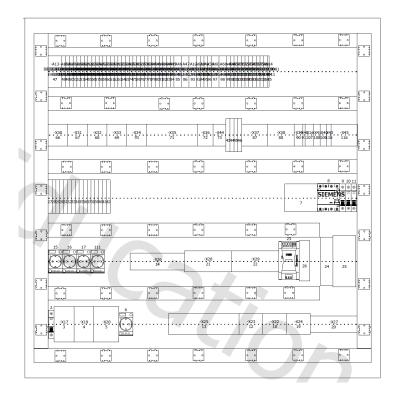

#### 6.1 Detector Architecture

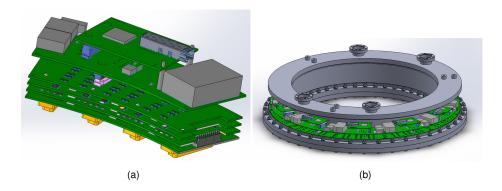

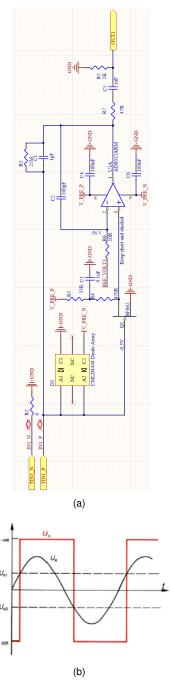

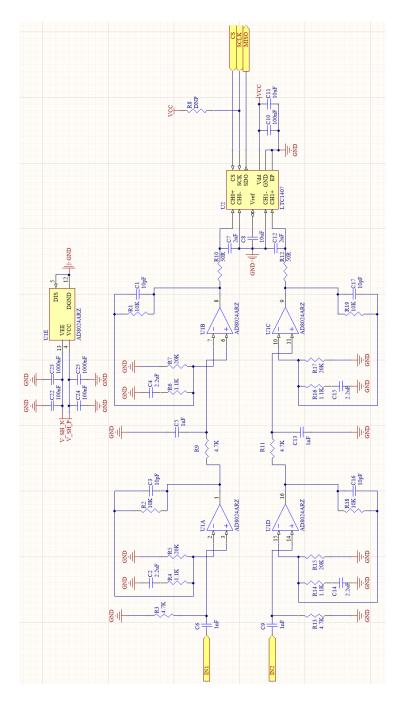

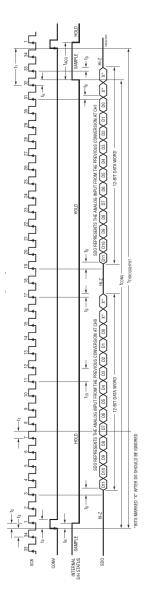

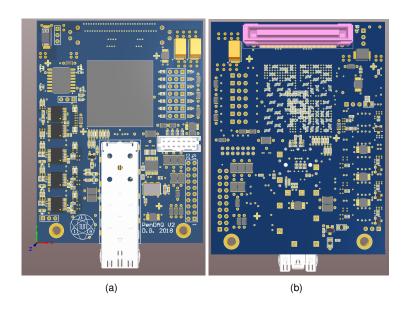

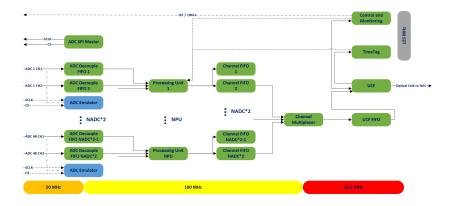

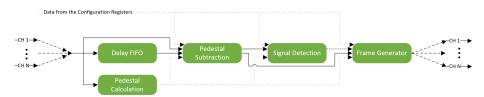

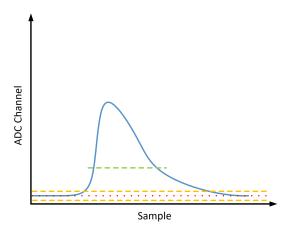

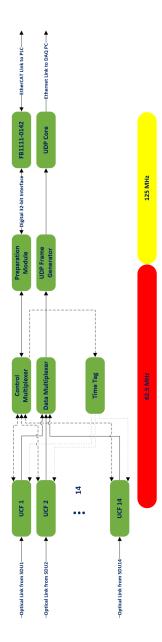

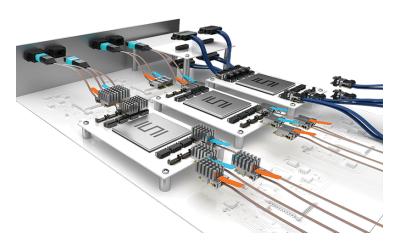

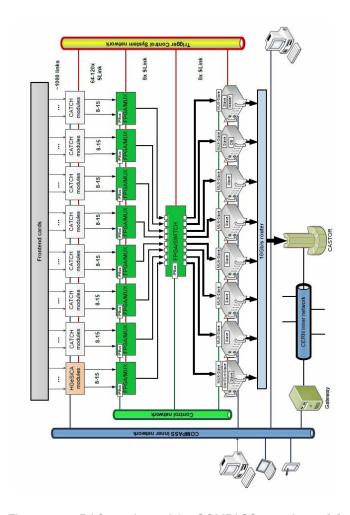

Figure 6.1 shows the data acquisition architecture of the proton detector. The upcoming section will, in detail, describe the data flow and each component from the left to the right. As mentioned in the previous section, the detector consists of 1344 APDs grouped in clusters of 24. Four of these clusters are connected to one bias

supply board where the bias voltage of the APDs and the signal path are separated. Signals will further proceed into the preamplifier and shaper boards where they are processed and digitized. Four of these chains are connected to one Signal Detection Unit (SDU) capable of handling 96 channels. 14 of these SDUs are placed within the cryostat on the high electrostatic potential and are connected via optical fibers to the multiplexer board called Network Access Controller (NAC). The NAC is placed outside of PENeLOPE and is galvanically isolated via optical links from the inside of the cryostat. Finally, the NAC is connected on the one side to the programmable logic controller (PLC) for slow control and monitoring and on the other side to the DAQ PC storing the events recorded.

Figure 6.1: DAQ architecture of the proton detector of PENeLOPE

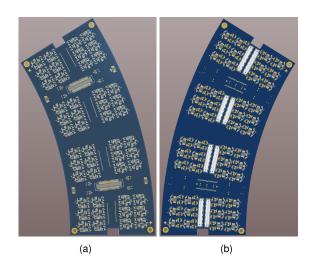

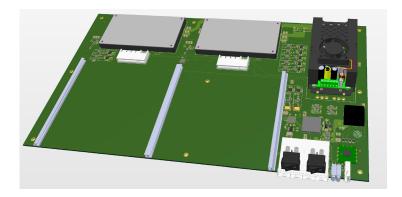

The different potential and temperature zones are symbolized with different colors in figure 6.1. Shaded with the blue color is the  $77\ K$  zone of the APDs followed by the greyish zone of room temperature within the detector tank and the yellow zone of room temperature outside of the cryostat. In the bottom part of the figure the red bar shows all components on the  $-30\ kV$  electrostatic potential and inside the cryostat and the orange bar shows the components on the ground potential and outside of the cryostat. Figure 6.2 shows a CAD model of one read-out stack for 96 channels and a CAD model of the 14 SDUs placed within the detector tank. On the top side of the tank six threads are placed which hold ceramic rods in order to mount the tank to the PENeLOPE cryostat. Furthermore, there are four CF40 feedthroughs to hold all optical fibers, the high voltage connection and the air flow inlet and outlet. Also, these feedthroughs will be ceramically isolated. A picture of the delivered tank can be found in 6.3.

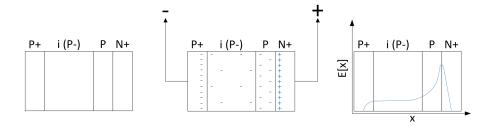

## 6.2 Large Area Avalanche Photodiodes

For each of the detector channels one Hamamatsu S11048 LAAPD [22] will be used. Each of the LAAPDs consists of several doped layers of silicon. Figure 6.4

Figure 6.2: (a) CAD model of a read-out stack of 96 channels. It is  $15 \times 8 \times 8$  cm in size. (b) CAD model of the detector tank with one meter in diameter and the read-out stacks inside.

Figure 6.3: Picture of the detector tank with a diameter of about one meter (Since it will be stored for some more time the air tight foil was not broken).

shows the structure of such an APD. It consists of a highly p-doped layer covered by a slightly p-doped intrinsic layer, a p-doped layer and a highly n-doped layer. A reverse-biased APD will internally create a field shown in the right part of figure 6.4. If a photon or low-energy proton is impinging the intrinsic zone of the diode an electron-hole pair is generated. The hole will drift towards the strongly p-doped zone, whereas the electron drifts towards the multiplication zone. When reaching this zone the electron is accelerated and generates more electron-hole pairs. This

avalanche of electron-hole pairs and the resulting jump in the photo current will stop when the last hole reached the highly p-doped area. Depending on the bias voltage of the APD, the signal on the photo current of the same photon/particle can be larger or smaller - this is called the gain of an APD. The gain M can be calculated via

$$M = \frac{1}{1 - \left(\frac{U_B - U_L}{U_D}\right)^m} \tag{6.1}$$

and depends on the bias voltage  $U_B$ , the breakdown voltage  $U_D$ , the loss voltage over the series resistance of the APD  $U_L$  and a characteristic factor m depending on the internal structure and material of the APD [22]. The current within the APD depends on the signal current, noise current and the gain. It can be written as

$$I_{APD} = (I_{Signal} + I_{Noise}) \cdot M \tag{6.2}$$

Figure 6.4: Structure of the APD in non biased (left), biased (right) mode and the resulting field strength inside of the APD when reverse-biased. Effective positive charges are marked with a blue plus and effective negative charges with a green minus.

Characteristic for all photodiodes is the temperature dependence of the noise on the photo current. The quadratic mean of the thermal noise can be formulated according to Nykvist as

$$\overline{I_{therm}^2} = \frac{4k_B T}{R} B \tag{6.3}$$

where T is the temperature, B the bandwidth and R the resistance of the APD. Additionally to the thermal noise there is the shot noise which depends on the background current  $I_B$ , the mean photo current  $\overline{I}_{ph}$ , the dark current  $I_D$ , the bandwidth B and the mean square of the gain  $\overline{M^2} \approx M^2 M^x$  [24]. In the approximation of  $\overline{M^2}$  x is a characteristic factor for the material used. For silicon it is 0.2 to 0.5. The shot noise can be formulated as

$$\overline{I_{shot}^2} = 2e\left(|\overline{I}_{ph}| + |I_B| + |I_D|\right) \cdot B \cdot \overline{M^2}$$

(6.4)

and together with the thermal noise it gives the total noise of an APD according to

$$\overline{I_{noise}^2} = \overline{I_{shot}^2} + \overline{I_{therm}^2}.$$

(6.5)

| Parameter            | Conditions | Value          |

|----------------------|------------|----------------|

| Bandwidth            |            | 320 to 1000 nm |

| Peak Sensitivity     | M = 100    | 580 nm         |

| Breakdown Voltage    |            | 420 V          |

| Terminal Capacitance | M = 100    | 250 pF         |

| Dark Current         | M = 100    | 30 nA          |

Table 6.1: Key parameters of the S11048 LAAPD according to [22]

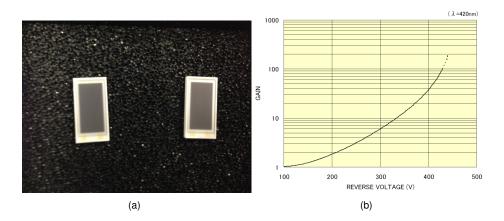

Figure 6.5: (a) Picture of two S11048 LAAPDs with a size of 14.5 mm x 7.2 mm. (b) A typical gain versus bias voltage curve of the S11048 [22].

An key parameter for a effective signal resolution of the detector is the signal-tonoise ratio which is defined as

$$\frac{S}{N} = \frac{\overline{I_{signal}^2}}{\overline{I_{noise}^2}} = \frac{\overline{I_{signal}^2}}{\overline{I_{shot}^2 + I_{therm}^2}}.$$

(6.6)

The key data of the Hamamatsu S11048 LAAPD used within PENeLOPE can be found in table 6.1, a picture of the APD and a typical gain versus voltage curve can be found in figure 6.5. In total, the S11048 has an active area of  $14.0~{\rm mm}$  x  $6.8~{\rm mm}$ . More details on measurements with the APD and the complete electronics can be found in 6.5.

## 6.3 Analog Electronics

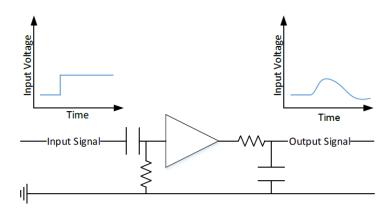

In the analog electronics part, the signals from the APDs are decoupled from the high voltage, amplified, filtered and shaped. Finally, the signals are digitized. The following sections will describe the way of the signal throughout the electronics and all related printed circuit boards. Topology wise the design is based on the design of [11].

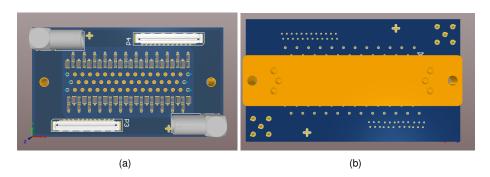

## 6.3.1 Bias Voltage Supply Board

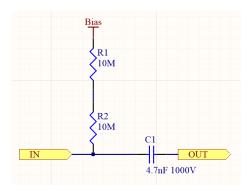

The APDs in the detector are connected via twisted pair cables with the D-Sub connectors welded into the bottom of the detector tank (see figure 6.2). Figure 6.6 and 6.7 show pictures of the bias voltage supply board and the schematic. Via LEMO connectors the bias voltage is inserted and then coupled with the two  $10~\rm MOhm$  series resistors  $R1~\rm and$   $R2~\rm to$  the APD. The capacitor  $C1~\rm is$  discharged when a photon or low-energy proton hits the APD within a time constant of less than  $91~\rm ns$ , corresponding to a cut-off frequency of  $11~\rm MHz$  of the S11048 APD. Each of the D-Sub connectors can hold twenty-four APD connections and so can the bias voltage supply board. This, in turn, means that the bias voltage of the detector can be regulated in clusters of twenty-four channels.

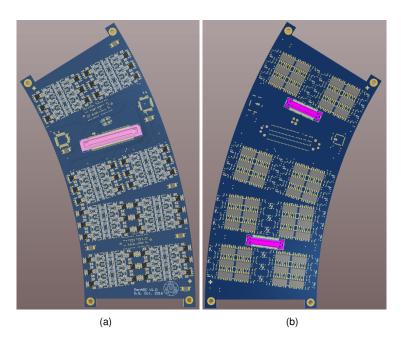

Figure 6.6: CAD model of top (a) and bottom (b) side of the bias voltage supply board. On the top side, the connectors to the following cards and the high voltage input via the LEMO connectors are visible. On the bottom side, the D-Sub connector can be seen which is plugged into the detector tank. The card is  $3 \times 8$  cm in size.

#### 6.3.2 Preamplifier Board

From the bias voltage supply board the signals are transferred via Molex 501083-5010 coaxial connectors and ribbon cable assemblies. The ground line of the pseudo-differential pair coming from the APD is connected via a zero Ohm resistor R2 to ground and the capacitor C1 in fig. 6.7 AC couples the output of the APD to the input stage of the preamplifier (see figure 6.8) consisting of a low-noise J-FET BF862 from NXP (Q1) and two over-voltage protection diodes CMLD4448

Figure 6.7: Schematic of the bias voltage supply board

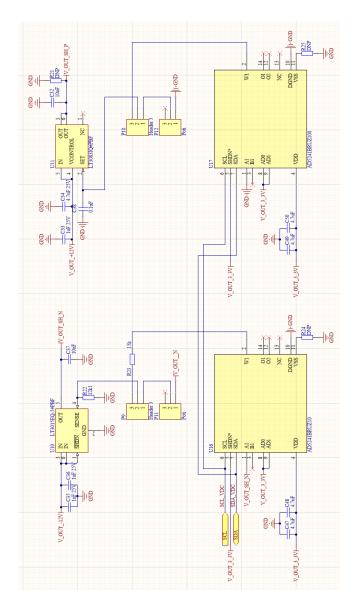

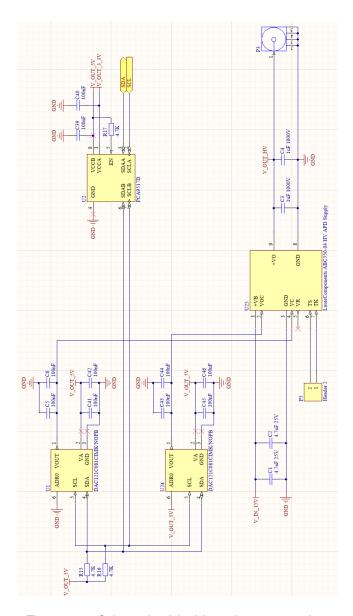

from Central Semiconductor (D1). Together with an open drain resistor of 470 Ohm (R4) the circuit results in an AC gain of 14.