# Trustworthy Verification of Realtime Systems

# **Simon Wimmer**

# Trustworthy Verification of Realtime Systems

## **Simon Wimmer**

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

#### Vorsitzender:

Prof. Dr. Francisco Javier Esparza Estaun

### Prüfende der Dissertation:

- 1. Prof. Tobias Nipkow, Ph.D.

- 2. Prof. Dr. Jaco van de Pol

Die Dissertation wurde am 07.10.2020 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 18.11.2020 angenommen.

# **Abstract**

Timed automata are a popular formalism for modeling real-time systems in safety-critical applications. Model checkers for timed automata are an effective verification method that can automatically prove safety of such a model with respect to a temporal specification. This thesis addresses the question of the trustworthiness of verification results obtained by timed automata model checkers. To this end, I have studied two approaches that try to significantly increase the level of trustworthiness by employing another popular verification method, interactive theorem proving. Interactive theorem provers are considered to be highly trustworthy as their correctness relies only on a small and well-tested program core that checks every logical inference made.

In the first approach, verification, a full model checker for timed automata, Munta, was constructed within the theorem prover Isabelle/HOL. Techniques from program refinement were used to obtain efficiently executable code. There is a full proof of correctness for Munta within Isabelle/HOL, meaning that verification results obtained by Munta can be considered as trustworthy as the correctness of Isabelle/HOL itself. Munta delivers reasonable performance and provides features comparable to mainstream model checkers for timed automata.

The second approach, certification, attempts to lift the trustworthiness of regular unverified model checkers to the level of trust put in Isabelle/HOL. The unverified model checker is modified to produce a proof for the verification result, a certificate. An independent checker confirms that the certificate is indeed a valid proof of the model checking result for the given model and property. As the checker is itself derived from Munta and thus constructed and verified in Isabelle/HOL, the same level of trustworthiness is achieved. The approach has many advantages: a uniform certificate format is applicable to a large range of model checkers that can employ many optimizations during model checking; certificates can be compressed to speed-up certificate checking; and the certificate checker can be easily parallelized.

# Zusammenfassung

Timed Automata sind ein beliebter Formalismus, um Echtzeitsysteme für sicherhheitskritische Anwendungen zu modellieren. Model-Checker für Timed Automata sind einen effektive Verifikationsmethode, die automatisch die Sicherheit eines solchen Modells im Bezug auf einen gegebene temporale Spezifikation beweisen kann. Diese Dissertation nimmt sich der Frage der Vertrauenswürdigkeit von Verifikationsresultaten, die von Timed-Automata-Model-Checkern produziert werden, an. Dazu habe ich zwei Ansätze untersucht, die versuchen das Level der Vertrauenswürdigkeit zu erhöhen, indem eine weitere Verifikationsmethode, das interaktive Theorembeweisen, eingesetzt wird. Interaktive Theorembeweiser werden als höchst vertrauenswürdig betrachtet, da ihre Korrektheit nur auf einem kleinen und gut getesteten Programmkern beruht, der jede durchgeführte logische Inferenz überprüft.

Im ersten Ansatz, Verifikation, wurde ein vollständiger Model-Checker für Timed Automata, Munta, innerhalb des Theorembeweisers Isabelle/HOL konstruiert. Techniken aus dem Bereich der Programmverfeinerung wurden verwendet, um effizienten ausführbaren Code zu erhalten. Es existiert ein vollständiger Korrektheitsbeweis für Munta in Isabelle/HOL, was bedeutet, dass die Verifikationsergebnisse, die von Munta produziert werden, genauso vertrauenswürdig sind wie Isabelle/HOL selbst. Munta erreicht eine angemessene Performanz und bietet Features an, die vergleichbar zu üblichen Model-Checkern für Timed Automata sind.

Der zweite Ansatz, Zertifizierung, versucht die Vertrauenswürdigkeit von Resultaten von regulären unverifizierten Model-Checkern auf das Level von Vertrauen, das in Isabelle/HOL gesetzt wird, zu heben. Der unverifizierte Model-Checker wird modifiziert, um einen Beweis für das Verifikationsergebnis, ein Zertifikat, zu produzieren. Ein unabhängiger Checker bestätigt, dass das Zertifikat tatsächlich ein korrekter Beweis für das Model-Checking-Ergebnis ist. Da der Checker selbst von Munta abgeleitet ist und in Isabelle/HOL verifiziert ist, wird dasselbe Level von Vertrauenswürdigkeit erreicht. Der Ansatz hat viele Vorteile: ein einheitliches Zertifikatsformat ist auf eine große Vielfalt von Model-Checkern, die viele Optimierungen während des Model-Checkens verwenden können, anwendbar; Zertifikate können komprimiert werden, um ihre Überprüfung zu beschleunigen; und der Zertifikat-Checker kann leicht parallelisiert werden.

# **Acknowledgements**

I want to start by extending my gratitude to those who keep producing information on the internet that is available to anyone, often without asking for anything in return. Without the work of these people, I would probably never have picked up computer science and the field of this thesis in particular.

Coming to university already with certain interests and a lot of curiosity to finally understand what I had peeked into, the theory professors at TUM, first and foremost Tobias Nipkow, were just ready to quench my thirst with the "Perlen der Informatik" lecture from week two. With Tobias Nipkow continuing this lecture into the second semester, it is no wonder I later ended up as his doctoral student. I want to thank him for his enthusiasm in teaching, for taking me under his wings already as a young student, and later luring me back from overseas by offering me the opportunity that culminated in this thesis. He has been a kind advisor who always had an open ear for me and who let me pursue my ideas freely, nudging me in the right direction when it was needed (though, sometimes I could probably have needed a stronger push as well). Special credit also goes to Lars Noschinski, who was the teaching assistant in those early "Perlen der Informatik" lectures and who cheerfully introduced me to the wonders of Isabelle from my second semester on.

I want to thank my colleagues at the Chair for Logic and Verification, Bohua, Fabian, Helma, Johannes, Jonas, Julian, Ondřej, Kevin, Lars, Lukas, Manuel, Max, Mohammad, and Peter, for providing a fun and friendly work environment and their never-ending motivation for bringing fresh habits to the group, pursuing new ideas and projects, discussing matters of the earth and the universe, teaching me new things, and sometimes motivating me to do sports or joining me in these activities. Some of these encounters were certainly life-changing. On this note, I specifically want to mention Ondřej and Max who became my dear "Heide" friends. I am very grateful to have met them. Helma needs to be commended for her ongoing friendliness and helpfulness, even when I had once again postponed my bureaucratic duties to the very last day (or later).

My co-authors, Frédéric, Jaco, Johannes, Joshua, and Peter, deserve to be mentioned for their enthusiasm for my ideas and their help in implementing them. Without the work of Peter in particular, this thesis would not have been possible. Also, having worked already as a pair-proving team in research, we proudly represented our group in the fun and engaging "VerifyThis" competition.

Max, Manuel, Frédéric, and Peter have provided helpful comments on earlier versions of this thesis. Thank you!

I thank my friends for being there and coping with me during all these year, particularly those who lived closest to me and therefore suffered the most from this thesis: Benedikt, Fabian, Julia, and Liesa. My final thanks goes to my family for their loving support, which I could always be certain of, even when they could not see me as much as they would have liked to. My mother drew the illustration on the cover.

# **Contents**

| Αι | ostrac                                                                                   | it.                                                                                                                                                                                                                                                                                                     | `                                                                                       |

|----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Zι | ısamı                                                                                    | menfassung                                                                                                                                                                                                                                                                                              | vi                                                                                      |

| Αc | know                                                                                     | vledgements                                                                                                                                                                                                                                                                                             | i×                                                                                      |

| Co | onten                                                                                    | ts                                                                                                                                                                                                                                                                                                      | x                                                                                       |

| 1  | 1.1<br>1.2<br>1.3                                                                        | Research Objective                                                                                                                                                                                                                                                                                      | 1<br>2<br>5<br>9                                                                        |

| 2  | Tim                                                                                      | ed Automata: An Overview                                                                                                                                                                                                                                                                                | 11                                                                                      |

| 3  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>Forr<br>3.1<br>3.2<br>3.3<br>3.4 | Introduction . Semantics . The Model Checking Task . Regions . Zones and Abstractions . Difference Bound Matrices . Other Model Checking Approaches . Summary .  malizing (Probabilistic) Timed Automata . Regions . Zones and Difference Bound Matrices . Extrapolation . Probabilistic Timed Automata | 111<br>122<br>144<br>155<br>166<br>188<br>199<br>200<br><b>211</b><br>221<br>222<br>233 |

| 4  | Con                                                                                      | structing a Verified Model Checker for Timed Automata                                                                                                                                                                                                                                                   | 27                                                                                      |

|    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                                          | Refinement                                                                                                                                                                                                                                                                                              | 27<br>29<br>30<br>31<br>32                                                              |

| 5  | Cert                                                                                     | tifying Model Checking of Timed Automata                                                                                                                                                                                                                                                                | 35                                                                                      |

|    | 5.1<br>5.2<br>5.3<br>5.4                                                                 | Certificates for Unreachability                                                                                                                                                                                                                                                                         | 35<br>37<br>40<br>41                                                                    |

## CONTENTS

| 6                | Con                                                                      | lusion                                                         | 43         |  |  |  |

|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|------------|--|--|--|

| 6.1 Related Work |                                                                          |                                                                |            |  |  |  |

|                  |                                                                          | 6.1.1 Formalization of Timed Automata and Markov Models        | 43         |  |  |  |

|                  |                                                                          | 6.1.2 Verified Model Checking                                  | 43         |  |  |  |

|                  |                                                                          | 6.1.3 Algorithm Verification and Refinement                    | 44         |  |  |  |

|                  |                                                                          | 6.1.4 Certification in Verification                            | 45         |  |  |  |

|                  | 6.2                                                                      | Limitations                                                    | 46         |  |  |  |

|                  |                                                                          | 6.2.1 Simplifying Assumptions                                  | 46         |  |  |  |

|                  |                                                                          | 6.2.2 Modeling Formalism                                       | 47         |  |  |  |

|                  |                                                                          | 6.2.3 Temporal Properties                                      | 48         |  |  |  |

|                  |                                                                          | 6.2.4 Efficiency                                               | 48         |  |  |  |

|                  |                                                                          | 6.2.5 Trustworthiness                                          | 48         |  |  |  |

|                  | 6.3                                                                      | 1                                                              | 49         |  |  |  |

|                  | 6.4                                                                      | General Reflections                                            | 51         |  |  |  |

| Bi               | bliogr                                                                   | aphy                                                           | <b>5</b> 3 |  |  |  |

| Α                | Forn                                                                     | alized Timed Automata                                          | 71         |  |  |  |

| В                | B MDP + TA = PTA: Probabilistic Timed Automata, Formalized (Short Paper) |                                                                |            |  |  |  |

| С                | Verified Model Checking of Timed Automata                                |                                                                |            |  |  |  |

| D                | Munta: A Verified Model Checker for Timed Automata                       |                                                                |            |  |  |  |

| Ε                | Veri                                                                     | ed Certification of Reachability Checking for Timed Automata 1 | 27         |  |  |  |

| F                | Certifying Emptiness of Timed Büchi Automata                             |                                                                |            |  |  |  |

# 1 Introduction

The advent of computer systems was probably the main technological advance that shaped the world's history over the course of the last 50 years. Nowadays, computers are ubiquitous: most of us carry at least one of them around everywhere we go and there is hardly any sector of life that they have not managed to penetrate yet. Increasingly, we have also trusted them with our lives: they steer our aircraft, control cardiac pacemakers, insulin pumps, ventilators, and other medical devices, and will soon drive our cars. The examples that I just named are all special in their common characteristic that they combine a software system with a component that interacts with the real physical world. Hence they are called *cyber-physical systems (CPS)* [131]. This characteristic sets them apart from regular software systems, like a text processor, your web browser, or an internet platform. While the latter are clearly important, an error in their software does usually not immediately lead to a catastrophe such as the loss of life or the explosion of a rocket.

Unfortunately, CPS have been plagued by fatal software failures from the early times of their existence until today [71, 87]. This is not really surprising as some of these software systems today are the most complex systems that have ever been constructed by human beings [1, 39, 48, 53]. Thus, it maybe startling to think that contrary to common engineering practice in many older disciplines, where construction starts from a detailed blueprint and calculations, the reliability of software is still largely established by simple trial-and-error: some test inputs are invented in one or the other way (ranging from very simplistic ad-hoc methods to sophisticated methods such as model-based testing [105]); they are given to the software and it is checked whether the expected outcome matches the actual outcome (where the outcome could be a concrete output produced by software, a change in its state, an action that is triggered, etc.). If the outcome is deemed incorrect for any of the test cases, then the software is said to have a bug that needs to be corrected.

Once the outcome for all test cases is correct, the whole system is assumed to function correctly. It was already noted by one of the pioneers of computer science, Edsger Dijkstra, in his influential Turing Award Lecture "The Humble Programmer" [61] that

program testing can be a very effective way to show the presence of bugs, but is hopelessly inadequate for showing their absence [.]

This is even more true for CPS as they continuously interact with the physical world (they are part of a "closed loop" [203]) and thus their expected behavior cannot even be described in terms of simple input/output pairs. In "The Humble Programmer", Dijkstra also suggested a pathway out of this situation [61]:

The only effective way to raise the confidence level of a program significantly is to give a convincing proof of its correctness.

Ever since, this has been the main theme of a subdiscipline of computer science named *verification*. It sets out to give a formal analysis of computer systems that *proves* that the system works correctly under all given circumstances *with mathematical rigor*. Researchers in the field soon came to the conviction that real software is far too complex to be analyzed in this way by hand (e. g. with a mathematical proof of correctness written on paper). This kind

of analysis can nowadays only be found in research papers or university textbooks. Instead, today, verification itself now uses computers to get the job done. That is, verification is usually always understood to be *computer-aided verification*.

With this, the following question immediately arises:

If we use a piece of software (the verifier) to guarantee that another computer system works correctly, how can we trust the result of the whole verification process if the verifier itself could have a bug?

This, of course, is an important question to answer, especially if verification is meant to be applied to CPS on which we want to trust our lives in the end. In this thesis, I attempt to answer this question for a certain class of CPS, so-called real-time systems (RTS) [113], by using a combination of different techniques from computer-aided verification.

## 1.1 Research Objective

In the following, I want to state the research objective that I just outlined in more explicit terms. I will start by summarizing the two particular flavors of computer-aided verification that this thesis is concerned with: interactive theorem proving and model checking.

Out of the two, interactive theorem proving [190, 167] is the older and more versatile method. It is built around the idea that formal logics are perfectly suited for being mechanized as computer programs. One such program is a proof checker: given a logical formula and a proposed proof for it (in some formal proof calculus), the proof checker either confirms that the given proof is indeed a valid proof of the formula, or it rejects the proof. This approach was pioneered by De Bruijn's Automath [145].

The logical formula and the proposed proof are usually written by a human. Thus this idea naturally leads to the concept of a proof assistant: in addition to providing the capabilities of a proof checker, the program also assists the user while developing the proof. Typically, this always includes feedback on the validity of individual proof steps while the user is spelling out the proof. However, the assistance can also take the form of more sophisticated features such as search tools for finding useful proven theorems, suggesting full proofs automatically, or identifying unprovable statements. In any case, the proof is developed through interaction between the user and the computer. Hence this method is also called *interactive* theorem proving. The terms "interactive theorem prover" and "proof assistant" are used interchangeably in the research community. I will also use both terms in this thesis.

In contrast to interactive theorem provers, a third form of these "logical programs", automated theorem provers [69], only take a formula as their input and try to automatically find a proof for it. With Newell's "Logic Theorist" [139, 82], this approach was studied even before the proof checker idea came along, as early as in 1956. Automated theorem proving is still an active field of research today but will not play a further role in this thesis. The reason is that these systems are typically not capable of proving anything as complex as I set out to do. While they have been used to resolve open mathematical conjectures [98] or to (semi-automatically) verify programs and algorithms [79], they lack in expressivity. Therefore, to me, there does not seem to be a simple way to apply them to anything that mixes a larger body of mathematical theory and verification of software. Nevertheless, automated theorem provers still played a crucial part in my work: they can be connected to proof assistants to find proofs for intermediate propositions automatically [31, 30, 160] and thus made my work significantly easier.

The main strength of interactive theorem proving is its expressivity. The logics that are typically used are powerful enough to capture computer programs on the one hand but also

to state any mathematical proposition on the other hand. This is also reflected in the broad range of domains that proof assistants have already been applied to: in the verification of an operating system [112] and a C compiler [24], for instance, but also for proving mathematical theorems like Hales' proof of the Kepler conjecture [86], the Four Colour theorem [75] or the Odd Order theorem [76]. The big weakness of interactive theorem proving (as a verification method) is also apparent: it requires human interaction. This makes it a quite laborious task and prevents it from scaling well to the verification of large systems.

Conversely, model checking [11, 53] is a push-button method, i. e. it works fully automatically, but it lacks in expressive power compared to interactive theorem proving. There are many different variants of model checking but they always follow the same basic recipe: the subject of study is a model of a system, and one wants to check certain properties of the model; the model checker's task is to answer these queries with "yes" or "no". The system might be a piece of software or hardware but could also be a board game or a biological process. The model is a description of the system in the language of some mathematical formalism. In the beginning, the formalism of choice was finite-state machines but now a large variety with many different features is in use. This variety is also reflected in the granularity of the model. For a computer network communication protocol, for instance, one could choose to model an abstract description of the protocol that captures how different entities exchange messages and when. Or, one could choose to model the C code of the bus drivers implementing the protocol.

In verification, we want to ask questions about this model. Sticking with the communication protocol example, we could e.g. ask:

Is it true that, whenever the sender emits a message that it will reach the recipient eventually?

Or we could also ask:

Will the sender always get a confirmation of delivery within 10 seconds after the message has reached the recipient?

We can see that these questions have a *temporal* component. Therefore, in model checking, these questions are asked in the form of a tailor-made language, as formulas in a so called *temporal logic* [164]. In the words of logic, the model checker's task can now be reformulated as follows:

Given a *model* and a temporal logic formula, *check* whether the model is indeed a valid model of the formula.

Model checkers have also been applied successfully to a number of complex verification tasks. It may not come as a surprise that there are also modeling formalisms that have been invented specifically to verify CPS, and RTS in particular. One popular such formalism is the concept of timed automata (TA). Since its invention by Alur and Dill in the 90s [2], a rich research area has evolved around it. Different temporal logics have been studied in connection with the formalism [53] and a number of model checkers have been constructed. They have been successfully applied to the verification of numerous real-world examples, ranging from pacemakers [108], over multimedia [90], communication [172], and clock synchronization [169] protocols, to vehicle control software [182].

TA lie at a certain sweet spot between expressivity and decidability within the range of modeling formalisms for CPS. For TA, most important questions can still be answered algorithmically [53], while for any slightly more complex CPS formalism, one can only provide semi-algorithms [181]: if these algorithms give an answer, then it is correct; however, for some

models they might never terminate, i. e. one may never get an answer. It is for this positive characteristic that I chose TA as the subject of study for my research.

Let us now return to the question that I raised at the end of the initial section. We have looked at two types of verification tools, interactive theorem provers and model checkers, and I have given some examples where these tools have been applied to critical systems in the real world. But how do we know that we have gained any assurance in the safety of the systems by applying these tools? How can we be sure that they themselves do not have a bug, jeopardizing the whole effort? For interactive theorem proving, the answer to this question essentially lies within the realm of logic itself. Just like a logical proof can be built from only a very small set of axioms, the proof assistant can implement these axioms in a small inference kernel. Then, every proof has to pass through this kernel to be accepted. This means that we only have to trust that the inference kernel implements the axioms correctly—any other code around it needs not be trusted. This design principle was first implemented in the system LCF [78] and is therefore often called the LCF approach. Many interactive theorem provers follow this tradition [178, 151, 77, 55, 88].

For model checkers, the story is different. They usually rely on a well-understood theory with model checking algorithms that are considered correct with respect to this theory. The arguments for the correctness of theses algorithms are usually spread out as pen-and-paper proofs in different scientific papers. This is a first potential source of errors. Often proofs are only given in a highly abbreviated form, are omitted, deferred to the appendix, or simply incorrect. In any case, it is often trusted to only a small number of experts in the community to understand the arguments for the correctness of model checking algorithms in detail.

Indeed, TA are one of the most prominent examples where this kind of error occurred. In 2003, Patricia Bouyer noticed that the common model checking algorithms that were used at the time (and are still in use today) were incorrect for the general class of timed automata [35]. This was only years after the first TA model checkers had been constructed and had already been used to verify real-world models. Fortunately, in practice the error could only lead to spurious incorrect behaviors of models being detected, and thus did not lead to any incorrect models be verified. Another notable example is an incorrectness in the widely-used partial order reduction technique which was only discovered last year [171]. This error could indeed have potentially fatal consequences by allowing unsafe models to be deemed correct by the model checker.

More common sources of errors, however, are in the implementation of a model checker. First, these tools are complex pieces of software, and as with any complex software (that is programmed by a human) there is ample room for human error. Second, while the model checking algorithms that are established in research can usually be considered correct, they typically have to be augmented with many small optimizations in the implementation to make the resulting model checker efficient. These optimizations are often very subtle and are frequently done on the spot, without even attempting to give a new correctness proof on paper.

For these reasons, proof assistants are often considered more trustworthy than model checkers. "But is that really so?", you might contest, "After all the axioms of your logic and their implementation in the inference kernel could also be incorrect". While that is certainly true, I would still argue that interactive theorem provers reach essentially the highest standard of trustworthiness that could be imagined. First, for one of them, HOL Light [89, 117], another layer of assurance has been added: the inference kernel itself was modeled in interactive theorem provers (HOL Light and HOL 4) and it was proven that it only allows sound logical inferences. Repeating this effort can certainly be imagined for any other proof assistant. But even for interactive theorem provers that lack such a formal proof of correctness,

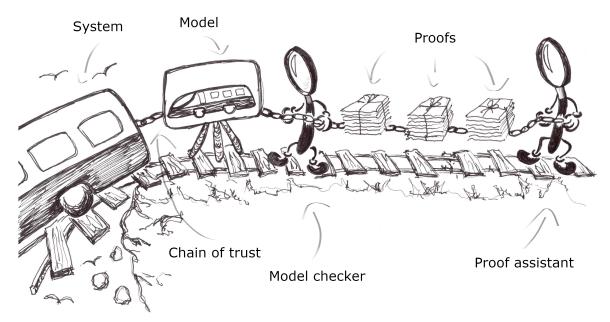

Figure 1.1: Illustration of trust reduction.

the trustworthiness of their kernel is manifested as a community effort. On the one hand, it is assumed that enough people have read and checked the code of the inference kernel. On the other hand, established tools can usually look back at a history in which many have used the tool but in which logical inconsistencies have only been discovered extremely rarely. I consider such an inconsistency much easier to spot than if a model checker gives an incorrect answer for a non-trivial model.

Finally, the most convincing argument is probably given by simply considering the size and complexity of the code that needs to be trusted in order to trust the verification result. To "trust" means here to assume that the code is programmed correctly. This is often referred to as the trusted code base (TCB) of a verification tool. For an interactive theorem prover, this may range from a few hundred to a few thousand lines of ML or OCaml code, while for model checkers the TCB may reach tens of thousands of lines of highly optimized C or C++ code. A similar argument can be given on the level of the formalisms. The axioms of a formal logic are typically much easier to be stated and to be checked by a human than the description of a modeling formalism and a temporal logic with corresponding model checking algorithms.

From this discussion, one can now derive the following idea of a "trust reduction". It is illustrated in Figure 1.1. Our goal is to obtain RTS (the train in the picture) that are as trustworthy as possible (e.g. to keep the train from taking a wrong turn and falling off a cliff). For this, we can model them (or more precisely, e.g. their control unit) as timed automata, and phrase a description of the RTS's correct behavior as a temporal logic formula. We then use a model checker to ensure that the model really exhibits the intended behavior. We have thus reduced our trust in the RTS to the question of whether we trust the model checker and the models and formulas we came up with. To increase our level of trust further, we can now attempt to reduce our trust in the model checker to trusting an interactive theorem prover instead. The theme of this thesis is to add this last step to the trust reduction chain. As I argued in the last paragraph, this is one of the highest levels of trustworthiness that we can reasonably expect to achieve.

# 1.2 Summary of Contributions

Now that I have laid out the goal of my research, I want to give a brief overview of what I have done to get there. As I already stated above, my model of choice are TA. My proof

assistant of choice is Isabelle/HOL [152]. Isabelle is a generic theorem prover that can in principle host a range of different object logics. Out of these, HOL is the most widely used flavor, which has also been implemented in many other systems [77, 88]. The logic provides a good tradeoff between expressivity and convenience of use, offering advantages such as fully automated type inference. Its implementation in Isabelle, Isabelle/HOL has been successfully applied to large efforts in verification [112, 86, 175, 65, 138].

There are multiple reasons for my choice of Isabelle/HOL. The most obvious are of social nature: I have been introduced to this tool already during the second semester of my undergraduate studies and later I joined Tobias Nipkow's research group in Munich that has been at the core of Isabelle development for years. However, Isabelle/HOL was also the most suitable choice beyond these social factors. I see three main points here.

First, Isabelle/HOL arguably offers the highest level of proof automation among all interactive theorem provers. This is mainly due to its powerful term rewriting engine, the *simplifier* [148], and its ability to hand off proof obligations to automated theorem provers and SMT solvers via the *Sledgehammer* tool [31, 30, 160]. However, there are also many other facets, such as offering the most convenient user interface, and a general culture of developing the tool with automation in mind.

Second, Isabelle/HOL offers a mature facility for *code generation* [84, 83]. This component allows one to export code in the functional programming languages Standard ML, OCaml, Haskell, and Scala from definitions in HOL. This feature is essential if one does not only aim to prove some mathematical theory correct but to also obtain practically usable verified software in the end.

Third, the fact that Peter Lammich has also conducted his work on refinement [123, 126, 127] in Isabelle/HOL. Building on this work, we were able to produce efficient highly trustworthy tools for TA model checking. If it were not for this previous work, I would probably have obtained highly trustworthy but terribly inefficient verification tools. A particularly fortunate coincidence was that his work on refinement to imperative code [126] had just emerged when I was looking into extracting verified tools for the first time.

As I outlined at the end of the last section, the overarching goal of the work that is presented in this thesis is to take one further step in the chain of trust reduction. This is, to replace the need to trust timed automata model checkers with trusting Isabelle/HOL instead. Another way to view this is as an effort in greatly reducing the TCB of timed automata model checking. I will now sketch the steps of my journey to achieve this goal.

Theory comes before its implementation. Therefore, before one can consider concrete model checking tools, the first natural step is to ensure that the theory behind them is sound. This was the first part of my work. In the basic recipe, one first defines TA in Isabelle/HOL and assigns a mathematical meaning to them (i. e. one defines their *semantics*). Then, one defines the model checking question. Recall that, usually, this question would be:

Is the given timed automaton a valid model for the given temporal formula?

However, in this first step I simplified the question by restricting the formula to so-called reachability properties. Speaking in terms of verification, reachability properties are highly useful for asking whether the system can ever encounter a fatal error, i.e. whether a fatal system state is *reachable*. In fact, in practice, model checking of timed automata is often restricted to or concerned with reachability properties. Nevertheless, I also provided an avenue to extend my work to more complex temporal properties later on.

So, at first, I proved in Isabelle/HOL that the essential constructions that are used in the most widely used approach for TA model checking are correct [191]. On the one hand, this is the region construction that was already put forward in the seminal paper by Alur and Dill [2].

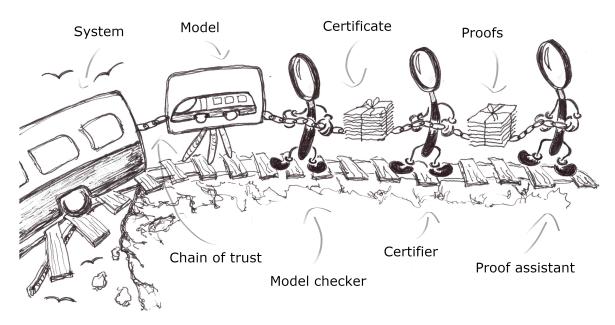

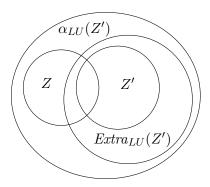

Figure 1.2: Illustration of trust reduction with certification.

On the other hand, there is a more scalable approach that relies on so-called zones to capture the time component of TA states symbolically. It was exactly this approach that was found to be wrong by Patricia Bouyer in 2003 [35]. My work mainly relies on her proofs that repair the classic results on zone-based model checking for the case of diagonal-free timed automata [34]. What makes the formalization of this work in Isabelle/HOL particularly interesting is that her proofs are rather intricate and themselves rely on the correctness of the region construction provided by Alur and Dill. We can now say with high certainty (in so far as we trust Isabelle/HOL) that Patricia Bouyer's work indeed salvages the theory of zone-based TA model checking and that no further fundamental errors have snuck in.

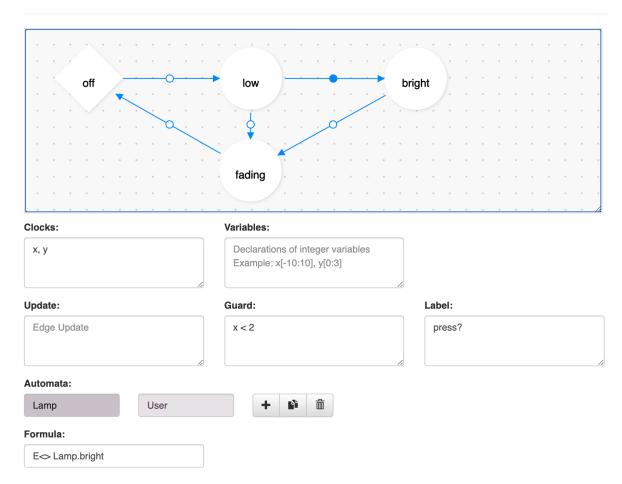

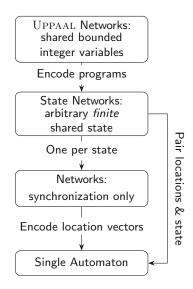

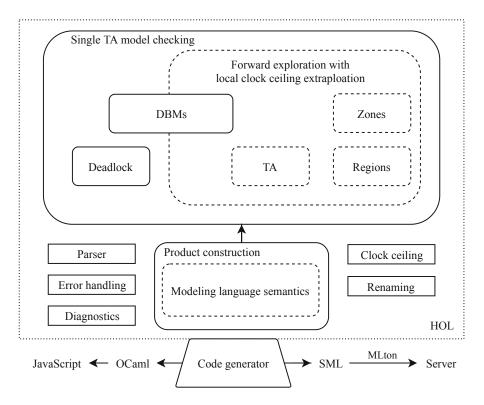

From the theory I could then move to tools. That is, my next goal was to consider actual model checkers for timed automata. I have considered two main approaches, verification and certification. In the verification approach (as illustrated in Figure 1.1), the goal is to construct the model checker fully within Isabelle/HOL accompanied by a proof of its correctness. We followed this approach in joint work with Peter Lammich [197]. Starting from the theory that I formalized in the first step, we developed verified abstract implementations of the main algorithms that are similar to the ones that are at work in the popular tool UPPAAL [16]. In the next step, we relied on Peter's previous work to refine these algorithms in multiple steps to turn them into concrete and efficient programs. Finally, we used Isabelle/HOL's code generator to obtain an actual executable version of the model checker that is comparable in its core functionalities to UPPAAL. One of the highlights of this work is that we were able to implement the main data structure that is used for the aforementioned zones, Difference Bound Matrices (DBMs) [19], imperatively. This way, we can achieve comparable efficiency to unverified model checkers. Later, I improved on this work by equipping the model checker with further capabilities and a graphical user interface. The resulting tool was named Munta [192, 196].

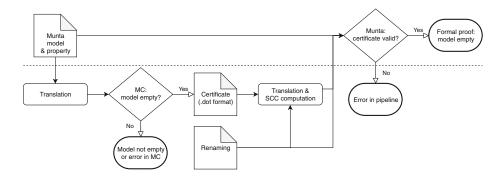

In the certification approach<sup>1</sup>, one does not simply attempt to supersede existing unverified model checkers but rather tries to validate their work. The idea (as illustrated in Figure 1.2) is that the model checker runs normally but in addition to just producing a yes/no answer, it also emits a proof that this answer is indeed correct, the *certificate*. Another tool, the *certifier* can then validate that the certificate is in fact a valid proof of the answer. If the certifier is in

<sup>&</sup>lt;sup>1</sup>In the literature, "to certify" sometimes refers to the act of verification with the help of a proof assistant. I will only strictly use the terms "to certify" and "certification" for what I describe in the following.

turn a tool that was proven to be correct in Isabelle/HOL, we can achieve the same level of trustworthiness as for the verification approach, without the need to construct a full model checker in Isabelle/HOL. We sacrifice *completeness*, however: if the model checker's certificate is rejected by the certifier, we know nothing. Conversely, if the certificate is accepted by the certifier, we know that we can put high trust in the model checker's answer.

Note that one can always build the trivially correct certifier that simply rejects every input. Thus one also has to argue for its non-triviality at least informally. One such completeness property would be that for every valid pair of a model and a formula, there is a certificate that will be accepted by the certifier. In addition, one could attempt to show that the certifier accepts any valid certificate. Proving any of these results might potentially require significantly more background theory, however. Moreover, even if we have proved both of these completeness properties, in the case that a certificate is rejected, we still cannot infer the reason for that. The cause could be a bug in the model checker or the certificate extraction, or the model might simply not satisfy the formula.

Certification has two main advantages. First, it can be much easier to verify the certifier in a proof assistant. Second, checking that the certificate is correct may be computationally much simpler than full model checking. For TA, we know that the asymptotic worst-case time complexity of certification is the same as of model checking because the problem is PSPACE-complete [2]. Yet, still, it turns out that the certificates can be checked much more efficiently for concrete models than performing full model checking in Munta.

Building on the existing work for Munta, I have first studied this approach in joint work with Joshua von Mutius for reachability properties [198]. With Frédéric Herbreteau and Jaco van de Pol, we have later extended this work towards so-called *liveness* properties [193], providing a crucial corner stone to handle full *linear temporal logic (LTL)* [164].

To conclude this section, I want to briefly touch on a few important points that are outside the scope of this thesis. Figuratively speaking, the work presented in this thesis extends the chain of trust for the verification process of TA at its tail. However, some potential pitfalls remain at both ends. On one end, we model the system under study (and its environment) using TA and formulate the criteria for its correctness using temporal logic formulas. However, there is no assurance that we do not get the model or the formulas wrong. For the formulas, this problem seems to be fundamental. It is similar to the problems an engineer would run into if they want construct an aircraft but base their calculations on the viscosity of water rather than air. These problems can probably only be addressed socially, i.e. by humans checking each other's work. For the model, there is a range of answers that can be given. First of all, the complete model usually falls into two parts: one for the components of the system and one for its environment. For the environment, the typical solution is over-approximation: the model of the environment should allow all behaviors of the environment in the real world and many more. Still, one also has to get this over-approximation right. If we consider autonomous driving, for instance, we may model other cars and humans on the street but we should also not forget about the notorious gigantic glass pane that might be carried across the street.

On the positive side, if we are certain that we got the formulas and the environment component right, we do not need to be concerned about the system anymore: if the model is a valid model for the formula, the system component has to be correct. There is one more aspect to worry about on the model side, however. We may now have a correct model of the system but how do we get a correct system from it? One solution that has been proposed in a broad body of work is to automatically synthesize code that correctly implements the model by construction [7, 23, 200, 85, 157, 38, 115]. Similarly to what is done in this thesis, the trustworthiness of this method could also be increased by verifying or certifying it with

the help of a proof assistant. But even if we now have code that we trust, how do we know that it will be correctly executed? How can we trust the compiler that turns the code into machine code? How can we trust the operating system that runs this code? And how can we trust the underlying hardware? Luckily, all the questions have already been considered by the verification community and are still the subject of active research [24, 177, 112, 52].

At the end of the chain, there is Isabelle/HOL. I briefly want to detail what exactly it means to trust this end of the chain. Essentially, there are two distinct parts: Isabelle/HOL itself and what I write down in Isabelle/HOL. As I argued above, there is a strong case for trusting a proof assistant like Isabelle/HOL, even though its logical inference kernel has not been verified. I will also discuss the correctness of Isabelle/HOL specifically in further detail in the conclusion (cf. Section 6.2). For what I write down in Isabelle/HOL, the strength of proof assistants being grounded in logic shows up again. Essentially, the only piece that needs to be trusted here is that I correctly define what the mathematical meaning of the TA formalism is, i. e. the *TA semantics*. This part is indeed very concise. It is only about 150 lines of Isabelle/HOL code and thus comparable in size and complexity to a pen-and-paper formulation of the semantics. The crux is now that all other theorems, and specifically the correctness theorem for Munta and the certifier are formulated with regard to this semantics. If you are ready to trust Isabelle/HOL and my semantics, then you can also trust these correctness theorems.

#### 1.3 Outline

To conclude the introduction of this thesis, I want to give a brief outline of its remaining contents. The thesis is based on six publications. In the next chapter, I will introduce the formalism of TA and summarize the main concepts of TA model checking, which will be crucial to understand the rest of the thesis. The subsequent three chapters will each set the stage for two of the papers by summarizing the main ideas, putting them into perspective with respect to the overall theme, pointing to related work, and considering aspects that I would do differently in retrospective.

The first of these chapters (Chapter 3) focuses on formalizing TA and abstract results on model checking in Isabelle/HOL. This also includes joint work with Johannes Hölzl [195], in which we formalized fundamental results about probabilistic timed automata (PTA). This formalism extends TA to model uncertainty, which is often desirable in practice.

The following chapters treat the approaches of verification (Chapter 4) and certification (Chapter 5). Finally, Chapter 6 concludes by providing some general reflections on the research I conducted, examining related work, pointing to remaining limitations, and laying out some future directions of research that build upon this thesis. The appendix consists of the six papers that constitute the thesis. These papers are:

Paper A Simon Wimmer. "Formalized Timed Automata." In: Interactive Theorem Proving - 7th International Conference, ITP 2016, Proceedings. Ed. by Jasmin Christian Blanchette and Stephan Merz. Vol. 9807. Lecture Notes in Computer Science. Springer, 2016, pp. 425–440. DOI: 10.1007/978-3-319-43144-4\_26

Paper B Simon Wimmer and Johannes Hölzl. "MDP + TA = PTA: Probabilistic Timed Automata, Formalized (Short Paper)." In: Interactive Theorem Proving - 9th International Conference, ITP 2018, Proceedings. Ed. by Jeremy Avigad and Assia Mahboubi. Vol. 10895. Lecture Notes in Computer Science. Springer, 2018, pp. 597–603. DOI: 10.1007/978-3-319-94821-8\_35

- Paper C Simon Wimmer and Peter Lammich. "Verified Model Checking of Timed Automata." In: Tools and Algorithms for the Construction and Analysis of Systems 24th International Conference, TACAS 2018, Proceedings, Part I. ed. by Dirk Beyer and Marieke Huisman. Vol. 10805. Lecture Notes in Computer Science. Springer, 2018, pp. 61–78. DOI: 10.1007/978-3-319-89960-2\_4

- Paper D Simon Wimmer. "Munta: A Verified Model Checker for Timed Automata." In: Formal Modeling and Analysis of Timed Systems 17th International Conference, FOR-MATS 2019, Proceedings. Ed. by Étienne André and Mariëlle Stoelinga. Vol. 11750. Lecture Notes in Computer Science. Springer, 2019, pp. 236–243. DOI: 10.1007/978-3-030-29662-9\_14

- Paper E Simon Wimmer and Joshua von Mutius. "Verified Certification of Reachability Checking for Timed Automata." In: Tools and Algorithms for the Construction and Analysis of Systems 26th International Conference, TACAS 2020, Proceedings, Part I. ed. by Armin Biere and David Parker. Vol. 12078. Lecture Notes in Computer Science. Springer, 2020, pp. 425–443. DOI: 10.1007/978-3-030-45190-5\_24

- Paper F Simon Wimmer, Frédéric Herbreteau, and Jaco van de Pol. "Certifying Emptiness of Timed Büchi Automata." In: Formal Modeling and Analysis of Timed Systems 18th International Conference, FORMATS 2020. Vol. 12288 LNCS. Lecture Notes in Computer Science. Springer, 2020, pp. 58–75. DOI: 10.1007/978-3-030-57628-8\_4

In the remainder, I will only refer to the papers by their identifiers, Paper A and so on.

# 2 Timed Automata: An Overview

In principle, the papers that constitute this thesis are either written to be self-contained or contain the relevant references to understand the material. However, these publications all needed to make concessions to space requirements, thus discussions of preliminary knowledge are sometimes cut quite short. For this reason and to set a common basis for the whole thesis, this section will explain the most important notions of timed automata and model checking that are relevant for understanding this thesis, without going into excruciating detail. Anyone with a background in computer science or mathematics should be able to understand this material. I will not give an introduction to Isabelle/HOL or other topics pertaining to interactive theorem proving, however. The remaining chapters can largely be understood without this knowledge, and the papers point to introductory material where relevant. To readers interested in an introduction to Isabelle/HOL, I recommend reading the first half of Nipkow and Klein's "Concrete Semantics" [150].

### 2.1 Introduction

Model checking needs to start with a model, of course. As I already state above, many different formalisms for the specification of these models have been studied before. Usually, the basic starting point is the notion of a Kripke structure, transition system or finite-state machine, which are augmented with additional features in more sophisticated modeling formalisms. These three formalisms only differ slightly in their precise definition and can be considered to be the same for the purposes of this thesis. Therefore, I will not explicate these differences here and will only use the term transition system from now on. The nodes of transition systems will be referred to as states and the edges as transitions.

Transition systems are essentially annotated graphs where the nodes of the graphs represent states of some system and edges represent transitions between these states. The nodes and edges can be labeled. One purpose of this is to model *communication* between systems. To this end, a separate transition system is used to model each system in a network of communicating systems. Transitions can then be annotated to model message exchanges over pre-defined channels.

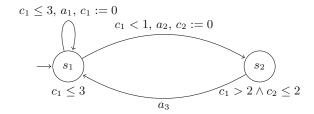

In timed automata [3], transition systems are extended with a notion of *clocks* to model physical time. These clocks act as stopwatches. A transition can choose to reset certain clocks when it is taken. While idling in a state, the time reading on all clocks is elapsing at the same speed (i. e. in physical terms all clocks are perfect). These time readings can be made use of on transitions: a transition can have a *guard* which demands that the transition can only be taken when certain conditions on the current values of the clocks are fulfilled.

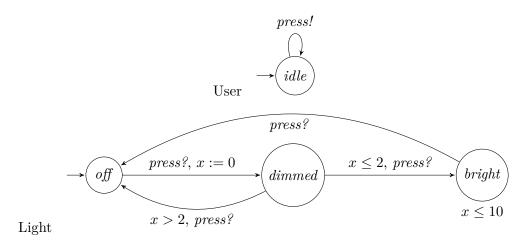

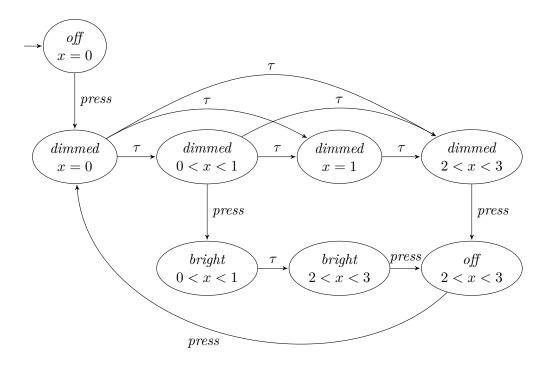

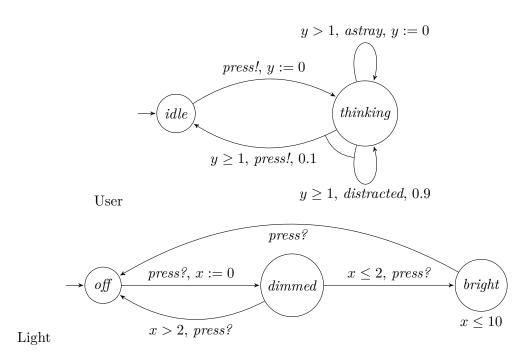

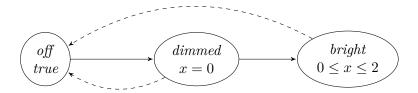

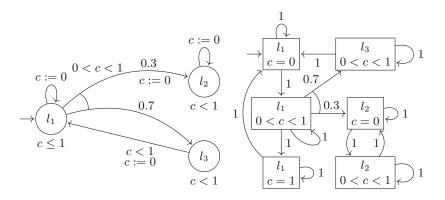

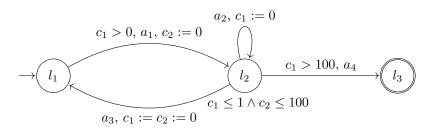

Figure 2.1 gives an example of two communicating timed automata<sup>1</sup>. They only use one channel for communication, which models the physical action of the user pressing the switch. This is often done by designating two special types of *action* labels for ingoing and outgoing actions. In this case, the channel is named *press*, and the input and output actions are *press*? and *press*!, respectively. The automata can *synchronize* on transitions with matching input and output labels, meaning they will take the transition at exactly the same time.

<sup>&</sup>lt;sup>1</sup>Similar examples can be found in the literature, for instance in the tutorial paper by Bengtsson and Yi [19].

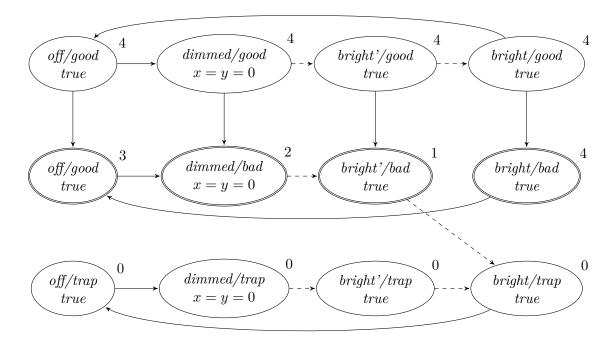

Figure 2.1: An example of two communicating timed automata.

The automata model a simple light switch and its user. The light can either be off, dimmed, or bright. The initial states, off for the light and idle for the user, are marked by short arrows going in from the left. If the user presses the switch once when the light is off, then the light should be turned on and dimmed. If the user quickly (that is, within two seconds) presses the switch a second time, then the light should turn bright. This behavior is achieved by adding the clock x. It is reset to 0 whenever the transition from off to dimmed, which turns the light on, is taken. Then, x is used to measure whether two seconds have already passed. While the value of x is at most two, the transition to the bright state is enabled by the guard  $x \le 2$ . If a second press is not received within this time, then the transition cannot be taken anymore and instead the transition to the off state is enabled by the guard x > 2.

The model also features an *invariant* on the *bright* state. Its meaning is that the system can only stay in this state while the condition  $x \le 10$  is true. This could be used to model that the light can only be bright for at most ten seconds before it has to perform an emergency shutoff due to overheating.

Observe that the model of the user is completely *nondeterministic* as the user can press the switch at any time. This is an example of a useful over-approximation of the environment in modelling. A realistic user will never be able to press the button a second time without a delay of say 10ms, for instance. However, any behavior that can be exhibited by a realistic user (as far as the light switch is concerned) is captured by our model.

#### 2.2 Semantics

I will now briefly give the formal semantics (i. e. the precise mathematical meaning) of the timed automata formalism as a basis for further explanations. As we have seen, clock constraints are used to guard states (as invariants) and transitions. Formally, a clock constraint is a conjunction of constraints of the form  $x \sim c$  or  $x - y \sim c$ , where x and y are clocks, c is an integer constant, and  $\sim$  is one of <,  $\leq$ , =,  $\geq$ , >. Clock valuations are used to give a semantics to clock constraints. A clock valuation is a mapping from clocks to their current time values. That is, if the clocks are drawn from the set X, then any function of type  $X \to \mathbb{R}_0^+$  is a clock valuation. A clock valuation v satisfies a clock constraint  $x \sim c$  iff  $v(x) \sim c$  and a clock constraint  $x - y \sim c$  iff  $v(x) - v(y) \sim c$ . I write  $v \models x \sim c$  or  $v \models x - y \sim c$  to signify this. We need two operations on clock valuations.

**Time shift** For a clock valuation v and a real d,  $v \oplus d$  is defined such that  $(v \oplus d)(x) = v(x) + d$  for any clock  $x \in X$ . That is, the values of all clocks are shifted by time d.

**Clock reset** For a clock valuation v and a set of clocks  $r \subseteq X$ ,  $[r \to 0]v$  is defined such that:

$$([r \to 0]v)(x) = \begin{cases} 0 & \text{if } x \in r \\ v(x) & \text{otherwise} \end{cases}.$$

That is, the values of all clocks in r are reset to 0.

Formally, a timed automaton A is defined as a pair  $(\mathcal{T}, \mathcal{I})$  where  $\mathcal{T}$  is the set of transitions, and  $\mathcal{I}$  gives the invariant for each state, i. e. it assigns a clock constraint to each state. I write an individual transition as  $A \vdash q \longrightarrow^{g,a,r} q'$  where:

- q and q' are a start and target state;

- $\bullet$  g, a clock constraint, is the guard of the transition;

- a is an action label (used for communication in networks);

- $\bullet$  and r is the set of clocks to be reset when the transition is taken.

A configuration of a timed automaton is a pair (q, v) consisting of a state q and a valuation v. These are the semantic states of a timed automaton. The operational semantics define two kinds of transitions on configurations.

**Delay** There is a *delay* transition  $(q, v) \to^d (q, v \oplus d)$  if  $d \ge 0$  and  $v \oplus d \vdash \mathcal{I}(q)$ .

**Action** There is an *action* transition  $(q, v) \to_a (q', [r \to 0]v)$  if  $A \vdash q \longrightarrow^{g,a,r} q', v \vDash g$ , and  $[r \to 0]v \vDash \mathcal{I}(q')$ .

A run of a timed automaton is an arbitrary sequence of delay and action transitions. Note that consecutive delay transitions can always be combined into a single delay transition. Moreover, between two consecutive action transitions, a delay transition with time value 0 can always be inserted. Thus, typically one only considers runs that are a strict interleaving of delay and action transitions, as given by the following transition system:

$$(l, v) \to (l', v') = (\exists d \ge 0. \ \exists a \ v''. \ (l, v) \to^d (l, v'') \land (l, v'') \to_a (l', v')).$$

Some general remarks about this semantics are in order. First, many extensions of timed automata have been studied [34, 43]. Generally, most extensions render model checking questions for TA undecidable [34, 46], with the notable exception of priced timed automata [43]. Thus, TA can be said to sit at a certain sweet spot between expressivity and decidability.

One restriction of TA is particularly important, namely diagonal-free TA. In diagonal-free TA, difference constraints of the form  $x-y\sim c$  are disallowed (in guards and invariants). This is important because Bouyer showed [35] that the typical DBM-based model checking algorithms for TA are incorrect when difference constraints are allowed. Therefore, the restriction to diagonal-free TA is usually made. Luckily, this does not mean that we will lose in expressivity: any TA can be translated to an equivalent diagonal-free TA [2, 20]. The translation may lead to an exponential blowup in the size of the automaton, however. There are also more practically efficient methods for model checking TA with difference constraints [19, 36, 73]. Still, in practice, mostly TA without difference constraints are used. For these reasons, like many authors in the field, I restricted this thesis solely to the study of diagonal-free TA.

Finally, a particularity to consider in connection with the semantics of formalisms for timed systems in general is the notion of Zenoness. A run of a TA is Zeno if it makes infinitely many transitions in only a finite amount of time. It is generally agreed upon that such runs should be excluded from consideration because they are not realizable in practice. There are multiple ways to handle this complication. First, any timed automaton can be converted into a strongly non-Zeno automaton that does not allow any Zeno runs but preserves all other behaviors. This conversion can lead to an exponential blowup (in the size of the automaton) however [96]. Thus, alternatively, specific model checking methods that try to avoid this exponential blowup in practice can be used [96]. The most common approach is to simply consider automata that allow non-Zeno runs to be incorrect models because they allow unrealizable behaviors. This condition can be checked algorithmically [180, 93]. Therefore, most authors work under the assumptions that all automata are strongly non-Zeno. I follow this convention (where relevant).

Usually, not a single timed automaton but a network of timed automata is considered. I will not give a precise definition for the semantics of such networks but rather allude to intuition. Essentially, such a network of automata is equivalent to a single TA, the *product automaton*. It uses vectors of states, with one dimension to record the current state of each automaton in the network. Each internal transition of a single automaton gives rise to a transition in the product automaton, where only the state of this single automaton is updated in the state vector. Synchronization over a channel with matching input and output transitions yields transitions in the product automaton that update two components of the state vector at the same time. The initial state of the product automaton is the vector of all initial states.

The product automaton for the TA in Figure 2.1 is trivial because the automata synchronize on every transition: it would look exactly like the automaton for the light switch with every state replaced by a state vector that has *idle* as its first component. Similar techniques can be used to add many more features to the formalism, such as shared program variables or other notions of communication.

Finally note that the network in the example has a slight semantic oddity. Because of the invariant on the *bright* state and because the automata have to synchronize on every transition, the user is effectively forced to press the button another time after at most 10 seconds. In a more realistic model, we would therefore add another transition from *bright* to *off*, which does not have to synchronize on *press*. I have omitted this to simplify the following examples.

## 2.3 The Model Checking Task

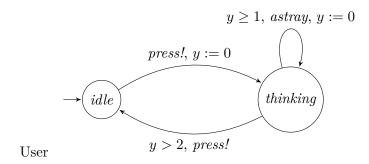

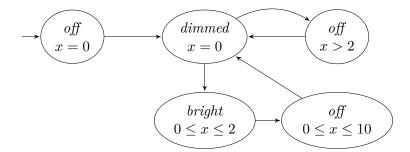

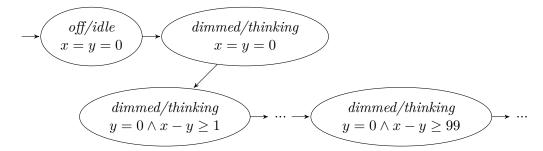

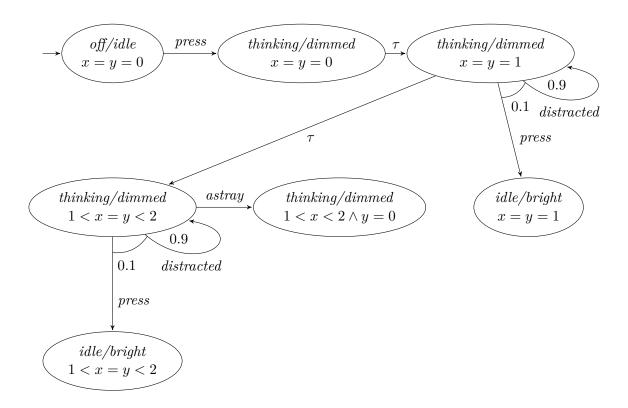

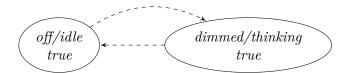

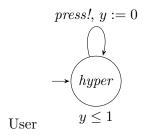

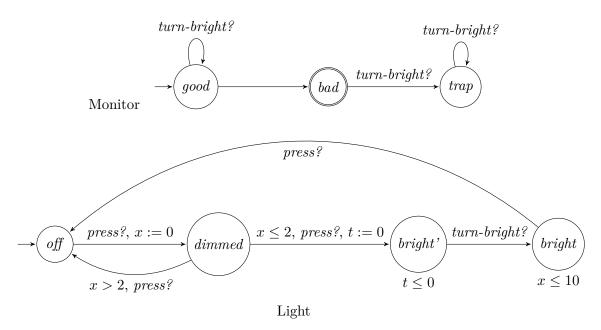

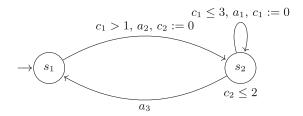

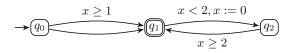

We are now ready to formulate model checking questions for TA. I will focus on the aforementioned reachability question for TA for now. It is whether a certain final state  $q_f$  can be reached from the initial state  $q_0$ . For networks of timed automata, one often considers the question whether a state vector can be reached, in which a single state automaton is in a final state. In the example from Figure 2.1, for instance, we could ask wether the light can ever turn bright, i.e. whether we can reach a state where the light switch is in state bright. For this model the answer is "yes" because the user can press the switch with arbitrary speed. If we model the user as in Figure 2.2, however, and add a second clock y and a state thinking, then the user is always too slow and the answer is "no".

For now, the model checking task I will focus on, is to provide an algorithm that can answer such reachability questions. This is not trivial as there are infinitely many clock valuations and thus there are (usually) infinitely many states in the semantics of TA. The rest of this section will give a brief overview of the most prominent approaches to derive such an algorithm. In

Figure 2.2: A modified version of the user model from Figure 2.1.

general, the model checking task is to check whether the model fulfills a formula from a range of different (timed) temporal logics [53]. I will revisit this question in Chapters 4 and 5.

## 2.4 Regions

It was already discovered by Alur and Dill [2] that most interesting properties of timed automata, including the reachability task, can be decided algorithmically. At the heart of all these algorithms lies the so-called region construction [2]. In the following, I will briefly sketch the core ideas behind the construction. For a more gentle introduction, see Chapter 9 of Baier and Katoen's textbook "Principles of Model Checking" [11].

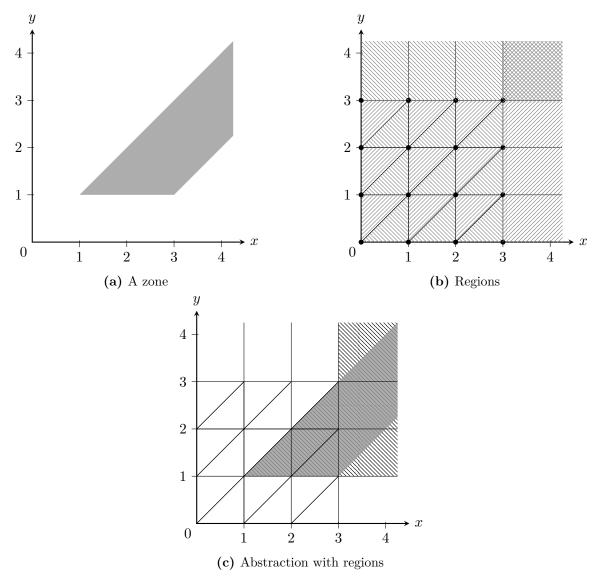

Considering Figure 2.1 again, a first key observation is that we are never interested in values of x for which x > 10. The reason is that there is no guard in the automaton which makes a comparison against a larger number than ten. Therefore, we do not need to know whether x = 10.1 or  $x = 10^{10}$ . We are just looking for the fact x > 10. Moreover, it is also irrelevant whether x = 1.4 or x = 1.999. As long as the clock constraints in the TA are only made up of integer constants, valuations with either value of x will always satisfy the same constraints. These observations give rise to a *finite* partitioning of the clock valuations into the regions, i. e. distinct sets of clock valuations. These are the points x = 0, x = 1, ..., x = 10; intervals of the form 0 < x < 1, 1 < x < 2, ..., 9 < x < 10; and unbounded regions capturing all valuations where the largest constant in the automaton has been exceeded, in this case the single region given by the constraint  $x > 10^2$ .

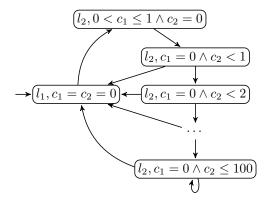

From these regions and the original TA, one can now construct a finite transition system, the region automaton. The states of this transition system are pairs of a state of the underlying TA and a region. There is a transition between two states of the region automaton if there is a transition in the semantics of the underlying TA between any of the valuations contained in the region. A part of the region automaton for the light switch example is depicted in Figure 2.3. As there are only finitely many regions, the region automaton is also finite. This means that we can easily decide the reachability question from the region automaton: we simply need to check whether a state in the region automaton that contains a final state of the TA is reachable. This task can be handled by standard search algorithms for graphs. In the example, we can see that the state (bright, 0 < x < 1) is reachable in the region automaton and thus we know that the state (bright, x = 0.1) is also reachable in the TA.

The disadvantage of the region construction is that there are prohibitively many regions when the number of clocks is increased as the number of regions grows exponentially in the number of clocks. This renders the construction rather useless for practical applications.

<sup>&</sup>lt;sup>2</sup>An example for two clocks appears in the next section.

Figure 2.3: Part of the region automaton for the light switch given in Figure 2.1.

## 2.5 Zones and Abstractions

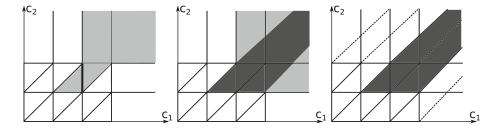

To overcome the limitations of the region construction, research on TA model checking has focused on finding larger "partitions" of the clock valuations to obtain smaller transition systems on which reachability can be decided. The basic idea is to consider so-called *zones* instead. A zone is a set of valuations that can be described by a clock constraint. This means that every region is also a zone. Also note that every zone is *convex*. Figure 2.4a depicts the zone given by  $y \le x \land x - y \le 2 \land y \ge 1$ . The state space of a TA can be explored symbolically with zones because it is possible to compute the following operations:

Arbitrary delay  $Z^{\uparrow} = \{v \oplus d \, | \, v \in Z \land d \ge 0\}$

Clock reset  $[r \rightarrow 0]Z = \{[r \rightarrow 0]v \mid v \in Z\}$

Intersection with a constraint  $Z \cap g = \{v \mid v \in Z \land v \models g\}$

By "compute" I mean here that these operations that were defined semantically on sets are operations that again yield zones. We are interested in the *strongest postcondition* of a transition  $q \longrightarrow^{g,a,r} q'$ . For a given state Z, it consists of all the valuations v that are reachable from any valuation  $u \in Z$  by taking any delay transition followed by the action transition  $q \longrightarrow^{g,a,r} q'$ . The strongest postcondition can be computed as follows:

$$Post(q \longrightarrow^{g,a,r} q',Z) = \{[r \to 0](Z^{\uparrow} \cap I(q) \cap g) \cap I(q')\}.$$

Similarly to the region automaton, we can then define a transition system on zones. The reachable part of this transition system is called the *zone graph*. Figure 2.5 depicts the zone

**Figure 2.4:** Illustration of (a) the zone given by the constraint  $y \le x \land x - y \le 2 \land y \ge 1$ , (b) the set of regions for two clocks x and y with the upper bound three (given as points, solid line segments, and hashed areas), and (c) the abstraction of the zone with its covering union of regions.

graph for the TA from Figure  $2.1^3$ . It can be seen that it is smaller than the region automaton and that we can decide reachability properties just as easily from it.

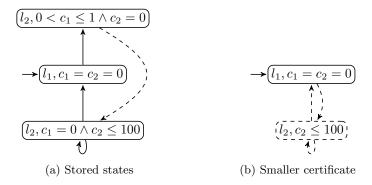

This need not always be the case, however. Figure 2.6 shows part of the zone graph for the system consisting of the user model from Figure 2.2 and the light switch model from 2.1. We can see that it is infinite, making it useless for algorithmic exploration. To overcome this problem, so-called *abstractions* are used [59]. An abstraction is an operation that computes an over-approximation of a zone. It should have the property that only finitely many such over-approximations can be computed. The zone graph where an abstraction is applied to every node is called the *abstract zone graph*. It is always finite. An abstraction should also be *precise*, in the sense that every run of the TA can be simulated by a path in the abstract zone

<sup>&</sup>lt;sup>3</sup>The state component for the user is not shown as there is only one state. I will follow this convention for the remainder of the thesis.

Figure 2.5: The zone graph of the TA from Fig. 2.1.

Figure 2.6: Part of the (infinite) zone graph of the TA from Fig. 2.2.

graph (which goes through the same locations) and every path of the abstract zone graph can be instantiated to a corresponding run of the underlying TA.

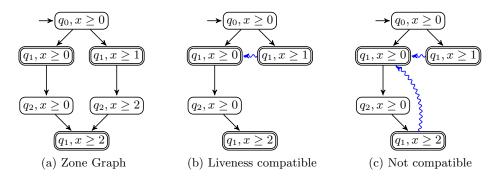

I will introduce one such abstraction by example. Assuming that the maximal constant in the automaton is 3, Figure 2.4b gives the regions for two clocks x and y. The abstraction computes the union of regions that cover a zone. This is illustrated in Figure 2.4c (for the zone from 2.4a). The abstraction is sound but not very useful<sup>4</sup>: as we can see from the picture, this abstraction is not necessarily convex and thus not a zone. Instead, other abstractions that always yield zones have been introduced [59, 13, 14]. These are often called *extrapolations*. It is these extrapolations for which Bouyer discovered soundness issues [35]. We will revisit the topic of abstractions in Chapters 3 and 5.

### 2.6 Difference Bound Matrices

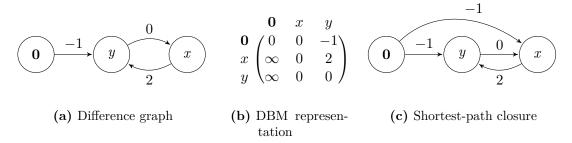

In practice, zone-based model checking algorithms for TA represent zones with the data structure of Difference Bound Matrices (DBMs). I will now give a brief explanation of this data structure. Every clock constraint can be seen as a weighted graph with the variables as nodes and where the edges represent difference constraints on these variables. Figure 2.7 illustrates this for the clock constraint  $y \le x \land x - y \le 2 \land y \ge 1$ . It is first converted into the equivalent set of difference constraints  $y - x \le 0 \land x - y \le 2 \land 0 - y \le -1$ . An edge from x to y with weight c is added to the graph if there is a difference constraint of the form  $x - y \le c$ . To encode constraints that only compare a single clock to a constant, a special node  $\mathbf{0}$  is added to the graph, representing an artificial variable that always has the value 0. Then the graph in Figure 2.7a can be read off directly. Any path in the graph corresponds to a difference constraint that is implied by the original clock constraint. For instance, from the path  $\mathbf{0} \xrightarrow{-1} y \xrightarrow{0} x$ , we can derive the constraint  $0 - x \le -1$  (or  $x \ge 1$ ).

<sup>&</sup>lt;sup>4</sup>Note that many years later Herbreteau et al. have found a way to make practical use of it nonetheless, even if only implicitly [95]. This will be relevant in Chapter 5.

**Figure 2.7:** A graph representation of the zone  $y \le x \land x - y \le 2 \land y \ge 1$  (a), its representation as a DBM (b), and its shortest-path closure (c).

We can also represent such a graph in matrix form as in Figure 2.7b. This matrix form representation is called a DBM [62]. The advantage of this representation is that all the operations that are necessary to compute the strongest postcondition of a transition can be computed efficiently on it. There is also a normal form for DBMs, which corresponds to the shortest-path closure of the underlying weighted zone graph. For the example, the shortest-path closure is depicted in Figure 2.7c. On DBMs, it can be computed with the Floyd-Warshall algorithm [19]. Viewed from the angle of difference constraints, the normal form of a DBM represents the set of the tightest difference constraints that can be derived from the original DBM. Normal forms are convenient because the strongest postcondition of a transition can be computed more efficiently on them and the questions of emptiness and subsumption (whether one zone is a subset of another zone) can be decided easily on them. Therefore, model checkers usually maintain the invariant that all DBMs stored are in normal form.

Note that the above presentation has been simplified in that constraints like x - y < c were not considered. To also include this type of constraint, DBMs do not store numbers but entries of the form (<,c),  $(\leq,c)$ , and  $\infty$ . Arithmetic on this domain can be defined in a straightforward way. Alternative data structures to DBMs to represent zones such as minimal constraints graphs have been considered but DBMs seem to be most efficient for model checking in practice (while other methods can decrease memory consumption) [19].

# 2.7 Other Model Checking Approaches

Other model checking methods do away with zones completely, and instead represent the (explored) state-space of a given TA fully symbolically. In comparison, the zone-based method can be described as semi-symbolic because the states of TA are represented explicitly in the zone graph, while the time-component is represented symbolically in DBMs. The fully symbolic methods fall into two categories: methods based on tailor-made data structures similar to binary decision diagrams (BDDs) [184] and methods based on general-purpose solvers for the satisfiability modulo theories (SMT) problem [142, 111]. While both approaches promise some convincing performance advantages, they are usually not used in practice. One reason is that implementations of these methods in "real-word" model checkers like UPPAAL are missing. Another is that, compared to the rich modeling language offered by UPPAAL for instance, the modeling formalism has to be severely restricted to apply these methods. Therefore, I only considered the classic, semi-symbolic approach to timed automata model checking in my work. This is what I will refer to by TA model checking in the remainder of this thesis.

## 2.8 Summary

The following is a summary of the key points that I tried to convey in this section.

- Transition systems are labeled graphs that model a system. Their nodes are called states and their edges are called transitions.

- Timed automata (TA) extend transition systems with clocks to model time. Clocks can be reset when a transition is taken. Clock constraints are used in guards and invariants. Guards impose an enabling condition on transitions. Invariants restrict the idling behavior of TA.