# Hardware-Software Co-Design of Deep Neural Networks: From Handcrafted to Automated Design and Deployment

### Nael Y. A. Al-Fasfous

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

### Doktors der Ingenieurwissenschaften (Dr.-Ing.)

genehmigten Dissertation.

#### **Vorsitzender:**

Prof. Dr.-Ing. Georg Sigl

#### Prüfende der Dissertation:

- 1. apl. Prof. Dr.-Ing. Walter Stechele

- 2. Prof. Dr.-Ing. Dr. h. c. Jürgen Becker, Karlsruher Institut für Technologie (KIT)

Die Dissertation wurde am 04.05.2022 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 18.08.2022 angenommen.

Two truths cannot contradict one another.

GALILEO GALILEI

## Acknowledgement

My deepest gratitude goes to my supervisor, mentor, and role model, Prof. Dr.-Ing. Walter Stechele, for his continuous support throughout this work. Walter's kindness, guidance, and calm demeanor gave me the confidence and reassurance I needed during the highs and lows of this journey. I am eternally indebted to Walter for his impact on this chapter of my life. I also have to express how grateful I am to have undertaken this journey with Dr.-Ing. Alexander Frickenstein and Manoj-Rohit Vemparala. The three musketeers. A key motivator to keep going when times are hard is to see that others have not stopped. We were the perfect sparring partners for each other. We celebrated each other's successes and gave comfort to each other during the hard times. Even being away from friends, family, and most colleagues during the pandemic years, I never felt lonely in this endeavor, always having them by my side. To my mother, my father, my sister, and my late brother, thank you for your continuous support throughout my life, some things cannot be expressed in words on a paper. To my friends, Ramzi, Serina, Endri, Jose, Jorge, and Anne, thank you for taking care of me like my own family would. I would like to thank my colleagues at the Chair of Integrated Systems at the Technical University of Munich, BMW AG, Politecnico di Torino, Karlsruhe Institute of Technology, and the FINN team at AMD Xilinx for being great academic and industry partners and nurturing strong collaborations that will go on beyond the scope of this work.

## **Abstract**

Over the past decade, deep neural network (DNN) algorithms have become increasingly popular in the field of machine learning (ML). Year-on-year improvements in off-the-shelf parallel computing hardware and the accessibility of big data have democratized the training, optimization, and development of DNNs. After rapidly surpassing classical algorithms in many domains, such as autonomous driving and robotics, DNNs solidified their state-of-the-art status for a wide range of classification and forecasting problems. Along with their popularity, new use-cases emerged to incorporate them in more deployment scenarios, ranging from constrained edge deployment to safety-critical settings. These presented several challenges in hardware and software design, where tight latency, energy, and resource budgets are typically set. This work reinterprets concepts from the mature discipline of hardware-software (HW-SW) co-design, which provides processes for finding synergies when deploying complex algorithms on hardware with precise execution targets and deployment costs. Handcrafted, semi-automated, and fully-automated methodologies are proposed to introduce co-design at different stages of development with varying design challenges. Hardware models in the form of analytical schedulers and mappers, look-up tables, hardware-in-the-loop setups, and differentiable regression models are developed to inject hardware-awareness into co-design problems for general-purpose or customized platforms, and spatial or dataflow architectures. Abstraction levels are exploited to enable divide-andconquer approaches that tackle design challenges throughout the HW-SW development life cycle. The contributions shed light on the benefits of bringing together algorithm and hardware design to achieve the targets set in both worlds, while reducing the independent development effort on both sides and avoiding incoherent design compromises. Over the course of this work, hardware components were handcrafted to suit different types of neural network computations. Genetic and gradient descent algorithms, autoencoders, and reinforcement learning agents were used to compress neural networks. Fast analytical hardware models were developed for evaluation and automated hardware design. Neural networks were made safer by analyzing threats of adversarial attacks and hardware errors on their function, and training them for joint efficiency, robustness, and accuracy preservation. The resulting co-designed algorithms tackled autonomous driving problems with high efficiency, enabled power-forecasting on multiprocessor chips, provided mask detection and correction during the COVID-19 pandemic, and empowered semi-autonomous prostheses for amputees. The contributions of this work in HW-SW co-design of DNNs brought applications with societal impact to edge devices.

## Zusammenfassung

Im Verlauf der letzten zehn Jahre sind tiefe künstliche neuronale Netze (engl. deep neural networks (DNNs)), eine Kategorie selbstlernender Algorithmen, im Bereich des maschinellen Lernens (ML) immer beliebter geworden. Jährliche Verbesserungen bei handelsüblicher paralleler Computerhardware und die Zugänglichkeit von "Big Data" haben das Training, die Optimierung und die Entwicklung von neuronalen Netzen demokratisiert. Nachdem sie die klassischen Algorithmen in vielen Bereichen wie dem autonomen Fahren und der Robotik schnell überholt hatten, festigten DNNs zunehmend ihren Status als Stand der Technik für ein breites Spektrum von Klassifizierungs- und Antizipationsaufgaben. Durch ihrer Popularität entstehen neuartige Anwendungsfälle und eine Vielzahl an Einsatzszenarien, welche von Anwendungen in stark eingeschränkten eingebetteten Systemen bis hin zu sicherheitskritischen Anwendungen reichen. Dies stellte eine Reihe von Herausforderungen für das Hardware- und Softwaredesign dar, bei denen in der Regel enge Latenz-, Energie- und Ressourcenbudgets vorgegeben sind. In dieser Arbeit werden Konzepte aus der ausgereiften Disziplin des Hardware-Software (HW-SW) Co-designs neu interpretiert, die Prozesse zur Erzielung von Synergien bei der Bereitstellung komplexer Algorithmen auf Hardware mit präzisen Ausführungszielen und Bereitstellungskosten bieten. Es werden im Rahmen dieser Arbeit handgefertigte, halbautomatische und vollautomatische Methoden vorgeschlagen, um das Co-design in verschiedenen Entwicklungsstadien mit unterschiedlichen Designherausforderungen einzuführen. Hardware-Modelle in Form von analytischen Schedulern, Umsetzungstabellen, "Hardware-in-the-Loop" Simulationen und differenzierbaren Regressionsmodellen werden entwickelt, um ein Hardwareverständnis in die Co-design Aufgabe für Allzweck- oder kundenspezifische Platformen sowie in räumliche oder Datenfluss-Architekturen einzubringen. Abstraktionsebenen wurden ausgenutzt, um Teile-undherrsche (engl. divide-and-conquer) Verfahren zur Bewältigung von Designherausforderungen während des gesamten HW-SW-Entwicklungszyklus zu ermöglichen. Die Beiträge beleuchten die Vorteile der Zusammenführung des Algorithmen- und Hardwaredesigns, um die in beiden Welten gesetzten Ziele zu erreichen und gleichzeitig den unabhängigen Entwicklungsaufwand zu reduzieren und inkohärente Designkompromisse zu vermeiden. Im Rahmen dieser Arbeit werden Hardwarekomponenten zur Berechnung von verschiedenen Arten von neuronalen Netzen entwickelt. Genetische Algorithmen und Gradientenabstiegsalgorithmen, Autocodierer und Agenten für bestärkendes Lernen (engl. reinforcement learning) werden zur Komprimierung neuronaler Netze eingesetzt. Es werden schnelle analytische Hardwaremodelle für die Bewertung und den automatischen Entwurf von Hardware entwickelt. Zudem werden neuronale Netze sicherer gemacht, indem die Bedrohungen durch gegnerische Angriffe und Hardwarefehler auf ihre Funktion analysiert und sie für eine gemeinsame Effizienz, Robustheit und Erhaltung der Genauigkeit trainiert werden. Die daraus resultierenden, gemeinsam entwickelten Algorith-

### Zusammenfassung

men bewältigten Herausforderungen im Bereich des autonomen Fahrens mit hoher Effizienz, ermöglichten Leistungsvorhersagen auf Multiprozessor-Chips, bietet eine Maskenerkennung und -korrektur während der COVID-19-Pandemie und ermöglichten halbautonome Prothesen für Amputierte. Die Beiträge dieser Arbeit zum HW-SW-Co-design von DNNs bringen Anwendungen mit gesellschaftlicher Bedeutung für eingebettete Systeme und Edge-Devices.

# **Contents**

| A۱ | bstrac          | t             |                                                  | vii   |  |  |  |  |

|----|-----------------|---------------|--------------------------------------------------|-------|--|--|--|--|

| Ζι | ısamn           | nenfass       | ung                                              | ix    |  |  |  |  |

| Li | List of Figures |               |                                                  |       |  |  |  |  |

| Li | st of T         | <b>Tables</b> |                                                  | xxi   |  |  |  |  |

| Li | st of A         | Abbrevi       | ations                                           | xxiii |  |  |  |  |

| Li | st of S         | Symbols       | 5                                                | xxvii |  |  |  |  |

| 1  | Intr            | oductio       | n                                                | 1     |  |  |  |  |

|    | 1.1             | Motiva        | ation                                            | . 2   |  |  |  |  |

|    | 1.2             | Object        | ives                                             | . 3   |  |  |  |  |

|    | 1.3             | Contri        | butions                                          | . 3   |  |  |  |  |

|    | 1.4             | Acade         | mic Work and Scope                               | . 4   |  |  |  |  |

|    | 1.5             | Copyr         | ight Notice                                      | . 6   |  |  |  |  |

| 2  | Bacl            | kgroun        | d                                                | 7     |  |  |  |  |

|    | 2.1             | Funda         | mentals of Artificial Neural Networks            | . 7   |  |  |  |  |

|    |                 | 2.1.1         | Dense Layers                                     | . 9   |  |  |  |  |

|    |                 | 2.1.2         | Activation Functions                             | . 9   |  |  |  |  |

|    |                 | 2.1.3         | Convolutional Neural Networks                    | . 9   |  |  |  |  |

|    |                 |               | 2.1.3.1 Convolutional Layers                     | . 10  |  |  |  |  |

|    |                 |               | 2.1.3.2 Pooling Layers                           | . 11  |  |  |  |  |

|    |                 |               | 2.1.3.3 Batch Normalization                      | . 12  |  |  |  |  |

|    |                 |               | 2.1.3.4 Dilated Convolution Layers               | . 12  |  |  |  |  |

|    |                 | 2.1.4         | Learning and Classifying                         | . 13  |  |  |  |  |

|    | 2.2             | Comp          | ression and Optimization of Deep Neural Networks | . 13  |  |  |  |  |

|    |                 | 2.2.1         | Data Quantization                                | . 14  |  |  |  |  |

|    |                 | 2.2.2         | Parameter Pruning                                | . 16  |  |  |  |  |

|    |                 | 2.2.3         | Neural Architecture Search                       | . 18  |  |  |  |  |

|    |                 | 2.2.4         | Adversarial Training                             | . 19  |  |  |  |  |

|    | 2.3             | Hardw         | vare Acceleration of Deep Neural Networks        |       |  |  |  |  |

|    |                 | 2.3.1         | Deep Neural Networks on General-Purpose Hardware | . 20  |  |  |  |  |

### Contents

|   |     | 2.3.2   | Deep Net   | ural Network Accelerators                                      | 21 |

|---|-----|---------|------------|----------------------------------------------------------------|----|

|   |     |         | 2.3.2.1    | Spatial Accelerators                                           | 22 |

|   |     |         | 2.3.2.2    | Schedules and Dataflow Mapping                                 | 24 |

| 3 | HW  | -SW Co  | -Design of | f Deep Neural Networks                                         | 27 |

|   | 3.1 | Contra  | dicting Ch | allenges of DNN and HW Design                                  | 27 |

|   | 3.2 | Compr   | omises and | d Extending the Hand of Truce                                  | 28 |

|   | 3.3 | Proble  | m Stateme  | nt and Paths to Effective Co-Design                            | 31 |

|   |     | 3.3.1   | Co-Desig   | gn Methodologies                                               | 31 |

|   |     | 3.3.2   | Executab   | le Models                                                      | 33 |

|   |     | 3.3.3   | Abstracti  | on Levels                                                      | 34 |

| 4 | Han | dcrafte | d Co-Desi  | gn                                                             | 37 |

|   | 4.1 | Orthru  | sPE: Runt  | time Reconfigurable Processing Elements for Binary Neural      |    |

|   |     | Netwo   | rks        |                                                                | 37 |

|   |     | 4.1.1   | BNN Tra    | ining Challenges and Motivation for Reconfigurable PEs         | 38 |

|   |     | 4.1.2   | Related V  | Work                                                           | 39 |

|   |     | 4.1.3   | Accurate   | Binary Convolutional Neural Networks                           | 39 |

|   |     | 4.1.4   | OrthrusP   | Е                                                              | 41 |

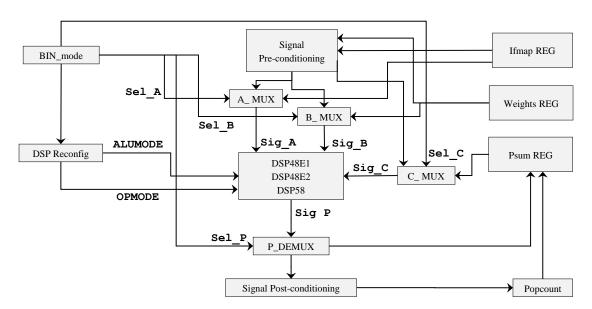

|   |     |         | 4.1.4.1    | SIMD Binary Hadamard Product in Binary Mode                    | 42 |

|   |     |         | 4.1.4.2    | Arithmetic Operations in Fixed-Precision Mode                  | 43 |

|   |     |         | 4.1.4.3    | Mode Switching and Partial Sum Accumulation                    | 44 |

|   |     | 4.1.5   | Evaluation | on                                                             | 46 |

|   |     |         | 4.1.5.1    | Experimental Setup                                             | 46 |

|   |     |         | 4.1.5.2    | Resource Utilization Analysis                                  | 47 |

|   |     |         | 4.1.5.3    | Dynamic Power Analysis                                         | 48 |

|   |     | 4.1.6   | Discussion | on                                                             | 49 |

|   | 4.2 | Mind th | he Scaling | Factors: Resilience Analysis of Quantized Adversarially Robust |    |

|   |     | CNNs    |            |                                                                | 50 |

|   |     | 4.2.1   | Hardward   | e Fault Resilience and Adversarial Robustness                  | 50 |

|   |     | 4.2.2   | Related V  | Work                                                           | 51 |

|   |     |         | 4.2.2.1    | Hardware Fault Resilience Analysis                             | 51 |

|   |     |         | 4.2.2.2    | Fault Resilient Training and Adversarial Robustness            | 52 |

|   |     | 4.2.3   | Methodo    | logy                                                           | 52 |

|   |     |         | 4.2.3.1    | Problem Formulation: Quantization and Bit-Flips                | 52 |

|   |     |         | 4.2.3.2    | Error Model and Benchmark Phases                               | 55 |

|   |     | 4.2.4   | Evaluation | on                                                             | 55 |

|   |     |         | 4.2.4.1    | Large Scale Resilience Analysis                                | 57 |

|   |     |         | 4.2.4.2    | In-depth Analysis of Adversarially Trained CNNs                | 59 |

|   |     |         | 4.2.4.3    | Results and Conclusions                                        | 59 |

|   |     | 4.2.5   | Discussio  | on                                                             | 61 |

| 5 | Sem  | Semi-Automated Co-Design |                                                                   |  |  |

|---|------|--------------------------|-------------------------------------------------------------------|--|--|

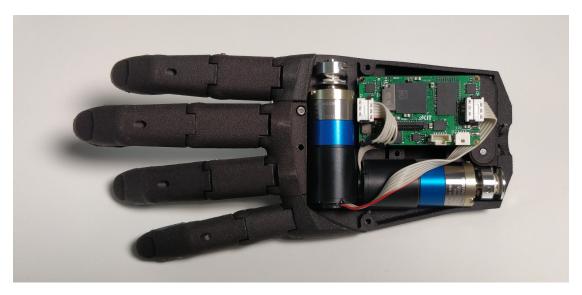

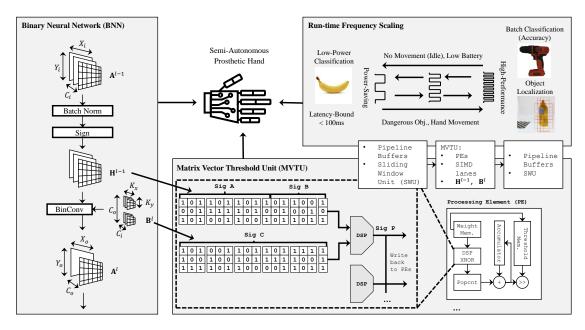

|   | 5.1  | -                        | -LoRAX: Low-power and Runtime Adaptable XNOR Classifier for Pros- |  |  |

|   |      | thetic                   | Hands                                                             |  |  |

|   |      | 5.1.1                    | HW-DNN Co-design for Intelligent Prosthetics 64                   |  |  |

|   |      | 5.1.2                    | Related Work                                                      |  |  |

|   |      |                          | 5.1.2.1 Efficient Intelligent Prosthetics 65                      |  |  |

|   |      |                          | 5.1.2.2 Binary Neural Networks for Intelligent Prosthetics 65     |  |  |

|   |      |                          | 5.1.2.3 The XILINX FINN Framework 66                              |  |  |

|   |      | 5.1.3                    | Methodology                                                       |  |  |

|   |      |                          | 5.1.3.1 Training and Inference of Simple BNNs 66                  |  |  |

|   |      |                          | 5.1.3.2 Hardware Architecture                                     |  |  |

|   |      |                          | 5.1.3.3 Runtime Dynamic Frequency Scaling                         |  |  |

|   |      |                          | 5.1.3.4 SIMD Binary Products on DSP Blocks 69                     |  |  |

|   |      | 5.1.4                    | Evaluation                                                        |  |  |

|   |      |                          | 5.1.4.1 Experimental Setup                                        |  |  |

|   |      |                          | 5.1.4.2 Design Space Exploration                                  |  |  |

|   |      |                          | 5.1.4.3 Runtime Dynamic Frequency Scaling                         |  |  |

|   |      | 5.1.5                    | Discussion                                                        |  |  |

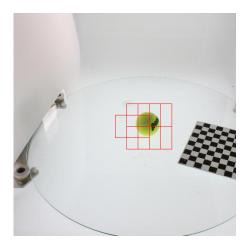

|   | 5.2  |                          | CoP: BNN COVID-19 Face-Mask Wear and Positioning Predictor 74     |  |  |

|   |      | 5.2.1                    | Efficient Deployment of CNNs for Mask Detection                   |  |  |

|   |      | 5.2.2                    | COVID-19 Face-Mask Wear and Positioning                           |  |  |

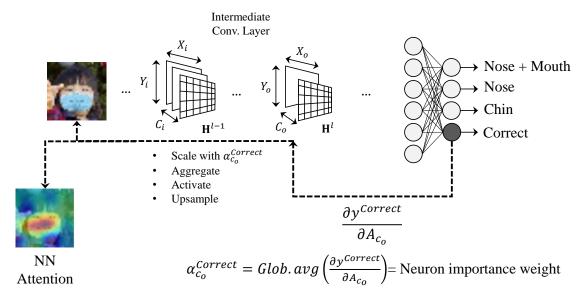

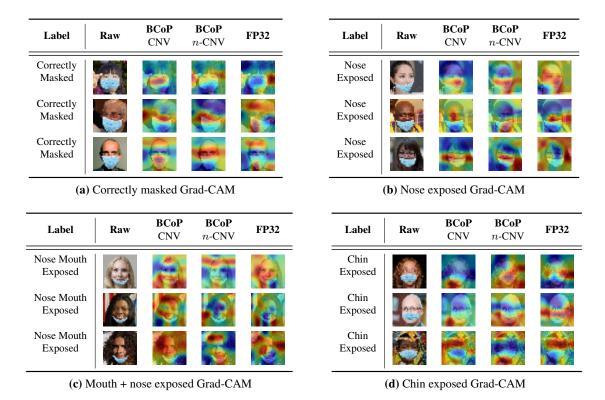

|   |      | 5.2.3                    | BNN Interpretability with Grad-CAM                                |  |  |

|   |      | 5.2.4                    | Evaluation                                                        |  |  |

|   |      | 0.2                      | 5.2.4.1 Experimental Setup                                        |  |  |

|   |      |                          | 5.2.4.2 Design Space Exploration                                  |  |  |

|   |      |                          | 5.2.4.3 Grad-CAM and Confusion Matrix Analysis                    |  |  |

|   |      |                          | 5.2.4.4 Comparison with Other Works                               |  |  |

|   |      | 5.2.5                    | Discussion                                                        |  |  |

|   |      | 3.2.3                    | Discussion                                                        |  |  |

| 6 | Full | v-Autor                  | mated Co-Design 85                                                |  |  |

|   | 6.1  | -                        | lowQ: A Multi-Abstraction Level HW-CNN Co-Design Quantization     |  |  |

|   |      |                          | dology                                                            |  |  |

|   |      | 6.1.1                    | The Tripartite Search Space                                       |  |  |

|   |      | 6.1.2                    | Related Work                                                      |  |  |

|   |      |                          | 6.1.2.1 Quantization Methods                                      |  |  |

|   |      |                          | 6.1.2.2 Quantization & Search Schemes                             |  |  |

|   |      |                          | 6.1.2.3 Hardware Modeling                                         |  |  |

|   |      |                          | 6.1.2.4 Hardware-Software Co-Design                               |  |  |

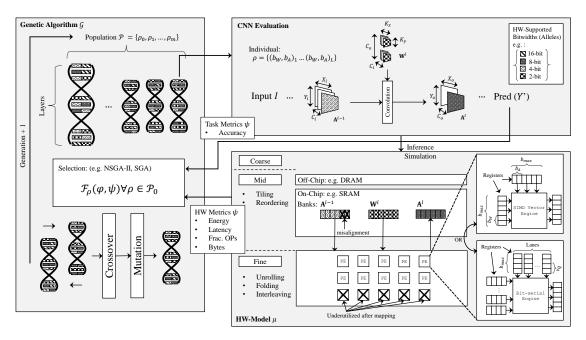

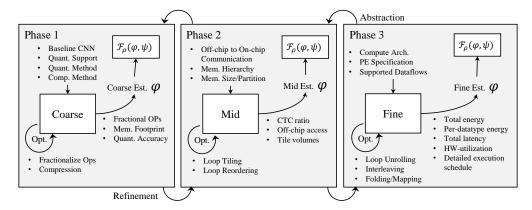

|   |      | 6.1.3                    | HW-FlowQ                                                          |  |  |

|   |      | 0.1.5                    | 6.1.3.1 HW-Model Abstraction Levels                               |  |  |

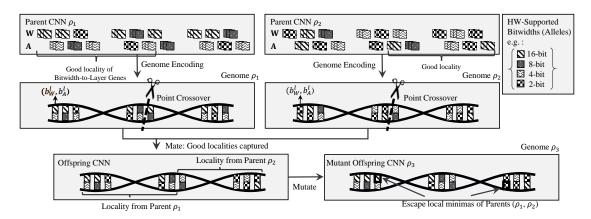

|   |      |                          | 6.1.3.2 Genetic Algorithm                                         |  |  |

|   |      |                          | 6.1.3.3 Fitness Evaluation                                        |  |  |

|   |      |                          | 6.1.3.4 Genetic Operators                                         |  |  |

|   |      |                          | *                                                                 |  |  |

|   |      |                          | 6.1.3.5 Modeling Mixed-Precision Inference                        |  |  |

### Contents

|    |        | 6.1.4   |            | recision Model Validation                                 | 96  |

|----|--------|---------|------------|-----------------------------------------------------------|-----|

|    |        | 6.1.5   |            | bstraction Level Interactions                             | 96  |

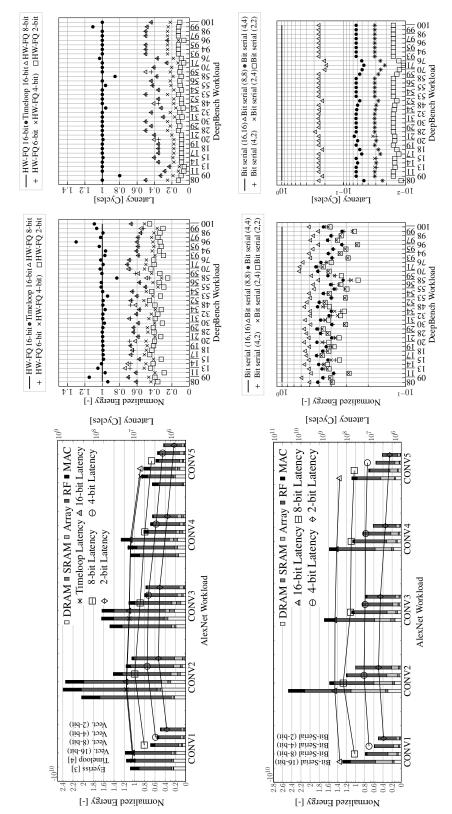

|    |        | 6.1.6   | Evaluation |                                                           | 99  |

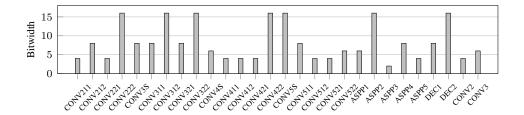

|    |        |         | 6.1.6.1    | A HW-CNN Co-Design Example                                | 101 |

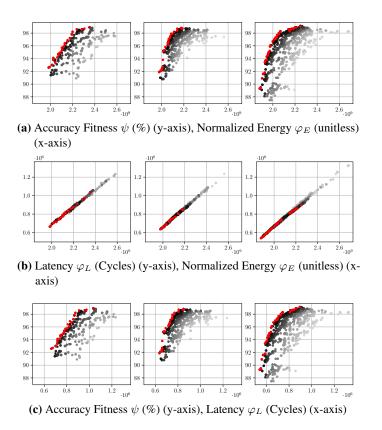

|    |        |         | 6.1.6.2    | Multi-Objective Genetic Optimization using NSGA-II        | 102 |

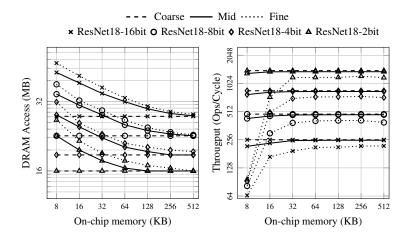

|    |        |         | 6.1.6.3    | HW Modeling and Exploration                               | 104 |

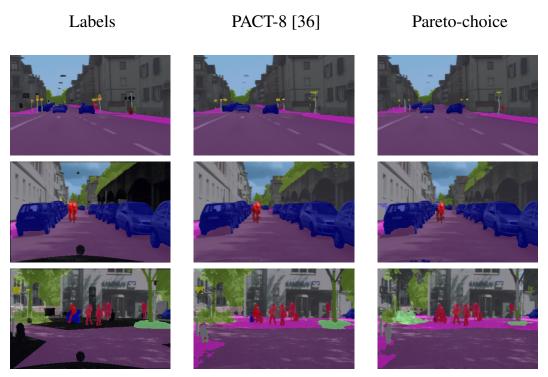

|    |        |         | 6.1.6.4    | Mixed-Precision Quantization for Semantic Segmentation    | 107 |

|    |        |         | 6.1.6.5    | Comparison with State-of-the-Art                          | 108 |

|    |        | 6.1.7   |            | on                                                        | 110 |

|    | 6.2    |         |            | alytical HW-CNN Co-Design using Nested Genetic Algorithms | 112 |

|    |        | 6.2.1   |            | tion                                                      | 112 |

|    |        | 6.2.2   |            | Work                                                      | 113 |

|    |        |         | 6.2.2.1    | CNN-Aware Hardware Design                                 | 113 |

|    |        |         | 6.2.2.2    | Joint HW-CNN Co-Design                                    | 113 |

|    |        | 6.2.3   |            | ology                                                     | 113 |

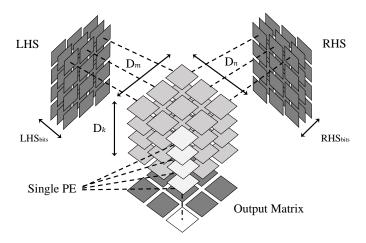

|    |        |         | 6.2.3.1    | Bit-Serial Accelerator Modeling for BISMO                 | 114 |

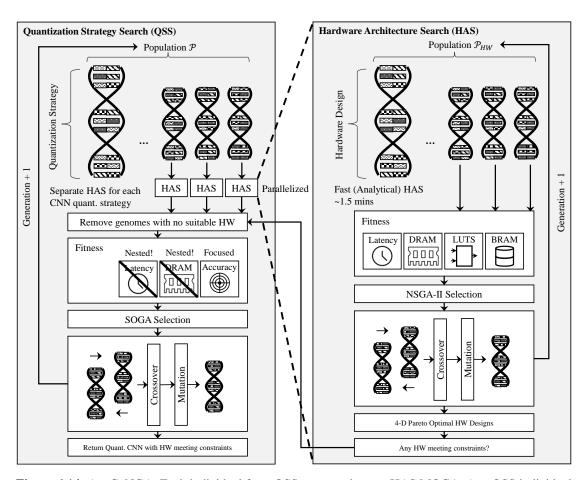

|    |        |         | 6.2.3.2    | Genetic Quantization Strategy Search (QSS)                | 116 |

|    |        |         | 6.2.3.3    | Genetic Hardware Architecture Search (HAS)                | 117 |

|    |        |         | 6.2.3.4    | Model Validation and Real Hardware Measurements           | 117 |

|    |        |         | 6.2.3.5    | AnaCoNGA: Nested HW-CNN Co-Design                         | 117 |

|    |        | 6.2.4   | Evaluation |                                                           | 120 |

|    |        |         | 6.2.4.1    | Experimental Setup                                        | 120 |

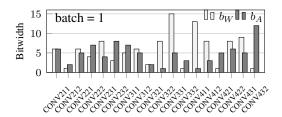

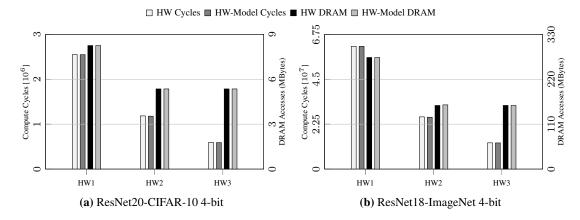

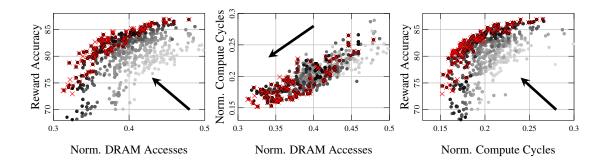

|    |        |         | 6.2.4.2    | Quantization Strategy Search (QSS) Loop Evaluation        | 121 |

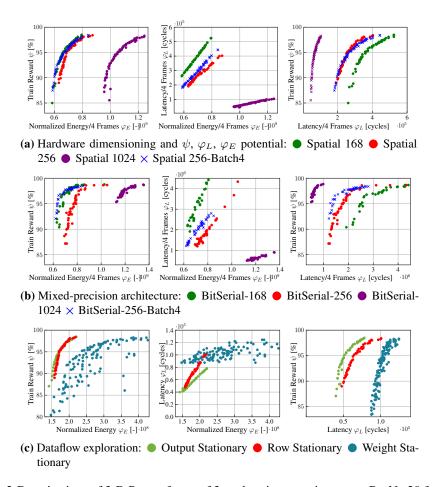

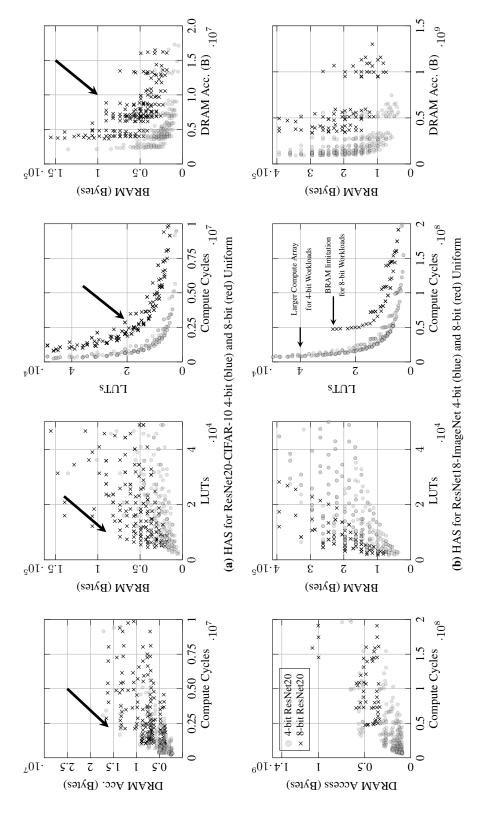

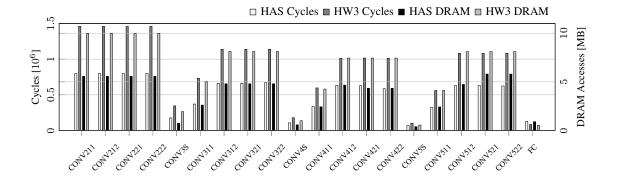

|    |        |         | 6.2.4.3    | Hardware Architecture Search (HAS) Loop Evaluation        | 121 |

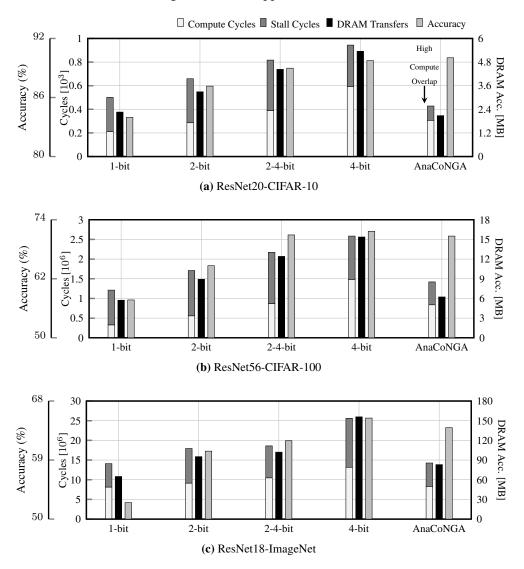

|    |        |         | 6.2.4.4    | Analysis of AnaCoNGA Co-Designed Solutions                | 122 |

|    |        | 6.2.5   | Discussi   | on                                                        | 126 |

| 7  | Con    | clusion | & Outloo   | k                                                         | 127 |

| Bi | bliogr | aphy    |            |                                                           | 131 |

| A  | App    | endix   |            |                                                           | 147 |

# **List of Figures**

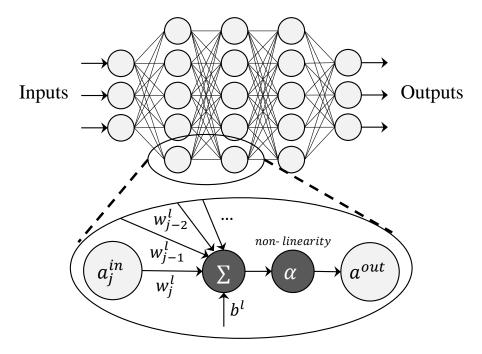

| 2.1 | Visualization of a single neuron in the context of a DNN                                                                                                             | 8   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

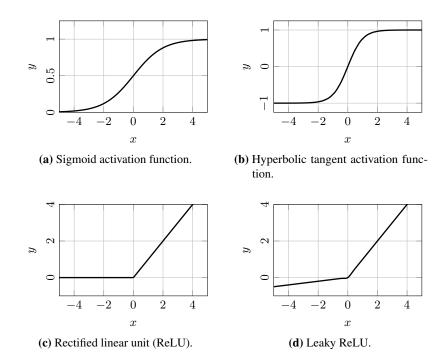

| 2.2 | Activation functions used to introduce non-linearities in DNNs. The simple rectified linear unit (ReLU) function is the most commonly used in modern                 |     |

|     | DNNs due to its simplicity in terms of computation and effective training results.                                                                                   | 10  |

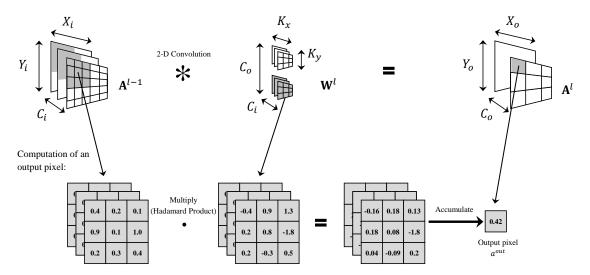

| 2.3 | Visualization of the convolution operation in convolutional neural networks                                                                                          | 10  |

| 2.3 | (CNNs). The computation of a single output pixel is highlighted                                                                                                      | 11  |

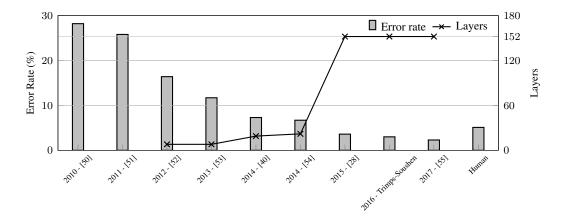

| 2.4 | Reduction in error rate during the ImageNet large scale visual recognition chal-                                                                                     | 11  |

|     | lenge (ILSVRC). Models needed more layers and parameters to push the bound-                                                                                          |     |

|     | aries each year. In 2010 and 2011, classical computer-vision algorithms were                                                                                         |     |

|     | used                                                                                                                                                                 | 14  |

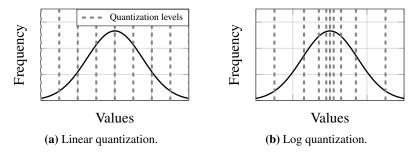

| 2.5 | Linear quantization represents the numerical distribution with uniformly spaced                                                                                      |     |

|     | quantization levels. Log-based quantization represents the more frequently occur-                                                                                    |     |

|     | ring values more finely, while less frequent values are more sparsely represented,                                                                                   | 1.0 |

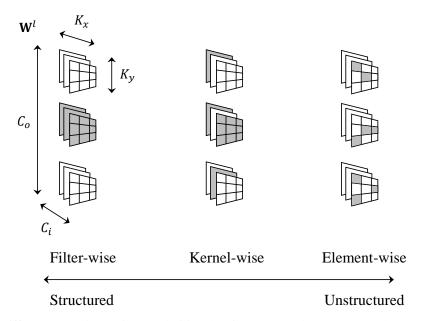

| 2.6 | with higher rounding error.                                                                                                                                          | 16  |

| 2.6 | Different example pruning regularities showing structured to unstructured parameter removal. Structured pruning can being benefits to be divisor according           |     |

|     | rameter removal. Structured pruning can bring benefits to hardware acceleration without any specialized zero-detectors or complex memory management                  | 17  |

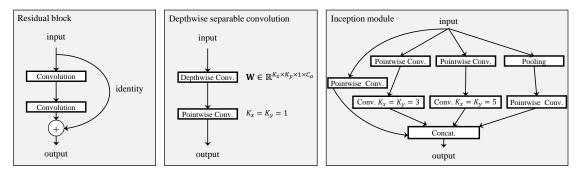

| 2.7 | Example handcrafted DNN architectural blocks developed to improve training                                                                                           | 1 / |

| 2.1 | and reduce total computations and parameters                                                                                                                         | 19  |

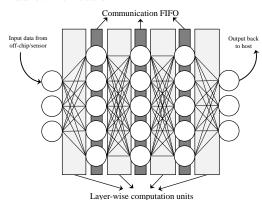

| 2.8 | Abstract visualization of spatial and dataflow architectures. Spatial accelerators use an array of processing elements (PEs) to perform the parallel operations of a |     |

|     | DNN. Dataflow architectures reflect the neural network architecture in hardware                                                                                      |     |

|     | and process the layers as a classical dataflow graph                                                                                                                 | 21  |

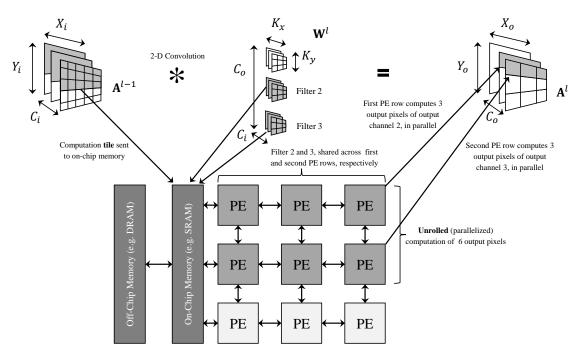

| 2.9 | Tiling and unrolling example on a spatial accelerator                                                                                                                | 24  |

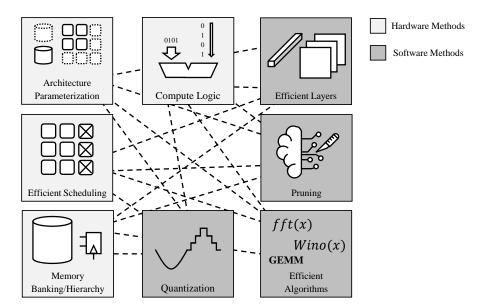

| 3.1 | Inter-dependencies of hardware and software DNN optimization techniques                                                                                              | 29  |

| 3.2 | Works published under the scope of this thesis categorized with respect to con-                                                                                      |     |

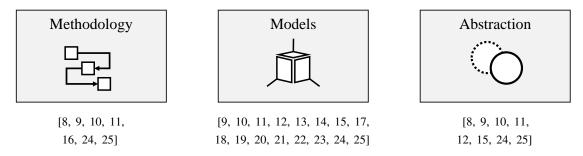

|     | cepts used from the very-large-scale integration (VLSI) design domain                                                                                                | 32  |

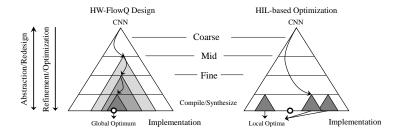

| 3.3 | The Gajski-Kuhn diagram (left) and the possible transitions to traverse the views                                                                                    |     |

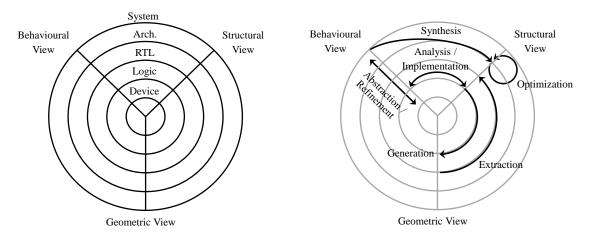

|     | and abstraction levels (right)                                                                                                                                       | 35  |

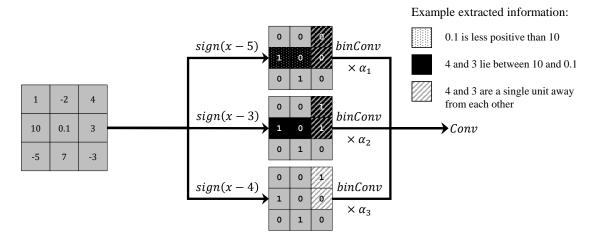

| 4.1 | Binary bases can differentiate the values of the full-precision kernel more accu-                                                                                    |     |

|     | rately by preserving more information through linear transformations                                                                                                 | 40  |

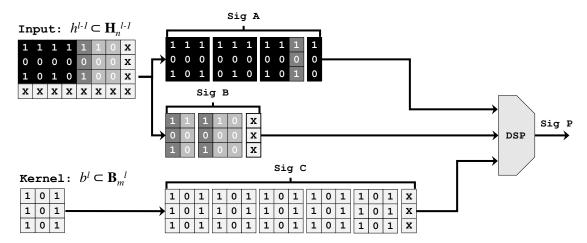

| 4.2 | Preconditioning signals A, B and C to compute five 3×3 Hadamard products.                                                                                            |     |

|     | Pixels represented with an X are not relevant for this cycle of operation                                                                                            | 42  |

### List of Figures

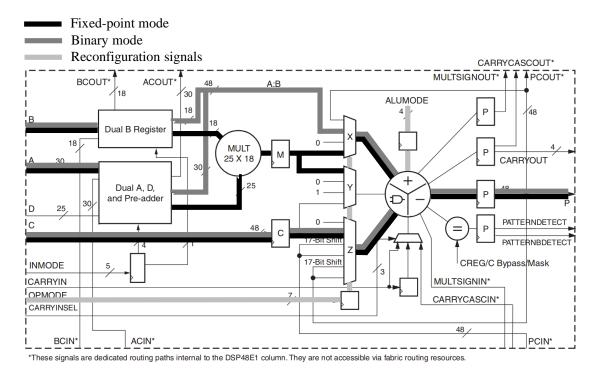

| The DSP48E1 Slice [1]. Appended bold paths illustrate the relevant signals for            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                           | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

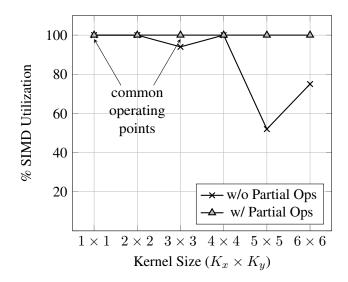

|                                                                                           | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

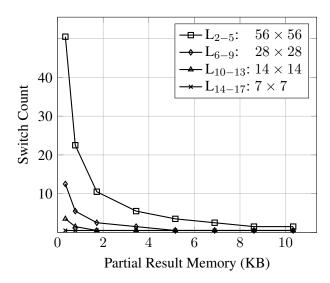

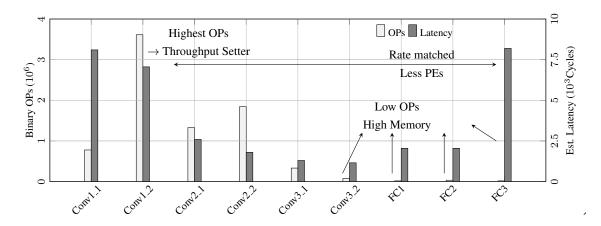

| different convolutional layers of binary ResNet18, with $M=3,N=3.$ Each                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                           | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

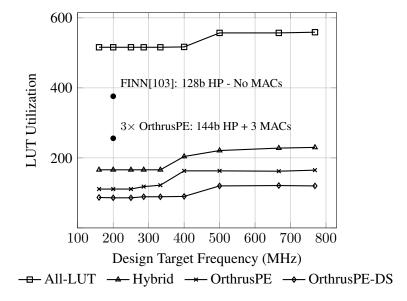

|                                                                                           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

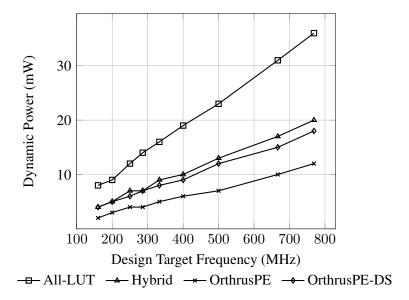

| Dynamic power estimation at different design target frequencies. Each plot point          | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| • • •                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

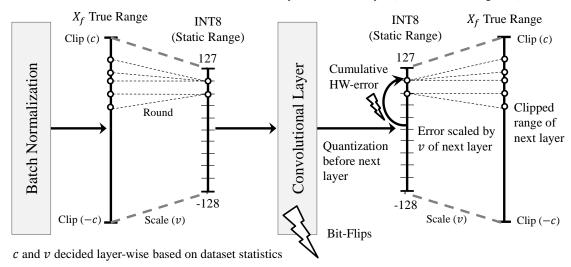

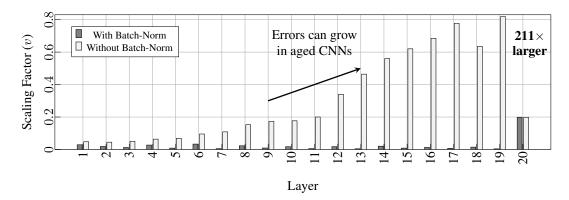

| •                                                                                         | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

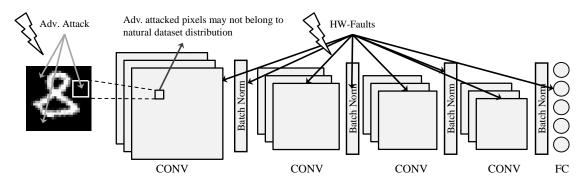

| •                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

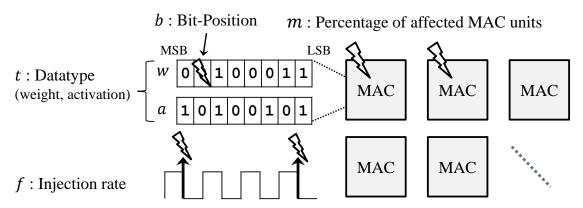

| · · · · · · · · · · · · · · · · · · ·                                                     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| •                                                                                         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

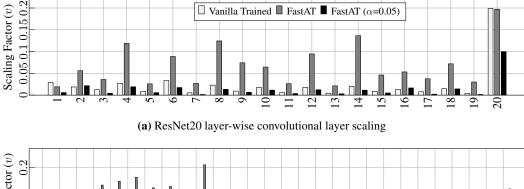

| Bit-flip experiments following algorithm 4.1 on vanilla, pruned and adversarially         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

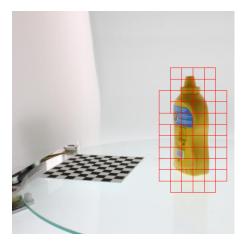

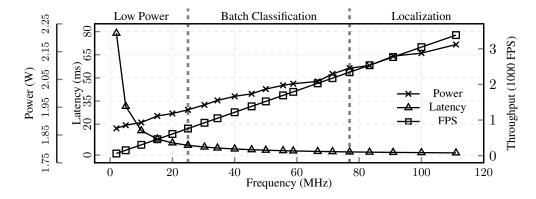

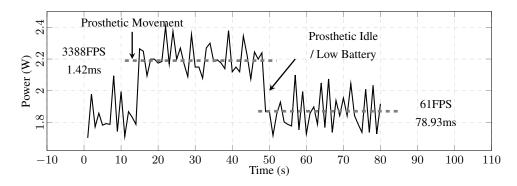

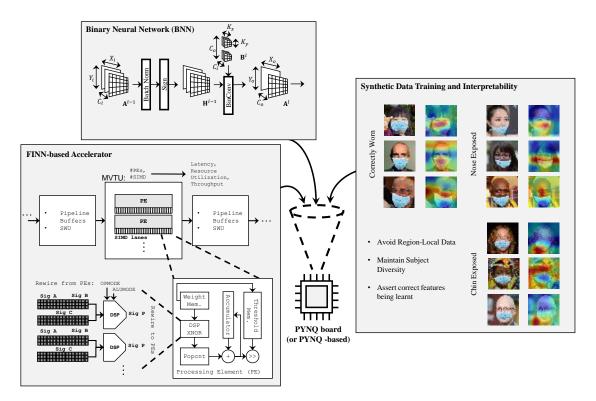

| •                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |