Technische Universität München Forschungsinstitut **caesar** in Bonn

# $\mathbf{G}\mathbf{P}\mathbf{U}^{++}$

# An Embedded GPU Development System for General-Purpose Computations

Thomas C. Jansen

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. Hans-Joachim Bungartz Prüfer der Dissertation: 1. Univ.-Prof. Dr. Dr.h.c.mult Karl-Heinz Hoffmann

2. Univ.-Prof. Dr. Rüdiger Westermann

Die Dissertation wurde am 26.04.2007 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 12.09.2007 angenommen.

© Copyright by Thomas Christopher Jansen 2007 All Rights Reserved

# Zusammenfassung

Der Einsatz der Grafikkarte (GPU) zur Beschleunigung allgemeiner Berechnungen hat sich im Laufe der letzten Jahre zu einer wichtigen Technik im wissenschaftlichen Bereich entwickelt. Aufgrund der dabei verwendeten grafik-orientierten Konzepte und Werkzeuge, führt diese Methode jedoch zu einer spürbaren Steigerung der Entwicklungskomplexität im Vergleich zur klassischen Umsetzung für den Hauptprozessor. Die damit verbundene Kostensteigerung verhindert bis jetzt den breiten industriellen Einsatz dieser Technik.

Diese Arbeit beschreibt einen neuartigen Ansatz zur generellen Programmierung der Grafikkarte – das  $GPU^{++}$  Entwicklungssystem. Dieses System ist nahtlos in die Programmiersprache  $C^{++}$  integriert und ermöglicht so die gleichzeitige Verwendung der CPU und GPU mittels einer bekannten Befehlssyntax. Zudem werden computer-grafische Konzepte wie die verschiedenen Berechnungseinheiten der GPU und deren Vektorarchitektur, effizient abstrahiert. So ermöglicht  $GPU^{++}$  eine einfache und schnelle Integration GPU-beschleunigter allgemeiner Berechnungen in einen existierenden Entwicklungsprozess – und hebt damit die Unterschiede zwischen Grafik- und Hauptprozessor größtenteils auf.

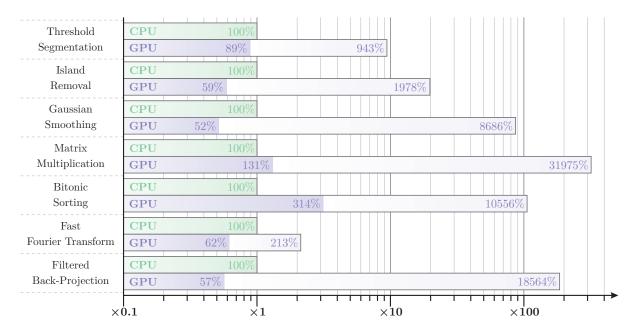

Die Evaluierung des in dieser Arbeit vorgestellten Entwicklungssystems geschieht durch die CPU- und GPU-basierte Umsetzung bekannter Algorithmen, wie der Multiplikation großer Matrizen, Sortieren, Schnelle Fourier-Transformation und die gefilterte Rückprojektion zur Berechnung einer tomografischen Rekonstruktion. Obwohl die auf GPU<sup>++</sup> aufbauenden Implementationen die Geschwindigkeit der CPU-basierten Umsetzungen um teilweise mehr als drei Größenordnungen übertreffen, hat dies keine spürbare Steigerung der Softwarekomplexität und Entwicklungszeit zur Folge.

Diese Ergebnisse demonstrieren überzeugend, dass sich die Entwicklungskomplexität und -zeit für die Umsetzung allgemeiner Berechnungen auf der Grafikkarte durch den Einsatz des GPU<sup>++</sup> Entwicklungssystems auf ein Niveau senken lassen, welches mit der klassischen CPU-basierten Implementation vergleichbar ist – ohne dabei auf die enormen Geschwindigkeitsvorteile des Grafikprozessors verzichten zu müssen.

#### ZUSAMMENFASSUNG

# Abstract

Using the graphics processing unit (GPU) to accelerate general-purpose computations has become an important technique in scientific research. However, the development complexity is significantly higher than for CPU-based solutions, due to the mainly graphics-oriented concepts and development tools for GPU-programming. As a consequence, general-purpose computations on the GPU are mainly discussed in the academic domain and have not yet fully reached industrial software development.

This thesis presents a novel contribution to general-purpose GPU programming – the  $GPU^{++}$  development system. It features a seamless integration into the  $C^{++}$  programming language to address graphics hardware via a familiar syntax, an abstraction layer to efficiently hide the different computation frequencies, and a novel approach to relax the vector processor paradigm of the GPU. The  $GPU^{++}$  development system enables software engineers to embed GPU-based development into their existing software engineering workflow, thus, largely dissolving the differences between main and graphics processor.

The developed system has been evaluated by the implementation of well-known generalpurpose algorithms on both processor platforms – including general matrix multiplication, sorting of values, the fast Fourier transform, and tomographic reconstruction via filtered back-projection. The  $GPU^{++}$  implementations outperform the CPU solutions by up to three orders of magnitude without a noticeable increase in source code complexity.

These results clearly demonstrate that the novel GPU<sup>++</sup> development system significantly reduces the source code complexity and development time of general-purpose GPU applications to a level which is comparable to main processor implementations, while obtaining the tremendous performance advantages of today's graphics hardware architectures.

ABSTRACT

# Acknowledgments

Over the last seven years I have had the privilege to work with a variety of people who have made my time at **caesar** an enjoyable and intellectually stimulating experience. I would like to thank all the people who have helped me and contributed to this dissertation.

First and foremost, I would like to thank my advisor Erwin Keeve who gave me the opportunity to work with him during my stay at the **caesar** research center. Having Erwin as an adviser has been an amazing experience. He was willing to take a chance on my research from the beginning, and has always pushed me to fill in that one last detail to elevate the level of my thinking and my work. I would also like to thank the other members of my reading committee, Prof. Karl-Heinz Hoffmann and Prof. Rüdiger Westermann, for their discussions on this dissertation. Their insights greatly improved this thesis.

One of the great things about being at **caesar**'s *Surgical Systems Lab* working on a variety of different topics is that I have gotten to work closely with a lot of people. I am extremely grateful for the collaborations with Bartosz von Rymon-Lipinski and Nils Hanßen – their insights and fruitful discussions about computer graphics, software engineering and image processing greatly improved this thesis. I also would like to thank anyone I have worked with: Lutz Ritter, Fabio Fracassi, Khai Binh Duong, Timo Dreiseidler, Marco Wedekind, Kristian Raic, Andreas Zollorsch, and Alexander Winter. They have been a great sounding board for many of my ideas and they have spent countless hours reviewing my papers and talks, and my work is much better for it.

I am also deeply indebted to my family for believing in me and for giving me the inspiration to apply and complete a doctoral degree. Their love, guidance, and encouragement have been a constant source of strength for me.

And last but not least, my heartfelt thanks go out to my beloved better-half, Kathrin, who has been so patient and supportive since I started graduate school. She has been my inspiration and provided encouragement when research progress was slow, and when research felt like spiraling out of control, she brought serenity. It should be no surprise that this dissertation would be impossible without her. I dedicate this thesis to her.

#### ACKNOWLEDGMENTS

# Contents

| Zusammenfassung |       |        |                                              |     |  |  |

|-----------------|-------|--------|----------------------------------------------|-----|--|--|

| A               | bstra | ct     |                                              | v   |  |  |

| A               | cknov | wledgr | nents                                        | vii |  |  |

| 1               | Intr  | oduct  | ion                                          | 1   |  |  |

|                 | 1.1   | Contra | ibutions                                     | 5   |  |  |

|                 | 1.2   | Outlin | ne                                           | 6   |  |  |

| 2               | Rela  | ated V | Vork                                         | 7   |  |  |

|                 | 2.1   | Shadii | ng Languages                                 | 7   |  |  |

|                 |       | 2.1.1  | History                                      | 8   |  |  |

|                 |       | 2.1.2  | Cg and HLSL                                  | 10  |  |  |

|                 |       | 2.1.3  | OpenGL Shading Language                      | 10  |  |  |

|                 | 2.2   | Langu  | ages for General-Purpose Computations        | 11  |  |  |

|                 |       | 2.2.1  | Brook for GPUs                               | 11  |  |  |

|                 |       | 2.2.2  | CUDA – "Compute Unified Device Architecture" | 11  |  |  |

|                 |       | 2.2.3  | CTM – "Close-to-the-Metal"                   | 12  |  |  |

|                 | 2.3   | Embe   | dded Languages and Libraries                 | 12  |  |  |

|                 |       | 2.3.1  | Sh and the RapidMind Development Platform    | 13  |  |  |

|                 |       | 2.3.2  | PeakStream Platform                          | 13  |  |  |

|                 |       | 2.3.3  | Accelerator                                  | 14  |  |  |

|                 | 2.4   | Comp   | arison Chart                                 | 14  |  |  |

#### CONTENTS

| 3 | Con | cepts                      |                                                 | 15        |  |  |  |  |  |  |  |

|---|-----|----------------------------|-------------------------------------------------|-----------|--|--|--|--|--|--|--|

|   | 3.1 | 3.1 Application Life-Cycle |                                                 |           |  |  |  |  |  |  |  |

|   | 3.2 | Streaming Paradigm         |                                                 |           |  |  |  |  |  |  |  |

|   | 3.3 | Vector Processor           |                                                 |           |  |  |  |  |  |  |  |

|   | 3.4 | Comp                       | utation Frequencies                             | 19        |  |  |  |  |  |  |  |

|   | 3.5 | Array                      | Access                                          | 20        |  |  |  |  |  |  |  |

|   | 3.6 | Requi                      | rements                                         | 22        |  |  |  |  |  |  |  |

| 4 | The | Expr                       | ession Graph                                    | <b>25</b> |  |  |  |  |  |  |  |

|   | 4.1 | Intern                     | al Representation                               | 26        |  |  |  |  |  |  |  |

|   |     | 4.1.1                      | Vector Decoupling                               | 27        |  |  |  |  |  |  |  |

|   |     | 4.1.2                      | Unified Kernel Definition                       | 27        |  |  |  |  |  |  |  |

|   | 4.2 | Embe                       | dded Creation                                   | 28        |  |  |  |  |  |  |  |

|   |     | 4.2.1                      | Custom Data Types                               | 29        |  |  |  |  |  |  |  |

|   |     | 4.2.2                      | Data Managing Classes                           | 32        |  |  |  |  |  |  |  |

|   |     | 4.2.3                      | Type Qualifiers                                 | 35        |  |  |  |  |  |  |  |

|   |     | 4.2.4                      | Example                                         | 36        |  |  |  |  |  |  |  |

|   | 4.3 | Fast I                     | DAG Processing                                  | 38        |  |  |  |  |  |  |  |

|   |     | 4.3.1                      | Custom RTTI Mechanism                           | 39        |  |  |  |  |  |  |  |

|   |     | 4.3.2                      | Efficient Use of Templates Using Visitor Traits | 40        |  |  |  |  |  |  |  |

|   |     | 4.3.3                      | Performance Results                             | 43        |  |  |  |  |  |  |  |

| 5 | Ker | nel Op                     | otimizations                                    | 45        |  |  |  |  |  |  |  |

|   | 5.1 | Expre                      | ssion Optimization Strategies                   | 46        |  |  |  |  |  |  |  |

|   |     | 5.1.1                      | Basic Optimizations                             | 46        |  |  |  |  |  |  |  |

|   |     | 5.1.2                      | Algebraic Simplifications                       | 46        |  |  |  |  |  |  |  |

|   |     | 5.1.3                      | Algebraic Reassociation                         | 47        |  |  |  |  |  |  |  |

|   |     | 5.1.4                      | Common Sub-Expression Elimination               | 48        |  |  |  |  |  |  |  |

|   | 5.2 | GPU-                       | Driven Optimizations                            | 49        |  |  |  |  |  |  |  |

|   |     | 5.2.1                      | Substitutions                                   | 49        |  |  |  |  |  |  |  |

|   |     | 5.2.2                      | Frequency Transitions                           | 51        |  |  |  |  |  |  |  |

#### CONTENTS

| 6                         | Back-End |                                     |                                              |    |  |  |  |  |  |  |  |

|---------------------------|----------|-------------------------------------|----------------------------------------------|----|--|--|--|--|--|--|--|

|                           | 6.1      | Creati                              | on of the Instruction Stream                 | 56 |  |  |  |  |  |  |  |

|                           |          | 6.1.1                               | Custom Instruction Set                       | 56 |  |  |  |  |  |  |  |

|                           |          | 6.1.2                               | Stream Creation                              | 58 |  |  |  |  |  |  |  |

|                           | 6.2      | Instru                              | ction Stream Optimization                    | 60 |  |  |  |  |  |  |  |

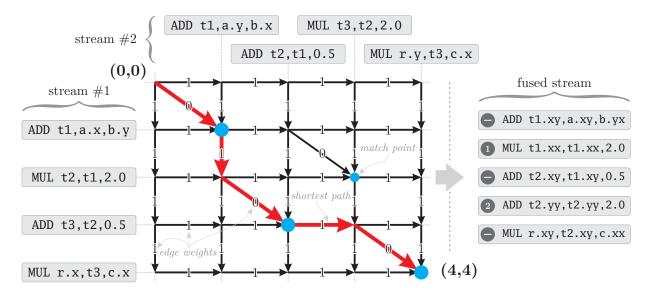

|                           |          | 6.2.1                               | Vector Fusion                                | 60 |  |  |  |  |  |  |  |

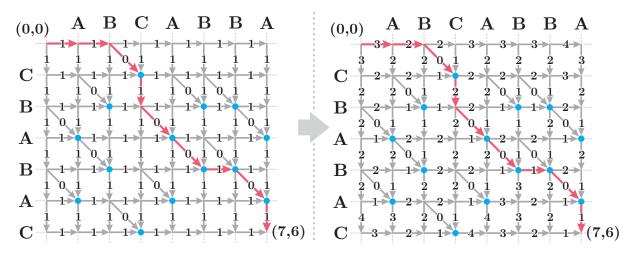

|                           |          | 6.2.2                               | Register Renaming                            | 64 |  |  |  |  |  |  |  |

| 6.3 Connecting to the GPU |          |                                     |                                              |    |  |  |  |  |  |  |  |

|                           |          | 6.3.1                               | Back-End Stubs                               | 66 |  |  |  |  |  |  |  |

|                           |          | 6.3.2                               | Low-Level API Interface                      | 67 |  |  |  |  |  |  |  |

| 7                         | Eva      | luatior                             | 1                                            | 69 |  |  |  |  |  |  |  |

|                           | 7.1      | Medica                              | al Image Processing                          | 70 |  |  |  |  |  |  |  |

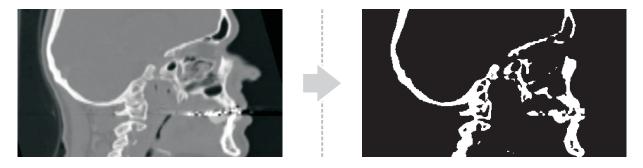

|                           |          | 7.1.1                               | Threshold Segmentation                       | 70 |  |  |  |  |  |  |  |

|                           |          | 7.1.2                               | Pixel-Island Removal                         | 71 |  |  |  |  |  |  |  |

|                           |          | 7.1.3                               | Gaussian Smoothing                           | 73 |  |  |  |  |  |  |  |

|                           |          | 7.1.4                               | Results and Discussion                       | 74 |  |  |  |  |  |  |  |

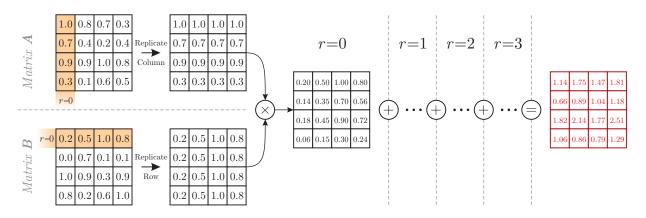

|                           | 7.2      | .2 Multiplication of Dense Matrices |                                              |    |  |  |  |  |  |  |  |

|                           |          | 7.2.1                               | Implementation Details and Results           | 77 |  |  |  |  |  |  |  |

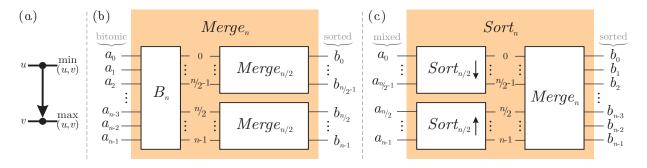

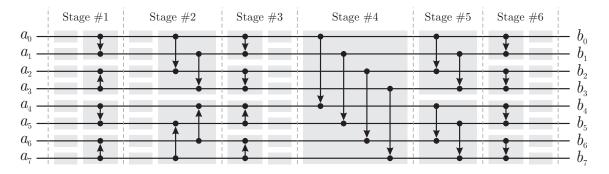

|                           | 7.3      | 7.3 Sorting                         |                                              |    |  |  |  |  |  |  |  |

|                           |          | 7.3.1                               | Bitonic Sorting                              | 78 |  |  |  |  |  |  |  |

|                           |          | 7.3.2                               | Implementation Details and Results           | 79 |  |  |  |  |  |  |  |

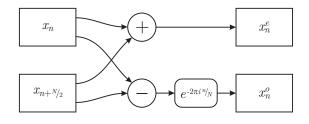

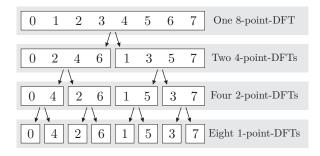

|                           | 7.4      | Fast F                              | ourier Transform                             | 80 |  |  |  |  |  |  |  |

|                           |          | 7.4.1                               | Adaptation to the GPU – The Split-Stream-FFT | 82 |  |  |  |  |  |  |  |

|                           |          | 7.4.2                               | Implementation Details and Results           | 82 |  |  |  |  |  |  |  |

|                           | 7.5      | Tomog                               | graphic Reconstruction                       | 85 |  |  |  |  |  |  |  |

|                           |          | 7.5.1                               | The Fourier Slice Theorem                    | 85 |  |  |  |  |  |  |  |

|                           |          | 7.5.2                               | Filtered Back-Projection                     | 87 |  |  |  |  |  |  |  |

|                           |          | 7.5.3                               | Implementation Details and Results           | 87 |  |  |  |  |  |  |  |

| 8                         | Dise     | cussion                             | l                                            | 91 |  |  |  |  |  |  |  |

|                           | 8.1      | Data 7                              | Transfer                                     | 92 |  |  |  |  |  |  |  |

|                           | 8.2      | Softwa                              | are Complexity                               | 93 |  |  |  |  |  |  |  |

xi

#### CONTENTS

| 9 | Con  | onclusion                        |     |  |  |  |  |

|---|------|----------------------------------|-----|--|--|--|--|

|   | 9.1  | Contributions                    | 96  |  |  |  |  |

|   | 9.2  | Future Work                      | 97  |  |  |  |  |

| A | Refe | erence of the Language Extension | 99  |  |  |  |  |

|   | A.1  | Vectors                          | 99  |  |  |  |  |

|   | A.2  | Matrices                         | 101 |  |  |  |  |

|   | A.3  | Type Qualifiers                  | 102 |  |  |  |  |

|   | A.4  | Built-In Functions and Variables | 104 |  |  |  |  |

| в | Exa  | mples                            | 113 |  |  |  |  |

|   | B.1  | Hello World                      | 113 |  |  |  |  |

|   | B.2  | Array Access                     | 114 |  |  |  |  |

|   | B.3  | Array Rotation                   | 115 |  |  |  |  |

|   | B.4  | Blending of Two Arrays           | 116 |  |  |  |  |

# List of Figures

| 1.1        | Evolution of Computer Graphics Hardware              | 1  |

|------------|------------------------------------------------------|----|

| 1.2        | Visual Paradigm                                      | 2  |

| 1.3        | Algorithmic Paradigm.                                | 3  |

| 2.1        | Evolution of Shading Languages                       | 8  |

| 3.1        | Application Life-Cycle                               | 17 |

| 3.2        | Output Region Masks the Resulting Array Elements     | 18 |

| 3.3        | Interpolation Schemes for Continuous Array Access    | 21 |

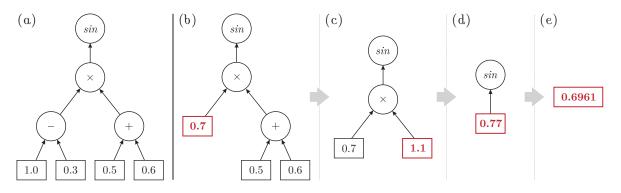

| 4.1        | Evaluation of a Simple Expression Tree               | 26 |

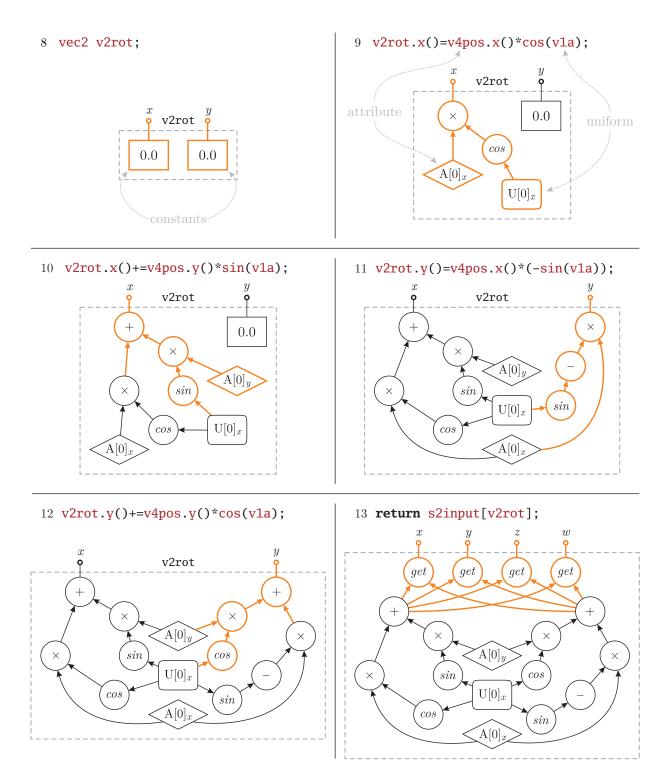

| 4.2        | Embedded Creation of the Directed Acyclic Graph      | 37 |

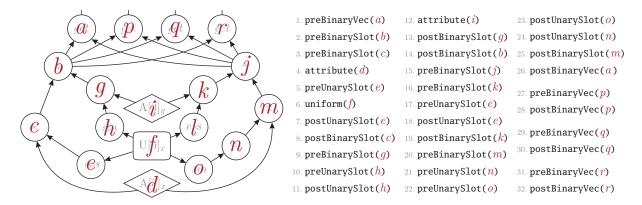

| 4.3        | Dispatch Functions for DAG Traversal                 | 39 |

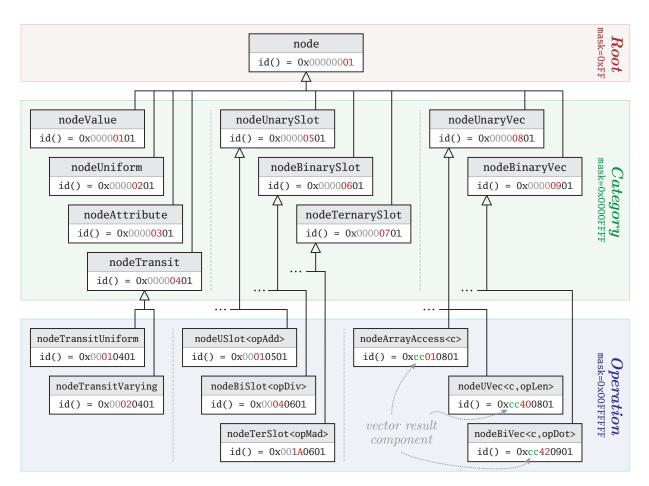

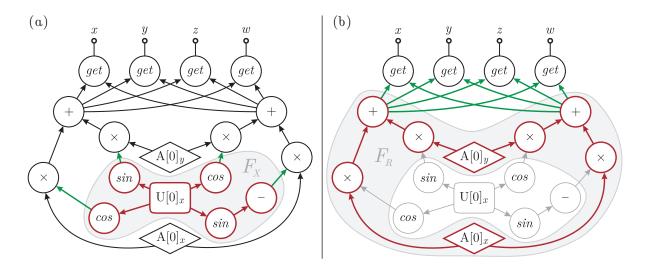

| 4.4        | UML Class Diagram for the DAG Node Hierarchy         | 40 |

| 5.1        | Substitution of a DAG Node                           | 49 |

| 5.2        | Frequency Transitions                                | 53 |

| 6.1        | Illustration of an Edit Graph                        | 62 |

| 6.2        | Heuristic Weighting Increases DIFF4 Performance      | 63 |

| 6.3        | Register Renaming                                    | 64 |

| 7.1        | Threshold Segmentation                               | 70 |

| 7.2        | Island Removal Using Erosion and Dilation            | 71 |

|            |                                                      |    |

| 7.3        | 5                                                    | 72 |

| 7.3<br>7.4 | Exploiting Linear Interpolation for Erosion/Dilation |    |

|            | Exploiting Linear Interpolation for Erosion/Dilation | 72 |

#### LIST OF FIGURES

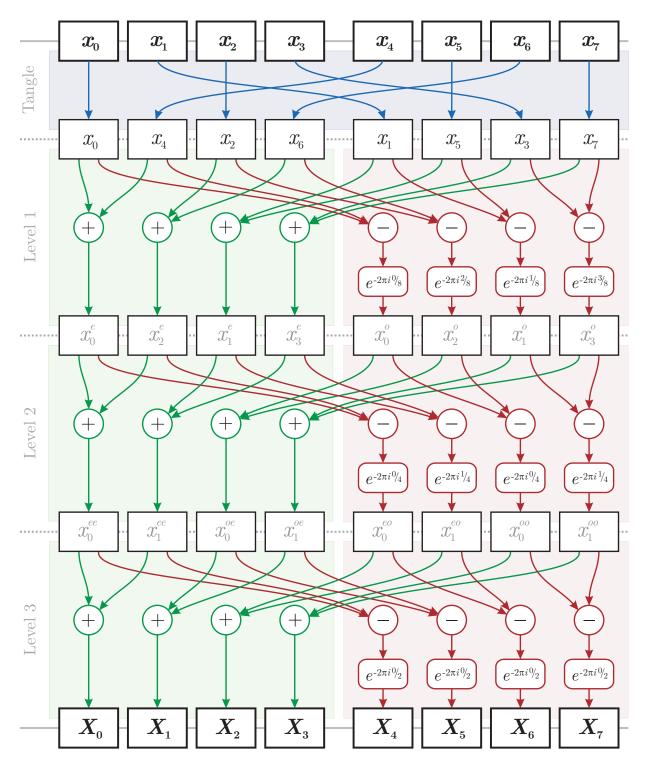

| 7.7  | FFT Butterfly Operation                            | 81  |

|------|----------------------------------------------------|-----|

| 7.8  | Tangling of FFT Indices                            | 81  |

| 7.9  | Data-Flow of the Split-Stream-FFT                  | 83  |

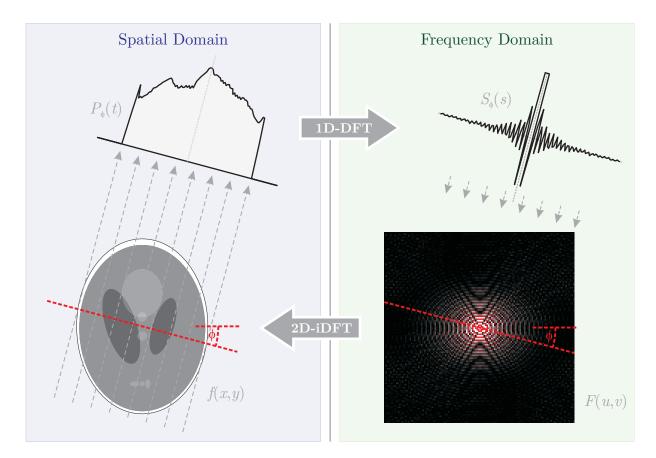

| 7.10 | Parallel Projections and the Fourier Slice Theorem | 86  |

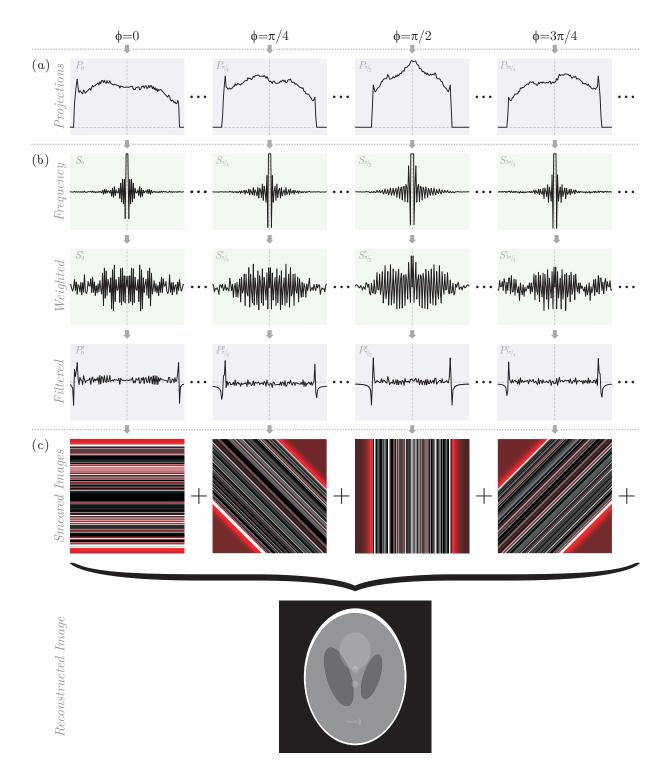

| 7.11 | Filtered Back-Projection                           | 88  |

| 8.1  | Comparison of CPU and GPU Implementations          | 91  |

| B.1  | Output of the "Hello World" Listing                | 117 |

| B.2  | Output of the "Array Access" Listing               | 117 |

| B.3  | Output of the "Rotation" Listing                   | 117 |

| B.4  | Output of the "Blending" Listing                   | 117 |

# List of Tables

| 2.1 | Comparison Chart of GPU Programming Languages               | 14  |

|-----|-------------------------------------------------------------|-----|

| 4.1 | Benchmark Timings for Expression DAG Processing             | 43  |

| 5.1 | Arithmetic Simplifications                                  | 47  |

| 5.2 | Grouping of Constant Values Via Algebraic Reassociation     | 48  |

| 5.3 | Substitutions for Unsupported Operations                    | 50  |

| 5.4 | Approximations of Trigonometric Functions Via Taylor Series | 51  |

| 6.1 | OpenGL Low-Level Instructions                               | 58  |

| 7.1 | Optimization for Gaussian Smoothing                         | 74  |

| 7.2 | Benchmark Timings for Basic Medical Algorithms              | 75  |

| 7.3 | Benchmark Timings for Dense Matrix Multiplication           | 77  |

| 7.4 | Benchmark Timings for Sorting                               | 79  |

| 7.5 | Benchmark Timings for Fast Fourier Transform                | 84  |

| 7.6 | Benchmark Timings for Filtered Back-Projection              | 89  |

| 8.1 | Benchmark Timings Including Data Transfer                   | 92  |

| A.1 | Supported Vector-Vector Operations                          | 101 |

| A.2 | Supported Matrix-Matrix and Matrix-Vector Operations        | 102 |

LIST OF TABLES

xvi

# Chapter 1 Introduction

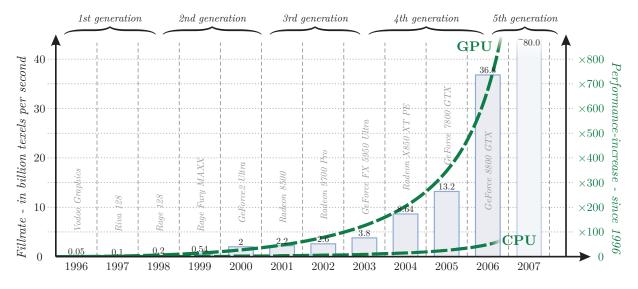

Commodity graphics hardware has evolved tremendously over the last years – it started with basic polygon rendering via 3DFX's VOODOO GRAPHICS in 1996, and continued with custom vertex manipulation four years later, the graphics processing unit (GPU) now has improved to a full-grown graphics-driven processing architecture with a speed-performance approx. 750 times higher than a decade before (1996: 50 mtex/s, 2006: 36,8 btex/s). This makes the GPU evolving much faster than the CPU, which became approx. 50 times faster in the same period (1996: 66 SPECfp2000, 2006: 3010 SPECfp2000) [69]. Figure 1.1 shows the GPU performance over the last ten years and how the gap to the CPU increases. Experts believe that this evolution will continue for at least the next five years [66, 76].

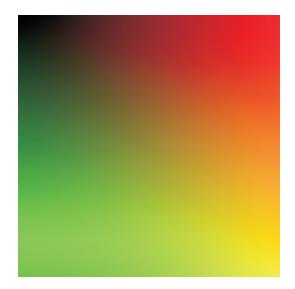

**Figure 1.1:** The performance-increase of computer graphics hardware over the last decade (using the "texels per second" metric). The green trend line shows that the GPU doubles its speed-performance every 13 months (i.e. GPUs of 2006 are approx. 750 times faster than GPUs of 1996). In contrast, the performance of the CPU doubles only every 22 months [69].

\*

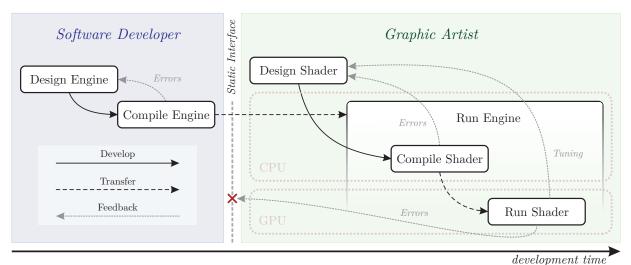

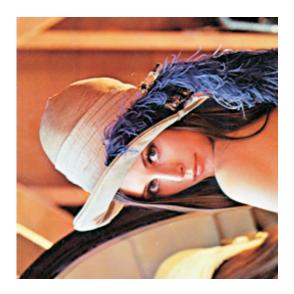

**Figure 1.2:** The "visual paradigm" knows two participants – the *software developer* and the *graphics artist* – each having its own workflow. The software developer creates the "engine" that is used by the graphics artist to create "shader" programs (that run as part of the engine).

As the name implies, the GPU was initially designed for accelerating graphical tasks. However, it was soon being exploited for performing non-graphical computations, for instance, the work of Lengyel et al. uses graphics hardware to compute robot motion, the CYPHERFLOW project by Kedem and Ishihara exploits the graphics accelerator to decipher encrypted data, and a GPU-based computation of Voronoi diagrams has been presented by Hoff et al. [72, 60, 54]. Today, implementations for various general-processing algorithms exist for the graphics hardware, e.g. sorting, linear algebra, Fourier analysis, partial differential equations, and tomographic reconstruction [63, 70, 56, 113, 19]. Nevertheless, while more and more algorithms are implemented for graphics hardware, most of the work stays in the academic field and has not yet found its way into industrial software engineering.

The reason is that GPU-based application development is *much more complex*, mainly because the developer has to be an expert in two domains – in the application's domain, and in *computer graphics*. This means that changing the graphics-oriented paradigms and corresponding GPU development tools may significantly reduce development complexity.

Most of the existing GPU-based development systems are founded on the graphicsoriented paradigm that is illustrated in figure 1.2 – the visual paradigm. This approach has been influenced by the entertainment and special-effects industry, where the software developer creates the so-called "rendering engine" and the graphics artist uses the engine to create so-called "shader programs" that compute visual phenomena. For instance, a very popular rendering engine is the RENDERMAN software – while the software itself is developed by PIXAR, the "visual effects" (i.e. shader programs) are created by individual special-effects companies [119]. In this case, the visual paradigm makes sense, because the graphics artists and the software developers usually do not know each other – and therefore, have separated workflows that are tailored to the specific needs of each group.

development time

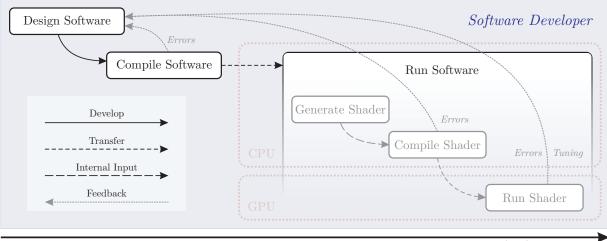

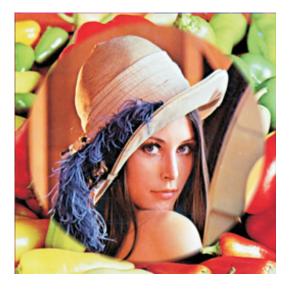

**Figure 1.3:** The "algorithmic paradigm" knows only the *software developer*, who creates the whole "software" including code for CPU and GPU. The GPU-based functionality of the software has to be extracted and transformed to the graphics hardware's internal format.

Examples for GPU-based development systems that are founded on the visual paradigm are RENDERMAN, PFMAN, INTERACT-SL, RTSL, CG, and GLSLANG [49, 91, 97, 99, 77, 104]. However, such development systems are inappropriate to implement general-purpose algorithms on the GPU, mainly because of the following two reasons:

- Due to the distinct specialized workflows, broad knowledge is required in both disciplines software engineering (developer) and computer graphics (artist).

- The visual paradigm also forces the software developer to *leave his familiar development environment* and to develop in the graphics artist's programming language.

Furthermore, because CPU and GPU-based code are developed in different programming languages, additional *binding code* is required to "glue" the different functionality together.

Please note that there are GPU-based development systems that relax the aforementioned issues. For instance, BROOK FOR GPUS, CUDA, and CTM are not graphicsoriented, but they still separate between CPU- and GPU-based code [18, 89, 106]. On the other hand, SH allows mixing the code of both processor platforms in the same programming language, but still requires knowledge in the computer graphics domain [101].

As a matter of fact, to efficiently develop general-purpose applications that are accelerated by the GPU, a significantly different approach is required – the *algorithmic paradigm*. Figure 1.3 illustrated the paradigm: the *software developer* creates the complete "software" that contains code for the main *and* the graphics processor at the same time. This means that there is a single development environment, where the same programming language is used to define CPU- and GPU-based code side by side and no *binding code* is required that connects the variables of the different processor platforms. The "GPU<sup>++</sup> development system" that will be presented in this thesis, makes use of the algorithmic paradigm. In other words, the *algorithmic paradigm* conceptually eliminates the separation between both processor platforms. In practice, GPU-based development systems that are founded on this paradigm have to deal with the following three challenges:

- **Compact Set of Generic Concepts** The development system has to present a *consistent set of generic concepts* to abstract techniques and terminology that are specific to computer graphics. For instance, *vertex* and *fragment* processing is hard to understand by the common software developer and need to be abstracted by a generic concept. The challenging task is that the new concepts have to be easier to learn, compared to the graphics-oriented concepts of the visual paradigm. While this is hard to evaluate, the rule-of-thumb is: the less concepts, the easier to learn.

- **Uniform Development Environment** Both processor platforms have to be accessible in the same development environment. In other words, CPU- and GPU-based code should be mixable in the same source code files, i.e. the code is specified in the same general-purpose programming language. Ideally, the software developer is able to use the same familiar syntax, the same compiler collection, and the same testing environment he is used to for both processor architectures. Please note that "familiar syntax" means that mathematical expressions are specified in the same way, no matter of the target platform i.e. that code should be interchangeable.

- Seamless Data Interchange Between CPU and GPU Development systems that follow the algorithmic paradigm have to eliminate the need of "binding code" – variables have to be accessed easily on both processor architectures. In other words, computation results of the graphics hardware have to be directly accessible in CPUbased code, and main processor variables have to be usable as GPU-based inputs. Please note that the prior challenges mainly addressed the syntax and style of source code and the software development workflow, while this is focused on the seamless interchange and automatic transfer of data between the main and graphics processor.

The aforementioned challenges are accomplished by using the following two-stage approach: On a theoretical level, the existing graphics-oriented concepts for programming the GPU are abstracted to generic concepts, e.g. pixel and fragment processing is abstracted via a "unified kernel definition", and the vector processor concept is abstracted via "vector fusion". Furthermore, on a practical level, graphics-hardware-based code is seamlessly integrated into the general-purpose  $C^{++}$  programming language, which is realized by using advanced object-oriented techniques like "ad-hoc polymorphism" and "generic programming". To further reduce the development complexity and to improve run-time performance, a variety of optimization strategies are automatically applied to the GPU-based code.

The GPU<sup>++</sup> development system will be evaluated extensively by implementing a broad set of general-purpose algorithms. This includes the performance comparison of CPUbased solutions with implementations for the graphics processor, as well as an analysis of the source code complexity for both processors to verify the aforementioned design goals.

#### 1.1. CONTRIBUTIONS

### **1.1** Contributions

This dissertation makes several contributions to the areas of computer graphics, graphics hardware programming, software engineering, and general-purpose computations on GPUs:

- An approach is presented that allows the implementation of general-purpose algorithms on computer graphics hardware by seamlessly extending the C<sup>++</sup> language using *ad-hoc polymorphism*. This technique enables developers to use the same environment and language for both platforms main *and* graphics processor. This approach significantly reduces development complexity for GPU-based applications.

- A consistent set of high-level graphics-independent concepts is presented, including the stream approach, vector processing, and computation frequencies. These concepts enable developers to efficiently exploit the computational power of today's graphics accelerators without the need of being an expert in computer graphics, computer graphics hardware, or the different graphics APIs for programming the GPUs.

- An abstraction scheme that hides the different computation units on the GPU (vertex and fragment processing) is presented: The *unified kernel definition* is partitioned automatically by the development system to efficiently exploit the different processing units. This technique enables the developer to specify all GPU-relevant functionality in a single place, resulting in a significant reduction of the source code complexity.

- The aforementioned GPU development system is extended to support on-the-fly optimizations, like dead-code elimination, constant folding, algebraic simplification, and back-end-dependent substitutions. These optimizations enable developers to focus more on algorithms than on implementations. The optimizations have proved to be useful for a variety of general-purpose computations, leading to a significant speed-up.

- A novel technique for vector component separation and efficient *vector fusion* is presented, i.e. scalar operations are efficiently combined automatically to exploit the vector processor architecture of the GPU. This leads to a much better granulation in the optimization stage, and furthermore, enables the developer to freely choose between vector and non-vector programming without a loss of run-time performance.

- A novel approach for efficient graph traversal and graph processing is presented, based on the *class traits* paradigm that features a *generic and extensible interface* and *optimal run-time performance*. Where the aforementioned optimizations lead to better run-time performance, the traversal approach significantly improves the GPU-based compile-time performance and therefore the overall processing speed.

- Finally, a variety of general-purpose algorithms is implemented on both processor platforms, main and graphics processor, to extensively evaluate the GPU-based development system. In all cases, the GPU-based implementation out-performs the CPU-based version by one to three orders of magnitude. Furthermore, the evaluation demonstrates that both implementations are of similar source code complexity.

## 1.2 Outline

The thesis begins in chapter 2 with a discussion of the related work, including historical and modern shading languages dedicated to computer graphics, as well as, the latest innovations in general-purpose languages for graphics hardware.

A consistent set of graphics-independent concepts for GPU programming is presented in chapter 3. Furthermore, it is shown how the aforementioned concepts confine the family of algorithms that can be accelerated by the graphics processing unit.

The major internal data structure (that represents any GPU-based code in the GPU<sup>++</sup> development system) is described in chapter 4. This includes the embedded creating of the graph via ad-hoc polymorphism, as well as its fast processing using the novel visual traits technique. This processing infrastructure is the foundation for a variety of generic and GPU-specific run-time optimizations of GPU-based computations that are presented in chapter 5. Chapter 6 presents the binding of the optimized kernel program to the graphics back-end using the OPENGL low-level shading language as an exemplar implementation.

The GPU<sup>++</sup> development system is evaluated in chapter 7 by implementing algorithms from digital signal processing, medical processing, and computer science. The run-time performance and source code complexity of the resulting implementations are further discussed in section 8. Finally, the thesis is concluded and areas of future research are suggested in chapter 9.

Additional information is presented in two appendices: Appendix A is a brief reference of the new data types, managing classes, and function calls. Appendix B contains basic examples, including their full source code and a line–by-line description. Both appendices do not contain conceptual information relevant to the thesis and were only included for the sake of completeness.

# Chapter 2 Related Work

The idea to implement general-purpose algorithms on computer graphics hardware has been introduced more than fifteen years ago, when Lengyel et al. used a rasterization device for robot motion planning in 1990 and Cabral et al. accelerated tomographic reconstruction in 1994 [72, 19]. However, most of the early work has been designed as a proof-of-concept and never meant to be used in industry-driven software development. But the introduction of programmable commodity graphics hardware in 2001 pushed the popularity of this approach even further, and shortly after, the abbreviation GPGPU ("general-purpose computations on GPUs") was coined for this new domain [73, 50]. At that time, the only way to program graphics hardware was via the detour of shading languages, because no explicit GPGPU development tools where available for quite a long time – but shading languages were mainly designed for the graphics and entertainment industry. As a consequence, most of the work and research were focused on the implementation instead of the algorithm. While this has changed lately when several companies released commercial GPGPU tools and languages by the end of 2006, most of the GPU-based programming is still done via shading languages. This chapter will present a broad overview of programming solutions including both – shading and general-purpose languages for computer graphics hardware.

## 2.1 Shading Languages

In computer generated imagery, the visual appearance of an object is influenced by both, shape and shading. The *shape* of an object is based on its surface geometry and its position relative to the viewpoint. In contrast, the *shading* depends on its optical properties and the illumination environment. Impressive images can be rendered from objects with a simple shape but a complex shading. Therefore, both attributes should are usually treated separately. In the very beginning of computer generated imagery, most of the shading was done by scanning textured images and attaching them to geometrical objects [20]. Soon after, *procedural shading* was introduced that evaluates the final color of particular points on the object's surface using a set of (sometimes very complex) mathematical equations.

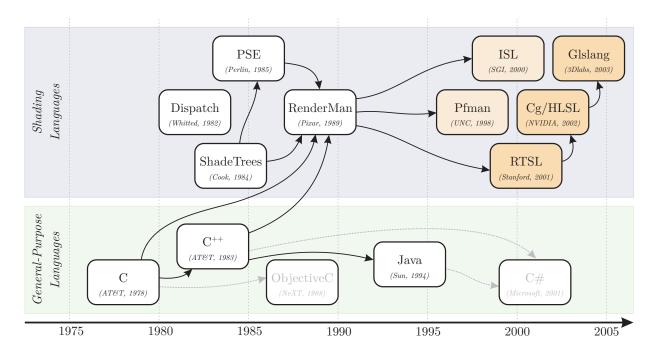

Figure 2.1: Evolution of shading languages. Most of them are inspired by the syntax and philosophy of C [61]. In the end of the 1990s, *interactive* shading languages entered the field, first for special hardware (lighter orange), then for consumer-market GPUs (darker orange).

Complex scenes usually contain many objects and each is associated to a different *shader* (i.e. the set of equations). Initially, shaders were hardwired in the rendering engine and selected via a *shader dispatch table* [125]. However, due to its *lack of portability* and the *required knowledge*, this technique was inappropriate for large productive environments like the movie industry, which resulted in a growing demand for higher-level languages. Figure 2.1 illustrates the evolution of these languages and how they influenced each other.

#### 2.1.1 History

As part of his *shader tree* work, Robert Cook developed a system where shaders (given as a sequence of mathematical equations) were read in, parsed and executed at run-time by the rendering system [24]. Even if this was not a full shader language, it decoupled the shader description from the actual rendering architecture. This concept was extended by Perlin, who developed the PIXEL STREAM EDITING LANGUAGE (PSE) that included high-level constructs, such as conditionals, loops, functions, and a rich set of arithmetic and logical operators [98]. Perlin considered shading as a postprocess, so he rejected the concept of distinct shader types (as proposed by Cook) in favor of a singular "space function", i.e. a per-pixel shading of the already computed frame-buffer. However, such an approach is hard to apply within a global context, e.g. for ray-tracing and radiosity.

#### 2.1. SHADING LANGUAGES

Based on the aforementioned work, Hanrahan et al. developed the RENDERMAN SHAD-ING LANGUAGE (RMSL) as part of PIXAR'S RENDERMAN rendering system [49, 119]. The language is similar to "C" but tailored especially to shading calculations [61]. It offers a very small set of fixed data types (color, point, float, and string) and there is no way to define new types or high-level constructs like data structures or arrays. Many built-in functions are provided, e.g. for geometric computations, image processing and texture access. Shaders may be instantiated multiple times with possibly different values for its arguments and particular instances are attached to the objects in the scene. Today, RENDERMAN is the de-facto standard for photorealistic rendering in movies.

In 1998, Olano et al. introduced PFMAN, the first real-time shading language (for the PIXELFLOW architecture). It is very similar to the aforementioned RENDERMAN shading language, but is slightly limited: only surface and light shaders are supported, fixed-point math has been added to avoid floating-point operations and  $C^{++}$  functions can be called directly from the shader [91]. Because of its scalability, the PIXELFLOW architecture was capable to render scenes at 30 frames per second, even for complex procedural shaders. Unfortunately, the PIXELFLOW hardware was too expensive and failed commercially.

A significantly different approach was introduced by Peercy et al.: Instead of using specific graphics hardware, the OPENGL software architecture itself is treated as a general SIMD computer, where the high-level shading description is translated into multiple rendering passes of the OPENGL library [97]. In combination with a small set of OPENGL extensions, a full implementation of the RENDERMAN shading language has been presented on top of this "SIMD model" approach – the so-called INTERACTIVE SHADING LANGUAGE (ISL). Unfortunately, the generality of this approach also is its major drawback – each command of the shader program is individually executed for all frame-buffer elements, hence, temporary values are written to the frame-buffer after one command and are read in for the next command. As a consequence, the ISL wastes most of its run-time for memory access and due to the large overhead of calls to the OPENGL programming interface.

Second generation GPUs started to provide (limited) programmability that was significantly extended in 2001 with the introduction of the "programmable vertex unit" [73]. Based on this new functionality, Proudfoot et al. developed the STANFORD REAL-TIME SHADING LANGUAGE (RTSL), which was especially designed for interactive procedural shading [99]. The RTSL is based on a unified framework – the "programmable pipeline" – that provides the same syntax, types and operators for different "computation frequencies", i.e. computations done per scene, per object, per vertex and per fragment. However, this may result in a part-time CPU-based emulation of several computation frequencies. A computational model, based on the virtualization of several pipeline stages, is used to remove resource constraints of existing hardware architectures. Beside native operations supported by all GPUs (e.g. scalar and vector multiplication), the RTSL introduces so-called "canned functions" that are supported by special graphics hardware or are not supported yet, but will be in future (e.g. bump-mapping). Most of these techniques can be found in succeeding shading languages – the RTSL itself is no longer maintained, because it evolved into the CG and HLSL shading languages that will be described in the next section.

#### 2.1.2 Cg and HLSL

Some developers of the RTSL joined hardware vendor NVIDIA at the end of 2001, to define and implement a new shading language. This has been done in close collaboration with MICROSOFT, thus, the result is one language with two different names – NVIDIA's "C for graphics" (CG) and MICROSOFT's "High-Level Shading Language" (HLSL) [77, 35, 45]. Even though the language is the same by syntax and semantic, they differ by *philosophy*: CG was designed as an additional layer on top of both popular graphics APIs (i.e. OPENGL and DIRECTX) for a small performance penalty, while the HLSL offers a clean interface and avoids API overhead due to a tight integration into the DIRECTX framework.

CG/HLSL is a further development of Stanford's RTSL. The language evolved broadly: many functions have been added to address the latest GPU functionality, control flow operators are supported, half and fixed have been added, vectors with up to four scalars and matrices with sizes up to  $4 \times 4$  are supported, and some C<sup>++</sup> techniques have been included. Changes can also be found in the architecture design: Although the concept of the "programmable pipeline" still exists, it is combined with the idea of a virtualized machine, leading to the concept of *language profiles*: subsets of the full language that are supported on particular hardware, computation frequencies, or APIs. CG is in active development, even though most of the changes apply to the architecture, instead of the language. In contrast, MICROSOFT decided to break the compatibility by the release of DIRECTX10, introducing support for "geometry shaders", and many extensions to the CGFX format.

#### 2.1.3 OpenGL Shading Language

The OPENGL shading language, GLSLANG, was designed and implemented by 3DLABS in the end of 2002 [104]. However, the final specification was delayed till 2004, because the OPENGL consortium had to decide if CG or GLSLANG should be included in the final OPENGL 2.0 specification [62]. At the end, GLSLANG made the race – mainly due to architectural purposes – and therefore became the first shading language that has been adopted in a truly cross-platform way by all major graphics hardware vendors.

Similar to most other shading languages, GLSLANG is based on "C" with some additional syntax from the RENDERMAN language. As a consequence, the important features are very similar to HLSL/CG. The main advantage of GLSLANG, compared to the aforementioned choices, is not one of syntactic finesse, but rather a fundamental difference in the design of not the language itself, but the *process of using it* – RTSL, CG, and HLSL all translate the source code to some kind of low-level assembler representation "outside" the underlying 3D API, using external tools (RTSL and CG) or via the API itself (HLSL). Then, the low-level code is translated a second time "inside" the 3D API to the machine code of the actual graphics hardware. In contrast, GLSLANG compiles directly from highlevel shader code to the machine code of the GPU, skipping the intermediate assembler representation. This leads to a significant performance gain, because graphics-driver developers know best how to optimize the generated instructions for their hardware.

## 2.2 Languages for General-Purpose Computations

All the aforementioned approaches are founded on the visual paradigm, i.e. they introduce a new programming language and they are focused on computer graphics. While the first property might be acceptable, the latter is a major limitation for a wider acceptance of GPGPU in industry-driven software development – additional graphics knowledge significantly increases development times and costs. However, for a long time, the aforementioned shading languages were the only way to develop applications for the GPU – but this has changed lately. This section presents GPU-based programming languages that are not focuses on computer graphics, but on general-purpose computations.

#### 2.2.1 Brook for GPUs

BROOK was developed at the Stanford University primarily as a programming language for "streaming processors", such as STANFORD'S MERRIMAC streaming supercomputer, and the IMAGINE processor [29]. Buck et al. adapted BROOK to the capabilities of computer graphics hardware, making it the first general-purpose language for the GPU [18]. BROOK extends the C programming language by *streams* – a "collection of elements" where each element is manipulated by the same computations. Streams are different to "arrays", because there is no index operation and element dependencies are not allowed. The functionality that is applied to each stream element is called *kernel* – which is comparable to a "shader".

Development with BROOK is a two-stage process: Once the program is developed, its compilation results in a set of  $C^{++}$  files that can be added to the host application. Unfortunately, the target operating system, the target graphics vendor, and the target graphics API have to be specified in advance. BROOK is not maintained since the end of 2004, except for some small progress to support ATI's CTM (presented in section 2.2.3).

#### 2.2.2 CUDA – "Compute Unified Device Architecture"

The CUDA environment, introduced by NVIDIA in the end of 2006, is similar to BROOK, i.e. the standard C programming language is extended to support streaming types and corresponding operations [89]. In contrast to BROOK, the CUDA environment generates full executables (instead of intermediate  $C^{++}$  files). CUDA can be used as a *unified environment* to develop applications for both processor platforms – CPU and GPU. Furthermore, this language does not need a graphics back-end, because it accesses NVIDIA graphics hardware directly and therefore supports unique features in GPU-based development, like a full integer and bit instruction set, branching, looping, pointer support, large kernel programs of up to millions of instructions, and thousands of threads.

In addition to the programming language, the CUDA framework also includes libraries for linear algebra (BLAS) and digital signal processing (FFT), that can be used outside the CUDA language. Unfortunately, the software is in an early stage and has not yet been opened for the public, i.e. there is no official distribution and documentation available.

#### 2.2.3 CTM – "Close-to-the-Metal"

At the same time NVIDIA release CUDA, ATI introduced the CTM platform – a dataparallel virtual machine that allows direct communication with ATI graphics devices alongside the graphics API [106]. Similar to the CUDA architecture, many constraints are imposed by this approach, including the ability to read, modify, and write memory in a single program, to directly access host memory, or to cast between formats without explicitly copying the data. CTM is distributed as a library that allows to open, use, and close "managed connections" to one of the three units of the graphics hardware: 1) The "command processor" is programmed via an architecturally independent language, 2) the "data-parallel processor" is programmed via a native (architecturally dependent) instruction set, and 3) the "memory controller" allows direct access to graphics and main memory.

As the name implies, CTM is used to access graphics hardware on a very low level. It has been designed for hand-optimized tuning the GPU-based functionality and not for every-day use. Furthermore, the application is responsible for all problems that occur in programming the graphics processor, which increases development complexity and costs.

### 2.3 Embedded Languages and Libraries

The aforementioned approaches all are stand-alone programming languages that are used in addition to the general-purpose programming language of the host application (except CUDA). This means that GPGPU developers have to switch between several languages to address the main and the graphics processor. Furthermore, additional code is required to "bind" GPU-based code to the CPU-based host application, e.g. to interchange data.

A different approach is based on the *expression template* technique (which is part of *template meta-programming*) exploits the compiler to pass expressions as function arguments [120, 121]. This usually means that *operator overloading* is used to overwrite the default behavior of the compiler to postpone the evaluation of an expression to a user-defined moment. In other words, instead of performing the actual evaluation of an expression, intermediate code is created that wraps the expression on a higher level of abstraction for later evaluation. The GPU<sup>++</sup> development system also uses this approach extensively, hence, the technique is described in much more detail in chapter 4.

The idea of using "expression templates" for GPU programming was first mentioned by McCool and Heidrich in the context of *texture shaders* in 1999 [82]. From a technical point-of-view, the presented API was designed as an intermediate layer for shader tree generation, located between the high-level texture shader specification and the low-level rendering API. McCool and Heidrich presented several ideas for the high-level specification, including shader compilers and the "expression template" approach. Based on this work, McCool enhanced the API and created the SMASH library ("Simple Modeling And SHading") [79]. This API was a non-hardware-accelerated testbed for low-level single- and multi-pass graphics concepts. In parallel, the aforementioned concepts were improved and McCool introduced the first version of SH, based on the SMASH testbed, in 2002 [83].

#### 2.3.1 Sh and the RapidMind Development Platform

The SMASH testbed – developed at the University of Waterloo – was experimental, not hardware accelerated, and important features were missing, e.g. only a limited subset of OPENGL was supported and no "render-to-texture" functionality was available. This changed in 2004, when SH addressed real graphics accelerators for the first time [81, 101]. As a result, the SH language was slightly downgraded, due to the limited instruction set of the available GPUs (e.g. data-dependent control constructs, and missing data types). Note that the SMASH API still existed as a thin intermediate layer in the SH framework, but different targets were addressable using separate back-ends of the SMASH layer.

While SH pioneered embedded GPU programming, it still was graphics-oriented, i.e. it was in-between the visual and the algorithmic workflow of chapter 1 (it addressed a single developer with knowledge in both – graphics and software engineering). Furthermore, the integration into  $C^{++}$  has been criticized, due to the massive use of macros and the lack of object-oriented features (e.g. polymorphism and inheritance) [32]. The development of SH has been stopped in 2006, mainly because it evolved into a commercial product.

The RAPIDMIND DEVELOPMENT PLATFORM (RMDP) is the commercial successor of the SH library that has evolved in two significant ways: It no longer is graphics-oriented and it also supports the CELL BROADBAND ENGINE as a target processor [80]. This makes it an attractive development platform for GPGPU programming. Unfortunately, most of the aforementioned  $C^{++}$  issues still exist, e.g. the use of macros to embed the language, the compilation of programs cannot be manually controlled, shader programs are not passed as classes – it still is not possible to derive shader programs from existing implementations or to use polymorphism – and the binding of parameters does not conform to common  $C^{++}$ argument passing. Furthermore, the developer is responsible for all optimizations – similar to SH, because the RMDP does not include any strategies for run-time optimization.

#### 2.3.2 PeakStream Platform

A comparable commercial product is the PEAKSTREAM PLATFORM that also uses the "expression template" approach for embedded programming of the GPU [96]. However, in contrast to other solutions, graphics hardware is optional, as long as the main processor supports the streaming extension command sets SSE2/SSE3. Unfortunately, the software is not yet made public and therefore no further information is available.

The PEAKSTREAM PLATFORM currently works on LINUX and extends the GCC or IN-TEL compilers. Such a coupling is required, because this software introduces own compiler **pragmas** and additional debugging information. Consequently, debugging and profiling the GPU-based code is fully supported. Furthermore, new types are natively built-in, which actually makes the PeakStream Platform an own programming language (section 2.2). The used programming model is based on "data parallelism" similar to the SIMD approach of ISL in section 2.1.1, i.e. special arrays (Arrayf32 and Arrayf64) are combined with high-level operations to create new arrays. As a consequence, there is no explicit kernel synthesis.

#### 2.3.3 Accelerator

A similar programming model is used in the ACCELERATOR library, which is the second programming library for graphics hardware from MICROSOFT – beside the graphics-oriented DIRECTX HLSL [116]. While ACCELERATOR is distributed as a library and does not actually use the "expression template" technique to embed into a host language, it integrates into most of the languages available as part of the .NET framework (e.g. C#). The common .NET just-in-time compilation generates CPU- or GPU-based code at run-time.

Similar to the PEAKSTREAM PLATFORM, ACCELERATOR does not support kernel synthesis, but uses special array types (so-called "data-parallel arrays") for GPU-based computations. Unfortunately, data-parallel arrays are different to normal memory arrays, because they lack of specific features (e.g. aliasing, pointer arithmetic, and the access of individual array elements). Therefore, a time-consuming explicit conversion is required each time the developer wants to share data between CPU and GPU. Currently, the ACCELERATOR library is a research project and does not allow to be used in commercial development.

## 2.4 Comparison Chart

Table 2.1 gives a detailed overview of the aforementioned approaches and the features they support – including architectural features, portability, and the used programming model. The more features the language supports, the better the GPGPU software development.

| Features         | CG  | $\operatorname{GLSL}$ | BROOK | CUDA | $\operatorname{CTM}$ | Sh  | RMDP | Acc. | GPU <sup>++</sup> |

|------------------|-----|-----------------------|-------|------|----------------------|-----|------|------|-------------------|

| General-Purpose  | No  | No                    | Yes   | Yes  | Yes                  | No  | Yes  | Yes  | Yes               |

| Embedded Lang.   | No  | No                    | No    | No   | No                   | Yes | Yes  | n/a  | Yes               |

| Object-Oriented  | n/a | n/a                   | No    | No   | No                   | No  | No   | No   | Yes               |

| Cross-OS         | Yes | Yes                   | Yes   | Yes  | No                   | Yes | Yes  | No   | Yes               |

| Cross-GPU        | Yes | Yes                   | Yes   | No   | No                   | Yes | Yes  | Yes  | Yes               |

| Direct Access    | No  | No                    | No    | Yes  | Yes                  | No  | No   | No   | No                |

| Kernel Synthesis | Yes | Yes                   | Yes   | Yes  | Yes                  | Yes | Yes  | No   | Yes               |

| Array Data-Type  | No  | No                    | Yes   | Yes  | Yes                  | Yes | Yes  | Yes  | Yes               |

| Optimization     | Yes | Yes                   | Yes   | Yes  | n/a                  | No  | No   | No   | Yes               |

| Non-Commercial   | Yes | Yes                   | Yes   | Yes  | Yes                  | Yes | No   | Yes  | Yes               |

| Active Develop.  | Yes | Yes                   | No    | Yes  | Yes                  | No  | Yes  | Yes  | Yes               |

**Table 2.1:** Comparison of the presented GPU-based development systems (and  $GPU^{++}$ ). PEAKSTREAM is not included, due to the lack of available information. *Object-Oriented* means, that inheritance and polymorphism work for kernel programs, and *Kernel Synthesis* means that kernel programs are specified explicitly (i.e. not using "data-parallel arrays").

# Chapter 3 Concepts

The GPU<sup>++</sup> development system has been designed to simplify the implementation of general-purpose computations on the GPU. As shown in chapter 1, this also includes the abstraction of GPU-specific techniques, terms and patterns. Otherwise, despite a nice programming interface it would still be required to be an expert in computer graphics and graphics hardware to implement non-graphical algorithms on the GPU. In other words, "the fewer technical details about the GPU and computer graphics, the better for GPGPU".

But this cannot be done to the maximum, due to the differences that exist between GPU and CPU. Such differences are the main reason that some algorithms run much faster on the graphics hardware than on the main processor. A full abstraction of the GPU therefore inevitably leads to a theoretical construct, a proof-of-concept without a practical value. Therefore, the  $GPU^{++}$  development system has not been designed to hide all differences between the CPU and the GPU architecture, but to abstract the most important features by generic concepts that common  $C^{++}$  developments are able to learn in a short time.

This chapter is about the five concepts that are relevant for GPU-based development using the  $GPU^{++}$  system. Each of these concepts falls into one of the following categories:

- Fundamental Only two of the concepts are fundamental the application life-cycle of section 3.1 and the streaming paradigm of section 3.2. Developers have to be familiar with these concepts, because they significantly affect the design of GPU<sup>++</sup> programs.

- **Optional / Optimization** The other concepts are optional the vector processor in section 3.3, computation frequencies in section 3.4 and array access in section 3.5. In fact, developers are able to implement algorithms in GPU<sup>++</sup> without further knowledge of these concepts. While this leads to adequate results, there is significant potential for further optimizations. To create the most efficient code with the GPU<sup>++</sup> system it is inevitable for the developer to be familiar with all of these concepts.

The remaining section 3.6 clarifies the consequences of the aforementioned concepts by presenting a list of GPU-based requirements. Even though the reader might be familiar with programming concepts for the GPU, it is strongly recommended to read the sections of this chapter, due to new terms and definitions that are used in the  $GPU^{++}$  system.

## **3.1** Application Life-Cycle

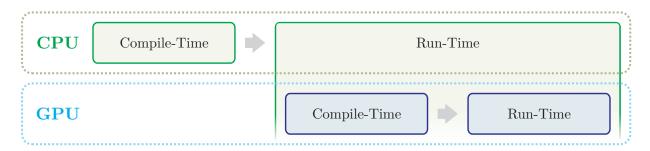

The life-cycle of a common application can roughly be divided into four stages – design, implementation, compile-time, and run-time. While the first and second stages both are independent of the target environment, the third and fourth stages are platform-specific, i.e. the compiler generates an executable for a dedicated target that can only be executed in this environment.<sup>1</sup> In the context of  $C^{++}$  applications, the CPU is "known" at compile-time and it is "used" at run-time.

But if also graphics hardware is used, there are actually two processors – the CPU and the GPU. While most parts of the application are compiled for and executed on the CPU, other parts are compiled for and executed on the GPU. Consequently, there are two compile-time stages and two run-time stages – one for the main processor and one for the graphics processor. The situation becomes even more challenging, because there is no unified GPU architecture, i.e. there is no unified GPU instruction set. In fact, each family of GPUs uses its own proprietary instruction format – which is encapsulated in the graphics library. This leads to the obscure situation that there is no way to fully compile a GPU-based program "in advance", because the target graphics hardware is unknown.

While multiple compile-time and run-time stages might be advantageous for the different developers of a visual workflow, they significantly hinder the single-developer algorithmic workflow (see chapter 1). There are two reasons that may lead to confusions – the absence of a clear nomenclature and the overlapping of the different processor stages. For instance, it sounds and it feels confusing that "a compile-time constant of the GPU can be a run-time variable of the CPU". To avoid irritation, the following definitions of the lifecycle stages are used (excluding the processor-independent "design" and "implementation") – figure 3.1 presents a graphical representation:

- **CPU-based compile-time** The full application is compiled to the specific CPU architecture, including "intermediate code" for embedded GPU processing. While CPU-based parts are optimized, no optimizations are applied to the GPU-based routines.

- **CPU-based run-time** The created executable is launched on the target mmain processor. While the CPU-based code cannot be changed anymore, the behavior of the GPU-based routines can be effected using CPU-based run-time variables.

- **GPU-based compile-time** This stage is performed at CPU-based run-time, when GPU-based code is processed for the first time. In this stage the GPU code is created, optimized, translated and uploaded to the available graphics processing unit.

- **GPU-based run-time** This stage is also performed at CPU-based run-time, when a specific GPU routine is executed. It launches the GPU-based code (that has been created and uploaded before), which then performs all GPU-based computations.

<sup>&</sup>lt;sup>1</sup>The *target environment* is dependent of the programming language – e.g. Java generates code for a virtual machine, while the target environment for  $C^{++}$  programs usually is a specific CPU. For the sake of simplicity, the term "CPU" is used as a synonym for all target environments in the remainder of this work.

Figure 3.1: The life-cycle stages of an application that works on both - CPU and GPU. The first two stages (*design* and *implementation*) are not shown, due to their hardware independence. Note that *compile-time* and *run-time* overlap for the different processors.

## 3.2 Streaming Paradigm

Graphics hardware has impressively evolved over the years, as shown in figure 1.1. This leads to the question, why all the optimizations on the graphics processor cannot also be done on the main processor. Where is the main difference between the CPU and the GPU?

Computations on the GPU can be *parallelized* much more efficient than CPU-based programs. In fact, state-of-the-art graphics hardware contains more than 100 unified computation units [90]. Graphics hardware initially was designed to accelerate the color computation of pixels on the screen. For common visual algorithms, like texture mapping or local illumination, such computations are independent from other pixels, i.e. a pixel can be computed without the (intermediate) results of other pixel computations. As a matter of fact, this independence of data allows the graphics hardware to compute a large set of pixels simultaneously – current GPUs are able to compute up to 24 pixels in parallel [90].

Such a parallelization scheme is known as *stream processing*, which means in general: given a set of input data (the so-called *stream*), a series of compute-intensive operations (the so-called *kernel*) is applied to each element of the stream. On the graphics hardware the stream is the "vertex list" or "input texture", and the kernel is known as "shader" [122]. Stream processing has been known in scientific computing before – a very popular streaming approach is the IMAGINE stream architecture developed at the Stanford University [103]. Furthermore, the streaming paradigm slowly finds its way to the design of next generation CPUs, as can be seen for the latest CELL and ITANIUM microprocessors [52, 84].

This concept is crucial, because it leads to most of the performance-boost of the GPU compared to the CPU. As a consequence, the streaming paradigm is fundamental in the  $GPU^{++}$  development system. However, because the term "stream" may be misunderstood as a one-dimensional data container, the following definitions are used:

Array – Arrays are equivalent to "streams" – they contain a set of elements. However, developers might be confused by this term, because streams are usually limited to one-dimensional data sets, while arrays can be also of higher dimensions. Furthermore, reading from such containers looks and feels like reading from memory arrays.

#### CHAPTER 3. CONCEPTS

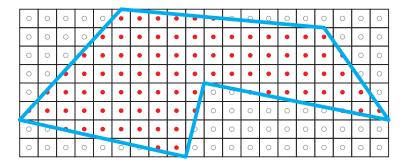

**Figure 3.2:** The *region* (blue) specifies the elements of an *array* (red dotted squares) that are computed by a *kernel*. Elements outside the region (gray circles) are not touched.

- Kernel A kernel is a series of commands that compute a value, which is then written to an output array. The computation may depend on the individual elements of several input arrays. Note that a kernel program is executed on an output array, i.e. the specified kernel is applied to each element of the array it has been executed on.

- **Region** A region confines the elements of an array, i.e. it is a "mask" that determines the elements that are computed by the given kernel. Regions also can be used for input arrays, to specify the array elements that should be used as inputs for the kernel.

Figure 3.2 illustrates, how a kernel is applied to some array elements that were specified by a region. The default case applies the kernel program to *all* elements of an array.

### **3.3** Vector Processor

Computer graphics is about *vectors*. The processing of geometries, the computing of colors, such computation heavily involves vectors – in the three-dimensional space, on the two-dimensional screen, by addressing one-, two- or three-dimensional textures, computing three- or four-dimensional colors (with transparency as the fourth component). Hardware that accelerates graphics computations has to address this special algebra.

As a consequence, a major difference between GPU and CPU is its "data scalarity", i.e. while a single instruction on the CPU usually manipulates a single data value, a single instruction of the GPU usually acts on multiple data entities simultaneously. This technique is classified as *single instruction, multiple data* (SIMD), while the CPU instruction set is classified as *single instruction, single data* (SISD) [37].<sup>2</sup> Processor architectures based on the SIMD approach – so-called *vector processors* – are known in scientific computing since the 1960s. The GPU is a very small vector processor, because an instruction is performed on four scalars at most. In contrast, the CONNECTION MACHINE of the early 1980s computed hundreds and thousands of scalars with a single instruction [118].

<sup>&</sup>lt;sup>2</sup>Today almost all CPU designs include SIMD extensions, e.g. Intel's MMX, SSE, and SSEx, AMD's 3DNow, or IBM's AltiVec. However, the core processing of these CPUs is still done via SISD commands.

#### 3.4. COMPUTATION FREQUENCIES

In other words, for a main and a graphics processor with the same core and memory speed, a dedicated algorithm theoretically runs up to four times faster on the GPU due to its vector architecture. While this is a rare case that cannot be generalized, many algorithms can be restructured to make partial use of the SIMD approach on the GPU.

This concept is optional, because  $GPU^{++}$  tries to find an optimal assignment of the vector components for a given kernel program using the vector fusion approach of section 6.2.1. It does not make a difference, if the developer uses the vector processor abilities of the system or not – internally, each vector component is treated as a separate equation that is merged with the other equations in a final stage. This results in acceptable performance. However, there are three reasons why the "vector processor" concept is recommended in GPU development anyway: 1) the vector processing paradigm may change the design of the kernel program, which leads to an implementation that can be optimized more efficiently, 2) to reduce GPU-based compile-time, a heuristic is used for merging vector instructions, which works best if the developer gives some "hints", and 3) the implementation of a kernel might be easier to understand and to maintain when using the vector processor concept.

It should be noted that there is an alternative way to interpret the GPU as a vector processor: On a higher level of abstraction, a single call of a graphics API function invokes the recomputation of the complete frame-buffer [97]. However, this thesis uses the term "vector processor" to describe the small scale parallelism of the most basic GPU vector type of today's graphics hardware – the four-component vector. The aforementioned large scale parallelism has been explained in section 3.2 using the "streaming paradigm".

### **3.4** Computation Frequencies

A computation frequency indicates "how often" a computation is performed in a larger context – the more often a task is done, the higher its computation frequency. This term usually is used in combination with the "direction" of computations, where the output of a *single* low-frequency computation is used as input in *multiple* high-frequency computations.

Developers are accustomed to this concept in their everyday work, e.g. using *precalculations*, where a complex sub-expression is computed once to be reused many times in the actual algorithm. While computations at lower frequencies might take more time, they also reduce the execution time of higher frequencies that are performed more often. Hence, computation frequencies may lead to optimized time and memory requirements for the algorithm, e.g. computations done at compile-time are available for free at run-time.

The paradigm of computation frequencies has been introduced to graphics hardware and shading languages by Proudfoot et al. as part of STANFORD'S REAL-TIME SHADING LANGUAGE [99]. A typical dependency-chain of computation frequencies in computer graphics is: SCENE  $\rightarrow$  OBJECT  $\rightarrow \underline{\text{VERTEX}} \rightarrow \underline{\text{GEOMETRY}} \rightarrow \underline{\text{EDGE}} \rightarrow \underline{\text{SCANLINE}} \rightarrow \underline{\text{PIXEL}}^3$ Note that there might be less or more computation frequencies, depending on the context.

<sup>&</sup>lt;sup>3</sup>Underlined frequencies are programmable on today's GPUs: *vertex* is programmable since 2001, *pixel* became programmable in 2002, and *geometry* programming started in 2006 with the NV80 chip set [90].

The context of the aforementioned frequency-chain is computer graphics, which seems to be inappropriate for general-purpose computations. As a consequence, the  $GPU^{++}$  development system defines its own chain of the following four computation frequencies:<sup>4</sup>

- **Compile** Expressions that can be evaluated at GPU-based compile-time belong to the COMPILE computation frequency. The inputs are taken from CPU-based run-time (i.e. constants and variables that have been evaluated by the CPU-based parts of the application) and the result of this computation is passed to following frequencies.

- **Execute** Expressions that can be evaluated before the GPU program is executed fall into the EXECUTE computation frequency. The input arguments can change between distinct executes, but they stay constant for all array elements. This includes all CPU-based constants and variables, as well as results from the COMPILE frequency.

- **Region** The REGION computation frequency evaluates all expressions that depend on the passed regions, e.g. any linear expression that uses the array element position as its input. As before, the inputs are taken from lower frequencies (i.e. COMPILE and EXECUTE), while the expression result is passed to the last frequency.

- Element Finally, the ELEMENT computation frequency evaluates the remaining expressions. Input arguments are the results of previous computation frequencies, as well as elements of input arrays. The result of these expressions is the final result of the overall computation, and therefore, it is stored in the elements of the output array.

The concept of "computation frequencies" is optional, because many algorithms can be implemented on the GPU without further knowledge if this paradigm. However, especially the use of "type qualifiers" (section 4.2.3) requires a brief understanding of this concept.

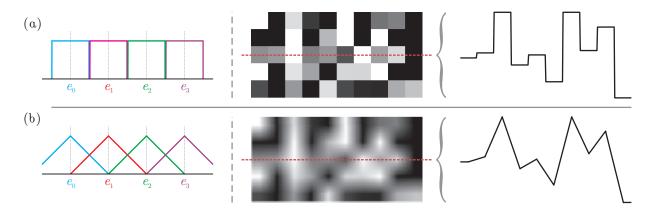

## **3.5** Array Access

Similar to CPU-based arrays, where an *index* addresses a specific element, GPU-based arrays can be read within a kernel program by using a *position*. However, while the index for CPU-based arrays is an *integral*, the GPU-based position is a *floating-point value*. This leads to the following two differences: First, each array dimension is scaled to the range [0...1], e.g. the fifth element of a one-dimensional array of size 20 is accessed by using position 5/20 = 0.25. Second, it is possible to access an *interpolated element* that lies "in-between" two array elements, e.g. position 0.251 results in a different values than 0.249.