### Lehrstuhl für Integrierte Systeme der Technischen Universität München

# Development of a fast DRAM Analyzer and Measurement of Typical and Critical Memory Access Sequences in Applications

### Simon Albert

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzende: Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. Ing. Ingolf Ruge (em.)

- 2. Univ.-Prof. Dr. Ing. Klaus Diepold

Die Dissertation wurde am 25.02.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 23.07.2008 angenommen.

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.d-nb.de abrufbar.

ISBN 978-3-89963-888-2

© Verlag Dr. Hut, München 2008 Sternstr. 18, 80538 München Tel.: 089/66060798

vww.dr.hut-verlag.de

Die Informationen in diesem Buch wurden mit großer Sorgfalt erarbeitet. Dennoch können Fehler nicht vollständig ausgeschlossen werden. Verlag, Autoren und ggf. Übersetzer übernehmen keine juristische Verantwortung oder irgendeine Haftung für eventuell verbliebene fehlerhafte Angaben und deren Folgen.

Alle Rechte, auch die des auszugsweisen Nachdrucks, der Vervielfältigung und Verbreitung in besonderen Verfahren wie fotomechanischer Nachdruck, Fotokopie, Mikrokopie, elektronische Datenaufzeichnung einschließlich Speicherung und Übertragung auf weitere Datenträger sowie Übersetzung in andere Sprachen, behält sich der Autor vor.

1. Auflage 2008

# Contents

| 1 | Intr         | roduction                                    | 1        |

|---|--------------|----------------------------------------------|----------|

|   | 1.1          | Evolution of Computer Systems                | 1        |

|   | 1.2          | Outline                                      | 2        |

| 2 | Me           | mory Systems                                 | 5        |

| _ | 2.1          | Memory Hierarchies                           | 5        |

|   | 2.2          | Random Access electrically rewritable Memory | 5        |

|   |              | 2.2.1 SRAM                                   | 7        |

|   |              | 2.2.2 Flash Memory                           | 7        |

|   |              | 2.2.3 SDRAM                                  | 8        |

|   | 2.3          | Hitting the Memory Wall                      | 8        |

|   | 2.4          | Computer System Architecture                 | 9        |

|   |              | - · · · · ·                                  | 9        |

|   |              | 1 0                                          | 3        |

|   |              | •                                            | 20       |

| 3 | Fw           | duation of Memory Access Sequences 2         | 25       |

| J | 3.1          | 1                                            | .o<br>26 |

|   | $3.1 \\ 3.2$ |                                              | 28       |

|   | 3.3          |                                              | 30       |

|   | ა.ა          | Weastrement                                  | W        |

| 4 | Mea          |                                              | 3        |

|   | 4.1          | Overview                                     | 33       |

|   |              | 4.1.1 Probe Head                             | 3        |

|   |              | 4.1.2 FPGA Board                             | 3        |

|   |              | 4.1.3 PC Backend                             | 11       |

|   |              | 4.1.4 External Triggering                    | 13       |

|   | 4.2          | Verification                                 | 13       |

| 5 | DR           | AM Performance Analysis 4                    | 5        |

|   | 5.1          | •                                            | 15       |

ii *CONTENTS*

|            |      | 5.1.1 Methodology                                                                                           |        |

|------------|------|-------------------------------------------------------------------------------------------------------------|--------|

|            |      |                                                                                                             |        |

|            | 5.2  | 5.1.3 Performance Limitations of future Memory Systems 5 Statistical Modelling of SDRAM Parameter Changes 5 |        |

|            | 3.2  | 9                                                                                                           | ю<br>3 |

|            |      | 9 0                                                                                                         |        |

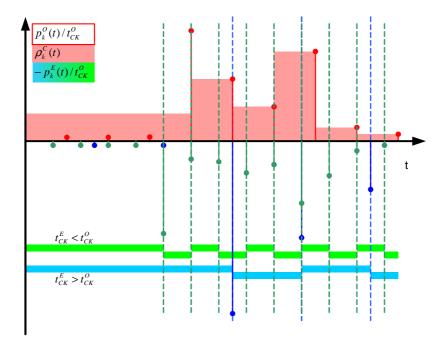

|            |      | 5.2.2 Changing the SDRAM Operation Frequency 6 5.2.3 Estimating Intercommand Spacing                        |        |

|            |      | 5.2.5 Estimating intercommand spacing                                                                       | 1      |

| 6          | Rep  | roducibility 7                                                                                              |        |

|            | 6.1  | Deviation of Key Figures                                                                                    |        |

|            | 6.2  | Local Distribution of Accesses                                                                              | 5      |

|            | 6.3  | Reproducibility and SDRAM Timings                                                                           | 0      |

| 7          | Con  | clusion 9                                                                                                   | 5      |

|            | 7.1  | Summary                                                                                                     |        |

|            | 7.2  | Limitations                                                                                                 |        |

|            | 7.3  | Related Work                                                                                                | 18     |

|            | 7.4  | Extensions and Future Work                                                                                  | 9      |

| ٨          | DB   | AM Timings 10                                                                                               | 3      |

| <b>1 L</b> |      | Intra Bank Timings                                                                                          |        |

|            | 11.1 | A.1.1 RAS to CAS delay $(t_{RCD})$                                                                          |        |

|            |      | A.1.2 CAS Latency $(CL)$                                                                                    |        |

|            |      | A.1.3 Row Active Strobe $(t_{RAS})$                                                                         |        |

|            |      | A.1.4 Row Precharge Time $(t_{RP})$                                                                         |        |

|            |      | A.1.5 Row Cycle Time $(t_{RC})$                                                                             |        |

|            |      | A.1.6 Write to Read Delay $(t_{WTR})$                                                                       |        |

|            |      | A.1.7 Write Recovery Time $(t_{WR})$                                                                        |        |

|            |      | A.1.8 Refresh Cycle Time $(t_{RFC})$                                                                        |        |

|            | A.2  | Inter Bank Timings                                                                                          |        |

|            |      | A.2.1 CAS to CAS Delay $(t_{CCD})$                                                                          |        |

|            |      | A.2.2 RAS to RAS Delay $(t_{RRD})$                                                                          |        |

|            |      | A.2.3 Four Activate Window $(t_{FAW})$                                                                      | 16     |

| В          | Con  | figurations 10                                                                                              | 7      |

|            | B.1  | PC System Configuration                                                                                     |        |

|            | B.2  | SDRAM Configuration                                                                                         |        |

|            | B.3  | Benchmarks                                                                                                  |        |

|            | -    | B.3.1 3D–Benchmarks                                                                                         |        |

|            |      | B.3.2 SPEC 2000 Suite                                                                                       |        |

| CONTENTS | iii |

|----------|-----|

|          |     |

111

C Calculations

# List of Figures

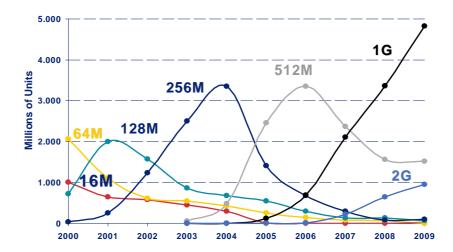

| 1.1               | Worldwide DRAM Component Sales by Generation                    |

|-------------------|-----------------------------------------------------------------|

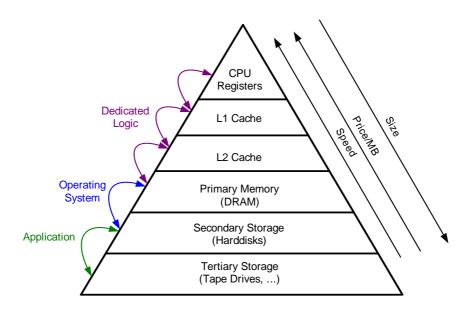

| 2.1               | Memory Hierarchy                                                |

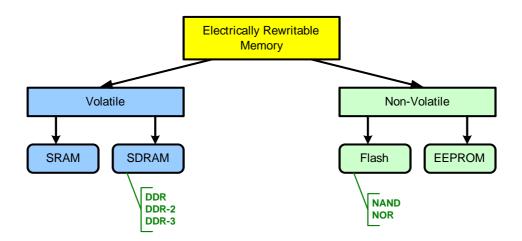

| 2.2               | Primary Memory                                                  |

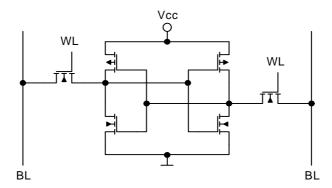

| 2.3               | SRAM Cell                                                       |

| 2.4               | Von Neumann vs. Harvard Architecture                            |

| 2.5               | Personal Computer System                                        |

| 2.6               | DRAM Cell Array                                                 |

| 2.7               | 1 Gibit DDR2 SDRAM                                              |

| 2.8               | Typical Read Sequence (worst case)                              |

| 2.9               | Interleaved Read Access to different Banks                      |

| 2.10              | DDR2 Finite State Machine                                       |

|                   | DRAM Modules, Ranks, Channels                                   |

|                   | Address Translation from virtual Addresses to DRAM Addresses 21 |

|                   | Latency Reduction by Transaction Splitting                      |

| 3.1<br>3.2<br>3.3 | Trace driven versus execution driven Simulation                 |

| 4.1               | Trace Acquisition Hardware                                      |

| 4.2               | Probe Head                                                      |

| 4.3               | 32 bit Sample                                                   |

| 4.4               | High Speed Sampling Frontend                                    |

| 4.5               | Clock Distribution Network                                      |

| 4.6               | Virtual Endpoints                                               |

| 4.7               | Ethernet Frame                                                  |

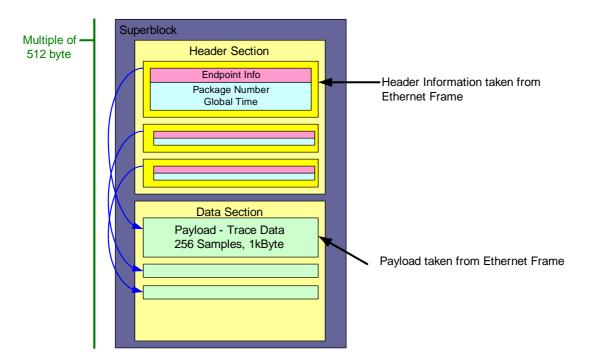

| 4.8               | Ethernet Frames within Superblock                               |

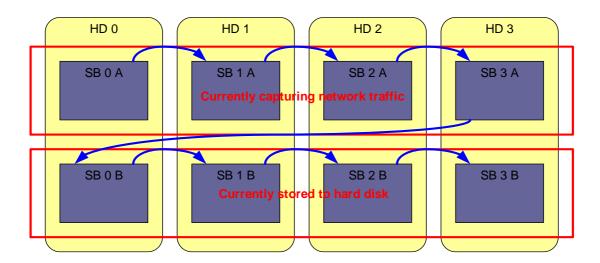

| 4.9               | Distribution of Superblocks to Hard Disk Drives                 |

| 5.1               | CA-Bus Utilization                                              |

| 5.2               | Pulling in of non-ND-Commands in Place of Deselects 48          |

LIST OF FIGURES

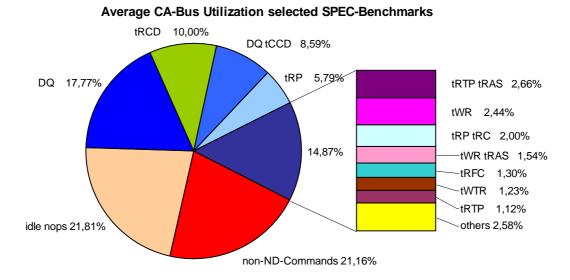

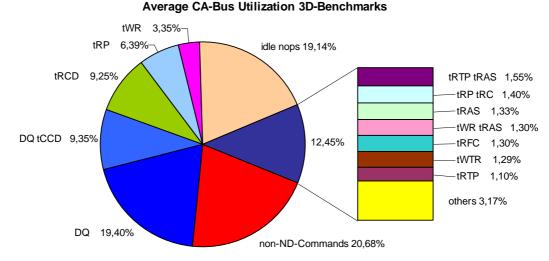

| 5.3  | CA-bus Utilization of selected SPEC 2000 Benchmarks 4            | .9 |

|------|------------------------------------------------------------------|----|

| 5.4  | CA-bus Utilization of selected 3D Benchmarks 5                   | 0  |

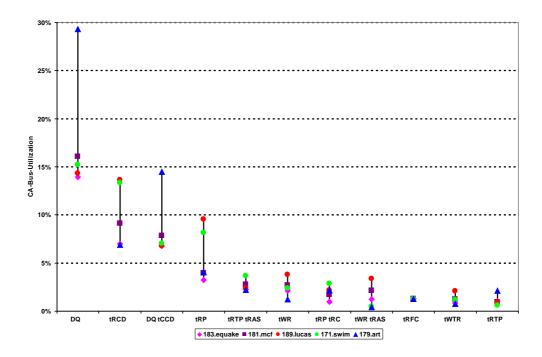

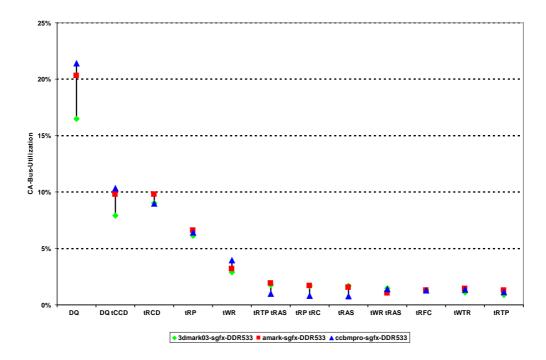

| 5.5  | Variation of CA-bus Utilization of SPEC 2000 Benchmarks 5        | 1  |

| 5.6  | Variation of CA-bus Utilization of selected 3D Benchmarks 5      | 1  |

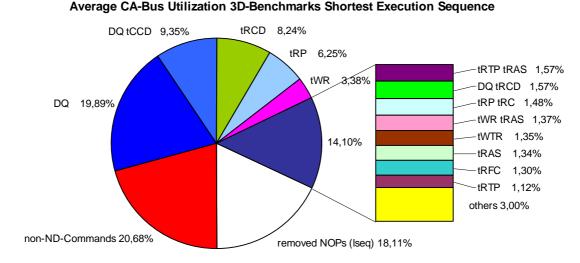

| 5.7  | Average shortest execution Sequence of selected 3D-Benchmarks 5  | 2  |

| 5.8  | Temporal Spacing of Command Pairs belonging to a particular      |    |

|      | SDRAM Timing                                                     | 6  |

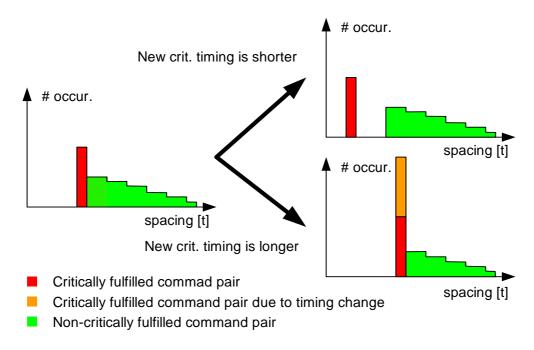

| 5.9  | Histogram Changes caused by Changes of SDRAM Timings 5           | 6  |

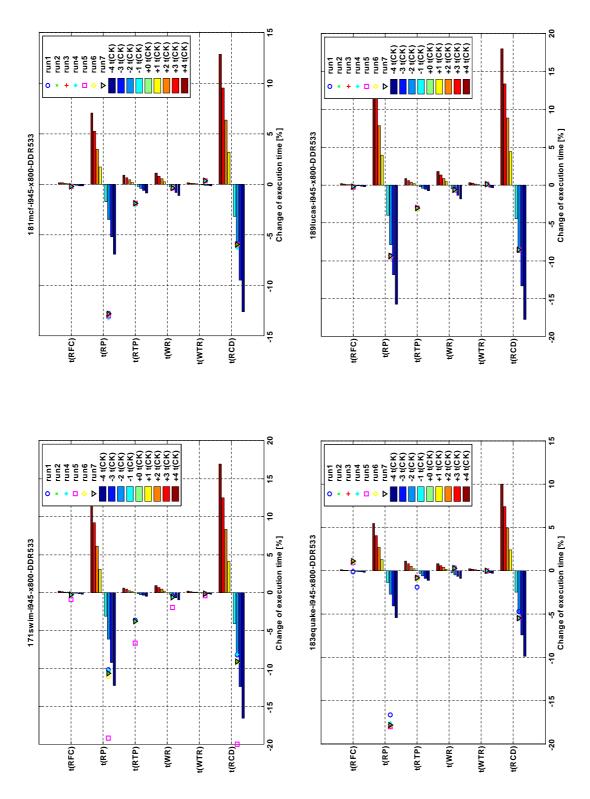

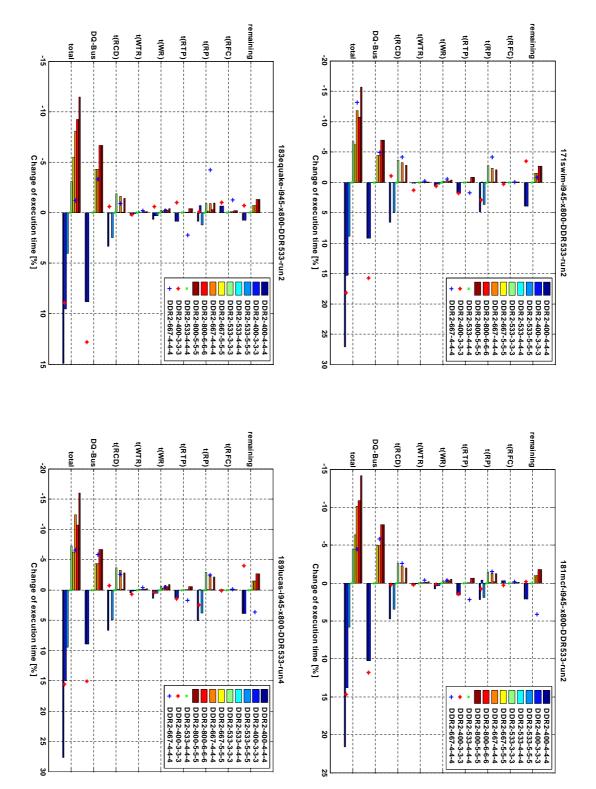

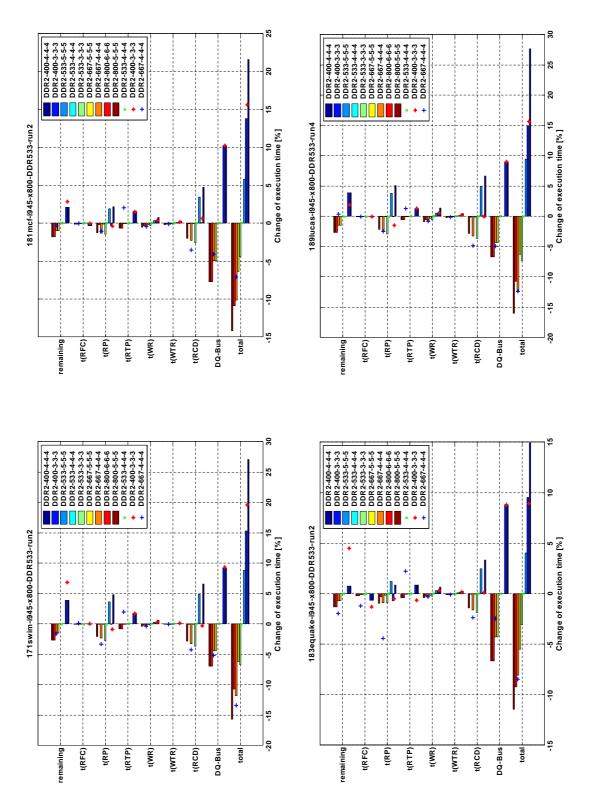

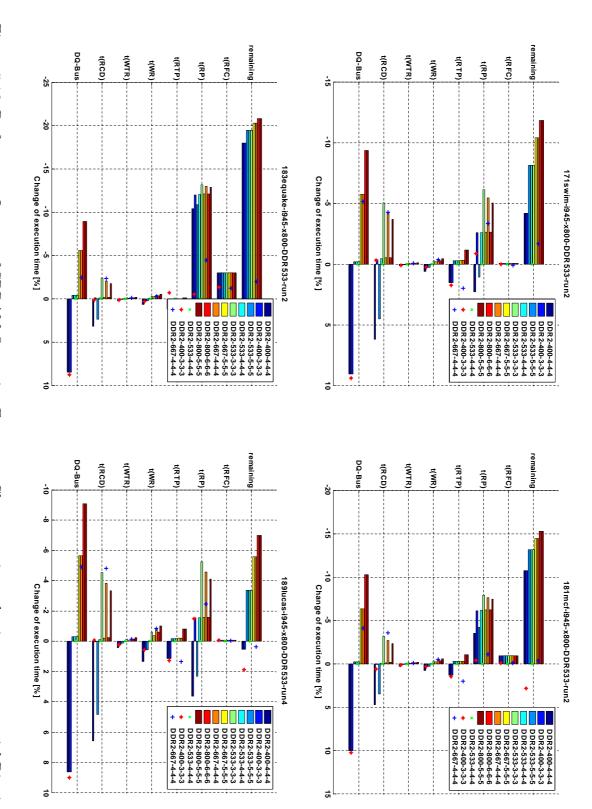

| 5.10 | Performance Impact of SDRAM Parameter Changes 5                  | 9  |

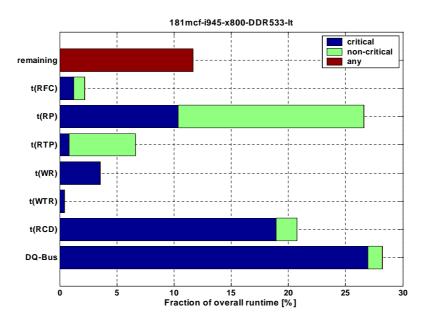

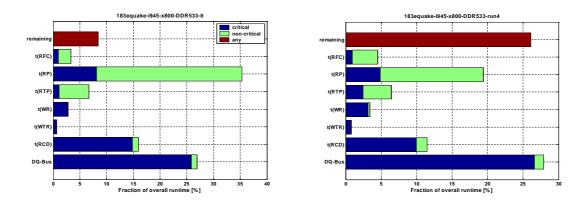

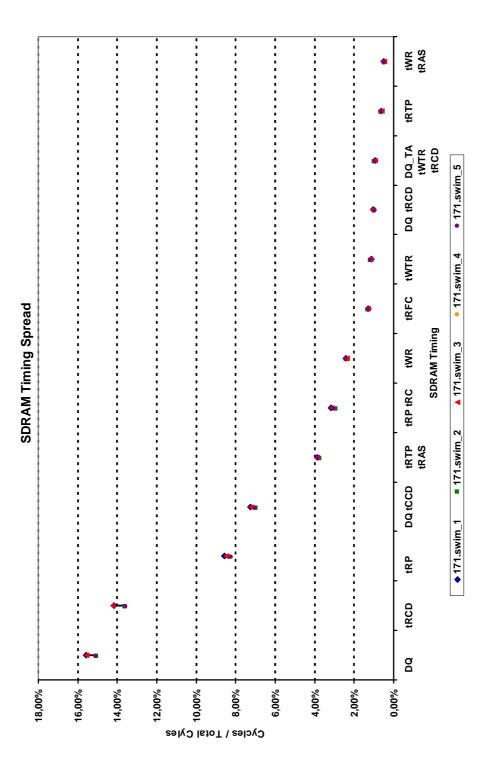

| 5.11 | Fraction of Time spent on different SDRAM Timings 6              | 0  |

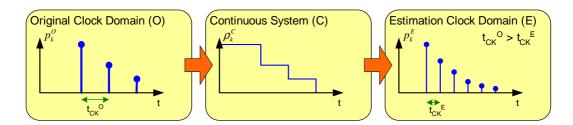

| 5.12 | Changing SDRAM Operation Frequency: Methodology 6                | i2 |

| 5.13 | Discrete and continuous Probability Density Function of Accesses |    |

|      | at different Clock Frequencies                                   | 5  |

| 5.14 | Performance Impact of SDRAM Operating Frequency Changes 6        | 6  |

| 5.15 | Performance Impact of SDRAM Operating Frequency Changes with     |    |

|      | normalized Access Pairs                                          | 9  |

| 5.16 | Performance Impact of SDRAM Operating Frequency Changes es-      |    |

|      | timated using an exponential Distribution                        | 6  |

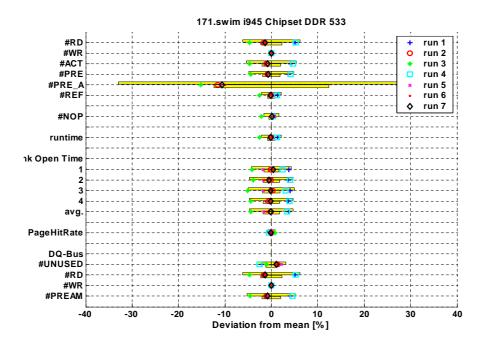

| 6.1  | Deviation of Key Figures from Mean Value: 171.swim 8             | 0  |

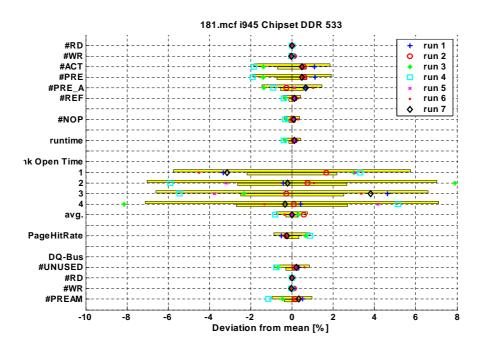

| 6.2  | Deviation of Key Figures from Mean Value: 181.mcf 8              | 1  |

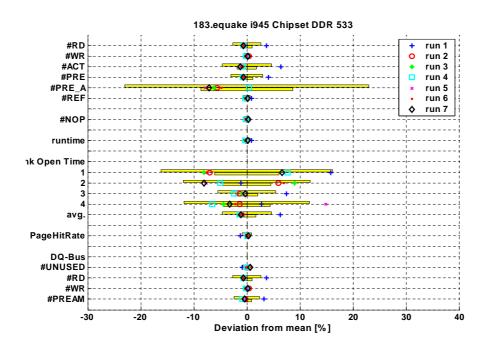

| 6.3  | Deviation of Key Figures from Mean Value: 183.equake 8           | 2  |

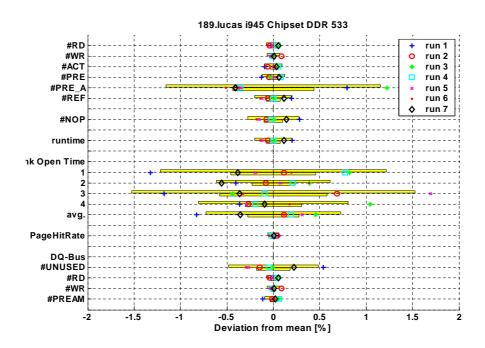

| 6.4  | Deviation of Key Figures from Mean Value: 189.lucas 8            | 3  |

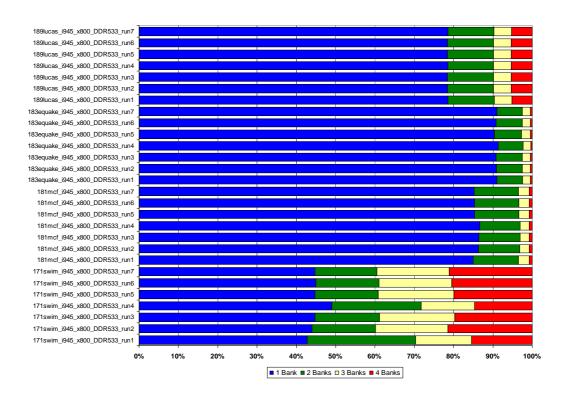

| 6.5  | Number of closed Banks per precharge all Command 8               | 4  |

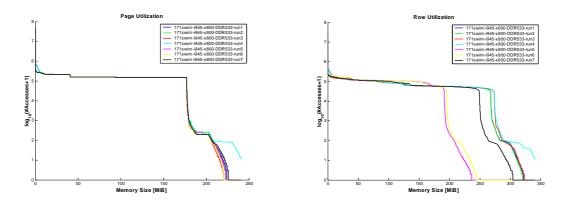

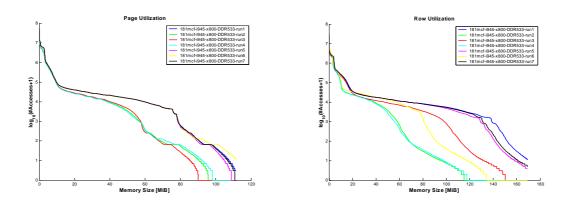

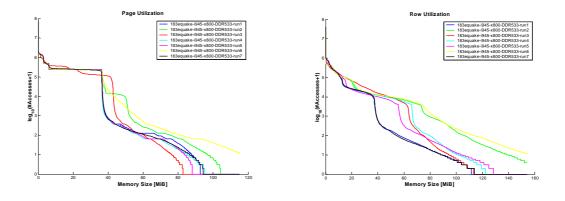

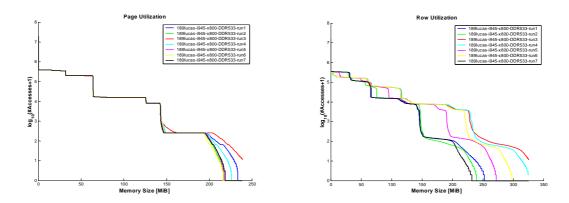

| 6.6  | Page and Row Utilization of 171.swim                             | 6  |

| 6.7  | Page and Row Utilization of 181.mcf                              | 6  |

| 6.8  | Page and Row Utilization of 183.equake                           |    |

| 6.9  | Page and Row Utilization of 189.lucas                            | 7  |

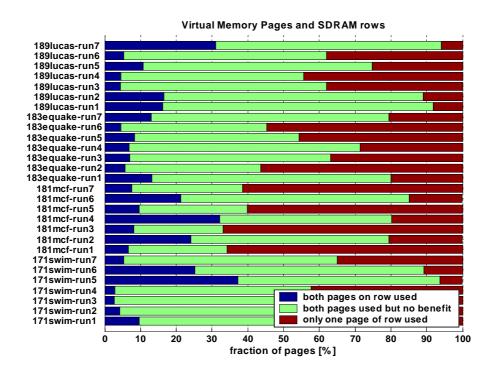

| 6.10 | SDRAM Row Sharing of virtual Memory Pages                        | 9  |

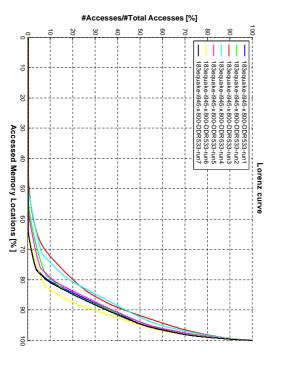

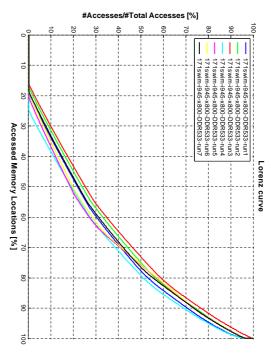

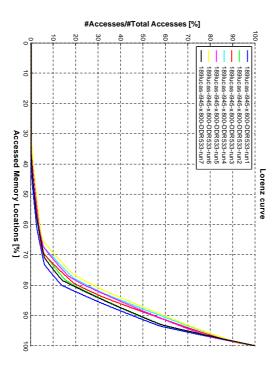

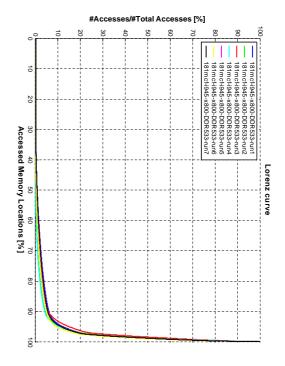

|      | Lorenz Curves of selected SPEC 2000 Benchmarks                   |    |

| 6.12 | CA-Bus Utilization                                               | 3  |

# List of Tables

| 2.1 | SDR / DDR SDRAM Data Rates and Frequencies                           | 16  |

|-----|----------------------------------------------------------------------|-----|

| 4.1 | Supported Capturing Modes depending on used Hardware Resources       | 36  |

| 5.1 | Benchmark Set                                                        | 48  |

| 5.2 | Impact of 2T Rule on System Performance                              | 50  |

| 5.3 | Accounting of Command Pairs to SDRAM Timings                         | 54  |

| 5.4 | Performance Impact of SDRAM Timing Changes                           | 61  |

| 5.5 | Performance Impact of SDRAM Frequency Changes                        | 70  |

| 5.6 | Optimal values for the parameter $b$ of the Exponential Distribution | 75  |

| A.1 | Timings to be fulfilled between Commands                             | 104 |

# List of Acronyms

AIO Asynchronous Input Output

AMB Advanced Memory Buffer

AGP Advanced Graphics Port

**BL** Burst Length

CA-Bus Command and Address Bus

CAS Column Address Strobe

CBR CAS before RAS refresh

CL CAS Read Latency

CPU Central Processing Unit

**CSA** Communication Streaming Architecture

**DDR** Double Data Rate

**DIMM** Dual Inline Memory Module

DMA Direct Memory AccessDQ Data Query (Data Bus)

**DRAM** Dynamic Random Access Memory

DSL Digital Subscriber Line

DVD Digital Versatile Disk

EDO Extended Data Output

FB-DIMM Fully Buffered DIMM

FSB Fronside Bus

FPGA Field Programmable Gate Array

**FPM** Fast Page Mode

**GPU** Graphics Processing Unit

HD hard disk

ICH IO Controller Hub

IEC International Electrotechnical Commission

IP Internet Protocol

ISI Intersymbol Interference

Ki... Kibi...  $(= 2^{10})$  Prefix specified in IEC 60027-2

LAN Local Area Network

viii LIST OF TABLES

LCD Liquid Crystal Display LSB Least Significant Bit

LVPECL Low Voltage Positive Emitter Coupled Logic

MACMedia Access ControlMCHMemory Controller Hub

Mi... Mebi...  $(= 2^{20})$  Prefix specified in IEC 60027-2

MMU Memory Management Unit

NFS Network File System

OS Operating System

PABX Private Automatic Branch Exchange

PCB Printed Circuit Board

PCI Peripheral Component Interconnect

PCIe PCI Express

PDA Personal Digital Assistant PEG PCI Express for Graphics

PLL Phase Locked Loop

PXE Preboot Execution Environment

RAS Row Address Strobe SDR Single Data Rate

SDRAM Synchronous Dynamic Random Access Memory

SMP Symmetric Multiprocessing

SRAM Static Random Access Memory

TLB Translation Lookaside Buffer

UDP User Datagram Protocol

USB Universal Serial Bus

# Chapter 1

# Introduction

## 1.1 Evolution of Computer Systems

Since the early eighties computer system performance has increased dramatically. Starting from some few megahertz, CPUs operating frequencies reach multiple gigahertz today. Similarly DRAM sizes have increased from some few kilobytes to multiple gigabytes even in cheap desktop PCs.

In addition, penetration of daily life with digital electronic has increased substantially. Today DRAM memory is no longer used in personal computers, workstations or servers only, but can be found in a wide range of applications from personal digital assistants (PDA), mobile phones, graphics cards, networking equipment (switches, routers, ...), entertainment devices (game consoles, digital TV sets, DVD players, set top boxes, ...), or peripheral components like printers or scanners. All these systems have different requirements to the memory system: Portable equipment enforces low power consumption as devices are usually powered by (rechargeable) batteries. Graphic cards require large bandwidth, while personal computers also profit from low latencies.

The increase in overall system performance also facilitates more demanding applications like audio and video (de)coding, image processing, web servers or multitasking and multiuser environments.

These performance improvements result not only from improvements in semiconductor manufacturing technology like smaller feature sizes and new materials but also from the implementation of even more complex architectures. Systems using bus master direct memory access (DMA), symmetric multiprocessing (SMP), out-of-order and speculative execution or providing multiple execution units on one chip (superscalarity) are no longer limited to the domain of supercomputers but can be bought off-the-shelf in every computer store.

Product cycles which are often even shorter than two years impose new chal-

Figure 1.1: Worldwide DRAM Component Sales by Generation (2004–2007 values are estimated) [28]

lenges to system developers and test engineers in order to keep pace with the upcoming technology changes (see figure 1.1).

The results of many traditional techniques which currently support system design engineers decisions regarding memory systems performance and power requirements have to be challenged or are no longer applicable for designing highly complex systems: Former researchers using system simulation either had the option to analyze only short program runs due to excessive simulation times of their simulation models or to extensively reduce the complexity of their simulation models making them less realistic. Researchers using measurements for memory system research also faced short measurement times due to low capturing bandwidth/low memory of their measurement equipment. The measurement setup which was developed during the thesis overcomes this severe limitation. It allows the capturing of long undisturbed command and address bus sequences from the DDR2 memory bus on real computer systems even over multiple hours.

Those *memory traces* provide system designers with a new and efficient way to gain new insights for the development of future SDRAM memory systems.

### 1.2 Outline

Chapter 2 provides a review of current microcomputer architectures, SDRAM memories and alternate primary memory technologies which might be used as a replacement for SDRAMs.

1.2. OUTLINE 3

Chapter 3 compares the two methods used for computer architecture evaluation: simulations and measurements for its pros and cons.

Chapter 4 explains the measurement setup developed during the thesis work for capturing trace sequences at the SDRAM bus.

From the gathered access sequences, those SDRAM parameters are determined which limit the system performance most significantly. A simple statistical model is derived to estimate the effect of changes of these SDRAM parameters on the system performance. The estimates of the statistical model are then compared with real measurements.

As all measurements have been done using a multitasking operating system, the reproducability of the measurements is a concern. Chapter 6 investigates the impact of an unknown computer system starting state and limited control of task scheduling and memory assignment.

Chapter 7 summarizes the findings of the thesis and concludes with an outlook to future SDRAM research activities, which are supported by the developed measurement hardware.

# Chapter 2

# Memory Systems

## 2.1 Memory Hierarchies

Traditionally, computer storage is integrated in a hierarchical memory system consisting of different memory types with different access times and cost profiles.

This concept turned out to be effective, as usually accesses to instruction and data memory are not distributed equally over the available memory but memory access sequences comprise spatial and temporal locality. Temporal locality denotes the effect that memory locations which have been recently accessed will be accessed in the near future again. Spatial locality means that accesses to memory locations adjacent to memory locations which have been recently accessed are more probable than accesses to memory locations which are far away [26, p.47].

Therefore, it is a good idea to store data items which are used frequently in fast cache memory "near" the CPU or even in processor registers, while data items which are rarely used can reside in cheaper DRAM memory or can even be held in secondary or even tertiary storage. The transmission of data items between different levels in the memory hierarchy is done by dedicated logic or may require support from the operating system or even user mode applications depending on the level in the hierarchy (see figure 2.1).

# 2.2 Random Access electrically rewritable Memory

For the design of a primary memory system different types of memory can be taken into account. These memory technologies are either volatile (they loose the stored information when the power is shut off) or non-volatile (the information is kept even if no power is applied to the device).

Figure 2.1: Memory Hierarchy

Figure 2.2: Primary Memory

Figure 2.3: SRAM Cell [27]

#### 2.2.1 SRAM

The SRAM cell is a RS-flipflop consisting of four transistors plus two transistors for selecting the addressed flipflop [27, p.362]. This six transistor topology provides low access times and does not need any periodic refreshment of the SRAM cell due to the regenerative feedback of the transistors (see figure 2.3). Unfortunately, having six transistors for one single SRAM cell leads to extremely high silicon area requirements. Today the use of SRAM memory arrays in the Gigabit range seems to be not acceptable from the cost to performance point of view. Therefore, SRAM is mostly used as cache memory only. In this application it is today almost allways implemented directly on the CPU die.

### 2.2.2 Flash Memory

Flash memory is an electrically erasable and programmable non volatile memory. The information is stored in an array of floating gate transistors. A NOR Flash cell consists of a single field effect transistor with two gate electrodes (control gate and floating gate). The NOR flash cell is programmed by setting a high voltage to the control gate. The electric field between gate and the drain/source path leads to a hot-electron injection onto the floating gate. To erase the cell, a negative voltage is set at the control gate, which allows a tunneling of electrons from the floating gate to the source electrode.

The captured charge on the insulated floating gate leads to a shift of the drain-source-current over gate-voltage curve, which can be detected and evaluated as either "1" or "0" by a sensing circuit. Todays flash memories even store multiple bits in one single cell by detecting small changes of the UI-Curve.

The charge on the floating gate remains even if the power is turned off (non

volatile memory). Manufacturers often guarantee a data retention of multiple years. As programming and erasing is done by the tunnel effect, write access times are high (in the range of some μs [27, p.347]). Furthermore, programming and erasing cycles cause permanent damage to the cell. Typically after around 10<sup>6</sup> program erase cycles the cells content can no longer be determined reliably [27, p.348]. Therefore, some mechanisms have been invented in order to equalize the number of reprogramming cycles across the memory array by changing the address mapping of memory dynamically [39]. This mechanism is called wear leveling.

In addition, if erasing of single memory cells within the cell area is desired, a second transistor is required for each cell. In order to keep silicon size requirements low, most flash memory devices allow only an erase operation on multiple cells (sector erase).

This makes flash memory usable as non volatile data storage (e.g. in portable devices like digital cameras, MP3 players or USB sticks) but unusable as the only primary memory system due to the limited number of write cycles and the sector erase function.

#### 2.2.3 SDRAM

The SDRAM cell consists of a single capacitor and a select transistor. The information is stored as charge within the capacitor. Due to leakage currents the capacitors need periodic refreshment of the SDRAM cell's contents. Access times are higher than for SRAM memories, but the single transistor/capacitor cell provides significant savings in silicon area size compared to SRAMs. These savings allow the manufacturing of SDRAM components currently containing up to  $2^{31}$  SDRAM cells per chip. Thus, SDRAM memory currently is the prefered choice for primary memory systems.

### 2.3 Hitting the Memory Wall

Unlike improvements in CPU design, improvements in DRAM memory design are mostly driven by an increase in memory size but not by an increase in memory speed [31].

While the architecture of the processor to DRAM interface was modified several times within the last years evolving from "traditional" DRAM over fast page mode (FPM) and extended data output (EDO) DRAM to single and double data rate synchronous DRAM focusing on improvements in DRAM bandwidth, the internal memory cell array remained mostly unchanged.

While improvements in bandwidth can easily be achieved by an increase in parallelism, meaning that multiple bits are read at the same time and are then forwarded to the CPU, the duration of one single read or write access was not significantly decreased. Unfortunately, an improvement in bandwidth does not necessarily mean that CPUs execution time decreases significantly (e.g. when the access locality is poor) [31].

This leads to the situation that the memory system becomes a bottleneck in future computers and programs execution speed will be mostly determined by the performance of the memory system and not by the processors operating frequency [57].

Moreover, with the introduction of fast page mode memory current DRAMs are no longer true "random access" memories, in the sense that the access time of all data elements is always the same. Instead, the DRAM device can handle multiple transactions at the same time and access times depend on the current DRAMs state. Therefore, the memory controller has some degree of freedom regarding the scheduling of commands sent to the DRAM device.

Furthermore, DRAM market is driven by price. Although most manufacturers sell memory products with reduced latency and higher throughput, the application of these memory types is limited to specific applications like graphics cards as most performance boosts are correlated with higher pricing due to larger die sizes or increased packaging costs due to higher pin counts. In addition, computer system manufacturers often prefer highly standardized commodity products to reduce their economic dependency on specific DRAM manufacturers.

Thus, DRAM manufacturers have to evaluate proposals of DRAM interface improvements thoroughly to evaluate if the increase in system performance justifies an increase in pricing.

### 2.4 Computer System Architecture

### 2.4.1 Modern Computer Systems

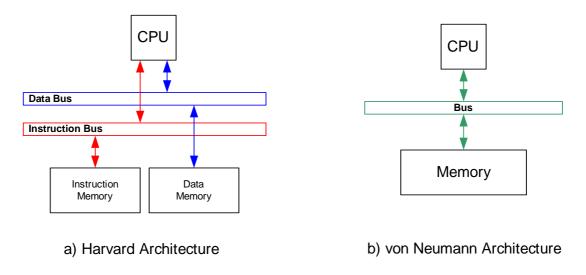

#### Harvard vs. von Neumann Architecture

The Harvard architecture implements physically separate storage and signal paths for instructions and data, enabling the transmission of both at the same time: Systems using the Harvard architecture can be found mostly in the area of digital signal processing. Furthermore, it is used for on chip busses within the CPU. As the memory has to be allocated to the separate busses in advance, the Harvard architecture is less suitable for versatile computer systems which shall be used in a large variety of applications. By contrast, the von Neumann<sup>1</sup> architecture

$<sup>^1{\</sup>rm John}$ von Neumann, Hungarian-American mathematician, 1903–1957.

Figure 2.4: Von Neumann vs. Harvard Architecture

handles instructions and data equally and transfers both from main memory over one common databus.

Most modern computer systems are a mixture of both architectures. Within the CPU core instructions and data are handled separately up to the level 1 cache while transactions from the L1 to the L2 cache and main memory are handled over the same system bus.

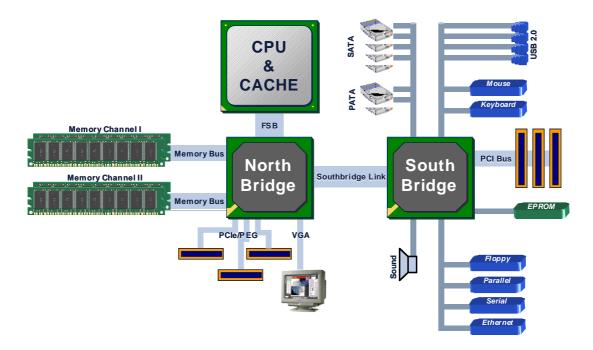

#### Personal Computer System

Figure 2.5 shows a typical modern personal computer system. On top the CPU including L1 and L2 cache, which is connected via the frontside bus to the memory controller, is shown. The memory controller is also called north bridge<sup>2</sup>. Newest processor generations like the AMD Opteron include the memory controller on the CPU as well. The north bridge handles all memory transactions between the CPU (or multiple CPUs on multiprocessor main boards) and the DRAM memory. Additionally, it provides a link to the graphics card (AGP) and to the south bridge. On latest chipsets the AGP port is replaced by a more general point to point high speed interconnect called PCI Express (PCIe), which can be used either for communication with the graphics card (PCI Express for Graphics, PEG) or other peripheral components with high bandwidth requirements like Gigabit Ethernet network adapters or hard disk controllers. Some north bridges also provide an integrated graphics card, which uses the main memory as graphics DRAM (shared

<sup>&</sup>lt;sup>2</sup>The company Intel uses the abbreviation memory controller hub (MCH).

Figure 2.5: Personal Computer System

memory graphics). Some north bridges may also provide additional (proprietary) interfaces e.g. for network controllers<sup>3</sup>.

The south bridge<sup>4</sup> is connected to the north bridge and contains most peripheral components found in typical PCs: the hard disk and floppy controller, USB, FireWire and PCI bus connections, (wireless) LAN, interfaces for mouse, keyboard or legacy IO (serial and parallel ports) or integrated sound. The north bridge/south bridge pair is also referred to as the PCs *chipset*.

#### **Embedded Systems**

While the concept of most embedded systems is similar to that of standard PCs, size and power requirements are a concern. Unlike PCs, the embedded CPU does not only include the processor core and the cache, but also integrates the functionality of the memory controller and peripheral components required for the particular application: LC-display, touchscreen, flash disk controller, sound, etc. for PDAs and mobile phones, various interfaces for networking or telecommunication equipment like DSL modems or PABX systems.

<sup>&</sup>lt;sup>3</sup>e.g. Intel CSA (Communication Streaming Architecture).

<sup>&</sup>lt;sup>4</sup>Intel also uses the term IO Controller Hub (ICH) when referring to the south bridge.

#### Caching

Caching provides a mechanism to hold a copy of frequently used data items in a fast static random access memory (SRAM) memory nearer to the CPU, providing data faster than standard DRAM memory. CPU references to memory for which a copy in the cache exist are served by the fast cache while references to memory locations which are currently not located in the cache are forwarded to the memory controller and reloaded from primary memory. A copy of the loaded data is placed in the cache, evicting some other data which is hopefully no longer required in the near future.

While up to the mid nineties cache memory was implemented using an external SRAM device on the computer's main board, increasing processor speeds forced L1 and L2 cache memories to be included on the processor die<sup>5</sup>. In addition, smaller feature sizes today easily allow the integration of cache sizes up some few Megabyte on the CPU die and can reduce system fabrication costs as well as the system size (as required by handheld equipment).

Most processors provide two separate L1 caches one for instructions and one for data items. This prevents eviction of needed instructions from the cache when large amounts of data are transferred by the CPU.

By contrast, in most systems the level 2 cache does not distinguish between instructions and data.

L1 and L2 cache operation is transparent to the user. Dedicated logic handles all transactions from the CPU to the memory controller.

In order to simplify cache design and to exploit spatial locality, the cache memory is managed on a cache line granularity. This means that the cache is divided into multiple equally sized blocks called cache lines which hold the requested data items and all data members in the direct neighborhood. Therefore, only complete cache lines are transferred from the CPU to the memory controller and vice versa<sup>6</sup>.

If the CPU reads data, a lookup in the cache has to take place to check whether the requested memory location is in the cache or if it has to be reloaded from memory. In order to reduce the search time, the number of cache locations to which a specific address range in primary memory can be mapped has to be reduced. This number is called cache associativity<sup>7</sup>.

Many publications have been released which investigated optimal cache replacement policies, the impact of variations in cache size, cache line size, or associativity on system performance, or which make proposals regarding cache aware design of software algorithms (e.g. [1, 43, 37, 35, 5, 24]).

<sup>&</sup>lt;sup>5</sup>Chip internal interconnects are faster than external connections.

<sup>&</sup>lt;sup>6</sup> During write operations, the cache controller could shorten the transfer size in order to write only data items which have been modified to the memory.

<sup>&</sup>lt;sup>7</sup>Current processors provide a cache associativity of 8 to 16 [4].

#### Virtual Memory / Paging

Virtual memory denotes the possibility to address more primary memory than is installed physically in the computer system, by moving infrequently used data to secondary storage (swapping) and reloading it when it is used by the CPU. Paging divides the physical memory into equally sized pages<sup>8</sup>. The memory management unit (MMU) which is part of the CPU core maps these pages to the CPUs virtual address space. If the CPU addresses memory locations which are not mapped to physical memory, the MMU signals a trap condition to the CPU. The CPU interrupts the running process and executes an operating system procedure which is responsible for acquiring a new physical memory page (e.g. by saving the content of an infrequently used page on disk) and mapping it to the requested memory location [46, 7]. The table which is used to translate virtual addresses to physical addresses is stored in physical memory as well. In order to eliminate the need of looking up the translation rules for every memory access, the CPU memorizes the last references to memory locations in a translation lookaside buffer (TLB) [42].

Locality analysis of memory accesses has to consider that memory locations in the physical address space which are not located on the same memory page are not necessarily related to each other (e.g. belong to the same process).

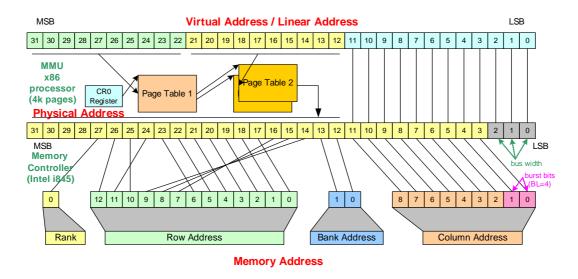

The top section of Figure 2.12 shows how the MMU translates memory references to virtual memory to linear physical addresses.

### 2.4.2 Operation Modes of DDR-SDRAM

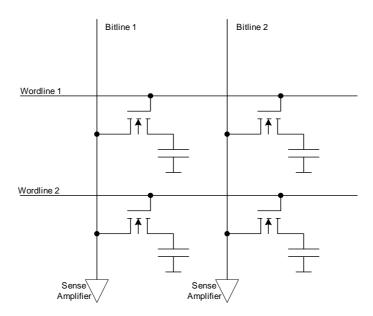

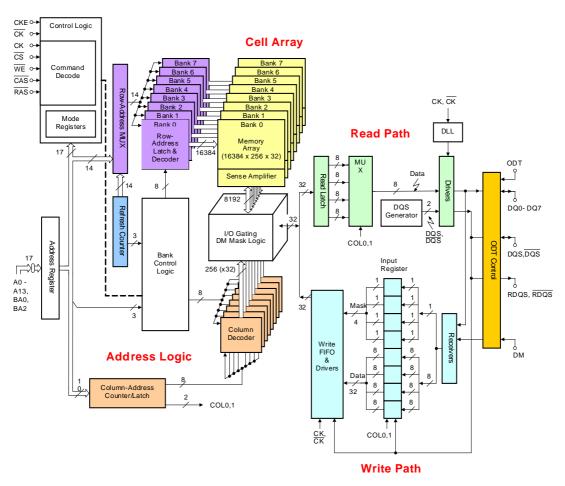

#### The Cell Array

Every SDRAM cell comprises a capacitor and a MOSFET as switching device (see figure 2.6). Information is stored by charging the capacitor<sup>9</sup>. All capacitor/MOSFET pairs are arranged in a matrix called SDRAM bank. The gate electrodes of all MOSFETs within one row are connected. This connection is called wordline. The sources of all MOSFETs within one column are also connected. This connection is called bitline.

Reading of memory contents is done by activating a single wordline. The mosfets build a conductive path between the capacitors belonging to that wordline and the bitlines so that the capacitors share their charge with the capacitance of the connected bitline<sup>10</sup>.

$<sup>^8</sup>$  Typically 4 KiB to 16 MiB in modern CPUs / operating systems [46, p.383].

<sup>&</sup>lt;sup>9</sup>A one can be represented by a fully charged capacitor, a zero may be represented by a discharged capacitor.

<sup>&</sup>lt;sup>10</sup>In modern SDRAMs the storage capacitor is in the range of 20 to 40 fF, thus the load capacitance of the bitlines has to be taken into account which can be nearly an order of magnitude larger than the capacitance of the storage capacitor and coupling between adjacent bitlines has

Figure 2.6: DRAM Cell Array

Depending on the previous voltage level of the capacitor, the bitline voltage increases or decreases. The cells information content is determined by sensing the voltages on the bitlines and comparing them to some mid reference voltage within the sense amplifier.

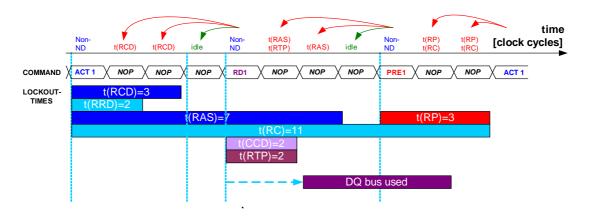

This is done for all bitlines of the SDRAM bank at the same time. The time required for activation and sensing determines the RAS latency or RAS to CAS delay  $(t_{RCD})$ .

The sense amplifier provides a positive feedback path to the cell array, refreshing the cells content while determining the voltage level on the bitline. The time required to recharge the SDRAM cells is called minimum bank activation time  $(t_{RAS})$ .

In a second step the read command selects some of the bitlines and provokes that their information is passed to the output pins. In order to enable the high throughput of modern SDRAMs, data is transferred in burst mode. This means that not only the requested data item is transferred but a complete burst of successive memory locations within the current row. DDR2 memory performs a by 4 prefetching. This means that each read command acquires the information of four consecutive addresses at the same time. The data is then time multiplexed to the output pins. Therefore, the minimum number of data items to be transferred is four (minimum burst length). Double data rate means that data is shifted out

to be considered as well [36].

Figure 2.7: 1 Gibit DDR2 SDRAM 8 banks, 128 Mibit each, by 8 organization (16384 rows, 8192 columns) [29]

| Name      | Clock Frequency      | Data Rate/Pin          | Core Frequency        | Prefetch |

|-----------|----------------------|------------------------|-----------------------|----------|

| SDR-133   | 133,0 MHz            | 133 MBit/s             | 133,0 MHz             | 1        |

| DDR1-266  | 133,0 MHz            | 266 MBit/s             | 133,0 MHz             | 2        |

| DDR1-333  | $166,5~\mathrm{MHz}$ | 333  MBit/s            | $166,5~\mathrm{MHz}$  | 2        |

| DDR1-400  | 200,0 MHz            | 400  MBit/s            | 200,0 MHz             | 2        |

| DDR2-400  | 200,0 MHz            | 400 MBit/s             | 100,00 MHz            | 4        |

| DDR2-533  | $266,5~\mathrm{MHz}$ | 533  MBit/s            | $133,25~\mathrm{MHz}$ | 4        |

| DDR2-667  | 333,5  MHz           | 667  MBit/s            | 166,75 MHz            | 4        |

| DDR2-800  | 400,0 MHz            | 800  MBit/s            | 200,00 MHz            | 4        |

| DDR3-800  | 400,0 MHz            | 800  MBit/s            | 100,000 MHz           | 8        |

| DDR3-1066 | 533,0 MHz            | 1066  MBit/s           | 133,250  MHz          | 8        |

| DDR3-1333 | 666,5 MHz            | 1333  MBit/s           | 166,625 MHz           | 8        |

| DDR3-1600 | 800,0 MHz            | $1600~\mathrm{MBit/s}$ | 200,000 MHz           | 8        |

Table 2.1: SDR / DDR SDRAM Data Rates and Frequencies [11, 33]

synchronously with every rising and falling edge of the external clock line.

The SDRAM component shown in figure 2.7 provides a by 8 organization. This means the component has eight data lines each delivering a single bit at a time. Thus, the number of bits acquired during each read command is  $32 (= 8 \times 4)$ .

The prefetching concept makes it possible to operate the SDRAM core four times slower than the bus interface. Table 2.4.2 gives an overview of SDRAM pin bandwidth, operating frequencies, internal core frequencies, and the number of prefetched bits. As one can see, improvements in pin bandwidth over DDR1 and even single data rate SDRAM result mostly from an increase in the number of bits which are prefetched, i.e. from an increase in parallelism within the SDRAM.

The time required from issuing the read or write command to the delivery of the first data item is called *CAS latency* (CL).

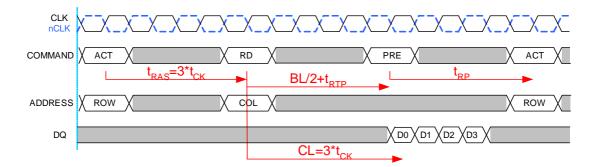

Before another row can be activated, the wordline has to be deasserted and the bitlines have to be biased to a mid voltage level. This process is called *precharging* and requires some more clock cycles<sup>11</sup>  $(t_{RP})$  until the new bank activation command can be issued. Figure 2.8 shows a typical activate-read-precharge cycle.

This leads to the situation that, depending on the current SDRAM state, three different "types" of memory accesses can occur:

If a memory access goes to a row which is already active, the read/write command can be issued directly. If the bank is not active, a new activation command has to be issued first. If the bank is active, but the wrong wordline is selected, the

$<sup>^{11}\</sup>mathrm{Currently}$  around 15 ns.

Figure 2.8: Typical Read Sequence (worst case) CAS latency=3 cycles, RAS latency=3 cycles, burst length=4

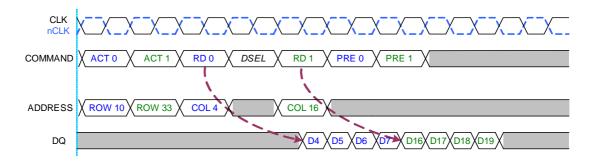

Figure 2.9: Interleaved Read Access to different Banks CAS latency=2 cycles, RAS latency=2 cycles, burst length=4

bank has to be precharged, the new row has to be activated, and the read/write command can be issued afterwards.

Thus, modern SDRAMs expose some cache functionality: Accesses going to a row which is already open (activated) can be served fast while accesses going to different rows require more time for activating the new row and probably for precharging the old one. In some systems where space, power, or cost are a concern (e.g. PDAs) modern SDRAMs may replace the level 2 cache.

Current DDR2 SDRAMs contain multiple banks (usually 4 to 8), sharing the same address and databus (*CA-bus*). From the system developers point of view they can be regarded as multiple chips within one single package. Having multiple SDRAM banks within one chip and the clock synchronous SDRAM interface provide the possibility to perform multiple concurrent commands on different banks at the same time (as long as there is no conflict using shared resources) in order to hide SDRAM access latencies.

Figure 2.9 provides an example of an interleaved read access sequence to two

different banks.

As the storage capacitors discharge over time due to leakage currents, the SDRAM content has to be refreshed periodically (in DDR2 every cell has to be refreshed every 64 ms) by activating the corresponding row. To simplify memory controller design, this can be done by issuing a refresh command (traditionally called CBR). A row address counter included in the SDRAM logic ensures that each refresh command refreshes a succeeding SDRAM row. The SDRAM refresh takes place on the same row of all SDRAM banks within the SDRAM component. It is mandatory that all banks are in a precharged state before a refresh command may be issued.

An additional power down operation mode is implemented called *self refresh*, which is used to retain the DRAMs content while the system is powered down. The *self refresh entry* command shuts down internal chip functions to reduce power consumption and ensures that the memory content is refreshed periodically using internal timers.

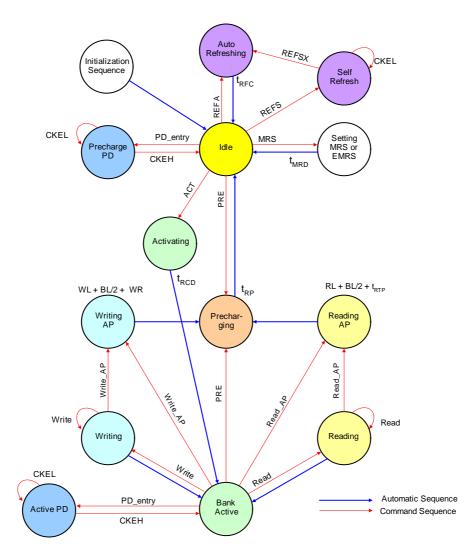

Figure 2.10 provides an overview of all DDR2 DRAM chips states and transitions between states. In addition to the commands described above, read and write commands can be combined with the precharge command so that the row is closed automatically after the data burst has been transmitted (Read\_AP, Write\_AP in figure 2.10). This simplifies memory controller design as no separate precharge command has to be issued and keeps the CA-bus unused for an additional clock cycle which would normally have been used for issuing the precharge command. Furthermore, when using auto precharging, the SDRAM's internal circuitry ensures that the SDRAM timings ( $t_{RAS}$  and  $t_{RTP}$ ) are fulfilled before executing the precharge operation internally.

#### **DRAM Modules**

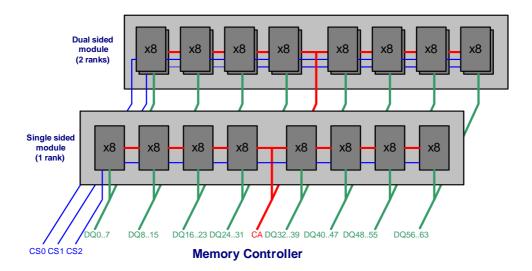

In order to increase the data bus width, in many applications (e.g. PCs and work-stations) multiple SDRAM components are soldered on a printed circuit board (called SDRAM module). Sharing the same command and address bus, they are equally addressed at the same time and each component connects to a subset of system data bus lanes. This topology is called a *DRAM rank*.

Multiple SDRAM ranks share the same CA-bus and data bus. The memory controller addresses the ranks (and distinguishes between different ranks) by asserting chip select lines which are unique for every rank.

Modern computer systems may even include multiple CA and data busses called *memory channels*. Multiple channels do not share any resources and can be operated independently in parallel or are operated equally in order to simply increase the memory bus width (*lock step operation*).

Figure 2.10: DDR2 Finite State Machine [30]

Figure 2.11: DRAM Modules, Ranks, Channels

### 2.4.3 Options for SDRAM Controllers

As seen in chapter 2.4.2 accessing SDRAM contents requires issuing a sequence of multiple commands. Additionally, multiple bank and rank topologies allow the execution of multiple concurrent memory requests at the same time. This leads to a large degree of freedom regarding the development of memory controllers and widens the design space for computer system developers.

#### **Address Translation**

The most obvious task for the memory controller is the address translation from a physical address to a "SDRAM compliant" addressing scheme by means of ranks, banks, rows and columns. Usually this is done by assigning specific bits of the linear physical address to the address components of the SDRAM (see figure 2.12 for an example of the address translation accomplished by the Intel 845 chipsets north bridge). As the address translation determines how consecutive addresses in the physical address space are mapped to the installed SDRAM memory devices, banks, and rows, it has significant influence on the row hit and miss rate of the memory system.

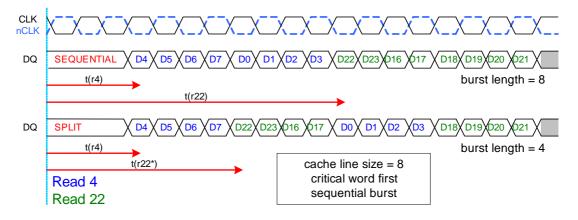

#### Cache Line Splitting

In systems using caching, only complete cache lines are exchanged between SDRAM memory and the cache. As the burst length does not necessarily have to match with the cache line size, splitting the cache line transfer into multiple

Figure 2.12: Address Translation from virtual Addresses to DRAM Addresses

Figure 2.13: Latency Reduction by Transaction Splitting

shorter SDRAM bursts may reduce the average SDRAM latency. The arrows in Figure 2.13 show the latency of two SDRAM read requests arriving at the same time at the SDRAM controller. In the top half of the diagram the SDRAM requests are executed with a burst length of eight, which is equal to the cache line size. In the bottom half the same two requests are shown as split transaction with a burst length size of four. In both cases the critical word is transferred first.

As nothing comes for free, issuing more read or write commands with shorter burst lengths occupies the command and address bus more frequently and may stall other pending requests on other SDRAM banks.

Furthermore, the memory controller can select whether to pass the cache line content in order or to pass critical data (the one which was originally requested by the CPU) first.

#### Temporal Access Ordering

As the time required to access DRAM memory depends whether the corresponding row is already open or closed, it may be advisable to collect and merge multiple accesses hitting the same row and schedule them appropriately. Additionally, transactions can be priortized, e.g. read transactions have high priority as the processor core has to wait for required data while write commands may be delayed [44].

#### Precharge Policy

The memory controller can select between an open page and a close page policy. Open page policy means that the memory row within one bank is kept open as long as possible. The idea is to exploit temporal and spatial locality as in most applications there is a significant probability that consecutive accesses will go to the same row again, making it unnecessary to issue a new activate command. The trade-off is that, if the next request addresses another row, the bank has to be precharged first, which takes additional time until the new row may be activated.

The close page policy automatically closes every bank after one transfer. This may reduce latency in applications where consecutive requests mostly go to different rows.

In addition, memory controllers may dynamically select an appropriate precharge policy by performing estimations whether they expect future references to the same row or not (dynamic page policy). The integration of memory controllers within the CPU core simplifies this task, as the memory controller may peek at the processors state (e.g. register contents, processor pipelines, cache) to support the estimation.

#### Power Awareness

In some applications (e.g. mobile devices) power consumption is a concern. The memory controller may put the memory devices in a power down state in order to reduce their power consumption. In return the memory access latency increases, if the device has to be waken up from power down to fulfill a memory request. It is the memory controllers responsibility to detect phases of low SDRAM utilization and to schedule power down phases accordingly.

#### Refresh Policy

SDRAM rows which are not accessed have to be refreshed from time to time. During these refresh periods no further requests can be handled by the SDRAM component. Therefore, it is advisable to schedule SDRAM refreshing cycles to times when there are no memory requests pending. Estimating points in times, where SDRAM components usage will be low will be one of the goals for future memory controller designers.

#### **Prefetching**

Similarly to processors performing speculative execution, the memory controller may also try to estimate future memory accesses and perform prefetching. This mechanism may reduce latency, as data items are moved to the cache before they are referenced by the processor. Unfortunately, it also increases bus bandwidth requirements as not all prefetched data items will be used. In fact wrong guesses may even decrease system performance [12]:

- High priority requests may have to be stalled in order to complete an already running prefetching operation.

- Prefetching may crowd out vital cache line from the cache, which will be referenced soon and therefore have to be reloaded again (while the prefetched data may not be used at all).

- Prefetched data may be prefetched too early so that it may be evicted from the cache before it has been used.

#### **Scatter Gather Operations**

Some applications have inefficient access patterns, e.g. algorithms which access every n-th element within a data array<sup>12</sup>. Accessing only few elements of a cache

<sup>&</sup>lt;sup>12</sup> One example is the vertical filtering of images (e.g. for deinterlacing of video frames).

line wastes memory bus bandwidth as most data items are not referenced. In addition, cache performance suffers as the cache gets filled with useless data.

Future memory controllers may map the memory content to the physical address space multiple times providing a different view of the memory array [59, 14]. Read accesses to this shadow address space will trigger the memory controller to assemble a cache line which may consist of data items located on different rows, banks or devices (gather operation). Similarly write accesses are distributed along the different DRAM memory locations (scatter operation).

This concept reduces bus bandwidth requirements as only used data is transferred and improves cache utilization.

# Chapter 3

# Evaluation of Memory Access Sequences

In order to study the behavior of a computer system, some software is executed on the device under test. At best the software should be selected for system evaluation, which will later run on the final target platform. Nevertheless, this approach is often not feasible:

- 1. The software is not yet available during the development phase of the target platform.

- 2. The hardware requirements of the software may be too high in order to be fully used in a simulator (e.g. large database applications).

- 3. The type of used application is not clear during the development phase (e.g. target applications of a personal computer may be text processing, computer gaming or numerical scientific computation all having different requirements on the hardware).

Therefore, studies are typically conducted with software which shall resemble the target application [34]. This software is called *workload* or *benchmark*. Many publications have been written on finding appropriate workloads for different applications and ways to determine metrics for the similarity and dissimilarity of different workloads and applications (e.g. [48, 38, 10, 15, 19, 51]). Nevertheless, even today determining appropriate workloads for system evaluation comes close to black magic and is often a source for dispute between different researchers.

Two types of benchmarks can be distinguished:

• The benchmark has a fixed task to be fulfilled (e.g. execution of an algorithm of a scientific application). A typical performance metric is the total benchmarks runtime.

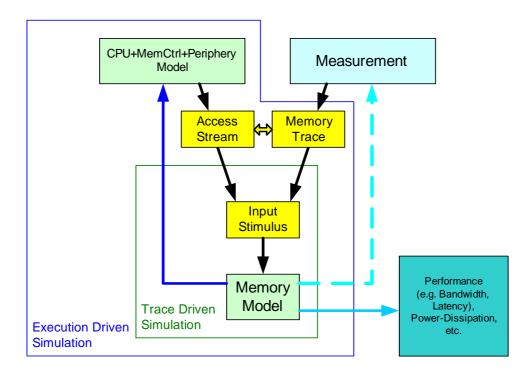

Figure 3.1: Trace driven versus execution driven Simulation

• The workload is variable. This type of workload can be found mostly in computer games. While the execution time of the workload is fixed, the system tries to perform as much computation of intermediate results as possible (e.g. in the case of a computer game the system renders as many frames on the computers screen as possible during the given time). A typical performance metric for this class of application is the number of rendered frames per unit time.

Traditionally, three techniques have been applied to study computer system behavior regarding the transactions between CPU, caches and primary memory: execution driven simulation, trace driven simulation and the measurement of access sequences (see figure 3.1).

### 3.1 Execution driven Simulation

Execution driven simulation tries to model the simulated computer systems components (CPU, cache, memory controller, buses, etc.) in software on a host systems. The applications binary is then run on the simulated target. Several simulation environments have been implemented during the last years and have been used

for research purposes: The SimpleScalar Toolset [6], SimOS [45], DRAMsim<sup>1</sup> [53], Rascas [2], POPeye [58], or Virtutech Simics [40] just to name some few.

The main advantage of execution driven simulation is that the state of all components is accessible to the engineer as the components are only software modules running on the host computer.

In addition, it is also possible to simulate hardware which is not yet existing or to run simulations which are based on unrealistic assumptions (e.g. unlimited bus width or no memory latency) to obtain critical values regarding system behavior. This makes execution driven simulation extremely useful during the design phase of new computer systems not only for performance estimation but also for functional verification of the components.

Unfortunately, as modern computer systems complexity increases, more and more hardware features have to be rebuilt in software. For the CPU side this includes the emulation of larger instruction sets, prefetching, pipelining, speculative execution, etc. . Processor manufacturers sell different processor variants for different market segments (server, workstations, notebooks) and the processor architecture/instruction set of different manufacturers may be completely different (e.g. x86-based, ARM, PowerPC, MIPS, Coldfire, 68k) extensively increasing the implementation effort for the simulator developer when different computer systems shall be compared.

The same holds for other parts of the computer system like the memory controller or peripheral components.

Additionally, the exact functionality of the components belongs to the intellectual property of the respective manufacturer and is usually not made public. So timing accurate modeling of these components becomes difficult if not even impossible.

Thus, severe simplifications of the computer system under investigation have to be imposed. Many simulators emulate only the processor and memory controller system and are therefore restricted to the execution of user mode applications, which do not rely on peripheral hardware and on the operating system which usually handles accesses to these peripheral components. Operating system calls exercised by the application are intercepted by the simulator and replaced by a functional equivalent routine on the host system. The result is returned to the application. Thus the application can use typical operating system calls (e.g. in order to communicate with the user), although these calls do not affect the simulation results.

More elaborate simulators try to emulate peripheral components like hard disk drives and graphics cards as well. The improved hardware support enables system designers to run the desired operating system on the simulated target platform,

<sup>&</sup>lt;sup>1</sup>DRAM model for other simulators like Sim-alpha [17] or GEMS [41].

enabling the simulation of operating system influences on the systems behavior. Recent studies [13] found out that omitting accesses from the OS may lead to an error in the cache miss rate of up to 100 percent even in simulations which do not use operating system calls excessively.

Unfortunately, emulation also means that tasks, which are usually handled by fast hardware on the target platform, have to be simulated by executing multiple instructions on the host platform, making execution driven simulation extremely slow. Depending on the simulations level of detail, typical factors are 10 to 10000 compared to the original system.

Therefore, system engineers have to bear programs execution time in mind and can run only short program sequences on the emulated hardware. Variations of simulation parameters (e.g. changes of the virtual computer hardware) require that the complete simulation has to be rerun.

## 3.2 Trace driven Simulation

Trace driven simulation tries to eliminate the need to simulate the entire target platform by acquiring a complete memory trace from the frontside bus. This can be done by measuring access sequences on a real computer system, or by logging all memory requests during an execution driven simulation. The logged memory accesses are then exercised on the simulation model of the memory system under investigation. In [52] Uhlig provides an overview of various software and hardware based approaches for acquiring and processing of memory traces.

This approach decouples the simulation of the CPU from the simulation of the memory system under investigation. It may reduce simulation times, as the CPU model has to be run only once and the gathered access sequence may be used as input stimulus for multiple memory models. Unfortunately, the memory system and the remaining computer parts are mutual interdependent. This means that parameter changes in either of them (e.g. changes in CPU frequency or the number of DRAM banks) render the memory trace invalid. Thus, some workarounds have to be applied in order to estimate the effect of memory system changes on the resulting access sequence. Chapter 5.2 tries to estimate the effect of SDRAM system changes on the SDRAM access sequence and thus the memory systems performance.

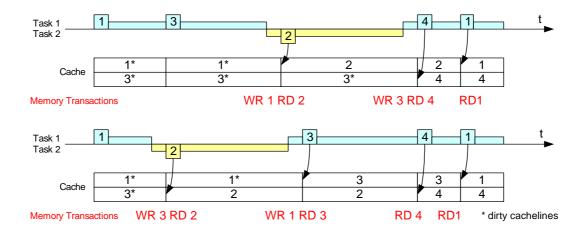

The significant interdependence of CPU and memory subsystem shall be clarified by looking at asynchronous events. Modern computer systems consist of multiple timing domains which run asynchronously to the CPU clock (e.g. the motor of the hard drive or the frame drawing of the graphics card) or are heavily influenced by user activity (movement of the mouse, reception of network packages), which determine the execution order of program sequences.

Figure 3.2: Asynchronous Timing (Dirty cachelines are marked with an asterisk)

Even worse, the memory systems performance determines not only how fast accesses are performed and how long the CPU is stalled due to memory latency, but also what accesses are performed.

Figure 3.2 shall clarify this issue. We assume a CPU using a very small fully associative cache of two cache lines. The replacement policy is *least recently used*, so that the cache line which has not been referenced for the longer period of time is replaced. We assume that the CPUs execution context is switched due to an external event (e.g. an interrupt due to user interaction). Figure 3.2 shows the caches content at each point in time, the referenced memory locations (read request), and the bus transactions issued due to the replacement of cache lines. Depending on the point in time when the first task is interrupted, the transaction sequence is completely different, although the processor executed the same two instruction sequences and although in the end the cache contents are completely equal in both versions.

Literature studies [22, 23] found out that context switches due to exception and interrupt execution account for a significant rise of the cache miss rate, leading to an increase in data transfers from main memory to the cache and vice versa.

While one could argue that context switches may be infrequently enough so that they do not influence access sequence statistics seriously, the situation becomes even more difficult with CPUs performing speculative execution. In this case the memory systems speed determines the number of execution paths the CPU core is able to follow while DRAM memory content is acquired. The different execution paths may touch different cache locations and therefore determine the cache lines which will be replaced next.

Although trace driven simulations which do not care about this fact have to be regarded suspiciously, trace driven simulation is used frequently in the research community where execution driven simulation is not applicable due to performance or complexity limitations.

But the missing feedback path also provides some benefits for the system developer. It guarantees that the input stimulus to the memory is always the same and thus eliminates the mutual interdependence of CPU and memory system. This simplifies the evaluation of different memory systems significantly, as the memory system does not affect its own input stimulus and allows the system designer to distinguish between effects which are caused by changes of the memory system and effects which are imposed by the CPU/memory interdependence [54, pp.137].

Literature studies also tried to evaluate the possibility to build artificial access patterns by combining short access sequences acquired by execution driven simulations or measurements in order to reproduce the behavior of multitasking environments or the impact of operating system calls while simplifying the design of the simulator [22].

## 3.3 Measurement

The most evident approach to determine system behavior is the direct measurement of memory accesses on the real hardware platform. The results obtained from these measurements are accurate, as no simplified hardware models have to be used. Additionally, one can generate memory traces from even most demanding software on highly complex multiprocessor computer systems on the fly.

Unfortunately, also the direct measurement of access sequences has serious drawbacks:

Firstly, the hardware platform must exist and changes in the hardware platform are limited to available and compatible hardware combinations.

Secondly, data acquisition by measuring provides only a limited view on the computer system at the point where signals are probed. Correlation of the acquired data with other components states (e.g. within the CPU or cache) are impossible unless accurate software models exist for the component and the complete stimulus has been recorded.

Thirdly, the repeatability of experiments is difficult to achieve. While it is very easy to save the starting state of the computer system in a simulator, the components of the real hardware platform cannot be stopped and probed to save the state of all components (CPU, cache, etc.). The typical solution to that problem is to use long access sequences, so that the startup phase of the benchmark is not statistically relevant.

Fourthly, the effort building appropriate acquisition hardware is extremely

Figure 3.3: Traditional Measurement of Memory Access Sequences

high. Acquiring memory access sequences requires recording the CA-bus content (and in some applications the data bus as well) on other secondary storage types like hard disks in realtime, which provide significantly lower bandwidth than the CA-bus, is an extremely demanding task. Currently DDR2-800 memory controllers may exercise up to  $400 \cdot 10^6$  commands per second on the DRAM component. Handling signals in this frequency domain does not only imposes a high complexity regarding signal integrity and processing, but also requires large storage capacities in order to sample longer periods of time.

Traditional measurement equipment like logic analyzers provide only very limited storage for sampling CA bus sequences. Current products available on the market provide a memory depth of up to 64 Megasamples [50]. The interface to store the sample buffer data to secondary storage usually provides very limited bandwidth and is therefore not suitable to transfer large amounts of memory trace data.

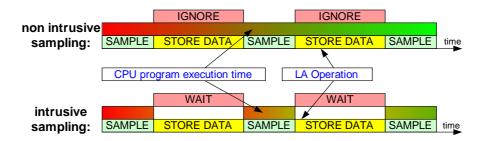

Most hardware probe solutions used in academia (e.g. [56, 55]) require to stop the tested target system periodically in order to be able to move the acquired data to secondary storage (intrusive sampling). Other solutions keep the system running and acquire only short sequences periodically, unloading the collected data while no acquisition is performed [52] (non intrusive sampling), and thus create discontinuities in the trace sequence (see figure 3.3).

Therefore, a high performance data acquisition system was implemented, which provides enough bandwidth to collect complete very large DRAM access sequences (of at least 960 Gigasamples) without altering the system behavior.

Unfortunately, the fact that data acquisition can be done on the fly does not necessarily mean that processing and evaluation of the acquired data afterwards can be done on the fly also. Therefore, a PC cluster is used, not only to store the acquired memory traces, but also for processing the acquired data, taking advantage of the computational power of the PC cluster.

# Chapter 4

# Measurement Hardware

## 4.1 Overview

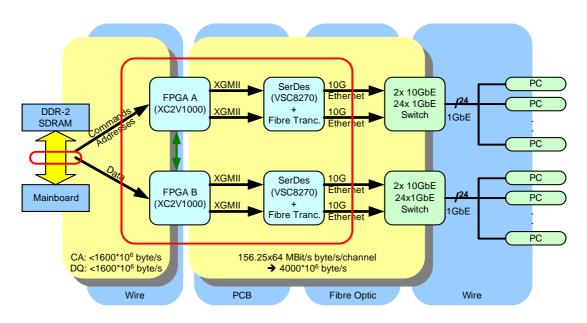

The trace acquisition hardware mainly consists of three parts: the probe head, the FPGA platform, and the PC backend.

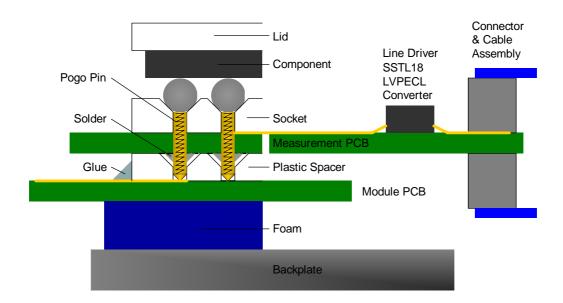

### 4.1.1 Probe Head

The SDRAM probe head consists of a six layer printed circuit board, which is placed in between the SDRAM module under test and the SDRAM component (see figure 4.2). Double ended pogo-pins, which are mounted in the PCB, form the contact between the SDRAM modules solder pads and the desoldered SDRAM component. All SDRAM signals are sent to high speed comparators (Micrel SY55857L) on the probe heads PCB, which compare them against the SDRAM's reference voltage  $V_{REF}$  and convert them to LVPECL levels, which can be transmitted over multiple centimeters of twisted pair cables to the FPGA board even at frequencies of multiple hundred Megahertz. All SDRAM lanes are length matched to minimize the skew of the CA-bus and data bus signals on the way to the FPGA.

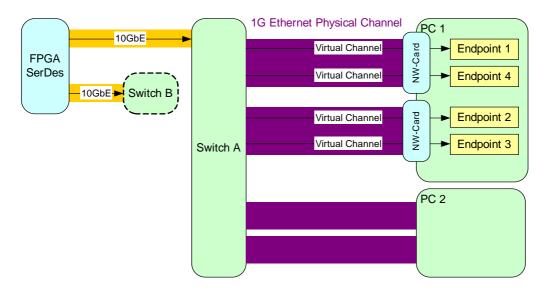

### 4.1.2 FPGA Board

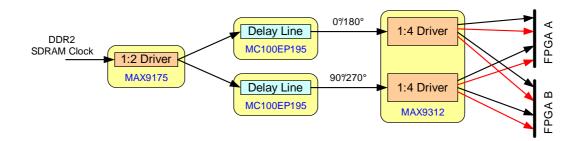

The FPGA platform basically consists of a ten layer printed circuit board with two high speed FPGAs (Xilinx XC2V1000), a 16 bit microcontroller with USB interface to download the FPGAs firmware and configuration data, a clock distribution network to propagate time shifted copies of the SDRAM clock signal to all FPGAs, and some power supply and monitoring logic to facilitate reference voltage generation and temperature sensing. Two additional eight layer PCBs are connected, containing an external SerDes chip, in order to provide 2 fibre optical channels of 10 Gigabit Ethernet per PCB.

Figure 4.1: Trace Acquisition Hardware

Figure 4.2: Probe Head

4.1. OVERVIEW 35

Figure 4.3: 32 bit Sample

### FPGA A

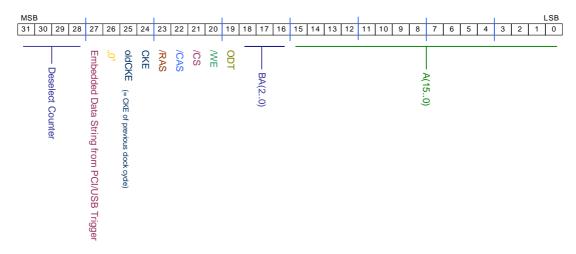

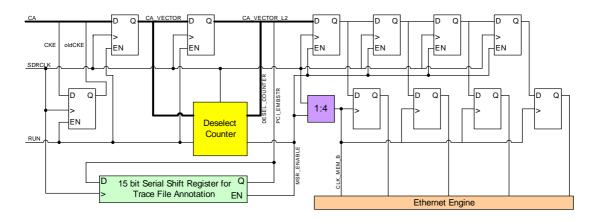

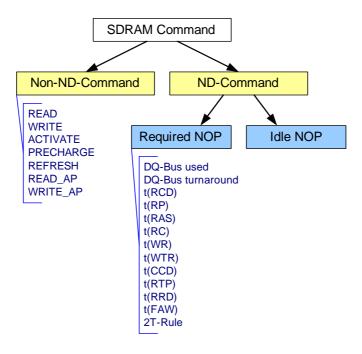

The first FPGA (A in figure 4.1) latches the LVPECL signals of the SDRAM's command and address bus from the probe head. It counts the number of deselect commands between successive "useful" commands to provide information about the temporal spacing between commands, and may optionally remove the deselect commands from the captured data stream to provide a reduction of the required bandwidth for data transmission and storage.

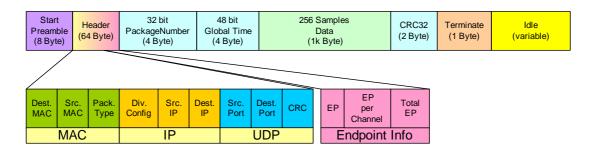

The FPGA packages time slices of 256 samples of non deselect commands and stores them in SRAM memory within the FPGA. One single sample consists of 16 bit of address bus data, four bank addresses, the four signals of the command bus (RAS#, CAS#, CS#, WE#), ODT, CKE the value of CKE of the previous clock cycle<sup>1</sup>, and the number of deselect cycles occurring before the command. This number is encoded in four bits. If a larger number of deselect commands occurred, deselect cycles are stored as samples within the trace file; so at least every 16<sup>th</sup> SDRAM clock cycle has to be stored. Furthermore, a serial data stream consisting of six user definable bits can be embedded in the trace file. This 6 bit value can be set by the device under test via the external triggering hardware (see below) to facilitate the detection of different program execution phases. The sample vector is padded with zeros to a 32 bit value (see figure 4.3).

Ethernet, IP, and UDP headers are prepended to each time slice in order to build an Ethernet frame. These Ethernet frames are transmitted together with a CRC-32 checksum via one or two 32 bit  $\times$  156.25 MHz DDR interfaces called

<sup>&</sup>lt;sup>1</sup>This simplifies analysis, as all commands can be decoded by looking at one single sample only.

|          | single   | channel    | dual channel |            |  |

|----------|----------|------------|--------------|------------|--|

|          | raw-data | compressed | raw-data     | compressed |  |

| DDR2-400 | ×        | ×          | ×            | ×          |  |

| DDR2-533 |          | ×          | ×            | ×          |  |

| DDR2-667 |          | ×          | ×            | ×          |  |

Table 4.1: Supported Capturing Modes depending on used Hardware Resources

Figure 4.4: High Speed Sampling Frontend

XGMII to the external SerDes-Chip (Vitesse VSC8270). The SerDes is responsible for 8B/10B encoding, introduction of lane resynchronization symbols, and serialization of the data to 4 differential signal pairs, which are operated at 4  $\times$  1.5625 GHz (3.125 Gbit/s). This serial interface is called XAUI.

The XAUI signals are fed into a fibre optical transceiver module, which sends them over a fibre optical link to the 10 Gigabit Ethernet uplink port of a 24 port 1 Gigabit Ethernet switch. Depending on the destination MAC address of the Ethernet frames, the Ethernet switch distributes the Ethernet frames to a cluster of PCs.

Starting with SDRAM frequencies of DDR2-533 (267 MHz), the required raw bandwidth of the CA-bus content becomes larger than the available bandwidth of one single 10GbE link, requiring the second 10GbE link. It turned out that the applied compression scheme (deselect removal) is sufficient to facilitate measurements of the CA-bus using only one single 10GbE port even at frequencies of DDR2-667 memory (see table 4.1).

Figure 4.4 shows a simplified block diagram of the high speed sampling logic implemented within FPGA A. As this part of the design has to be operated with the SDRAM's clock frequency of up to 400 MHz, it imposes the highest restrictions

4.1. OVERVIEW 37

regarding the design complexity of the implemented logic. Furthermore, placement and routing of the logic within the high speed path becomes a demanding task in order to fulfill all timing requirements.

If the system is capturing data (RUN=1), the content of the entire CA bus (i.e. the 25 LSBs of the 32 bit sample shown in 4.3) is sampled with every rising clock edge. The CKE value of the previous clock cycle (oldCKE) is added to the vector. This ensures that power down entries end exits can be recognized during trace file analysis even when deselect removal is active. The first register stage is placed directly in the IO blocks within the FPGA. This guarantees that the routing delay is almost equal for all CA bus members (minimizing the skew between the CA bus signals).

The deselect counter evaluates the command bus signals (i.e. RAS#, CAS#, CS#, WE#) to detect deselect cycles which can be removed from the trace file. The counter appends the number of deselects to the four MSBs of the sample vector (DESEL\_COUNTER). It also decides whether a sample is passed to the four stage shift register shown on the right side of figure 4.4. MSR\_ENABLE is high when sampling is in progress (RUN=1) and deselect removal is disabled (i.e. all sample vectors are propagated to the shift register) or the command is not a deselect command or the deselect counter is 15 (i.e. the deselect is the sixteenth command in a continuous sequence of deselects). The annotation data is also added to the sample vector (bit 27) in the high speed domain.

Whenever four sample vectors have been propagated to the shift register, data is transferred to a set of latches. From there it is forwarded to the Ethernet engine. The Ethernet part of the design always handles four sample vectors at a time in a 128 bit vector. Demultiplexing the data stream by a factor of four reduces the clock frequency to at most 100 MHz (and even less if deselect removal is active), simplifying placement and routing of logic within the FPGA. Furthermore, demultiplexing is required in order not to exceed the maximum write rate of the FPGAs internal static RAM.

In an early design stage a set of counters was implemented to count the number of commands of every command type (activate, read, write, precharge, etc.). The counter which had to be enabled to count the particular clock cycle was determined by evaluating CA\_VECTOR. The SDRAM analysis conducted in [3] used the results obtained by these counters. Although the counters were implemented using a carry-look-ahead strategy to facilitate counting at these high clock rates, they limited the performance of the FPGA acquisition hardware to frequencies of at most 267 MHz. Therefore, the counters were removed in a later design stage<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup> If counting of commands is desired (e.g. for verification of recorded trace files), it is highly recommended to implement the counters in the "low speed domain" behind the 1 to 4 demultiplexer.

Figure 4.5: Clock Distribution Network

### FPGA B

The second FPGA (B in figure 4.1) is intended to capture the data bus content of a SDRAM component with a data bus width of up to 16 bit. As there is currently no application for analyzing the transmitted data, the second FPGA was not programmed and equipped with a SerDes backend during the creation of this thesis.

#### **Clock Distribution Network**