#### Technische Universität München Lehrstuhl für Entwurfsautomatisierung

## Waveform Based Statistical Timing Analysis of Integrated Digital Circuits

#### Manuel Volker Schmidt

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Wolfgang Utschick

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr.-Ing. Ulf Schlichtmann

- 2. Univ.-Prof. Dr. rer. nat., Dr. h. c. mult. Manfred Glesner, Technische Universität Darmstadt

Die Dissertation wurde am 30.09.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 01.12.2008 angenommen.

# Waveform Based Statistical Timing Analysis of Integrated Digital Circuits

Manuel Schmidt

September 30, 2008

## **Preface**

Any possible calculation can be performed by an algorithm, running on a computer that provides sufficient time and storage space.

(Alan M. Turing)

This work is a result of my activities as a research assistant at the Institute for Electronic Design Automation. I would firstly like to thank the head of the institute Professor Ulf Schlichtmann, who gave me the opportunity to do my research work at his institute. His support and advice and the friendly and open atmosphere at the institute made this work possible. Professor Ulf Schlichtmann's commitment was invaluable in initiating relations with industry. These relations were vital in order for me to carry out my research with the aim of applicability.

Furthermore, I would like to thank all the colleagues at the institute for the great time I had there and especially the colleagues of the timing group, Christoph Knoth, Bing Li and Walter Schneider. Our discussions and their contributions and friendly attitude helped me immensely.

As this work is closely related to the industry, I would like to thank the involved persons working for Infineon AG. I am especially thankful to Harald Kinzelbach for helping me out with excellent ideas and knowledge about the industrial environment and Klaus Koch for the collaboration regarding the implementation of the proposed method as an in-house tool.

Finally, I want to express my gratitude towards my family and especially towards my fiancée, Ann, for giving me their love and support.

## Contents

| 1 | Intr | Introduction                             |                                       |    |  |  |  |

|---|------|------------------------------------------|---------------------------------------|----|--|--|--|

|   | 1.1  | State-                                   | of-the-Art                            | 3  |  |  |  |

|   |      | 1.1.1                                    | Deterministic Static Timing Analysis  | 3  |  |  |  |

|   |      | 1.1.2                                    | Technology Data                       | 9  |  |  |  |

|   |      | 1.1.3                                    | Statistical Statistic Timing Analysis | 13 |  |  |  |

|   | 1.2  | Contr                                    | ibutions of this Work                 | 19 |  |  |  |

| 2 | Pro  | Problem Formulation                      |                                       |    |  |  |  |

|   | 2.1  | Delay                                    |                                       | 21 |  |  |  |

|   | 2.2  | Timin                                    | ng Analysis                           | 22 |  |  |  |

|   | 2.3  | Variat                                   | tions                                 | 23 |  |  |  |

|   |      | 2.3.1                                    | Uncertainties in Timing Analysis      | 23 |  |  |  |

|   |      | 2.3.2                                    | Process Variations                    | 24 |  |  |  |

|   |      | 2.3.3                                    | Physical Parameter Variation          |    |  |  |  |

|   |      | 2.3.4                                    | Statistical Parameters                | 27 |  |  |  |

|   | 2.4  | Waveform Relevance and Suitable Modeling |                                       |    |  |  |  |

|   | 2.5  | Integr                                   | ration into Industrial Context        | 37 |  |  |  |

| 3 | Wa   | veform                                   | Based Timing Analysis                 | 39 |  |  |  |

|   | 3.1  | Model                                    | ling                                  | 39 |  |  |  |

|   |      | 3.1.1                                    | Waveform Model                        | 40 |  |  |  |

|   |      | 3.1.2                                    | Driver Model                          | 40 |  |  |  |

|   |      | 3.1.3                                    | Receiver Model                        | 41 |  |  |  |

|   | 3.2  | Wavef                                    | form-Based Nominal STA                | 41 |  |  |  |

|   | 3.3  | Paran                                    | neter Variations                      | 42 |  |  |  |

|   |      | 3.3.1                                    | Linear Modeling of Variations         | 42 |  |  |  |

|   |      | 3.3.2                                    | Statistical Variations                | 43 |  |  |  |

|   | 3.4  | Path-l                                   | based Analysis                        | 44 |  |  |  |

|   |      | 3.4.1                                    | Single Stage Analysis                 | 44 |  |  |  |

|   |      | 3.4.2                                    | Sensitivities from SPICE Simulations  | 49 |  |  |  |

II CONTENTS

|                           |                | 3.4.3                     | Propagation of Variations through a Path                     | 55         |

|---------------------------|----------------|---------------------------|--------------------------------------------------------------|------------|

|                           |                | 3.4.4                     | Lumping of Local Variations                                  | 56         |

|                           | 3.5            | Processing of the Results | 57                                                           |            |

|                           |                | 3.5.1                     | Composition of Arrival Time Variation and Voltage Variations | 58         |

|                           |                | 3.5.2                     | Computation of the Variance with Lumped Parameters           | 58         |

| 4                         | Res            | m sults                   |                                                              | 63         |

|                           | 4.1            | Imple                     | mentation                                                    | 63         |

|                           | 4.2            | Setup                     | of Monte Carlo Analysis                                      | 63         |

|                           | 4.3            | Influe                    | nce and Accuracy of Waveforms                                | 64         |

|                           | 4.4            | Statis                    | tical Results                                                | 65         |

| 5                         | 6 Conclusion   |                           |                                                              | 71         |

| $\mathbf{B}_{\mathbf{i}}$ | bliog          | graphy                    |                                                              | <b>7</b> 3 |

| ${f Li}$                  | ist of Figures |                           |                                                              |            |

## Chapter 1

### Introduction

The history of integrated digital circuits is a history of success as microelectronics pervade the everyday life of modern people. The most important fact for enabling the success of integrated digital circuits is the ability to produce more and more functions on each chip for drastically reduced cost per function. This is only possible by scaling down the dimensions of the basic building blocks – the transistors. With smaller sizes more transistors can be placed on each chip which led to Gordon Moore formulating his famous law in 1965 [Moo65] stating that the number of components on each chip doubles every year. Moore reduced this to every two years in 1975 [Moo75] and this rate is still valid leading to billions of transistors on present chips.

The concept of the Turing Machine [Tur36] is one of the fundaments of machine computation. The Turing Machine is a theoretical concept and was never built as such. It works by reading a character from a tape and depending on this character and the internal state of the machine, the head moves on over the tape, writes to the tape, and the internal state of the machine changes. The Turing Machine is the basis for the theory of Finite State Machines (FSMs). It is stated that every computation can be accomplished by such a Turing Machine and still most fabricated ICs comprise state machines in order to control the computation of the data. One fundamental implication is that the operations are synchronized. The state machine changes states according to a time signal called *clock*. Therefore, the computations of each step have to be finished before the next clock signal and the internal blocks have to meet certain timing constraints.

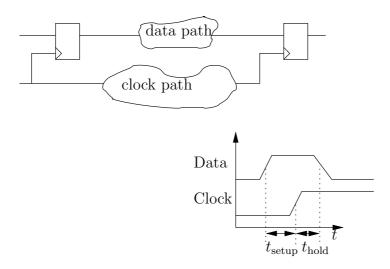

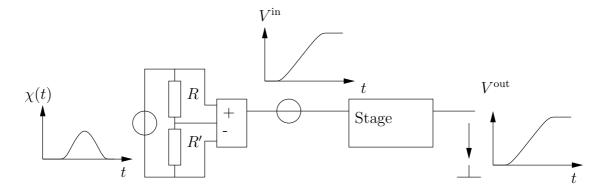

Figure 1.1 shows a common circuit structure comprising a data path, a clock path, and two registers. The data path performs the data computation and is located between two storage elements or registers. The clock signal is transported

Figure 1.1: Combinatorial path between two flipflops

over the clock path to the receiving register. Due to their physical implementation, the registers exhibit two timing constraints. (i) The data through the combinational data path has to arrive by at least the setup time  $t_{\rm setup}$  before the clock edge and (ii) the data signal has to remain stable for at least the hold time  $t_{\rm hold}$  after the clock edge. These two constraints ensure the correct latching of the data in the flipflops.

In order to ensure before fabrication that these constraints are met, timing analysis in different stages of the design is crucial. The focus of this work is the timing analysis for semi-custom digital designs. In this design style, logic gates from a given library are used to implement the required logic functions. The transfer characteristics of the single gates have to be modeled in order to obtain sufficiently accurate estimates for the delay of the entire circuit. As the values of the input signals of the circuit are unknown at this stage, this delay estimate has to be independent of the actual signal value assignments, which is called *static* timing analysis (STA).

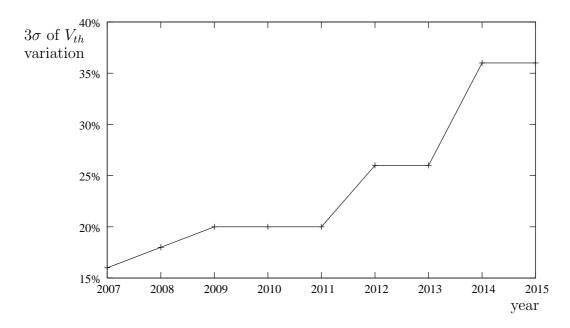

The shrinking of feature sizes causes accuracy problems in the manufacturing process. The physical structures could never be fabricated with infinite accuracy and with smaller physical dimensions, these imperfections have a larger impact on the timing of the circuit. The International Technology Roadmap For Semiconductors (ITRS) [TIT07] contains some information on the expected development of threshold voltage variation as an example. The values of the estimation are displayed in Figure 1.2. The  $3\sigma$  value of the variation of the threshold voltage is expected to rise from 17% in 2007 to more than 35% in 2015. According to the ITRS, the need for novel methods of timing analysis considering these variations is evident. Existing methods of STA have to be extended to consider statistical variations of process

Figure 1.2: Rise of threshold voltage variation.

parameters leading to statistical static timing analysis (SSTA).

#### 1.1 State-of-the-Art

This section gives an overview of the development in the area of timing analysis of digital circuits. It starts from the basic approach to static timing analysis, covers the methods used in industry today and ends with the latest publications of the research community. The first subsection deals with the development of deterministic STA. The second part introduces more process related publications, where the origins, statistical metrology (measurement, characterization, and modeling [SFS<sup>+</sup>99]) and implications of process variations are discussed. The third part shows the various statistical extensions to deterministic static timing analysis in a mainly chronological order.

#### 1.1.1 Deterministic Static Timing Analysis

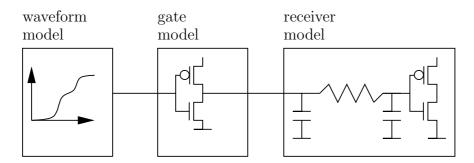

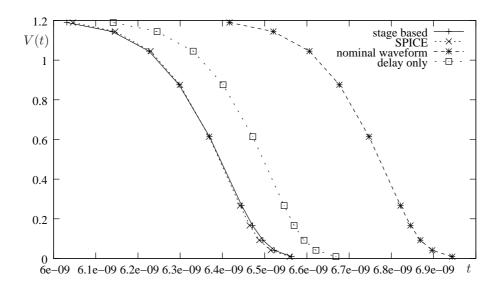

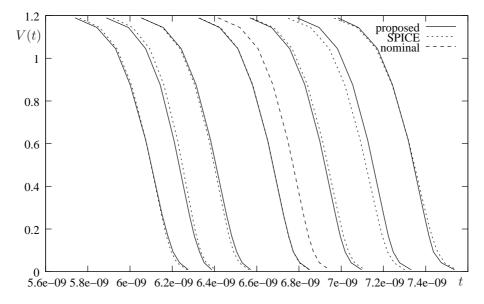

Figure 1.3 shows the three main problems which can be identified for timing analysis:

1. Waveform modeling: The waveform has to be described in a way that is compatible with the gate model. Starting with just the arrival time, current industrial tools also model the slope. Methodologies proposed in research literature model the shape of the waveform as well.

Figure 1.3: Three essential models for timing analysis

- 2. Gate modeling: The gate model describes the timing characteristics of a single cell considering the input waveform and the output load. The development progressed from a fixed delay to a load dependent delay, further to the consideration of slope and, latest, the shape of the waveform. Since the first linear models proved insufficient, nonlinear analytical models as well as look-up tables were used to capture nonlinear dependencies.

- 3. Receiver modeling: The receiver or load of a gate consists of the interconnect and all connected gates in the fanout. The entire receiver structure has to be modeled with compatibility to the gate model. The most common modeling is to use a single capacitor, while the value of this capacitor can be computed in various different ways. Only recently, these single capacitances became insufficient and are replaced by more complex structures.

An overview of the literature dealing with these three problems, waveform modeling, gate modeling, and receiver modeling is given in the following. In the beginning of static timing analysis, only the arrival time is propagated through the circuit in a path-based or block-based manner. Fall delays and rise delays are considered separately but the impact of different slopes or loads is neglected. The author of [Hit82] describes how the delay of combinational blocks between memory elements must meet certain timing constraints. The delay must not be too large or too small, otherwise the resulting data can not be successfully captured by the memory elements at the end of the combinational block. Further, the two basic procedures for traversing a circuit are described: Path enumeration and block-based analysis.

Path enumeration works by starting from a particular start point and traversing the circuit backwards until a primary input or other terminal node is reached. This method is very accurate and can detect and eliminate paths which can never be sensitized. However, this method suffers from the high number of possible paths through a circuit and thus, high computational effort. The second option, block-based traversal, starts at primary inputs or the output of memory elements. All elements to which this starting point is connected to by signals are processed and for each element the earliest and latest arrival times for the output signal is computed. Doing so, the output arrival time of each element is computed only once. The way of proceeding through all elements is adopted from the *Project Evaluation and Review Technique* (PERT). The block-based method is significantly faster than the path-based approach but tends to be pessimistic. Because the logic function of the gates are neglected, specific paths cannot be excluded from the analysis. Thus, paths which would not affect the arrival time at the output – as these paths are not sensitized – would influence the outcome of the analysis possibly leading to a later arrival time.

In order to incorporate the load of the connected cells in the fanout, analytical models were proposed. According to [Sap04], one of the first approaches models the gate delay as a linear function of the purely capacitive output load:  $D = k_1C_L + k_2$  with gate delay D and output capacitance  $C_L$ . Due to the factor k in the linear expression, this model and later models enhancing this basic analytical delay model are called k-factor models. One of these enhancements was introduced in [HJ87] where the authors proposed a method to also incorporate the dependence of the input slope to the gate delay. The authors show an analytical solution for the CMOS inverter output response to an input voltage ramp instead of the step response. The delay of a gate is expressed by the step response delay plus a correction term. This correction term is linearly dependent on the input transition time. Hence, the influence of the input transition time can be considered in the computation of the delay of the inverter [WE93].

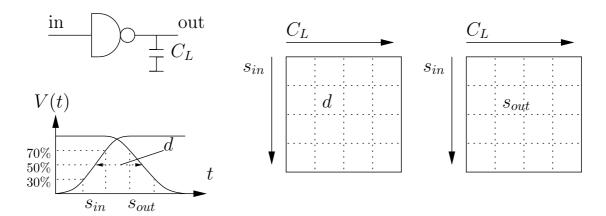

A major problem for this delay model is the nonlinearity of the relationship between input transition time, load capacitance and delay. To capture this nonlinearity, an empirical approach evolved, which uses look-up tables. The values for gate delay and output transition time are stored dependent on load capacitance and input transition time. This delay model is called *Nonlinear Delay Model (NLDM)* as the nonlinear functions are represented by the look-up tables. The table structure is depicted in Figure 1.4. The entries of the tables as well as the input capacitance of each library cell are obtained during library characterization.

Using these tables, a combinational circuit consisting of cells from the previously characterized library can be analyzed with high efficiency. Starting at a primary input the input transition time is known as the input signal is known. The output

Figure 1.4: Look-up tables for deterministic STA. The tables store delay d and output slope  $s_{out}$  depending on input slope  $s_{in}$  and output load  $C_L$

load is composed of the input capacitances of the receiving gates and the equivalent capacitance of the interconnect. With this data, the values for the gate delay and the output transition time can be read from the tables. The delay is added to the arrival time at the input and the result is the arrival time at the output. Thus, the previously described block-based traversal of the circuit is extended by the dependency of the input slope to the gate delay and the slope of the signals are propagated through the circuit together with the arrival time.

With scaling down feature sizes, increasing interconnect resistances and decreasing gate capacitances lead to inaccurate results when assuming purely capacitive load at the output [DMQP94]. However, the complex interconnect structures are reduced to a single effective load capacitance in order to use the existing analytical or table-based methods. In [QPP94] the authors address this problem and describe how the resistance of interconnects become more relevant as the length of connected lines does not scale down with feature sizes as the density is growing. Once the wire resistance reaches the values of gate resistance, a significant part of the load capacitance is shielded from the driving gate. Thus, the delay of the driving gate will be smaller as the gate can not "see" the full capacitance. As a solution to this problem the authors propose the incorporation of a resistance model into the computation of the effective capacitance. Mapping the effects of resistive shielding to the effective capacitance allows the further usage of k-factor models.

The effects of resistive shielding on arrival time and slope is captured but the underlying mechanism is still not addressed: Due to the increased resistance of the interconnect, the signal waveforms show long "tails" at the end of a signal transition. Such waveforms differ significantly from the ramp based model as it is used during

propagating slope and arrival time. With shrinking feature sizes to the nanometer region, however, this deviation from the ramp based model induces unacceptable inaccuracies to the results of timing analysis [KL01]. It is crucial to refine the modeling of the waveforms and thus to consider a wider range of different waveform shapes. Besides the inaccuracy induced by overly simplistic driver models, a second effect concerning the receivers gained importance. The input capacitance of a gate shows increasingly nonlinear behavior. The main cause for that is the Miller effect. The gate capacitance of the transistors depends on the drain voltage and as the drain voltage changes during the switching of the cell, the input capacitance changes as well.

An enhancement is needed which models the waveform more accurately and considers nonlinear effects in the receiver model but is also compatible to established NLDM in order to be applicable in the industry without changing the entire timing concept. Two slightly different extensions of the NLDM were introduced as  $Composite\ Current\ Source\ Model\ (CCSM)$  and  $Effective\ Current\ Source\ Model\ (ECSM)$ . ECSM was first introduced by [KL01] proposing to replace each gate by a current source. The current is modeled by a piecewise linear function with one turning point at  $V_{th}$  of the output voltage separating the saturation mode from the linear mode of the transistors. The gate model consists of the current source parallel to a linear resistor and parallel to an internal capacitance for small load capacitances. The capacitance values are chosen to match library timing data at any operating point in the look-up tables depending on  $s_{in}$  and  $C_L$ .

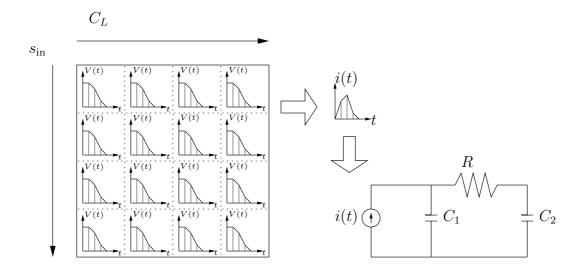

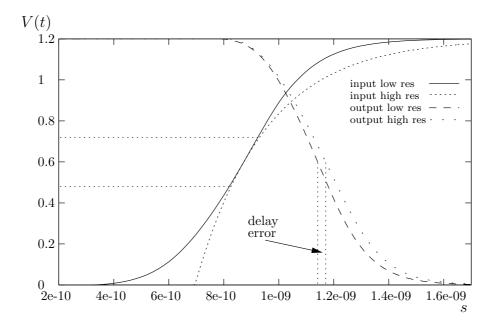

The meaning of ECSM changed slightly as a new ECSM was developed [Kez06]. Load-slope look-up tables are still in use but now for each combination of load and slope a time-voltage waveform is stored as depicted in Figure 1.5. During STA, for a specific effective output load and an input slope the time-voltage waveform is retrieved from the tables. This waveform is then converted to a current waveform and applied to the complex interconnect structure. Solving this system yields the arrival time and slope at the input of the next gate. In order to account for the Miller effect, the receiver gates are modeled by a variable capacitor.

The second extension to NLDM is CCSM which differs only slightly from ECSM. Instead of time-voltage waveform, CCSM stores time-current waveforms. This results in a different library characterization but the general STA procedure is equal to the procedure using ECSM.

Figure 1.5: Look-up tables for different waveforms depending on input slope and output load and  $\pi$ -model driven by a current source.

Figure 1.6: Current source model comprising a voltage controlled current source and intrinsic capacitance

In [HYO04] the authors introduce equivalent waveforms. The equivalent waveform is a waveform with a different arrival time than the original waveform but with a standard shape. This equivalent waveform produces the same output waveform as the original input waveform. The use of only standard shapes simplifies the consideration of waveform dependencies. This approach is not used widely by research or industry.

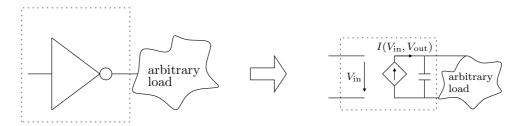

Another approach with different modeling and without compatibility to NLDM is the Current Source Model (CSM) (see Figure 1.6). The output current is still stored in look-up tables and instead of current waveforms, the static current depending on  $V_{\rm in}$  and  $V_{\rm out}$  is stored. These values are obtained by a DC sweep during library characterization. The input signal for one cell is known as well as the initial value of the output voltage. For each time step of the input transition, the current into the receiver model can be retrieved from the look-up table. Solving the appropriate differential equation yields the voltage waveform at the input of the following

gate.

The different approaches for CSM differ in the additional elements in the gate model. The authors in [CW03] propose to use a voltage-controlled current source (VCCS) and a constant, intrinsic capacitance. This intrinsic capacitance is used to reflect the effects of parasitic capacitances in the gate. The capacitance value is determined by matching the output signal of the model to the output signal of a transient simulation on transistor level.

In [KTV04] the CSM is enhanced by capturing the Miller effect, using an additional capacitance between the input and output nodes of a gate. Introducing crosstalk into current source models was shown in [KTV04] and also the more detailed modeling of the receiver. A further improvement was described in [FNP06] using an additional capacitance between the input node and ground and in [NP06] the authors describe a CSM method not storing the current in the tables but the derivatives of the current with respect to time. These values are dependent on input voltage and output load. Using these values the output current is progressively computed by numerical integration. The authors state that their model is superior as it reflects the effects of the parasitic capacitances more accurately.

Apart from the current source models, the authors in [ADI03, ADI05] model the waveform using the Weibull function. It is an exponential expression with two parameters resembling typical waveforms. The two parameters can be interpreted as slope and shape parameters. Look-up tables are used to propagate the Weibull parameters through the circuit.

Another timing methodology based on HSPICE simulation of individual cells was proposed in [CM06]. Not the entire waveform but only the delay and the transition time are propagated.

#### 1.1.2 Technology Data

The aim of all the methods described above is to analyze the timing properties of a given circuit for a set of fixed device parameters. However, these parameters deviate from their intended values due to manufacturing imperfections. This section gives an overview of the published literature on the topic of technology data and manufacturing variations.

Variation can be classified into global and local variations. Global variations affect each device on one die equally, i. e. all devices on one die have the same pa-

rameter values but different values to devices on other dies. Local variations affect each device differently.

In the design of digital circuits, global variations can be considered by corner case analysis. The set of parameters which causes the worst timing result, e.g. the largest delay of a data path, is determined and the design is tweaked until the timing constraints are met assuming that worst-case corner. As this approach is relatively uncomplicated, the focus of the following is more on local variations.

In contrast to digital circuits, where the influence of absolute values of parameters are dominant, in analog circuit design the values relative to others are more significant than their absolute values. One example is the ratio of the widths of two transistors in a current mirror. The deviation from the intended ratio is called mismatch. These relative values are not affected by global, i.e. perfectly correlated, variations but by local variations. Therefore, local variations became an issue in analog circuit design much earlier than in digital circuit design.

One example for a publication from the analog domain dealing with mismatch is [LHC86]. The authors present measurement data from a  $3\mu$ m CMOS process with excluded influence of global variation showing more than 11% relative standard deviation  $\sigma_{V_{th}}/V_{th}$  of the threshold voltage of a p-channel MOS transistor. This value is for the smallest transistor investigated and it is shown that the relative standard deviation depends linearly on  $1/\sqrt{LW}$ , where L and W is the transistor length and width respectively.

The influence of local variations on the delay of digital paths was examined in [EBSLM97]. The influence of threshold voltage variation on gate delay was determined for a  $0.5\mu \rm m$  CMOS process resulting in a relative standard deviation of up to 5%. This value falls below 1% for larger transistors and higher ratio of supply voltage and threshold voltage  $V_{DD}/V_{th}$ . The effect on the path delay was investigated by a test structure of a 24 bit carry select adder. The relative standard deviation of the delay of a path of four gates was measured as up to 10% for a  $0.5\mu \rm m$  process using the lowest threshold voltage and the smallest transistors. This value rose up to 15% for a  $0.35\mu \rm m$  process. The projection of gate delay variation shows the rise from 5% for a  $0.5\mu \rm m$  CMOS process up about 15% for a  $0.18\mu \rm m$  process. Further, it was shown that local variations have most impact on designs with many critical paths with small logic depth, e.g. in highly pipelined circuits.

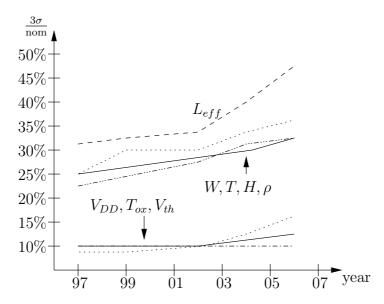

Also the author in [Nas00, Nas01] shows the trends and sources of process vari-

Figure 1.7: Technology parameter variation [Nas00] for device parameters ( $L_{eff}$ ,  $T_{ox}$ ,  $V_{th}$ ) and wire parameters ( $W, T, H, \rho$ )

ability and how intra-die variations gain importance in the future. The author shows numbers for the  $3\sigma$  value relative to the nominal value. The variation of  $V_{th}$  is shown to rise from 10% in 1997 for 250nm to 15% in 2006 for 70nm. Besides this moderate increase, the development of the variation of other parameters is considered being more dramatical. The variation of the effective channel length rises from 30% to 45% in the same time range. The contribution of devices (34%) and wires (66%) to the overall delay variation is specified as well as the impact of device and wire parameters on delay. It is shown that the wire parameters have a significant share of the overall delay variation of 66%.

In [BKN<sup>+</sup>03] the authors present measurement data showing the larger variability in operating frequency of manufactured chips due to process variations. The  $3\sigma$  value of the  $V_{th}$  variation is stated as 30mV causing a 30% variation in the chip operating frequency. It is also shown that lowering  $V_{th}$  and the logic depth increases the performance but also increases the variability of the delay of the entire chip. The authors in [OMC<sup>+</sup>00, OMC<sup>+</sup>02] show measurements from a 180nm process revealing a large intrachip  $L_{gate}$  variation of 10% in average causing a variation of the delay of the critical path of up to 17%. The authors claim further, that the variation of the gate length is rather systematic spatial than random. Thus, the actual value of the gate length depends on the location of the gate on the die and the proposed method to consider this effect is to use different values of the gate length for each gate depending on the location after placement.

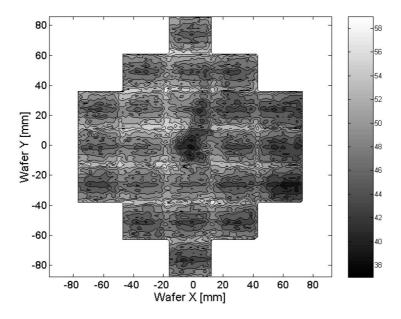

Figure 1.8: A CD contour map as the average over all measured wafers [CS03a]

[CS03a] shows measurements of critical dimension (CD) done by electrical measurements or scanning electron microscopy. The different scales of systematic variation is described. The given CD contour map of measured data is reprinted in Figure 1.8. The contour map is obtained by computing the average of the measurements on all wafers at the positions on the map. The systematic variation of the CD can be seen by the spatial dependence inside each die and also over the entire wafer.

Similar countour maps for a 130nm process are given in [FCC<sup>+</sup>05] and the problem of modeling spatial correlations is addressed. The authors propose a piecewise linear function of the correlation coefficient depending on the distance. [Kuh07] provides some data of variations of the threshold voltage down to 45nm stating an increase of the standard variation  $\sigma$  from 25mV for 130nm to 45mV for 45nm. The author also proposes a way of simulating the effect of random dopant fluctuation on the threshold voltage. He uses a three-dimensional numerical model with an adaptive local meshing scheme. The results showed a significant deviation from the measurements indicating room for process improvement.

The effect of non-rectangular gate (NRG) for a 65nm process is discussed in [SBS<sup>+</sup>07]. NRG is caused by the distortion of the light as the optical wavelength of 157nm is much larger than the minimum feature size. The authors point out that

this effect mainly influences the off-current of the transistor which can deviate up to 20X. This causes a large deviation of the leakage current. The on-current on the other hand is only deviated by up to 5%. In [YLNC08] the authors mention the increasing impact of NRG on the threshold voltage and describe the integration of this effect together with line edge roughness and random dopant fluctuation into a standard SPICE environment avoiding complex atomistic simulations.

Possible improvements to deal with the increasing influence of process variations are classified in [BBC<sup>+</sup>08, BBC<sup>+</sup>07]. The authors note that the basis of improvements is the statistical metrology. This measurement and modeling of process variations generates data which is crucial for the further operations. The metrology data can be handed over in two different directions: The process and equipment control on one hand and to the circuit design in the other hand. The latter aims for a design which is robust to process variations called design for manufacturability (DFM). "A core need is variation impact analysis, particularly tools that can utilize richer representations of process variations, such as statistical timing analysis with spatially correlated process variations" [BBC<sup>+</sup>08]. The state of the art of this topic will be the focus of the next section.

#### 1.1.3 Statistical Statistic Timing Analysis

Due to unavoidable variations in the fabrication process, the parameters of the circuit elements deviate from their nominal value. Most of these deviations are random variations which can be described by a probability density function (pdf). The traditional way of dealing with these variations is to model the pdfs by intervals formed by the extreme points of the distribution. The points in the process parameters space which lie on the extreme value of every parameter are referred to as corners. The worst-case corner shows the worst combination of extreme points. Therefore, it used to be sufficient to show that the circuit works for the worst-case corner in order to show that it works for all other corners.

For long data paths between two registers, the slowest case for the data path and the fastest case for the clock path is the worst case as a setup time violation can be caused if the data signal does not arrive at the receiving register early enough before the clock signal. For short data paths on the other hand, the worst case is the fastest case for the data path and the slowest case for the clock path as a hold time violation occurs if the data signal of the next clock cycle arrives at the receiving register before the previous data has been latched properly. Regardless wether it is the slowest or the fastest case, the most problematic corner is always referred to

as worst-case. The process parameters will not exceed the worst-case parameter set and thus all chips will meet the timing specifications. This concept works well if the process parameters on one die are perfectly correlated, i.e. all devices are in the worst-case corner if one device is in the worst-case corner.

However, with increasing relevance of within-die (i.e. uncorrelated, local) process parameter variations, the delay of the worst-case corner will be overestimated which can be overly pessimistic [SSB05] if the worst-case is the slowest case or even optimistic if the worst-case is the fastest case. If the worst-case is the slowest case, meeting the constraints at the overly pessimistic worst-case corner implies spending a substantial amount of time and area and loosing power efficiency without much benefit. If it is vice versa, the timing constraints could be violated even though the timing check passed. In addition to that, the number of corners in the process parameter space rises exponentially with the number of process parameters. Therefore, it becomes increasingly difficult to determine the worst-case corner.

First attempts to reduce pessimism is the consideration of within-die variations by an on chip variation factor (OCV). The OCV contributes to the fact that the influence of local variations declines for longer paths. Thus, different factors are multiplied on path delays depending on the length of the path. It became clear, however, that process variations need to be considered statistically and that the traditional concepts of timing analysis had to be changed to incorporate the statistics of the parameters. This leads to statistical static timing analysis (SSTA). The random variation of process parameters leads to a variation of gate delays and further to variation of signal parameters such as arrival time and slope. These random variations can be described by pdfs.

First publications on SSTA model gate delays as discrete pdfs [LCKK01, Nai02] or piecewise linear pdfs [DK03]. The statistical information has to be propagated through the circuit. Therefore, two basic operations need to be executed: The arrival time at the input of a cell has to be added to the delay of the cell and as both quantities are random variables, a statistical add function has to be available. While the add function is straightforward, the second operation can become cumbersome: If a gate has more than one input, the statistical maximum has to be computed by a max function. The problem arises if the two input signals are not independent because they share common gates in their path or the process parameters of the gates in the paths are not independent. The problem with dependency is the computational complexity: Each combination of samples of the pdfs on which the two input signals depend has to be considered. The number of combinations rises

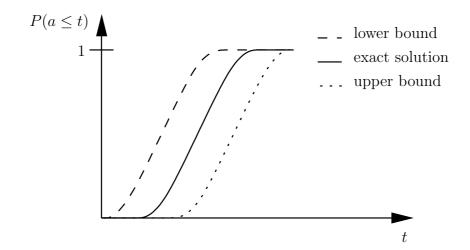

Figure 1.9: Upper and lower bounds of the cdf of the arrival time a

exponentially in the number of dependent pdfs, e.g. common gates of two paths, causing prohibitive computational complexity.

Therefore, instead of computing the exact pdfs, bounds were introduced and it was proven that these bounds are never exceeded. [OK02] describes how to derive the joint probability distribution of the delay of a number of paths. The authors describe a way to obtain upper and lower bounds for the distribution of the maximum of the path delays in order to get an estimate on the circuit delay distribution. [OB04] and [WO06] show how to obtain bounds for N most critical paths using stochastic majorization. In [ABZV03b] the authors propose a block-based method to obtain bounds on the circuit delay. The computation of these bounds is based on neglecting some of the inputs or assuming independence between the arrival times. In [ABZV03a, AZB03] the same method as before is used for obtaining the bounds which are then refined by selective enumeration, i.e. the exact computation of some most significant nodes. The use of Bayesian networks is proposed in [BVB05] in order to obtain bounds for the pdf of the circuit delay. The authors in [JKN<sup>+</sup>03, JKN<sup>+</sup>06] show how to find the yield, i.e. the probability that the timing constraints are met by three different ways: 1) Dividing the feasibility region, which is the area in the process parameter space which satisfies timing constraints, into rectangles and integrate the jpdf inside the rectangles, 2) finding the maximal ellipsoid inside the feasibility region and integrate over the volume of that ellipsoid and 3) using tightness probability as in [VRK<sup>+</sup>04] (see below).

On the one hand, it seemed too complex to compute the exact pdf of a circuit and on the other hand, it was observed, that most process variations can be modeled by Gaussian distributions with sufficient accuracy. As Gaussian distributions are fully described by the mean value  $\mu$  and the standard deviation  $\sigma$ , it is sufficient to consider only these two characteristics of the random variables. In addition, it was assumed to be sufficient to model the gate delay as a linear function of transistor parameters. This is used in [GNDL01] in a path-based approached, where the nmost critical paths are obtained from STA and the sensitivities of the path delay with respect to the process parameter variations are obtained. With this information and assuming Gaussian random variables, the distribution of the path delay can be computed. The linear assumption leads to a simple representation of the arrival times in a circuit by weighted sums of process parameter variations referred to as canonical sums. In [ABZ03] this form is used and a method is proposed to compute the addition and bounded maximum operation of two of these canonical sums in order to propagate the canonical sums through the circuit. [CS03b] describes how an estimate of the maximum of two canonical sums can be computed using the work of [Cla61]. In [OYO03] the authors describe in more detail how to obtain the sensitivities for all relevant values of input slope and output load. The representation of the transfer function of an interconnect structure in a canonical form is shown in [AFP06] and [AFP07].

Using the canonical form solves the problem of reconvergent fanouts: The representation as a sum of random variables keeps track of all variables from previous gates. If two signals reconverge, the canonical sums of their arrival times show common variables. With this information the correlation between the two arrival times can be obtained and used for the computation of the maximum. Besides the problem of reconvergent fanouts, the problem of correlated process parameters still remains open. The random variables used in the canonical form have to be independent. If the process parameters are correlated, i. e. not independent, these parameters have to be transformed into a set of independent variables.

Principle Component Analysis (PCA) can be used to decorrelate random variables. For Gaussian random variables uncorrelatedness also implies independence (see Section 2.3.4). The PCA itself is described in [HKO01] while the application to obtain a linear sum of process parameters is shown in [CS03b, CS05b]. A more detailed description of the application to die-to-die and wafer-to-wafer variations and the description of a constraint PCA can be found in [CKK<sup>+</sup>08].

For non-Gaussian random variables, PCA can not be used as uncorrelatedness does not imply independence. A more complex transformation of a set of random variables into a set of independent random variables is Independent Component

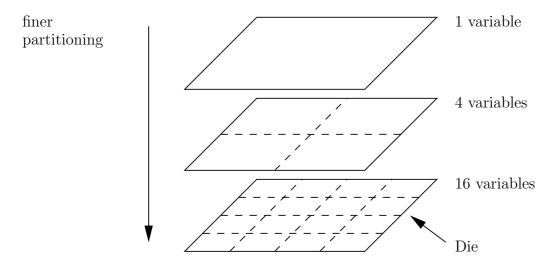

Figure 1.10: Quad-tree partitioning of the die to model spatial correlations [ABZ03].

Analysis (ICA), which is also described in [HKO01] and applied in [SS06] and [SS08]. ICA was developed to separate different sources, e.g. audio signals, from a linear mixture. The basic principle is the reduction of the Gaussianity of the output signals because a mixture of two random variables is always more Gaussian than the original signals. ICA can be applied only on non-Gaussian random variables.

Apart from the transformation of the original random variables into independent variables, other methods exist to obtain a sum of independent random variables more directly. One such method for obtaining a canonical form representing correlated delays is a quad-tree model [ABZ03]. Figure 1.10 shows how several layers are used to partition the die into rectangles with lower layers showing a finer granularity of the partitioning. One independent random variable is assigned to each rectangle. Each parameter of a device on the die is represented by a sum of the random variables which are assigned to the rectangles in which this particular device is located.

In a similar way the die can be divided into a grid [CS03b, CS05b, CS05a, KS05, SSA+05]. Besides quad-tree and grid-based models, correlations can also be modeled by distance-dependent functions. In [FCC+05] a linear function was proposed, but in [LWA06, XZH07a, XZH07b] it is shown that the resulting assumed covariance matrix is not positive semidefinite and thus lacks the property of a covariance matrix. Thus, a methodology is proposed to obtain a nonlinear spatial correlation function and a correlation matrix from measurement data. In [LTCC08] a set of polynomials is used as spatial correlation function using Singular Value Decomposition and Polynomial Fitting. The property of the correlation matrix being positive semidefinite is obtained by a post-processing step. To overcome the problem of

modeling the spatial correlation, the authors in [ISNM08] propose a Monte Carlo based approach. In their work, a vector of sampled delays for each gate is used for SSTA.

Using the linear canonical form, the addition of two arrival times or delays is a straightforward addition of the appropriate coefficients. For the maximum operation some of the authors use the analytical expression of Clark [Cla61] to compute the moments of the maximum. A simpler approach to estimate the maximum of two arrival times is to linearize the max function. In [VRK+04, VRK+06] the authors introduce the idea of tightness probability and use it as factors of the canonical form. The tightness probability is defined as the probability that one signal arrives earlier than the other signal:  $P(a_1 < a_2)$ . Wherein  $a_1$  and  $a_2$  are the arrival times of the two signals. The linear expression for the arrival time o at the gate output is then:  $o = P(a_2 < a_1)a_1 + P(a_1 < a_2)a_2$ . An extension to this linear approach is presented in [ZCHpC06] where the authors propose to estimate the nonlinearity of the max function at the current gate and keep a tuple of the input arrival times if this estimate of the nonlinearity is above a certain threshold.

The assumption of linear influence of process parameters on gate delay is discussed controversially and some authors claim that linear modeling is too inaccurate. In order to enhance the accuracy of the linear model, higher order timing models were introduced: [LLGP04] shows how to represent a circuit performance f of an analog or digital circuit by a transfer function of linear time invariant (LTI) system. The cumulative density function (cdf) and probability density function (pdf) can then be approximated by the step response and impulse response of the LTI system, respectively. In [CZNV05] an additional term is introduced in the canonical form, which captures nonlinear dependencies to process parameters. [ZCH+05, ZCH+06] offer a quadratic gate delay model and the according atomic operations add and max. A similar quadratic gate delay model is proposed [ZSL+05] but in addition to that, also a quadratic wire delay model and a slightly different max operation is shown. Apart from these polynomial models, [CC05, CC07] proposes an analytical model for the gate delay and [BVGC06] enhances it by using Karhunen-Loève Expansion to model the spatial correlation between transistor parameters.

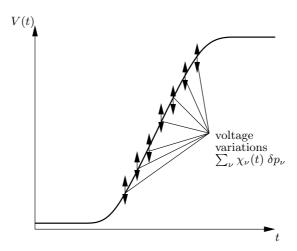

All methods mentioned above model only the delay and in some cases the slope. With downscaling feature sizes, however, this simplification of the waveforms leads to unacceptable inaccuracies of SSTA. Thus, similar as in the deterministic case, recent publications propose the application of current source models to SSTA: [FNP06] uses Markov chains to model the variations of the voltages at the output. The authors of

[ZXA<sup>+</sup>07] model the variation of the waveform by basic operations like time shift, time scale, voltage shift and voltage scale. The parameters of these basic operations are then considered as random variables and propagated through the circuit in a block-based manner. In [GV08] a variational current source gate model is proposed but it remains unclear how the variation of the input signal propagates to the output.

Another wide field of research using the results of SSTA is the optimization of circuits by altering design parameters. As this is not the main focus of this work, only the work in [LLCP08] shall be mentioned. The authors describe a method of finding the arcs of the timing graph which are best suited to be optimized, i.e. upor downscaled in order to improve the maximal frequency or the parametric yield.

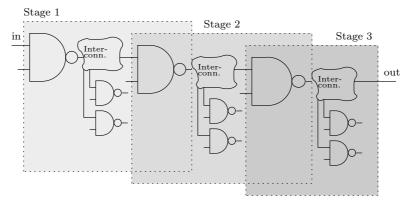

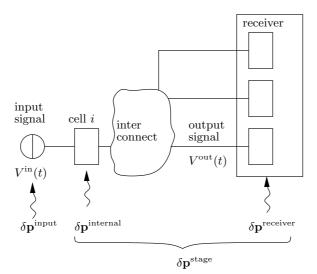

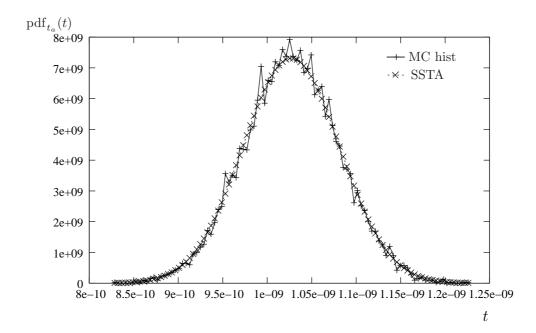

#### 1.2 Contributions of this Work

This work provides a novel path-based method for variational analysis of digital integrated circuits. The method works on a netlist of a particular path of a digital design, which includes all extracted parasitics after the layout. The intention is to build a highly accurate and reliable reference tool for SSTA. Therefore, higher runtimes are accepted, even though these runtimes inhibit the use as a tool for timing sign-off. The method extends an existing industrial tool, which provides the functionality of deterministic timing analysis, the partitioning of a path into separate stages and the determination of the critical path. This work adds the functionality of statistical analysis to this tool.

Different to existing methods, the entire waveform resulting from analog simulations as well as the complete interconnect structure and the dynamic load of the fanout are considered. The result is the information of the variation of the voltage at a number of points on the waveform at the output of a path. More precisely, the influence of each transistor parameter on the voltage at each specific point is available. This information can be used to compute the probability of violating the timing constraints or the optimization of the circuit to change the influence of specific parameters. The results show that the accuracy of the proposed method is comparable to analog Monte Carlo simulation but with a considerably shorter execution time. The method was implemented as an in-house reference tool at a leading manufacturer of integrated circuits with the need for evaluating available sign-off tools. The following publications resulted from this work: [SLS+07, SKS08c, SKS08b, SKS08a]

## Chapter 2

## **Problem Formulation**

#### 2.1 Delay

The main characteristic of digital circuits is the processing of two distinc signal states referred to as True/False, 1/0, On/Off or  $V_{dd}/V_{ss}$  depending on the abstraction level. The specification, which should be fulfilled by the circuit, can be represented by a logic function. The logic function consists of basic operations, e.g. NAND, NOR, etc., and each of these basic operations is represented by one logic gate in the circuit. Each gate has a specified number of inputs and most gates have one output. The gate library is the collection of all available gates and the optimal partitioning of the logic function to basic operations has to be found.

The gates are built of transistors which realize the basic functionality of switches. These switches connect or disconnect two circuit nodes and thereby control the flow of electrons, i.e. charge, depending on the signal value of the control pin, i.e. the gate, of the transistor. The transistor gates and various other parts of the physical implementation shown capacitive behavior. These capacitors have to be (dis-)charged whenever the signal value changes. This requires the transportation of charge through the transistors. The transported amount of charge per time and thus, the required time to (dis-)charge the capacitors depends on the physical properties of the transistors, e.g. threshold voltage or resistance in the on-state.

The delay of a logic gate is defined as the time from when the input signal crosses half the voltage swing,  $(V_{dd} - V_{ss})/2$ , to when the output signal crosses half the voltage swing. The gate delay depends on the physical properties of the transistors as well. Not only gates but also interconnects cause delay, which is defined similarly to the gate delay. The next section describes the problem of finding the delay of an entire circuit, given the delay of the individual logic gates and interconnects.

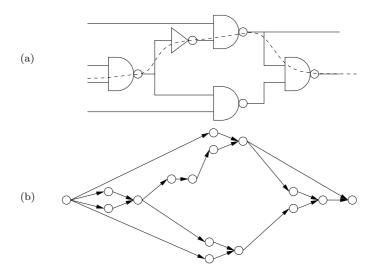

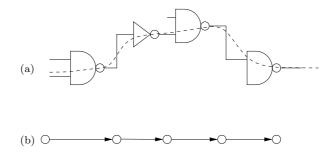

Figure 2.1: Example circuit (a) and corresponding timing graph (b)

#### 2.2 Timing Analysis

The subject of timing analysis is to obtain the total delay of a circuit. An example circuit is shown in Figure 2.1(a). The circuit is represented by a timing graph which is a directed, acyclic graph (DAG)  $\mathcal{G} = (N, E, n_s, n_f)$  as in Figure 2.1(b) [Hit82]. N denotes the set of nodes, E the set of edges,  $n_s$  the source node and  $n_f$  the sink node. The nodes represent primary input and output pins or the input and output pins of the gates. The edges represent the delay between the nodes, which can be either the gate delay or the interconnect delay.

The procedure of deterministic static timing analysis (STA) is to propagate the timing information through the timing graph in order to obtain the arrival time at the sink node  $n_f$ . Let  $p_i$  be a path in  $\mathcal{G}$ , represented by an ordered set of edges from the source node  $n_s$  to the sink node  $n_f$ . An example path is shown in a dashed line in Figure 2.1. The methodology proposed in this work is intended to serve as a verification tool to evaluate commercially available timing tools. Therefore, the analysis is confined to particular paths  $p_i$ . The path delay is not the delay of the entire circuit, but the result can be compared to the results of the path analysis of other tools. In addition, the proposed method enables the accurate analysis of special paths which are critical for the design.

In the following, the gate delay is merged with the interconnect delay, as it is analyzed in the same step and the two are physically closely related. The resulting timing graph for the example path from Figure 2.1 is shown in Figure 2.2.

2.3. VARIATIONS 23

Figure 2.2: Example path (a) and corresponding timing graph (b)

The timing information is now propagated from the source node  $n_s$  to the sink node  $n_f$  through the path. Thus, the only operation which is needed is the transfer of timing information through one node. The operation for merging two or more incoming edges is not necessary in this path-based approach.

#### 2.3 Variations

#### 2.3.1 Uncertainties in Timing Analysis

During timing analysis of digital circuits, uncertainties arise from three different directions:

- 1. modeling and analysis errors: The modeling of devices and interconnects is based on simplifications, which cause inaccuracies. Also timing tools which employ these models possibly induce further errors.

- 2. variations in the manufacturing process: Parameters of devices and interconnects show die-to-die and within-die variations.

- 3. variations in the operating conditions: Supply voltage and temperature are examples of operating conditions which are subject to variations and influence the timing characteristics of the circuit.

The first influence occurs during the design process. During logic synthesis, buffer insertion, and place and route, timing analysis is performed. However, at each stage different inaccuracies are introduced due to effects such as undetected false paths, error in the cell delay, error in the extraction of interconnect parasitics, SPICE models, etc. All these effects cause the result of the timing analysis to be close to reality but not perfectly matched.

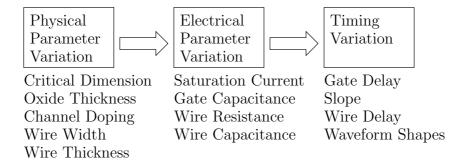

Figure 2.3: Variation of physical parameters causes variation in electrical parameters, which causes variation in timing parameters [BCSS08].

The next influence is due to process limitations or equipment imprecision. This influence is the main focus of SSTA and thus it is described in more detail in Section 2.3.2 below. Variations in operating conditions are especially relevant for circuits designed to operate in changing environments, e.g. mobile or automotive applications. Supply voltage and temperature influence the performance of a circuit and therefore, these influences have to be accounted for during the design. These variations in operating conditions are usually captured by corner-case margins, as each individual chip has to work properly under all temperature and supply voltage conditions.

#### 2.3.2 Process Variations

With scaling feature sizes down to the nanometer region, it becomes harder to achieve accurately manufactured chips. Parameters that show variation caused by manufacturing inaccuracies can be classified into three categories:

- 1. physical parameters,

- 2. electrical parameters, and

- 3. performance or timing parameters.

The influence of physical parameters on electrical parameters and further on performance parameters is shown in Figure 2.3. The variation of physical parameters are due to various effects including chemical mechanical polishing (CMP). CMP is used to planarize insulating oxides and metal lines. Other effects are the optical proximity effect, which causes inaccuracies in structures which are smaller than the wavelength of light used in the lithography and lens imperfections in the optical system. Due to these and other effects, the parameters of devices and interconnects, such as gate length or critical dimension (CD), gate-oxide thickness, channel doping concentration, interconnect thickness and width, etc., show a substantial amount of

2.3. VARIATIONS 25

variation.

The electrical characteristics of a device such as driving current or input capacitance depend on the physical parameters of the device. Thus, the variations of the physical parameters causes a variation of the electrical parameters. And, further, performance or timing parameters, e.g. delay, slope, or more complex quantities, in turn depend on the electrical parameters and the timing or performance parameters show variation as well caused by the variation of the electrical parameters.

It is important to note that more than one electrical parameter depends on a single physical parameter. For example, the wire resistance and capacitance both depend on the wire width and are thus correlated. The worst-case for wire resistance would mean a thin wire while the worst-case for the wire capacitance would mean a thick wire. Thus the worst-case for the wire delay – worst-case resistance and capacitance – is physically impossible. This shows how important it is to correctly consider the correlation between the electrical parameters.

Besides the three classes of parameters described above, a fourth class of parameters is introduced as model or  $transistor\ parameters$ . These are the parameters of the device models, e.g. BSIM4.3. They can be either physical parameters like channel length offset xl, electrical parameters like threshold voltage  $vth\theta$  or parameters which are derived from physical and electrical parameters, e.g. electrical gate equivalent oxide thickness toxe. Most tools operate on these model parameters and therefore, in the following mainly model parameters are used.

#### 2.3.3 Physical Parameter Variation

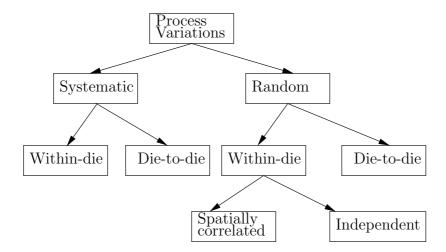

The classification of physical parameter variation can be based firstly, on whether the variation is systematic or random or secondly based on the spatial range, i.e. long-distance or short-distance effects. The classification is shown in Figure 2.4.

1. Systematic variations are deterministic variations caused by well-understood physical effects. Systematic variations of physical parameters are mainly due to optical proximity effects, CMP and the associated metal fill. Since these effect are layout-dependent, they can be considered once the layout is finished. Thus, the consideration of systematic variations is possible at the end of the design process especially for timing sign-off. However, there is a need to include systematic effects into the analysis of earlier stages of the design when the

Figure 2.4: Classification of physical parameter variations [BCSS08].

layout is not available. Therefore, systematic variations are also considered statistically even though they occur due to deterministic effects.

2. Random variations are purely random variations of the process parameters. Before manufacturing, only the statistical characteristics are known and therefore, these variations have to be modeled by random variables. Examples for random variations are line-edge roughness (LER) and random dopant fluctuations (RDF).

Besides the classification into systematic and random variations, the variations can be classified according to the spatial characteristics.

- 1. Die-to-die variations (global, inter-die variations) affect each device on one die equally. This can be caused by a non-uniform etch concentration, which causes CD variation. The concentration might be different in the center of the wafer than on the edge causing a gradient in the CD. This gradient doesn't cause significant variation on one die but variation from one die located in the center of the wafer to another die which is located on the edge of the wafer. Other sources can be misalignment of the stepper carrying the lithography masks or a drift of the intensity of the laser. The spatial range of die-to-die variations could be further expanded to wafer-to-wafer, lot-to-lot, and fab-to-fab variation.

- 2. Within-die variations (local, intra-die variations) influence each device on the die differently. The CD of one transistor might be smaller than the CD of the transistor in close proximity to the first one.

2.3. VARIATIONS 27

Within-die random variations can be further classified into correlated and independent parameter variations. Within-die systematic variations can not be independent as they would be classified as random variations in that case. The reasons and implications of correlations are explained in the following section.

#### 2.3.4 Statistical Parameters

#### Distribution of a Random Variable

This section describes the mathematical basis for the description of statistical parameters by random variables. The notations are derived from [HKO01] and more detailed information can be found in [Pap91]. Each statistical parameter s can be described by a random variable and is characterized by its *cumulative density function* (cdf)  $F_s(s)$ . The cdf shows the probability that the value of this parameter is below a certain threshold  $s_0$ :

$$F_s(s_0) = P(s \le s_0) \tag{2.1}$$

For continuous random variables the cdf is a non-negative, nondecreasing continuous function. The values of  $F_s$  lie in the interval  $0 \le F_s(s) \le 1$  and the limits are  $F_s(-\infty) = 0$  and  $F_s(+\infty) = 1$ . Another way of describing the distribution is the probability density function (pdf) of a parameter s. The pdf is obtained as the derivative of the cdf:

$$p_s(s_0) = \frac{dF_s(s)}{ds} \bigg|_{s=s_0} \tag{2.2}$$

The pdf can also be computed from a known pdf using the inverse relationship

$$F_s(s_0) = \int_{-\infty}^{s_0} p_s(\xi) \ d\xi \tag{2.3}$$

For simplicity F(s) is used instead of  $F_s(s)$  and p(s) instead of  $p_s(s)$  when no confusion may arise.

Assume now that  $\mathbf{s} = (s_1, s_2, \dots, s_n)$  is a random vector with the continuous random variables  $s_1, s_2, \dots, s_n$ . The generalized form of the cdf becomes

$$F_{\mathbf{s}}(\mathbf{s_0}) = P(\mathbf{s} \le \mathbf{s_0}) \tag{2.4}$$

and the pdf can be obtained by

$$p_{\mathbf{s}}(\mathbf{s_0}) = \frac{\partial}{ds_1} \frac{\partial}{ds_2} \dots \frac{\partial}{ds_n} F_{\mathbf{s}}(\mathbf{s}) \bigg|_{\mathbf{s}=\mathbf{s_0}}$$

(2.5)

The distribution of two different random variables  $s_1$  and  $s_2$  can be described by the joint cumulative distribution function (jcdf)

$$F_{s_1, s_2}(s_{1_0}, s_{2_0}) = P(s_1 < s_{1_0}, s_2 < s_{2_0}) \tag{2.6}$$

Similarly to Equation 2.2, the *joint probability density function (jpdf)* can be defined by differentiating the jcdf  $F_{s_1,s_2}$  with respect to both variables  $s_1$  and  $s_2$ . Thus, Equation 2.3 can be written as

$$F_{s_1,s_2}(s_{1_0},s_{2_0}) = \int_{-\infty}^{s_{1_0}} \int_{-\infty}^{s_{2_0}} p_{s_1,s_2}(\xi,\eta) \, d\eta \, d\xi \tag{2.7}$$

Integration of the jpdf  $p_{s_1,s_2}(s_1,s_2)$  over the variable  $s_2$  leads to the marginal density  $p_{s_1}(s_1)$  of  $s_1$  and vice versa for  $p_{s_2}(s_2)$ :

$$p_{s_1}(s_1) = \int_{-\infty}^{\infty} p_{s_1,s_2}(s_1,\eta) \, d\eta \tag{2.8}$$

$$p_{s_2}(s_2) = \int_{-\infty}^{\infty} p_{s_1,s_2}(\xi, s_2) d\xi$$

(2.9)

#### **Expectations and Moments**

In most cases, the exact pdf of a model parameter s is unknown. The only data available are measurements from the production process. With this data expectations and higher order moments can be estimated. The expectation of a random variable s is defined by

$$E\{g(s)\} = \int_{-\infty}^{\infty} g(s) p_s(s) ds \qquad (2.10)$$

The expectation can be estimated from measurements  $g(s_j)$  by

$$E\{g(s)\} \approx \frac{1}{K} \sum_{j=1}^{K} g(s_j)$$

(2.11)

In the case of g(s) = s Equation (2.10) describes the first moment or mean of the random variable

$$\mu_s = E\{s\} = \int_{-\infty}^{\infty} s \, p_s(s) \, ds \tag{2.12}$$

and the estimated mean value can be obtained by

$$\hat{\mu}_s = \frac{1}{K} \sum_{j=1}^K s_j \tag{2.13}$$

Higher order moments can be centered by subtracting the mean from the random variable. The centralized second moment is called variance and is defined by

$$\sigma_s^2 = E\{(s - \mu_s)^2\} \tag{2.14}$$

2.3. VARIATIONS 29

Considering more than one variable, vector notation for  $\mathbf{s}$  is more convenient. The second moment of pairs of elements in  $\mathbf{s}$  is called *covariance* and given by

$$c_{s_i,s_j} = E\{(s_i - \mu_{s_i})(s_j - \mu_{s_j})\}$$

(2.15)

When no confusion can arise, the notation  $c_{s_i,s_j}$  may be simplified to  $c_{i,j}$  and for other variables respectively. The covariances of all statistical parameters  $s_i$  are put together to form the covariance matrix

$$\mathbf{C_s} = E\{(\mathbf{s} - \mu_{\mathbf{s}})(\mathbf{s} - \mu_{\mathbf{s}})^T\}$$

(2.16)

The elements of the covariance matrix normalized by their variances are called *correlation coefficients*

$$\rho_{i,j} = \frac{E\{(s_i - \mu_{s_i})(s_j - \mu_{s_j})\}}{\sigma_i \sigma_j}$$

(2.17)

Combining the correlation coefficients into a matrix yields the *correlation matrix*  $\mathbf{R_s}$ . The correlation matrix is symmetric ( $\mathbf{R_s} = \mathbf{R_s}^T$ ) and positive semidefinite ( $\mathbf{a}^T \mathbf{R_s} \mathbf{a} \leq 0$ ). Further, the eigenvalues of  $\mathbf{R_s}$  are real and non-negative, all eigenvectors of  $\mathbf{R_s}$  are real, and it is always possible to find mutually orthonormal eigenvectors.

#### Uncorrelatedness and Independence

The elements of a random vector are uncorrelated if the following condition holds for the covariance matrix  $C_s$ :

$$\mathbf{C_s} = E\{(\mathbf{s} - \mu_{\mathbf{s}})(\mathbf{s} - \mu_{\mathbf{s}})^T\} = \mathbf{D}$$

(2.18)

with the diagonal matrix

$$\mathbf{D} = \operatorname{diag}(c_{1,1}, c_{2,2}, \dots, c_{n,n}) = \operatorname{diag}(\sigma_{s_1}^2, \sigma_{s_2}^2, \dots, \sigma_{s_n}^2)$$

(2.19)

For the special case of two random variables  $s_1$  and  $s_2$ , the condition leads to the fact that their covariance  $c_{1,2}$  is zero

$$c_{1,2} = E\{(s_1 - \mu_{s_1})(s_1 - \mu_{s_2})\} = 0 \tag{2.20}$$

or equivalently

$$E\{s_1s_2\} = E\{s_1\}E\{s_2\} \tag{2.21}$$

It is important to note that the correlation coefficient does not capture the complete relationship between two random variables. In order to completely describe the relationship or dependence copulas are needed. Only for special cases like the Gaussian distribution, the correlation coefficient describes the entire dependence between two random variables.

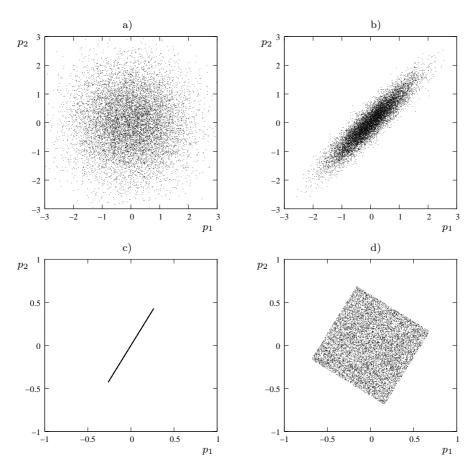

Figure 2.5 shows distributions of two random variables  $p_1$  and  $p_2$ . a) and b) show two Gaussian random variables which are a) uncorrelated and b) correlated. Note that the correlated variables are closer to a line through the center. c) and d) show two uniformly distributed random variables. In c) they are perfectly correlated and in d) the two variables are uncorrelated but not independent. These two random variables in d) are obtained by rotating two independent random variables  $s_1$  and  $s_2$ :

$$\begin{bmatrix} p_1 \\ p_2 \end{bmatrix} = \begin{bmatrix} \cos \alpha & -\sin \alpha \\ \sin \alpha & \cos \alpha \end{bmatrix} \begin{bmatrix} s_1 \\ s_2 \end{bmatrix}$$

(2.22)

with an arbitrary rotating angle  $\alpha$ .

In general, uncorrelatedness does not imply independence of two random variables [Pap91]. Two random variables  $s_1$  and  $s_2$  are independent if and only if

$$p_{s_1,s_2}(s_1,s_2) = p_{s_1}(s_1)p_{s_2}(s_2)$$

(2.23)

The jpdf  $p_{s_1,s_2}(s_1,s_2)$  must factorize into the product of their marginal densities  $p_{s_1}(s_1)$  and  $p_{s_2}(s_2)$ . Two independent random variables satisfy the following condition:

$$E\{g(s_1)h(s_2)\} = E\{g(s_1)\}E\{h(s_2)\}$$

(2.24)

Comparing to (2.21) it can be seen, that independence is much stronger than uncorrelatedness and that uncorrelatedness only considers the second moment while independence considers all moments. This aspect becomes especially interesting when dealing with Gaussian random variables which are introduced in the following.

#### Gaussian Random Variables

In this work, it is assumed that model parameters can be modeled by Gaussian random variables with sufficient accuracy. Therefore, some details of the Gaussian distribution are highlighted in the following. The n-dimensional vector  $\mathbf{s}$  of random variables is said to be Gaussian if the pdf of  $\mathbf{s}$  has the form

$$p_{\mathbf{s}}(\mathbf{s}) = \frac{1}{(2\pi)^{n/2} (\det \mathbf{C_s})^{1/2}} \exp\left(-\frac{1}{2} (\mathbf{s} - \mu_{\mathbf{s}})^T \mathbf{C_s}^{-1} (\mathbf{s} - \mu_{\mathbf{s}})\right)$$

(2.25)

For just one single variable s this simplifies to

$$p_s(s) = \frac{1}{\sqrt{2\pi}\sigma} \exp\left(-\frac{1}{2} \left(\frac{s - \mu_s}{\sigma}\right)^2\right)$$

(2.26)

2.3. VARIATIONS 31

Figure 2.5: a) uncorrelated Gaussian variables b) correlated Gaussian variables c) perfectly correlated uniformly distributed variables d) uncorrelated but not independent uniformly distributed variables (see Equation (2.22))

Gaussian random variables have some special properties which make the assumption of Gaussianity attractive:

- 1. The distribution is completely described by only first and second moments. If the mean value  $\mu_s$  and the standard deviation  $\sigma_s$  is known, the entire distribution can be obtained. This becomes an advantage in SSTA if it is assumed that signal arrival times are Gaussian as well. In which case, only the values for  $\mu$  and  $\sigma$  of the arrival time have to be propagated through the circuit in order to compute a distribution of the arrival time at the output.

- 2. Gaussianity is preserved under linear operations. If  $\mathbf{x}$  is a Gaussian random vector and  $\mathbf{y} = \mathbf{A} \mathbf{x}$  a linear transformation, then  $\mathbf{y}$  is also Gaussian with mean vector  $\mu_{\mathbf{y}} = \mathbf{A} \mu_{\mathbf{x}}$  and covariance matrix  $\mathbf{C}_{\mathbf{y}} = \mathbf{A} \mathbf{C}_{\mathbf{x}} \mathbf{A}^T$ . This property is useful if linear sensitivities of timing quantities to transistor parameters are sufficient to achieve an acceptable accuracy. The transistor parameters can be modeled as Gaussian random variables and the timing characteristics like arrival time, slope or others will also remain Gaussian, which results in the advantages of the first property.

- 3. The third property regards the uncorrelatedness and geometrical structure of the Gaussian distribution. As mentioned earlier, the first and second moment are sufficient to describe the Gaussian distribution. If two Gaussian variables are uncorrelated according to Equation (2.21), Equation (2.23) holds as well and thus, both variables are independent.

Any non-diagonal covariance matrix  $C_s$ , i.e. correlated random variables, can always be written in the form

$$\mathbf{C_s} = \mathbf{E} \,\mathbf{D} \,\mathbf{E}^T = \sum_{i=1}^n \lambda \,\mathbf{e}_i \,\mathbf{e}_i^T \tag{2.27}$$

where **E** is an orthogonal matrix with columns  $\mathbf{e}_1, \mathbf{e}_2, \dots, \mathbf{e}_s$  being the n eigenvectors of  $\mathbf{C}_s$  and  $\mathbf{D} = \operatorname{diag}(\lambda_1, \lambda_1, \dots, \lambda_n)$  being the diagonal matrix comprised of the eigenvalues  $\lambda_i$  of  $\mathbf{C}_s$ . Applying the rotation **E** to the centered vector s

$$\mathbf{u} = \mathbf{E}^T(\mathbf{s} - \mu_{\mathbf{s}}) \tag{2.28}$$

then yields a vector  $\mathbf{u}$  of uncorrelated and hence independent Gaussian random variables.

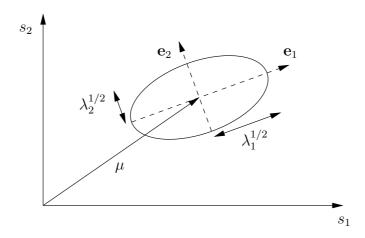

The eigenvectors  $\mathbf{e}_i$  and eigenvalues  $\lambda_i$  of  $\mathbf{C}_{\mathbf{s}}$  can be interpreted geometrically as in Figure 2.6. All points on the jpdf with constant value  $(p_{\mathbf{s}}(\mathbf{s}) = \text{const})$

2.3. VARIATIONS 33

Figure 2.6: Geometric illustration of a two dimensional Gaussian distribution [HKO01].

form hyperellipsoids centered at the mean value  $\mu_s$ . The principal axes are parallel to  $\mathbf{e_i}$  have the length  $\lambda_i$ . The figure intuitively shows, how a rotation decorrelates the random variables.

Using Gaussian random variables leads to sufficient accuracy of the proposed algorithm and also to a highly reduced complexity. Therefore, in the following Gaussianity is assumed and correlation is used to describe statistical dependence between random variables.

#### Correlations in SSTA

In the following, the implications of correlation for SSTA are highlighted. Correlations can occur between transistor parameters and between timing parameters such as arrival times and also between transistor and timing parameters. Correlations between arrival times can be caused by two effects:

- 1. Spatial correlation denotes correlation of transistor parameters depending on the distance to each other. Especially when systematic variations are modeled as random variables, they often show significant correlation. E.g. a gradient on the wafer leads to similar parameters for neighboring transistors. As the arrival times at the output of the cells are determined by the transistor parameters, these arrival times are also correlated.

- 2. Topological correlations arise when the circuit is analyzed in a block-based manner. If the output of a gate is connected to more than one following gate (fanout), the arrival times of all signals in the fanout cone are dependent on the

first fanout gate. Thus, all of these signals are correlated. The computation of the maximum arrival time at a reconvergence point becomes cumbersome.

As the proposed method is path-based, the problem of reconverging paths does not occur. Therefore, the following focuses on spatial correlations. If two parameters  $s_i$  and  $s_j$  of devices on one die belong to the class of die-to-die variations, they vary equally or in other words, these variables are perfectly correlated ( $\rho_{i,j} = 1$ ). Within-die variations, on the other hand, can be either correlated ( $0 < \rho_{i,j} < 1$ ) or completely independent ( $\rho_{i,j} = 0$ ) as outlined in Section 2.3.3.

In order to capture correlations between parameters, the correlated parameters are represented by weighted sums of independent random variables. Two perfectly correlated parameters are described by one single random variable. If two parameters show arbitrary correlation, two independent random variables are contained in both weighted sums and the weights determine the correlation coefficient between the two parameters. To adapt this to spatially correlated transistor parameters, several methods have been published, which are all compatible with the SSTA method proposed in this paper. The method based on principle component analysis (PCA) and the method based on quad-tree partitioning of the chip will be explained in the following.

If the covariance matrix of the parameters is known and it is assumed that the random variables are Gaussian, PCA can be applied to generate the factors of the weighted sums to represent each correlated parameter as a sum of independent random variables [CS03b]. Let  $\mathbf{z} \sim N(\mathbf{0}, \mathbf{C_z})$  be the vector of correlated Gaussian, zero mean random variables that have to be represented as a weighted sum of the independent, Gaussian, zero mean random variables  $\mathbf{p} \sim N(\mathbf{0}, \mathbf{I})$  where  $\mathbf{C_z}$  is the symmetric and positive definite covariance matrix obtained by an appropriate correlation model.  $\mathbf{C_z}$  can be factored by the Cholesky factorization as

$$\mathbf{C}_{\mathbf{z}} = \mathbf{K} \, \mathbf{K}^T \tag{2.29}$$

For more detailed information refer to [GvL85]. Using the Cholesky root  $\mathbf{K}$  the vector  $\mathbf{z}$  can be represented by

$$\mathbf{z} = \mathbf{K} \,\mathbf{p} \tag{2.30}$$

and **z** will also be Gaussian with mean

$$E\{\mathbf{z}\} = \mathbf{K} E\{\mathbf{p}\} = \mathbf{0} \tag{2.31}$$

and covariance matrix from (2.16):

$$E\{(\mathbf{K}\mathbf{p})(\mathbf{K}\mathbf{p})^T\} = E\{\mathbf{K}\mathbf{p}\mathbf{p}^T\mathbf{K}^T\} = \mathbf{K}E\{\mathbf{p}\mathbf{p}^T\}\mathbf{K}^T = \mathbf{K}\mathbf{K}^T = \mathbf{C}_{\mathbf{z}}$$

(2.32)

2.3. VARIATIONS 35

During the analysis the independent random variables  $\mathbf{p}$  are used and after performing the SSTA, the parameter set  $\mathbf{p}$  can be transformed back to the original set  $\mathbf{z}$ .

A second option was introduced on page 17 and Figure 1.10 as a quad-tree model [ABZ03] where several layers are used to partition the chip into rectangles with lower layers showing a finer granularity of the partitioning. One independent random variable is assigned to each rectangle. Each parameter of a device on the chip is represented by a sum of the random variables which are assigned to the rectangles in which this particular device is located.

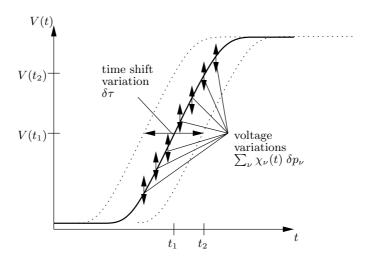

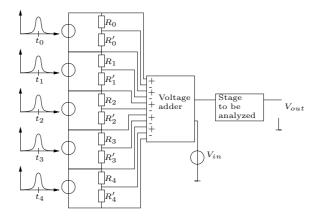

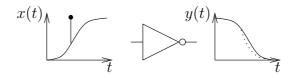

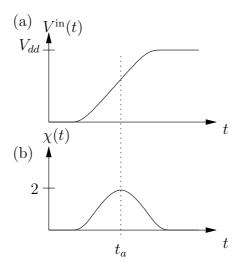

#### Canonical Sum