### Lehrstuhl für Rechnertechnik und Rechnerorganisation der Technischen Universität München

# Live Replication of Paravirtual Machines

Daniel Stodden

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. Hans Michael Gerndt

Prüfer der Dissertation: 1. Univ.-Prof. Dr. Arndt Bode

2. Univ.-Prof. Dr. Uwe Baumgarten

Die Dissertation wurde am 20.03.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 18.07.2008 angenommen.

### **Abstract**

System virtualization has seen largely renewed interest in recent years, primarily due to the emerge of effective virtualization techniques for commodity platforms in both hardware and software.

Beyond improved resource utilization and administration cost, driving past and present adoption in the data center, virtual machines offer a fair degree of system state encapsulation, which promotes practical advances in workload migration, system debugging, profiling and, last but not least, an ongoing "commoditization" in high-availability system design.

This thesis investigates deterministic replay and semi-active replication for system paravirtualization, a software discipline trading guest kernel binary compatibility for reduced dependency on costly trap-and-emulate techniques. Deterministic replay constitutes consistent recovery of system state by reexecuting an original computation from an event log.

The Xen hypervisor, as one major contender of the paravirtualization paradigm, features an abstract I/O model mapped to shared memory and a small set of inter-VM communication primitives. Demonstrably, this contributes much to a balance between a compact machine interface, thereby low overhead, and full application compatibility. However, Xen's overall architecture also promotes a shift from monolithic VMMs to elements borrowing from classic microkernel design.

A primary contribution is evidence that trace capturing under a piecewise deterministic execution model can be added to an abstract but inherently asynchronous, split I/O model for virtual machines without compromising a typical run-time overhead of about 5% reported with monolithic systems. Furthermore, integration into a commodity monitor does not thwart original system design, which suggests that the approach taken remains generally defendable under maintenance cost considerations as well.

# **Acknowledgments**

This thesis was written under the careful supervision of Prof. Dr. Arndt Bode and Dr. Carsten Trinitis. Turning, with an original background in operating systems software research, to availability at the application level, then finally back to system software could not have been done without the support and freedom I received.

I am honored to receive expert's second opinions. Thanks go to Prof. Dr. Uwe Baumgarten for kindly devoting his time and expertise as part of my grading committee.

The Department of Informatics at TU München provided an excellent working environment, without which I doubt that any of my ideas would have come to fruition. This includes Hubert Eichner, Toby Klug, Michael Ott, Max Walter and Josef Weidendorfer at LRR. Thank you all, for occasional coffee, listening and frequent helpful suggestions.

I owe the deepest gratitude to my wife, Xenia, who encouraged and supported me so much over the years.

Last but not least, special thanks go to Jonas, our son, for reminding me ever so often that any OK book needs to have a proper tiger in it.

# **C**ontents

| Intro | oductio | on                                    |

|-------|---------|---------------------------------------|

| 1.1   | Motiv   | ration of the Thesis                  |

| 1.2   | Thesis  | s and Contribution                    |

| 1.3   | Organ   | nization of the Thesis                |

| Bac   | kgroun  | d                                     |

| 2.1   | Real I  | Machines                              |

|       | 2.1.1   | Machine Architecture                  |

|       | 2.1.2   | Microprocessor Trends                 |

|       | 2.1.3   | High-Availability and Fault-Tolerance |

|       | 2.1.4   | Cluster Architectures                 |

| 2.2   | State   | Machines                              |

|       | 2.2.1   | Deterministic Machines                |

|       | 2.2.2   | Coordination                          |

|       | 2.2.3   | Global State Consistency              |

|       | 2.2.4   | Active Replication                    |

|       | 2.2.5   | Facing Non-Determinism                |

|       | 2.2.6   | Semi-active Replication               |

|       | 2.2.7   | Causal Logging                        |

|       | 2.2.8   | Duplicate Output                      |

|       | 2.2.9   | Related Work                          |

| 2.3   | Virtua  | al Machines                           |

|       | 2.3.1   | Machines                              |

|       | 2.3.2   | Virtualization                        |

|       | 2.3.3   | System Virtualization                 |

|       | 2.3.4   | ISA Virtualizability                  |

|       | 2.3.5   | Machine Relocatability                |

|       | 2.3.6   | Piecewise Deterministic VM Execution  |

|       | 2.3.7   | Related Work                          |

|   |     | 3.1.1 Processor                         |

|---|-----|-----------------------------------------|

|   |     | 3.1.2 Memory                            |

|   |     | 3.1.3 I/O                               |

|   | 3.2 | Hardware x86 Virtualization             |

|   | 3.3 | Paravirtual Machine Design              |

|   |     | 3.3.1 Concept                           |

|   |     | 3.3.2 Processor                         |

|   |     | 3.3.3 Memory                            |

|   |     | 3.3.4 I/O                               |

|   |     | 3.3.5 Applicability                     |

|   |     | 3.3.6 Related Work                      |

|   | 3.4 | Taxonomy of Commodity VMs               |

|   | 3.5 | Future Evolution                        |

| 4 | The | Xen Virtual Machine Monitor 71          |

|   | 4.1 | Architecture                            |

|   | 4.2 | Domain Privileging                      |

|   | 4.3 | Machine Interface                       |

|   | 4.4 | Event Virtualization                    |

|   | 4.5 | Split device I/O                        |

|   | 4.6 | Example: Network I/O Virtualization 80  |

|   | 4.7 | Memory Sharing                          |

|   | 4.8 | Supplementary Interfaces                |

| 5 | Xen | /VLS Architecture 85                    |

|   | 5.1 | Processor                               |

|   |     | 5.1.1 Shared Information                |

|   |     | 5.1.2 Non-deterministic Instructions 88 |

|   | 5.2 | Machine Memory                          |

|   | 5.3 | I/O                                     |

|   |     | 5.3.1 Programmed I/O vs. DMA            |

|   |     | 5.3.2 Generalized I/O Ring Protocol     |

|   | 5.4 | Design Considerations                   |

|   | 5.5 | Design Alternatives                     |

|   |     | 5.5.1 Virtual I/O Memory and Protection |

|   |     | 5.5.2 Deferred Processing               |

|   |     | 5.5.3 Deferred Memory Updates           |

|   | 5.6 | SMA Channels                            |

|   |     | 5.6.1 Programming Interface             |

|   |     | 5.6.2 Split I/O Rings                   |

|   |     |                                         |

|   |      | 5.6.3   | Cooperating Frontends                   |

|---|------|---------|-----------------------------------------|

|   |      | 5.6.4   | Memory Sampling                         |

|   | 5.7  | Inter-F | Processor Synchronization               |

|   |      | 5.7.1   | Shared Info SMA                         |

|   |      | 5.7.2   | Grant Table Updates                     |

|   |      | 5.7.3   | Summary                                 |

|   | 5.8  | Event   | Log                                     |

|   |      | 5.8.1   | Context-Sensitive Logging               |

|   |      | 5.8.2   | Cooperative Synchrony                   |

|   |      | 5.8.3   | Transport                               |

|   |      | 5.8.4   | Flow Control                            |

|   |      | 5.8.5   | Trace Data Format                       |

|   | 5.9  | Examp   | ole: SMA-Channeled Block I/O            |

|   |      | 5.9.1   | Implementation                          |

|   |      | 5.9.2   | Maintenance Cost                        |

|   | 5.10 | Evalua  | ation                                   |

|   |      | 5.10.1  | System Configuration                    |

|   |      | 5.10.2  | Linux Kernel Build                      |

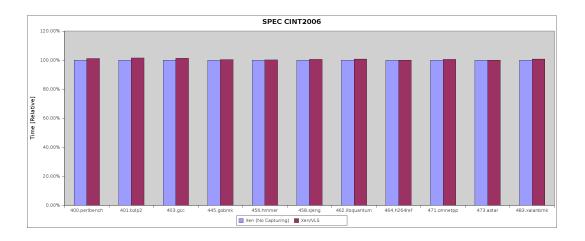

|   |      | 5.10.3  | SPEC CPU 2006                           |

|   |      | 5.10.4  | Anticipated Bandwidth Limitation        |

| 6 | Hard | lware I | nstruction Counting on x86 Machines 145 |

|   | 6.1  |         | d Work                                  |

|   | 6.2  | Perform | mance Monitoring on x86 Processors      |

|   | 6.3  | Impler  | mentation Details                       |

|   |      | 6.3.1   | Interrupt Latency                       |

|   |      | 6.3.2   | Interrupt Interference                  |

|   |      | 6.3.3   | String Instructions                     |

|   | 6.4  | Driver  | Architecture                            |

|   | 6.5  | Perform | mance Impact                            |

|   | 6.6  | Count   | er Quality                              |

|   | 6.7  | Future  | e Work                                  |

| 7 | Con  | clusion | 163                                     |

|   | 7.1  | Summ    | ary                                     |

|   | 7.2  | Future  | e Research                              |

|   |      | 7.2.1   | Time-Travelling Storage Systems         |

|   |      | 700     | 73.54 77 - 1                            |

|   |      | 7.2.2   | DMA Engines                             |

# List of Figures

| 2.1  | Active replication: replicas (R) with frontends (FE) and clients   |    |

|------|--------------------------------------------------------------------|----|

|      | (C) [23]                                                           | 18 |

| 2.2  | Dual redundancy in a leader/follower scheme                        | 19 |

| 2.3  | Agreement in message passing systems                               | 24 |

| 2.4  | Semi-active replication replaces multilateral agreement with uni-  |    |

|      | lateral decisions                                                  | 25 |

| 2.5  | Synchronization and duplicate output with semi-active replication. | 27 |

| 2.6  | Machine decomposition and system interfaces                        | 31 |

| 2.7  | The machine virtualization homomorphism [65]                       | 32 |

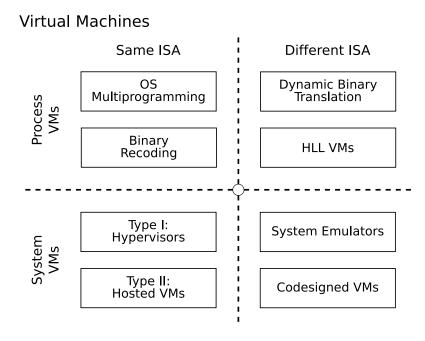

| 2.8  | A virtualization taxonomy.                                         | 33 |

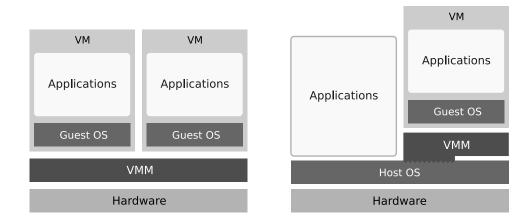

| 2.9  | Type I (Hypervisors) and Type II (Hosted) VMMs                     | 34 |

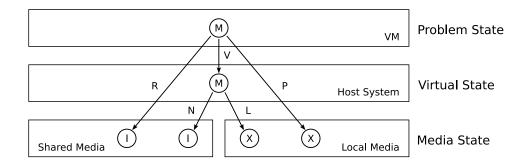

| 2.10 | Migratability of machine resources                                 | 39 |

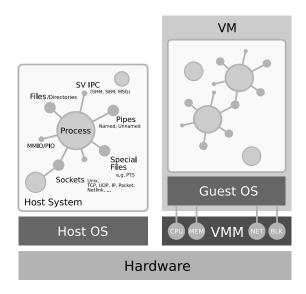

| 2.11 | Resource complexity in OS vs. VM processing environments           | 41 |

| 2.12 | A classification of system calls in the Linux 2.6 kernel           | 44 |

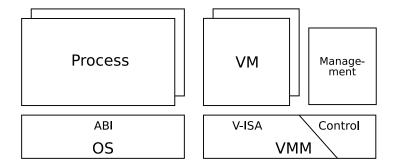

| 2.13 | Control interfaces in virtualization and process management        | 44 |

| 2.14 | Formal requirements for non-deterministic instructions emulation   |    |

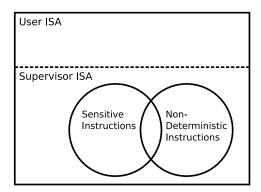

|      | in virtualizable ISAs                                              | 48 |

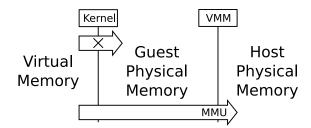

| 3.1  | Virtual and pseudophysical address translation through shadow      |    |

|      | paging                                                             | 58 |

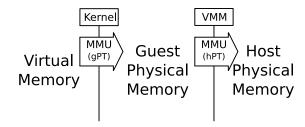

| 3.2  | Address translation with nested paging                             | 61 |

| 3.3  | A present and future taxonomy of commodity system VMMs             | 69 |

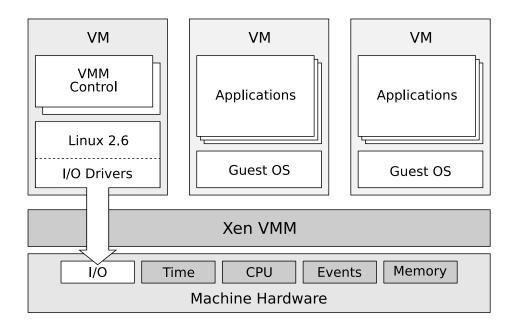

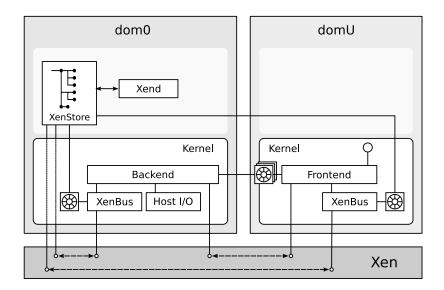

| 4.1  | Xen virtual machine architecture                                   | 72 |

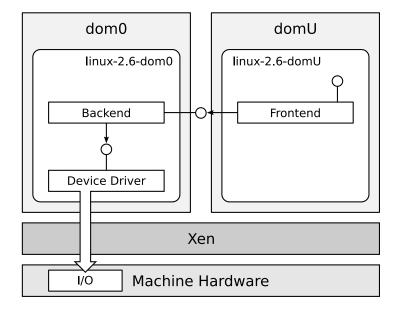

| 4.2  | Xen split driver model on paravirtual Linux guest OS instances.    | 79 |

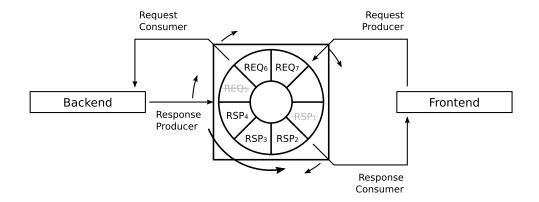

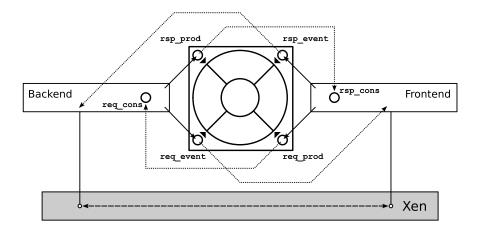

| 4.3  | Message flow in Xen I/O rings                                      | 80 |

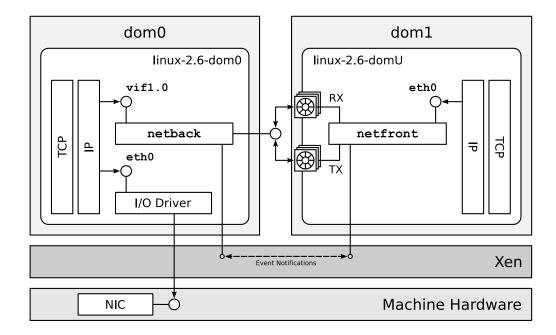

| 4.4  | Xen network virtualization architecture                            | 81 |

| 4.5  | The XenStore directory service                                     | 84 |

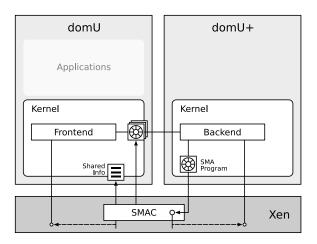

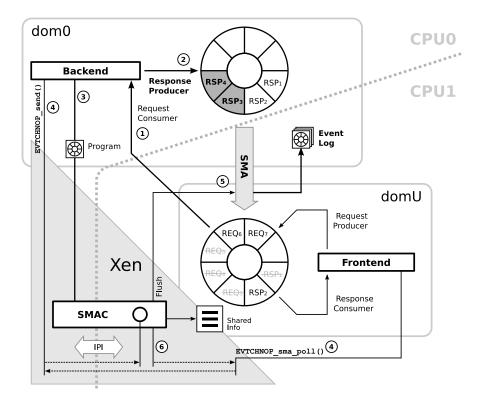

| 5.1  | Data flow between split device drivers in Xen                      | 92 |

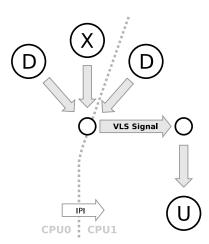

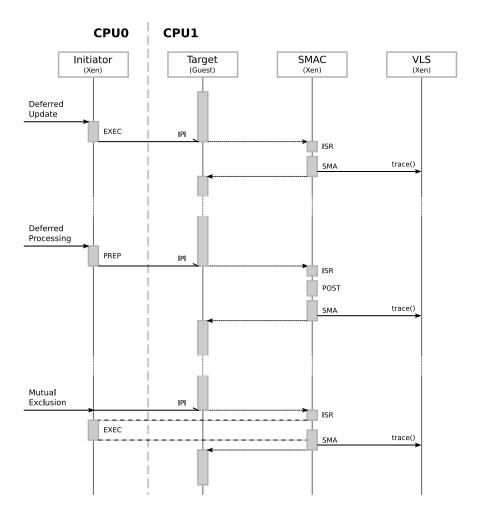

| 5.2  | Inter-processor event migration. VLS signals constitute software   |    |

|      | event processing. Hardware IPIs migrate events across different    |    |

|      | CPUs                                                               | 98 |

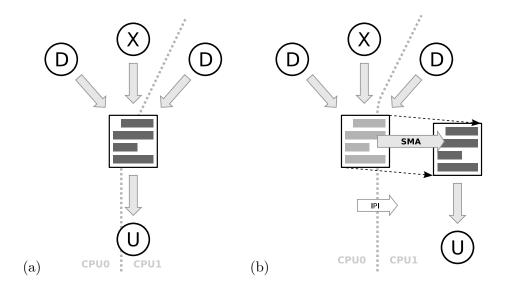

| Original (a) memory accesses in Xen vs deferred, double-buffered         |

|--------------------------------------------------------------------------|

| (b) SMA updates                                                          |

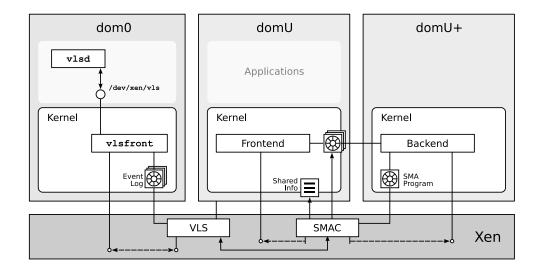

| SMA Channels                                                             |

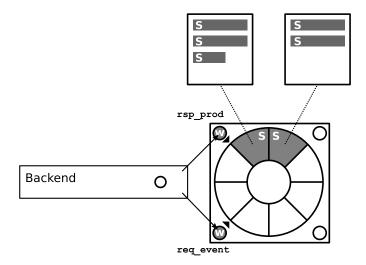

| Split I/O rings, decoupling backends (dom0) from frontends (domU)        |

| entirely                                                                 |

| SMA access in shared I/O rings. (S) indicates memory sampling            |

| on message bodies and bulk data transferred, (w) 32-bit writes           |

| to ring indices                                                          |

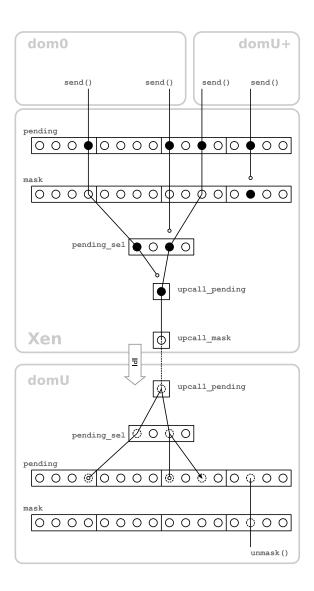

| Event channel activations in Xen                                         |

| Summary of flow control during SMA updates                               |

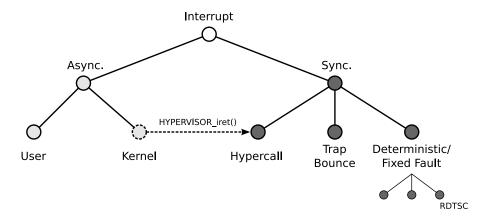

| Events and synchronous control transfers                                 |

| Log transport in Xen/VLS                                                 |

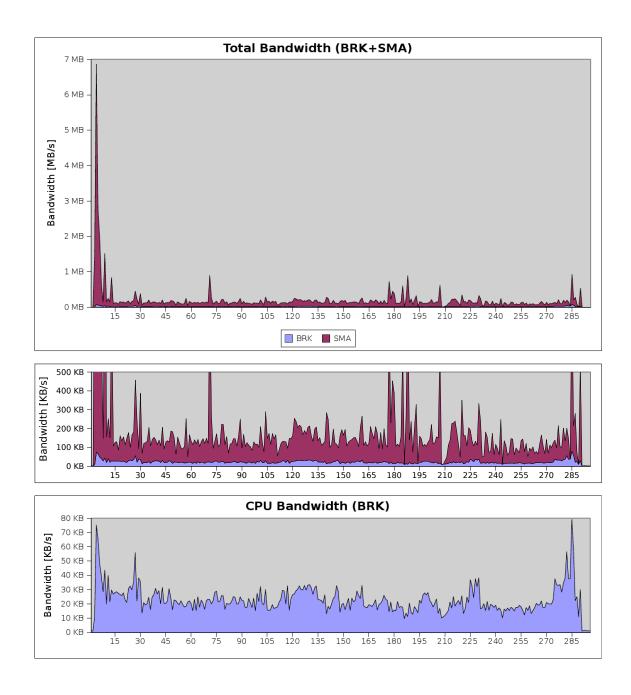

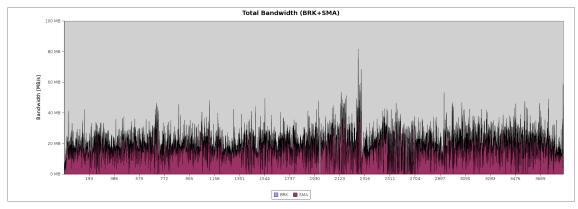

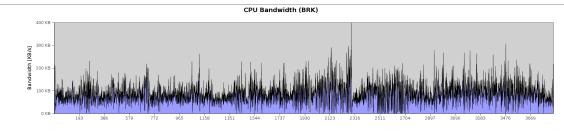

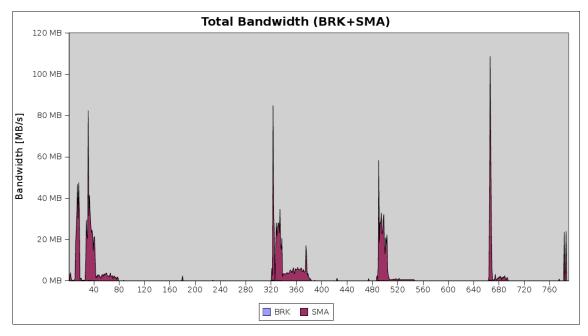

| Trace bandwidth for a Linux 2.6 kernel build (256 MB RAM). $$ . 136      |

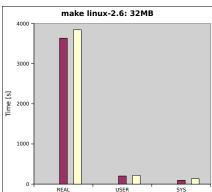

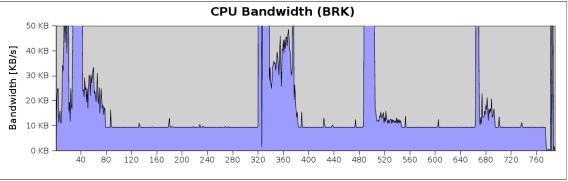

| Trace bandwidth for a Linux 2.6 kernel build (32 MB RAM) $138$           |

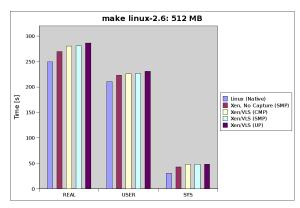

| Relative Performance: Linux 2.6 kernel build 139                         |

| Sample CINT2006 execution trace for 401.bzip2 140                        |

| Relative Performance: SPEC CINT2006                                      |

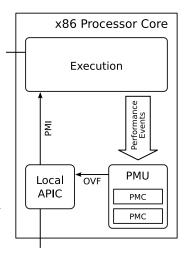

| High-level microarchitectural model of x86 performance monitoring. 149   |

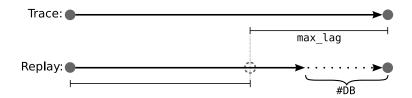

| Construction of an instruction interval in follower mode 153             |

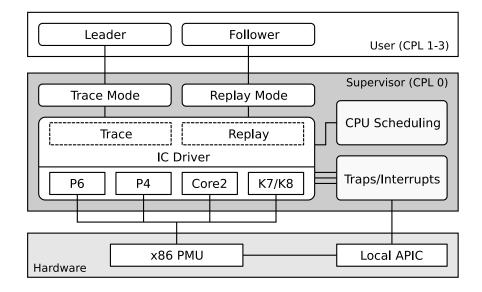

| PMU-based instruction counter architecture for x86 systems $157$         |

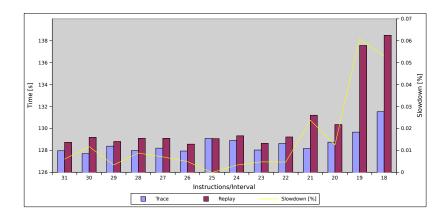

| Performance downgrade by interval length                                 |

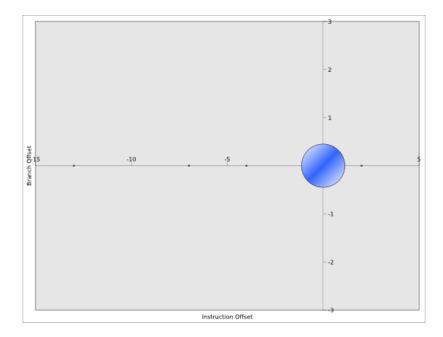

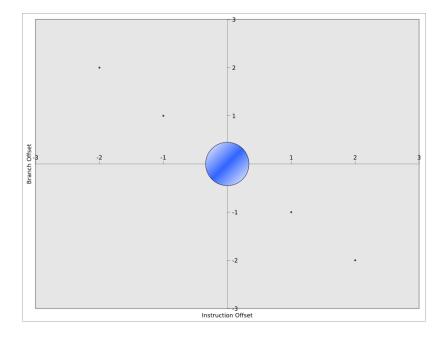

| Branch and instruction counter precision on a Core2 processor $160$      |

| Branch and instruction counter precision on a Pentium M processor. $161$ |

|                                                                          |

### 1 Introduction

Around 2004 to 2005, I was working on project Balance, an academic/industrial research cooperation on high-availability (HA) middleware designs for commodity system platforms. HA middleware systems are software frameworks for highlevel application development in languages such as C/C++ and Java. The term commodity in such systems refers to clustered computer architectures built from comparatively inexpensive, industry-standard processors and I/O components, most notably a shift from switched circuits to packet-switched internetworking. The motivation behind software availability frameworks is that while building highly available applications at any level of a layered system architecture can hardly ever be considered trivial, application programmers willing to let their programs conform to a standardized, component-oriented system design can at least be relieved from dealing with low level details of distributed failure detection and control over redundant software component instances.

In hindsight, considering technical properties and perceivable market adoption, there were multiple lessons to be learned. One is that while such frameworks may reduce the overall cost of developing or porting applications, significant effort remains left in doing so. Another simple truth is that while unwanted system outages represent a widespread phenomenon in everyday computing practice, the development process of few projects today incorporates costly countermeasures at the software level, unless availability considerations by users and customers explicitly require to do so.

This is one reason why *transparent* mechanisms, i.e. those which do not require adaption on the side of system architects, are so attractive. Transparent mechanisms basically derive from two concepts: (a) Execution of computer systems comprises a sequence of states, and (b) fault-tolerance is generally achieved through redundancy. Conceptually, fault-tolerance can be reduced, to some degree, to the problem of replicating system state on independent machines.

Transparent checkpointing exploits this concept by replicating system state without introspection of what distinguishes the state of a *service*, such as the contents of a database, from checkpoints of overall processing state, which comprises an entire program context to roll back and resume from [29]. There are

two common problems which prevent above idea from widespread application on arbitrary (software) systems. One is bandwidth consumption: system state can be large, and peak system memory bandwidth typically exceeds network or storage bandwidth by orders of magnitude [22]. Active replication is one technique known to overcome the first issue to some degree. Instead of passive state transfers, system execution is replicated, regenerating redundant state from. In distributed, message-passing systems, information guiding execution may be regarded as limited to only sequences of input messages processed. Deterministic replay carries the idea of active replication over to a more general system model which, in theory, could be applied to any of the software execution environments common today.

Another issue is consistent recovery of system workloads within an execution environment matching the original one. The basic workload unit managed by users today are operating system processes, or groups thereof. While processes thereby appear as a viable unit of state replication, this is unfortunately not the case. The reason is that while raw software state can always be relocated, in practice it is never self-contained. The rich and complex variety of resource interfaces provided by common operating systems makes this task difficult. More importantly, it will require complex changes to any operating system hosting these environments [29, 27].

System virtualization techniques are almost as old as time-sharing computer systems, but saw largely renewed interest in recent years. Like operating systems, virtual machines (VMs) ultimately host application software. Different from customary OS kernels, workload units carried by system VMs are whole operating systems and processes, multiplexed on a single physical machine instance. Sole domain of expensive mainframe architectures in the past, their renaissance is due to the emerge of effective hardware and software virtualization techniques applicable to popular processors and system architectures. As with the HA architectures mentioned above, another round of technological commoditization emerges.

Until today, the driving forces behind the ongoing adoption of system virtualization remain system consolidation, improved resource utilization and reduced maintenance cost. To ease system maintenance, some server-class system virtualization products soon featured VM migration, with remarkable performance and apparent ease of implementation. In contrast, almost 20 years of prior research in process migration did not yield much impact on any commodity server operating system. The feature demonstrates an important difference to the software environment facilitated by customary operating systems: transparent, fast workload relocatability for host systems sharing a common network segment.

Recovery for highly available system architectures shares similar properties.

Beyond the design of highly-available systems, replayable VM execution has a considerable number of additional potential applications. Starting from an initial system state, replay can recover any intermediate state a given system traversed in a preceding run. Known applications of such facilities include:

- System debugging, such as running applications to a point where an original computation failed. Inspection of not only failure state, but the entire computation which produced it, provides valuable means for failure analysis [20].

- Improved system profiling. Collection of run-time information on systems is a valuable tool in system design and research. However, specific results are often not repeatable if the execution is inherently non-deterministic. Furthermore, capturing detailed system information has usually a notable performance impact and may itself lead to distortion of original phenomenons encountered. Capturing only non-determinism guiding an execution alone may conserve a particular system run with comparatively low distortion. Deterministic replay then makes the task of detailed analysis repeatable [97].

- Enhanced system security. Similar to profiling and debugging, more recent research revealed the benefits of deterministic replay for system security measures [28]. Future system intrusion detection and analysis tool sets might make use of deterministic replay. Similar to debugging, returning to an uncompromised system state, then replaying execution to a point where compromisation took place can provide valuable insight in how attacks were arranged and how they succeeded.

Various virtualization architectures presently exist. Anticipating that the service relocatability achievable with system virtual machines opens a wider spectrum of future applications, this thesis focuses on deterministic replay for one specific virtualization class, called *paravirtualization*. The motivations for this specific virtual machine families is summarized in the following section.

#### 1.1 Motivation of the Thesis

System virtual machines allow for multiple guest operating systems to share a common hardware platform. They are implemented by virtual machine monitors (VMMs) mapping the execution of a guest system to underlying (real) machine hardware. The mapping is maintained through control over a critical subset of

the instruction set executable by guest systems. Similarly, deterministic replay requires a monitoring facility achieving similar control over a particular ISA subset. Demonstrably, these subsets are not necessarily equal, but in practice overlap to a considerable degree. In order to reduce the development effort spent on a suitable monitor, available VMMs may be extended.

Seeking practical applications, system size and respective overhead needs consideration. What users or system developers on a single machine ultimately expect is *application* support and compatibility. Typical applications comprise only one or a limited number of processes. Compared to processes, whole systems as the future standard unit of repeated execution are considerably more than originally asked for. Moreover, the raw machine interface is comparatively complex. A native operating system is more heavyweight, and takes more cycles to initialize than just the number of processes it carries [13].

Essentially, deterministic replay facilities log information about occurring non-determinism, which are system state changes originating externally from the software system executed. This log may then be replayed on alternate instances. To achieve consistent logging and replayability, the structural complexity of the system's environment dictates the amount of change imposed on any existing implementation of that environment, such as a VMM. Given that an existing monitor is to be modified, not only technical feasibility, but maintainability, i.e. purely economical considerations, are of practical concern.

In short, the ideal guest system running inside a virtual machine would be small. It would be supported therein if its operating environment were simply structured, as would be determination of environment interactions guiding guest execution. Such properties need not sacrifice feature completeness and an application interface compatible to those of standard operating systems. Changes to a guest kernel, to aid the task at hand, require cooperation on the side of system vendors, but the change appears justifiable.

Although for different reasons, such properties closely match some of the motivations behind system paravirtualization. Paravirtualization is a virtualization technique which, different from classic virtualization, breaks with raw machine interface compatibility at the guest system interface. Beyond performance considerations, one reason to do so used to be lack of proper virtualizability of some popular processor architectures, such as the ones based on the prevalent IA-32 and derived instruction sets [69]. In order to virtualize such systems efficiently, paravirtual guest systems will not rely on an original system instruction subset, but request VMM assistance for privileged operations instead. This yields comparatively low overhead due to less dependency on low-level instruction em-

ulation. Similarly, raw I/O device interfaces can be replaced with abstractions at a significantly higher level.

Variants of system paravirtualization are presently implemented by a small number of open and commercially available products. One is the Xen hypervisor originally developed at the University of Cambridge [13]. This thesis evaluates deterministic replay for the paravirtual machine environment as implemented by Xen, recognizing differences to alternative implementations of basic machine paravirtualization where appropriate.

#### 1.2 Thesis and Contribution

In summary, the contributions of this work are

- Architecture and implementation of an extension to a paravirtual machine monitor to efficiently capture non-determinism encountered by paravirtual machine guest systems.

- The system replays uniprocessor guest operating systems controlled by a monitoring facility integrated in a fashion scalable on modern multiprocessor and multicore processor architectures.

- It demonstrates that some specific properties of the Xen VMM, most notably mapping of machine resources to data structures maintained in shared memory, can greatly reduce unwanted interference of such extensions to an existing VMM implementation.

- Experimental evaluation of the performance impact on workloads executed by virtual machines, derived from above implementation.

- An overall slowdown as low as 0.65% for CPU-intensive programs such as the SPEC CINT2006 benchmark suite has been measured.

- Experimental evaluation of bandwidth of determinant log capturing for typical I/O and CPU-intensive workloads.

- Directions on the practical use of performance monitoring facilities available on present x86 family processors for the purpose of replaying asynchronous events on virtual machines (or processes).

Implementation techniques and results presented here were largely inspired by the architecture of the Xen hypervisor, due to the paravirtualization technique it featured. With a background in high-availability system design, the project was called Xen/VLS (*Virtual Lock-Step* or *Virtual Logical Synchronization*). The idea shall be summarized as follows:

System virtual machines are the most practical solution to achieve deterministic replay for present commodity system applications. Therein, paravirtual machines perform best.

Retrospectively, meaning of the term *performance* is at least twofold. One obvious performance implication to evaluate is relative performance downgrade to target guest systems. Relative performance denotes time spent by the system while capturing event logs, performing a specific task, in comparison to the same task in an unmodified environment. Additionally, bandwidth requirements play a significant role.

Performing "best" requires comparable numbers. Deterministic replay with system VMs was first researched in 1996, back then in order to achieve highly-available guest instance pairs in distributed systems, i.e. semi-active replication. HA-applications, however, come at additional cost, due to its dependency on replica consistency, which adds additional latencies. Full semi-active replication of presently customary network interconnects has not been implemented as part of this thesis. Instead, most of the results presented here have been focusing on proper execution trace generation. The difference will be more thoroughly explained in chapter 2. However, some applications for deterministic replay rather depend on efficient tracing than subsequent replay, or a simultaneous combination thereof [97]. Furthermore, overall performance downgrade in semi-active replication is largely beyond log generation at the system core.

As outlined as part of the motivation, part of how a particular VMM extension "performs" in practice is not determined by slowdown, but rather simplicity. Compared to the present overall popularity of system virtualization, presently known applications of deterministic replay exist in niche markets. If a respective extension is too intrusive to the VMM implementation, or hampers development of future revisions, it is not maintainable under economic considerations. Within the prototype developed here, integration into the VMM ultimately needs not clash with original system design. Elements implementing the original virtualization layer remained largely unchanged, which suggests that the general approach taken remains defendable under above maintenance cost considerations as well. This is not only despite the issues outlined above. In order to achieve proper event logging, changes to the VMM are inevitable. But shared memory as the underlying communications primitive contributed as much to a device-independent I/O model for trace capturing and replay as it presently does for the Xen's core virtualization layer.

Regarding system performance, it turns out that the VMM architecture examined throughout this document has both advantages and disadvantages. Xen's

overall virtualization environment differs from traditional virtualization architectures. Is is based on two simple primitives: shared memory and an abstract event notification mechanism. On the one hand, this contributed much to a comparatively simple extension mechanism to achieve event logging. On the other hand, virtualization of I/O devices in Xen is not performed by the VMM, but one or a small number of privileged guest systems. The overall virtualization environment promotes asynchronous communication with isolated subsystems running in separate addresses spaces. Arguably, the architecture shares some similarities with common microkernel design. Xen's decomposed I/O architecture makes thereby extensions for proper trace capturing non-obvious. Suitable event logs need to reflect state changes at the granularity of single guest instructions in order to achieve full determinism during replay, where I/O virtualization commits device status asynchronously and across separate address spaces.

Core of the extended VMM architecture presented here mainly consists of a device abstraction inspired by customary physical I/O architectures. In real machines, asynchronous memory accesses originating from peripheral system components are typically performed by DMA (*Direct Memory Access*) engines. The same abstraction, as a software-implemented pseudo-device embedded into the machine virtualization layer, can be effectively and efficiently employed to make formerly arbitrary memory access interleaving consistently replayable. The resulting memory access paradigm has been called SMA (*Synchronous Memory Access*). At the source code level, some critical parts of it could be integrated almost transparently into intercommunicating guest systems.

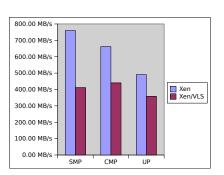

Traditional system VMMs are rather monolithic in design. Recently published results derived for full virtualization on a monolithic virtualization layer reported a performance downgrade of approximately 5% experienced when tracing compute-intensive tasks. While some of the techniques employed are not necessarily fully comparable yet, the results achieved with Xen have been encouraging. On Xen/VLS, run time overhead as low as 0.65% for above CPU-intensive workloads has been measured.

### 1.3 Organization of the Thesis

Chapter 2 will provide a overview of systems and methods upon which the thesis builds. This includes present trends in computer architecture. Additionally, theory of consistent state replication in fault-tolerant system design will be introduced, commonly referred to as the *state-machine approach*, or variants thereof. Finally, the merits of contemporary virtual machine technology as the

basis for applied state machine replication will be investigated.

The following two chapters turn to system virtual machines in more detail. Chapter 3 introduces basic techniques to efficiently virtualize today's commodity systems. Present paravirtualization techniques, as well as it's individual advantages and disadvantages, is a general technique closer examined. As noted above the specific virtualization architecture pursued throughout this document is not only determined by the paravirtual machine paradigm, but the Xen hypervisor as one specific representative. Xen will be discussed in chapter 4.

Chapter 5 will then describe methods to achieve determinism in monitored paravirtual machine execution, closing with a description of the resulting log format and an evaluation of event frequencies and bandwidth, as well as overall performance impact measured.

A small, but nonetheless important technical detail is consistent replay of asynchronous events. At the bare machine interface, these are typically device interrupts. Efficient replay of those is best performed when aided by dedicated facilities in processor hardware. Unfortunately, few processor architectures in computing history implemented such a feature. The ubiquitous x86 platform on which Xen, the VLS prototype and thereby this thesis build is no exception to this problem. Many contemporary x86 family processors implement a performance monitoring facility, which can be used for this purpose. This will be described in chapter 6.

The thesis will conclude with chapter 7, summarizing on overall results and experience gained. Finally, areas for future research will be suggested.

## 2 Background

The introductory material presented throughout this chapter is structured as follows. This thesis deals with techniques for the effective replication of software system instances as they are executed on physical machines or, simultaneously, a number thereof. Section 2.1 will touch on past and ongoing trends in the architectures of contemporary computer systems. One are improved multiprocessing capabilities in contemporary processor design, from which scalable architectures for the monitoring facility should benefit. Another is the potential of commodity components and cluster architectures in high-availability system design.

Built upon such systems, the underlying mode of replica execution requires careful inspection of control and data flow during input processing of each such instance. This functionality is commonly implemented as a monitoring facility between the target system and its surrounding execution environment. Section 2.2 introduces monitoring and event logging to execute replicas consitently in distributed architectures.

Finally, section 2.3 will turn to machine virtualization. Similar to the above facility for monitoring replica execution, virtual machines comprise a monitor to achieve resource sharing between a number of guest systems. The remainder of this document mainly considers integration of replica monitoring into multiprocessing-capable virtual machine monitors.

#### 2.1 Real Machines

#### 2.1.1 Machine Architecture

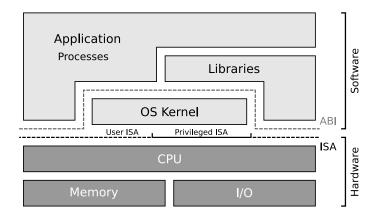

A general purpose computer system comprises a number of resources, divisible into three main types of components: (1) A processor, or a number thereof, executing instructions located in main memory (2) main machine memory, randomly accessible in a single global address space shared by all processors. (3) A number of devices for peripheral data input and output (I/O) [86].

Depending on the number of processors they contain, computers can be classified into uniprocessor (UP) or multiprocessor (MP) systems. Multiprocessor

systems became an option with the advent of multitasking operating systems. Processors in such systems are tightly coupled, managing a number of program instances simultaneously. Program instances at the machine level are processes and threads, which perform sequences of instructions, sharing resources on a common hardware platform.

Symmetric multiprocessing (SMP) machines are built from multiple physical processors with identical instruction sets. Symmetry among processors implies that all processors serve identical purposes, but execute separate threads of machine instructions in parallel. In preemptive multitasking systems, assignment of individual processors to any given thread of execution is largely transparent at the application level.

Microcomputer performance experienced sustained and rapid growth over the past three decades. Moore's law predicted exponential growth in chip complexity over time, and has been confirmed since its invention 1965 [62]. Likening complexity to processing power, performance gains used to evolve accordingly. Continuous gains in computing power, however, come at the cost of tremendous investments in research, engineering and component manufacturing.

With the advent of multiprocessing systems, memory access became a primary concern. Notwithstanding its programming model as a single shared entity, if memory is implemented as such (*Uniform Memory Access*, UMA), bandwidth consumption at the memory interface becomes a major bottleneck, which in turn accounts for limitations in the overall scalability SMP systems can achieve [9]. NUMA (*Non-Uniform Memory Access*, [50]) distributes physical memory among a number of processors, while maintaining the shared memory paradigm at the processor ISA.

Past advances in processor manufacturing were dedicated to individual performance gains in the single thread, satisfying perpetual demand for more data bandwidth and faster speed in sequential processing. The solutions were higher clock speeds, larger caches and implicit concurrency in the sequential execution model. Instruction-level parallelism (ILP) expands performance of sequential programs, but cannot advance beyond a point where ultimately correctness would be at risk. Higher clock speeds come at the cost of increased power consumption and heat dissipation. For years to come, only caching increases will prevail. Single-threaded performance will not sustain its past rate of growth.

2.1 Real Machines 11

#### 2.1.2 Microprocessor Trends

Starting from 2001, the evolution of microprocessors saw a fundamental turn in orientation regarding the question whether, and how, performance improvement in future processor generations are to be maintained. While the question is not whether Moore's law continues to apply, future increases in chip complexity would not map to single-threaded application performance and additional consumer value.

The major shift of focus is an overall shift ILP to thread-level parallelism (TLP). Chip-level multiprocessor (CMP) architectures combine two or more processor cores of one and the same architecture on a single integrated circuit. While the functional interface equals that of symmetric systems, physical colocation of inter-processor communication and the integration of common resources such as the memory and caching hierarchy provide additional performance improvements. Different from ILP, however, thread-level parallelism in single processors does not benefit from a larger number of cores without assistance on the side of application programmers. Multithreaded application development and tuning can be a time consuming and costly task, but within the foreseeable future a necessity to utilize increases in processor bandwidth appropriately.

Shared memory multiprocessor systems represent a commodization from high-performance computer to everyday workstation computer usage. A second major change in is virtualization of instruction set architectures, memory and I/O interfaces in machine hardware. While the motivations are various, one of the major issues the software industry is presently facing is that classic programming models are as sequential as the original machine architecture they derived from. Beyond the high-performance and high-end server market segment, many systems remain underutilized. A turn to virtualization in the industry is in part due to the shift to chip multiprocessing. One of the major issues the software industry is presently facing is that classic programming models are as sequential as the original machine architecture they derived from. Beyond the high-performance and high-end server market segment, many systems remain underutilized. Consolidation of multiple operating system instances and, presumably single-threaded, application programs may reduce overall system and maintenance cost [31].

#### 2.1.3 High-Availability and Fault-Tolerance

Availability is the capability of a system to provide a given service. The concept of a service is arbitrary. Services may be interactive ones, i.e. provided to users,

or provided among individual system components, each being a subsystem of an overall more complex system.

An ideal system would be available at any time during its scheduled times of operation. Time of availability is referred to as *uptime*, while scheduled times of unavailability are usually referred to as *planned downtime*. Unfortunately, systems are generally not ideal, but prone to failures. With general-purpose computer architectures, faults in hardware or software may occur, as do externally induced failures (such as power outages). Either case may lead to *unplanned downtime*. In some environments a given level of service during failure-free operation may be reduced to some degree during recovery, such as performance, but service continuity must be maintained, with reasonably high probability.

Once failures are considered, repair must be as well. Both uptime and unplanned downtime become transient states. Two variables are often found across the relevant literature:  $mean\ time\ to\ failure\ (MTTF)$  and  $mean\ time\ to\ repair/recovery\ (MTTR)$ , both expectancy values of uptime and unplanned downtime in a probabilistic model [84]. The availability A of any given system is thereby defined as follows:

$$A = \frac{\text{MTTF}}{\text{MTBF}}$$

Availability can therefore be quantified in terms of uptime per scheduled time of operation. The value often specified as percentage; in many fields where unconstrained availability is of major concern, such as life-critical services (e.g. telecommunication, medical equipment) availability of 99.999% (dubbed "five-nines") is an often-quoted requirement. With continuous services, where even the concept of planned downtime is not accepted, an alternative expression is downtime per year. For five-nines availability, expected downtime would evaluate to 315.36 seconds per year, about five minutes.

High-availability (HA) is an expression for a considerably large availability, generally at a level which cannot be met by interactive repair, such as fivenines. Under the assumption that failure of individual components in a system cannot be ruled out with sufficient confidence, such systems need to adapt upon failures. Fault-tolerance implies that partial failures are expected, and provided for. Adaption to failures requires redundancy of system components, which will be revisited in section 2.2.

2.1 Real Machines 13

#### 2.1.4 Cluster Architectures

The material presented throughout this document is targeting hardware and system design customary in present cluster architectures. A distributed system is a collection of computer *nodes* interconnected by a network. A *cluster* is distributed system in a local or system area network, cooperating for the purpose of serving common goals. A node is an otherwise autonomous computing device, comprising a number of processors. Generally, cluster computing is classified into three major branches:

**Compute clusters** comprise a potentially large number of interconnected processing nodes in order to increase overall system performance for computationally intensive tasks.

**Load-balancing clusters** distribute client requests among a number of servers. Unlike compute clusters, load-balancing clusters comprise at least two different tiers: server nodes providing actual service to clients, and routing nodes (frontends) distributing incoming client requests among servers.

**High-Availability clusters** comprise multiple machines to improve reliability for a service or group of services. That is, availability clustering nodes operate foremost *redundantly*, while compute clusters process jobs cooperatively.

For the purpose of this chapter, the two fundamental concepts are availability (redundant) and compute (performance) clustering. The major difference between compute clustering and load-balancing is due to the type of service provided. Compute cluster nodes cooperate on a single task issued by one or only a small number of users. Load-balancing clusters provide network services typically designed to a client-server model, for a large number of clients. This in turn accounts for different communication models. Performance gains achievable in compute clusters largely depend on the performance of network links carrying necessary node intercommunications. In contrast, client-server traffic routed in and out of the cluster accounts for most of the consumed network bandwidth in load-balancing.

Availability clustering and load-balancing are correlated in that they are sometimes combined. Since frontend nodes represent a single point of failure for a large number of clients, redundant deployment is a fundamental requirement in order to retain desired levels of availability. Conversely, multiple load-balanced servers may provide the corresponding level of redundancy without further augmentation. Many successful client-server protocols, such as HTTP, are stateless, rendering servers immediately redundant. Once a faulty machine is excluded from request forwarding by frontends, clients may regain service at any other

machine without readjustment.

#### 2.2 State Machines

One major motivation when replication is applied to virtual machines is to run applications unmodified, i.e. transparency. In contrast, many fault-tolerant system designs require applications and interfaces meeting individual constraints of the overall system model, which then in turn makes recovery from failures possible. Running applications unmodified, in contrast, requires the opposite approach: an overall system model meeting the properties of commodity application environments. This requirement lends itself to a replication technique called semi-active replication [14], a variant of active replication in distributed systems, with properties which make it particularly attractive when applied to general-purpose and commodity systems.

The introductory material regarding active replication is organized as follows: All variants of active replication originally derive from state machines as the underlying processing model. This concept is introduced in section 2.2.1. Second, replicated state machines and fault recovery must meet two important requirements. One is *agreement*, on the sequence of state transitions, subject of section 2.2.2. The other is global *consistency* of recoverable state, discussed in section 2.2.3. A reference architectural model integrating agreement and replicated execution is then briefly introduced in section 2.2.4.

Section 2.2.5 turns to inherent non-determinism in general-purpose runtime environments. The fact that few real-world applications meet the state machine assumption inspired *piecewise determinism* (PWD), a reformulated execution model. It forms the basis of *deterministic replay*, i.e. event (as opposed to *message*) logging to save system state during execution for later recovery.

Different from the state machine approach, some sources of non-determinism predominant in general purpose runtime environments cannot be efficiently agreed upon. Deterministic replay imposes lesser demands on replica agreement to achieve better efficiency. This constitutes *semi-active* replication, introduced in section 2.2.6.

Deterministic replay and semi-active replication mostly differ by the concept of fault-tolerant log dissemination in a distributed system. Section 2.2.7 will discuss causal logging as a fault-tolerant log protocol, which combines maintenance of global state consistency with comparatively low latency induced by replica synchronization.

2.2 State Machines 15

#### 2.2.1 Deterministic Machines

The basic model underlying any variant of active replication are deterministic, finite state machines, or simply *state machines*. A state machine  $M = (S, s_0, \Sigma, T, \Gamma, \omega)$  comprises:

- A finite set of states S, where the machine starts from an initial state  $s_0 \in S$ .

- Finite sets  $\Sigma$  and  $\Gamma$  representing input and output of the machine.

- A state transition function  $T:(S,\Sigma)\to S$ .

- An output function  $\omega: S \to \Gamma$

A computation (or execution) of M with length n is a sequence of states  $s_0s_1...s_n$  in S traversed for a series of inputs  $\sigma_0\sigma_1...\sigma_n$  in  $\Sigma$ .

The machine is deterministic because any state transition performed by the machine is uniquely determined solely by T, that is: present state and input. Similarly, output at any point during the computation is entirely driven by present machine state. Hence, if input is determined, then the resulting state sequence is determined as well, as is observable output.

In the design of fault-tolerant systems, this model is applied to processes, which constitutes the so-called *state machine approach* for replication in distributed systems [73]. Different from the static model above, it is usually formulated in more convenient terms of *deterministic programs* which operate on *state variables*. Programs execute *commands* upon client *request* and generate output accordingly. Again, both state transformations and outputs are determined solely by commands and present state.

It is well recognized that this model may applied to systems implementing requests and outputs in any conceivable fashion. For subsystem decomposition in programming environments, procedure calls may be considered. In distributed systems, the most practical paradigm is the sending and receiving of messages. For virtual machines, I/O instructions will be considered.

#### 2.2.2 Coordination

For distributed, deterministic state machines to produce the same state, all must encounter same set of requests (input). The reason why state machines are a convenient model is that requests are processed *sequentially*. In contrast, concurrent dissemination and/or physical reception of messages in distributed

systems is often arbitrary, due to the properties of the underlying communication network. *Coordination* governs agreement and ordering on the request sequence among all replicas [73]. Coordinated processing of request implies two properties.

**Atomicity** Any request is either performed by all (correct) replicas, or none. In other words, all correct replicas *agree* on the same set of requests.

**Ordering** All (correct) replicas process requests in the same (total) order.

Coordination may be performed by clients and servers or, if clients are independent of each other, by the replicated state machines themselves. Ordering of requests may be constrained, depending on requirements of the protocol established<sup>1</sup>. Stateful protocols typically assume an implied order which adheres to the intuitive concept of (potential) causality as observable in space and time, constituted by Lamport's more general happens-before (" $\rightarrow$ ") relationship among events in distributed processes [56]. The happens-before relation is defined as follows:

- 1. Processes execute sequentially. If event  $e_a$  happens before  $e_b$  at the same process, then  $e_a \rightarrow e_b$ .

- 2. Message transmission is causal. If  $e_a$  is the sending of a message and  $e_b$  its reception, then  $e_a \rightarrow e_b$ .

- 3. Causality is transitive. If  $e_a \to e_b$  and  $e_b \to e_c$ , then  $e_a \to e_c$ .

Causality imposes a partial order on the sequence of events. Replica coordination, in contrast, demands a total order on requests. Intuitively, an arbitrary superset of (potential<sup>2</sup>) request causality:

- 1. Specifically: Two requests issued by the same client shall be processed in the order in which they were sent.

- 2. Generally, if clients intercommunicate: For any pair of requests  $r_1$  and  $r_2$ , if  $r_1 \to r_2$ , then  $r_1$  shall be processed before  $r_2$ . This order can only be determined by clients.

Mutual agreement has seen intensive research, as it is probably the most elementary problem in distributed system design. The most challenging assumptions are those considering byzantine conditions, i.e. under the assumption of

<sup>&</sup>lt;sup>1</sup>Independent clients and stateless protocols are typically robust against server-side reordering of independent requests. A prominent example is HTTP in the World Wide Web.

<sup>&</sup>lt;sup>2</sup>Whether *true* causality actually applies is up to data flow guiding state transformation. Causality in the *happens-before* relation adheres to *potential* causality, e.g. as derivable from external observation.

2.2 State Machines 17

(arbitrary) process failures [73]. In order to disseminate messages to an arbitrary number of replicas under the conditions outline above, reliable multicast protocols play an important role. Frameworks for reliable multicast provide for agreed, ordered message to process groups with a sufficiently general transport layer interface. View-synchronous group communication systems augment reliable multicast with support for dynamically changing replica configurations and network partitioning [23].

#### 2.2.3 Global State Consistency

A global state G of a distributed system is the aggregation of the individual states of all participating nodes. The challenge with global system state is that there is no global entity which is capable of capturing such state instantaneously. Any single node can only capture its own state, as well as its input and output events [21].

One may thereby characterize an execution of a distributed system as a series of transitions in G. A consistent global state is one that may occur during a correct, failure-free execution of the system. This is the case if causality is maintained, which again can be expressed in terms of Lamport's happens-before relation: For any two events  $e_0$  and  $e_1$ , if  $e_1 \rightarrow e_2$  and  $e_2$  happened in G, then  $e_1$  must also have happened in G.

Consistency in distributed systems is an important factor in a number of different fields, including of global predicates such as termination or deadlock, commonly performed on "snapshots" of global state [21], or applications in distributed debugging and garbage collection [23].

Maintenance of local causality in a single sequential process (clause 1 in the definition of the *happens-before* relation) is trivially achieved: Any synchronously taken snapshot of a single node is consistent. However, the consistency of inter-process dependencies (clause 2) is harder to maintain. Intuitively, consistency across machine boundaries demands that for a collection of states in a distributed system is to remain consistent, the following must apply: If one process's state is caused by reception of a message, then the respective sender's state must reflect its transmission [29].

In fault-tolerant system design, one method where the rules of consistency require considerable consideration is state *recovery*, i.e. restoration of system state after a fault. If only part or outdated system state is recoverable, consistency is at risk. This is commonly the case in passive replication, which spurred of

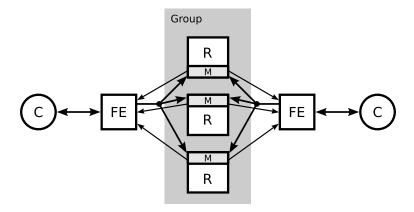

Figure 2.1: Active replication: replicas (R) with frontends (FE) and clients (C) [23].

past research in rollback recovery for complex systems, i.e. systems comprising multiple distributed, intercommunicating components. In that case, a failure in one component may cause the need to roll back respective clients [29].

With active replication, global state consistency needs special consideration when communicating with an "outside world", i.e. externally visible system behavior. This includes any remote client served, as well as peripheral devices a system is connected to. Different from an orchestrated rollback outlined above, outside clients cannot be subject to recovery procedures, hence any interaction with these systems is irreversibly manifested in global state. This in turn constitutes demand for reliable multicast and request atomicity: if e is the sending of a message to the outside world, then any event  $e'(e' \rightarrow e)$  must be recoverable by all replicas [29].

#### 2.2.4 Active Replication

Actively replicating systems organize replicas into groups of redundant system components, forming a single *logical machine*. The overall architecture is shown in figure 2.1. Each replica acts as a state machine. System software on nodes hosting individual replica operates as a *replica manager* [23], or simply *monitor* [73]. Dedicated nodes act as a *frontends* which mediate between individual replicas and clients. Frontends fulfill several functions in one entity:

• Client access: Clients (both client components in complex fault-tolerant

2.2 State Machines 19

Figure 2.2: Dual redundancy in a leader/follower scheme.

systems or clients in the outside world) may remain unaware of the group topology masked by the FE.

- Dissemination of input messages: Frontends act as transmitters [73], forwarding input messages received from any client to all replicas in coordination, i.e. the set of requests and a total order of delivery is agreed upon. In message passing systems, reliable multicast implementations perform this task. Note that if clients are communicating with each other, ordering must reflect causality.

- Collection of output messages: Only one response is delivered to clients, duplicates which are due to replication will be discarded. Depending on the failure model, the FE may act as a voter by comparing responses received from individual replicas.

If only crash-failures are to be considered, up to t failures can be survived by deploying at least t+1 replicas. Since any response is correct under this assumption, the first response collected may be forwarded to the client. Up to t byzantine failures can be tolerated by (2t+1)-fold replication. In this case, the voter may accept a majority after collecting t+1 identical responses [23]. Given one or more dedicated nodes for input coordination and voting, three replicas are sufficient to mask up to either t=2 crash faults or t=1 arbitrary node failures.

A single frontend is generally considered insufficient, since it would represent a single point of failure between service provisioning by replicas and service delivery to clients. However, there is no requirement to integrate all functions described above in one single processing entity. Many systems, e.g. NSAA [16],

comprise dedicated, redundant frontend logic.

Others, such as RAPIDS [94] or the hypervisor system by Bressoud and Schneider [19], do not employ dedicated nodes to that purpose, which deserves additional consideration. Indeed, simpler topologies are possible, assuming that only crash faults matter. The role of communication with clients may be assigned to one or more replica nodes, e.g. via election. In that case, voting can be omitted, since no faulty messages can occur. Hence, output operations on the follower may be discarded by the local monitor.

Simplifying the topology further, the number of replicas may be reduced to a pair, as depicted in figure 2.2. In this case, the multicast scheme for event dissemination may be replaced to a simple ordered, reliable unicast protocol (i.e. a FIFO channel). On IP networks, a respective group communication layer can be replaced by TCP, as long as adequate failure detection is provided for.

Independent of the state replication applied, the resulting topology then resembles the general primary/backup fault-tolerance scheme, where a respective primary is exclusively assigned with the frontend role. In case of a failure of the primary, provisioning of the service must be taken over by the backup system. A combination takeover of both network ("IP Takeover") and block storage I/O interfaces was published in [17], building a highly-available file server.

#### 2.2.5 Facing Non-Determinism

The state machine approach works best if applied to guide program design. Any component of a fault-tolerant system subject to replication must qualify as a state machine. This is of no concern when building systems from ground up accordingly: anything that can be structured in terms of procedures and procedure calls can also be structured using state machines [73].

However, it is often considered insufficient if either programs or, ultimately, the processes executing them are inherently non-deterministic in the state sequence they traverse. The former case of non-deterministic programs is important when seeking to replicate arbitrary applications. The latter is case of non-deterministic processes applies to a large fraction of customary execution environments.

**I/O Instructions** The original state machine approach demands that requests from remote processes are the only source of information affecting process state [73]. Indeed, the implied request/response scheme of operation is commonplace in client/server architectures, like database systems or web servers. However,

2.2 State Machines 21

few real-world applications obey strict determinism in processing requests. Typical examples are queries on system time, time-sensitive operations, or true randomness, as e.g. employed in cryptographic functions, none of which behave deterministically across redundant invocations.

Considering high-level languages, many synchronous I/O primitives, e.g. those of event multiplexing (consider the UNIX select() call [42]) yield non-deterministic results<sup>3</sup>.

Schneider recognized this fact and suggested careful redesign of all replicas in order to externalize all such data sources [73]. Intending to run applications unmodified, the simple assumption of processes behaving like state machines rarely applies in practice.

**Concurrency** Some non-determinisms derive from the basic requirement of *sequential* execution of either requests as well as individual request processing. Requests are not necessarily processed sequentially. In complex systems, cooperative threads or processes may execute requests in arbitrary order. Processing of individual requests may essentially be multithreaded and/or operating on shared memory.

Concurrent processes on shared memory may produce arbitrary interleavings of state accesses, and therefore perform different transformations on overall state under different timing conditions. Non-determinism due to thread arbitration may be induced by the physical machine. Processors in hardware multiprocessing systems are essentially behaving like distributed systems. It may as well be as part of an essentially non-deterministic software execution environment, e.g. thread scheduling on preemptive uniprocessors, which is essentially driven by time and timers.

**Asynchrony** Asynchronous event delivery to any software system is typically performed by an immediate control transfer to a service routine which is implemented by that system. Initiation of the control transfer at runtime is performed by the processing environment, not the system itself. The control transfer interrupts the running thread, and resumes execution after termination of the service routine.

In order to have any impact at all, service routines unilaterally need to affect global state. Consistent with the *happens-before* relation, the state transition

<sup>&</sup>lt;sup>3</sup>Note that this applies at the language level. Admittedly, when considering the machine level, one may argue that non-determinism in I/O multiplexing is due to asynchrony. This is discussed below.

induced by a service routine may depend on the precise point of event delivery within the state sequence traversed by the interrupted thread. Hence, deterministic behavior among replicas can only be enforced by agreement on the precise point of delivery.

Asynchrony in I/O processing is featured by virtually all general-purpose execution environments, since it is fundamental to efficient communication with external entities<sup>4</sup>. Non-determinism due to asynchronous events is propagated across virtually any software layer in the affected system. At the ISA level, asynchrony is induced via external interrupts. POSIX-compatible environments empty signals as one possible mapping of asynchronous events to processes. The select() system call, being a synchronous source of non-determinism at the process level, is determined by asynchronous I/O events at the system level. If service routines are not involved, constructs equivalent to select() may be found in most high-level language environments, such as the Java Runtime Environment<sup>5</sup> [51].

In order to overcome these problems, a different model for the execution of such systems needs to be applied. Generally, the concept of machine *state* will prevail. But different from mere state machines, *execution* driving state transitions needs to reflect the effective complexity of the systems described.

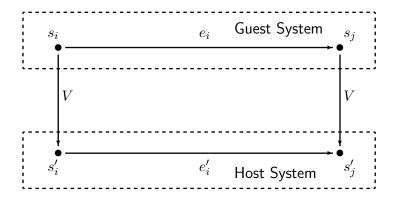

Given finite amounts of memory, any practical machine has a finite number of states S. An execution event  $e \in E$  is a binary relation between states in S:  $e \subset S \times S$ . For any event  $(s_i, s_j) \in e$ , write  $s_i \stackrel{e}{\to} s_j$  (e produces  $s_j$  from  $s_i$ ). An event may comprise any one of a number of different actions performable by the underlying machine at a given state. One example is execution of a machine instruction residing in memory. Another possible state change would be a control transfer induced externally. In shared-memory multiprocessors, the notion of an event includes changes to state variables performed externally as well. A suitable model may partition the set E of all observable events accordingly:  $E = I \cup N \cup D$ , where I comprises the set if instructions implemented by the processor, N externally-induced control transfers, and D the set of all externally-induced changes to in-memory machine state.

**Deterministic Events** An event  $e \in E$  is *deterministic*, if and only if for any states  $s_i$ ,  $s_j$  and  $s_k$  in S the following applies:

<sup>&</sup>lt;sup>4</sup>One alternative is *polling*, i.e. frequent synchronous inquiries on the status of such entities. Polling is not an efficient alternative for events occurring at high frequencies or when latency is critical [82].

<sup>&</sup>lt;sup>5</sup>Earlier versions of the JRE employed the second alternative: Threading, which trades nondeterminism due to event handlers with non-determinism due to concurrent thread scheduling.

2.2 State Machines 23

$$s_i \xrightarrow{e} s_j \wedge s_i \xrightarrow{e} s_k \Rightarrow s_j = s_k$$

That is, e is a (partial) function in S, as opposed to a relation. Informally, deterministic instructions are those which are guaranteed to produce the same result in machine state whenever issued from the same original state.

Events due to instruction execution will be termed synchronous, i.e. occurrence of such an event is predetermined from present machine state, but may be preempted by asynchronous events. The complementary set of asynchronous events  $N \cup D$  must be monitored for the reasons outlined above.

In fault-tolerant, distributed system design, extension of the state machine approach to include the notion of non-deterministic events lead to postulation of the so-called *piecewise deterministic execution* (PWD) model, attributed to Strom and Yemini [29, 77]. Typically described only informally, it assumes that a suitable monitor must be enabled to intercept and control any execution event whose effect on machine state is not determined from original state. In message passing systems conforming to the state machine model, the PWD assumption is trivially met by controlling message delivery to replicas. For the extended machine model outlined above, this includes synchronous, but non-deterministic, as well as asynchronous events.

#### 2.2.6 Semi-active Replication

The attractiveness of the state machine approach is due to the fact that only events determining the transformation of replica state need to be disseminated. This constitutes *active*, as opposed to *passive* replication (e.g. checkpointing [29, 23]), where critical application state needs to be captured and updated as a whole. Hence, actively replicated state is not captured, but the computational state sequence regenerated, by mutual agreement on any information guiding that sequence.

This is practical for message-passing systems of intercommunicating processes which satisfy the state machine assumption. The need for coordination then only pertains to messages received from clients. Agreement between two nodes according to the state machine approach is shown in figure 2.3, where total ordering on messages in performed by one or several transmitters.

Contrasting message-passing systems, piecewise deterministic execution requires coordination not only of application-level messaging. Instead, *any* non-deterministically occurring event must be agreed upon, i.e. including those

Figure 2.3: Agreement in message passing systems.

relating to the runtime environment executing a given application. The problem is that agreement on events originating from individual replicas, as opposed to a central frontend device, is beyond reliable multicast, but requires a solution to the consensus problem.

Protocols to achieve agreement on individual events are not practical if the tolerable delay in reaching an agreement approaches or even goes below achievable latency on the communication path. This is potentially the case for a large number of the event sources outlined in section 2.2.5. A prominent example are timers and thereby timeouts and the delivery of timer-driven asynchronous events.

In order to reach an agreement, their exact point in an ongoing computation must be agreed upon in order to deliver the event deterministically on all nodes. On a single node, the event would be delivered timely, for maskable events at the immediately next point during a computation where the event is not masked. Reaching agreement among distributed replicas, in contrast, takes a synchronous intercommunication sequence. Since no sufficiently synchronized clocks are available, all replicas must exchange their *prospective* points of event delivery. States reached by active replication cannot be rolled back, hence the most advanced point in the computation needs to be agreed upon. Slower nodes then need to catch up. The result is that while state machine synchrony demands that slower nodes dictate the overall speed of computational progress, delivery latency through agreement always represents the worst-case scenario.

2.2 State Machines 25

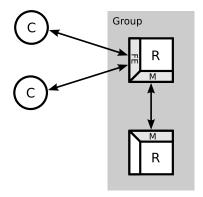

Figure 2.4: Semi-active replication replaces multilateral agreement with unilateral decisions.

Generally, for events occurring at a comparatively high frequency, e.g. interrupts delivered to a virtual machine, the cost of a consensus protocol may easily approach the frequency of events experienced during non-replicated execution, slowing down systems by orders of magnitude. Discussions of the number of messages required to reach distributed consensus and the implied performance impact are found in e.g. [12] and [94]. This excludes systems employing low-latency interconnects in dedicated hardware, such as NSAA, which aims at negative impacts in the range of 5-10% [16].

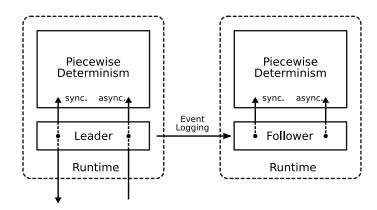

Semi-active replication [66], also called the *leader/follower* model [14], is a variant of active replication avoiding the relative cost of distributed agreement. For this purpose, the set of nodes is partitioned into one *leader* and a number of *followers*. The idea is to replace consensus, formerly achieved by participation of all nodes, with unilateral decisions about all non-determinism. In short, it is an application of deterministic replay. In semi-active replication, logging of determinants is solely performed by the leader instance. These log entries are disseminated to all follower nodes, which *replay* the original state sequence. The overall structure of this approach is shown in figure 2.4.

The difference to deterministic replay under the PWD model is that fault tolerance requires events to be recoverable in case of failures, where replay for debugging or profiling purposes has lesser requirements. Protocols maintaining consistency across replica failures are discussed in the following section.

Semi-active replication is usually proposed to render virtual machine instances fault-tolerant against crash failures, i.e. it is assumed that faulty host systems halt execution upon occurrence of such a fault. Admittedly, byzantine conditions due to arbitrary node failures cannot be easily covered by the leader/follower model. This is due to the fact that mutual agreement on any state change induced by the processing environment is dictated by the leader processor alone. In case of a defect, the leader node may therefore propagate erroneous events to all follower nodes. Powell noted that this restriction can be relaxed to some degree, if followers check all log entries against a given range of valid ones [66]. Such checks were implemented as part of the Delta-4 architecture. Upon encountering a log entry deemed invalid, all follower nodes fall back to a common default one. Still, an erroneous valid event would cause state divergence to go unnoticed. Delta-4 employed external voting logic in order to correctly mask such faulty events.

# 2.2.7 Causal Logging

Deterministic replay on one or a number of follower instances enables state consistency among failure-free replicas, but does not guarantee that all events are recoverable if the leader fails, if processing and log transmission are performed asynchronously. Due to the fact that a follower instance is not in synchrony with the leader, failover always implies some (hopefully small) degree of rollback in computational state. This is the major difference from classical lockstepping techniques implemented in hardware (e.g. [15]). In order to recover consistent global state beyond failures, *synchronization* between leader and followers needs to take place.

Generally, synchronization is concerned with the concept of *stability* of events, respectively messages: In rollback recovery, an event is stable if it is recoverable, i.e. as soon as it is saved on stable storage [29]. With log dissemination through messaging, stability implies multilateral agreement on a respective message [73]. For a log transmission over a reliable FIFO channel to a single follower, a simple acknowledgment on the last event received will suffice.

Different approaches when to perform synchronization exist. One is to synchronize on every event, before it affects the replica computation. This constitutes *pessimistic*, or *synchronous* logging [29]. Causal logging, in contrast, exploits the fact that replica state only needs to be recoverable once it becomes observable. As shown in section 2.2.3, this is only the case as soon as a respective system component is communicating with its environment. Hence, to maintain global state consistency, synchronization needs to take place just before performing an output operation.

2.2 State Machines 27

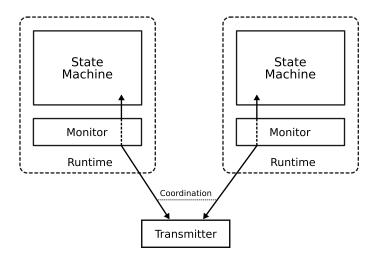

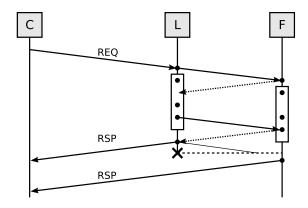

Figure 2.5: Synchronization and duplicate output with semi-active replication.

Figure 2.5 depicts causal logging<sup>6</sup> for only a single client and follower. Bars denote input processing by the replica instance, dots individual events to be logged, arrows indicate communication in space and time. Dotted arrows indicate a notification that an event has stabilized on the follower side. Client C sends a request REQ to a service. The monitor of leader node L emits a corresponding log message and delivers REQ to the local replica. It then continues processing REQ, which for the case depicted leads to execution of 3 additional non-deterministic events. Figure 2.5 shows only log transmission for the first and last event before RSP. RSP is only committed after the last non-deterministic event is known stable in F.

One benefit of causal logging is that asynchronous log dissemination can be performed parallel to replica execution. Furthermore, asynchronous transmission enables buffering and bulk transfers of events. Still, the remaining need for synchronization imposes some amount of latency imposed on all output operations committable by the leader. As depicted in figure 2.5, every event which happened before the sending of RSP must be waited for to become stable. The effect is called *output commit problem* [29].