## TECHNISCHE UNIVERSITÄT MÜNCHEN

### Lehrstuhl für Technische Elektronik

# Device Aging in Analog Circuits for Nanoelectronic CMOS Technologies

#### Florian Raoul Chouard

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. U. Schlichtmann

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. rer. nat. D. Schmitt-Landsiedel

- 2. Univ. Prof. Dr.-Ing. S. M. Sattler, Friedrich-Alexander-Universität Erlangen-Nürnberg

Die Dissertation wurde am 18.01.2012 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 25.04.2012 angenommen.

## Chapter 1

## Summary

This work covers an elementary study on the emerging topic of device degradation and the impacts on CMOS analog circuits. Thereby, aging effects are considered leading to a time and stress dependent drift of device characteristics but not to a destruction of the device itself. In fact, parameter drift can also lead to a circuit fail due to a violation of specification. The considered degradation effects are known as Bias Temperature Instability (BTI) and Hot-Carrier Injection (HCI). Different from the numerous investigations on the aging effects themselves, this study starts from the circuit point of view, taking into consideration typical circuit related device design constraints and arising operation states. To provide results valid for future circuit design in latest CMOS processes, the used CMOS technology provides an advanced 32nm high- $\kappa$ , metal gate process. This approach reduces occurring device aging for most of the cases to a domination of area independent BTI effects due to the typical large area devices used to provide accurate analog signal processing. Distinct investigations on elementary analog circuitries like current-mirrors, reference circuits, amplifiers and oscillators gave a fundamental insight into the individual sensitivity of these circuits towards the aging of incorporated devices. Studies are performed on exemplary state-of-the-art circuitry and the found results are generalized so that they are universally valid and mostly transferable to other circuit implementations. The focus is on the circuit dependent performance parameter with largest impact by device degradation, which is used as circuit aging output monitor, but also accompanying second order effects on other circuit characteristics are studied. With analytic approaches to describe circuit aging dependent on critical operation states, a new circuit reliability concept is developed, providing deeper insight into circuit aging than all other state-of-the art reliability tools do up to now. This forms the basis for the development of new concepts and approaches to provide equivalent but accelerated circuit level aging for test and the usage of the built-in circuit's analog signal processing to measure degradation effect behavior, which is not included in today's degradation modeling. But also countermeasures are derived by profiting from general effect behavior on circuit level for an aging suppression, that even offers new design approaches with respect to area requirements given by matching specifications. All relevant findings are approved by stress measurement on hardware built in the high- $\kappa$ , metal gate CMOS process. The universal validity of the found results provides circuit designers the knowledge about aging critical circuit blocks and operation states. Furthermore, recommendations for aging aware circuit design and outlooks to future circuit aging behavior in novel CMOS processes are provided in this work.

## Contents

| 1 | Sun  | nmary                |                                                  |      |    |     |                   | i    |

|---|------|----------------------|--------------------------------------------------|------|----|-----|-------------------|------|

| 2 | Intr | $\mathbf{roduction}$ |                                                  |      |    |     |                   | 1    |

|   | 2.1  | Motivation .         |                                                  |      |    |     |                   | 1    |

|   | 2.2  | State-of-the-A       | Art in Circuit Reliability Research              |      |    |     |                   | 2    |

|   | 2.3  | Contributions        | s of this Work                                   |      |    |     |                   | 4    |

| 3 | Agi  | ng Physics           |                                                  |      |    |     |                   | 6    |

|   | 3.1  | CMOS Devic           | e Wearout                                        |      |    |     |                   | 6    |

|   | 3.2  | Impact on De         | vice Parameters                                  |      |    |     |                   | 6    |

|   | 3.3  | Bias Tempera         | ture Instability (BTI)                           |      |    |     |                   | 8    |

|   |      | 3.3.1 NBTI           | in pMOSFETs                                      |      |    |     |                   | 9    |

|   |      | 3.3.2 PBTI           | in nMOSFETs                                      |      |    |     |                   | 11   |

|   |      | 3.3.3 PBTI           | /pMOS and NBTI/nMOS                              |      |    |     |                   | 13   |

|   | 3.4  | Hot-Carrier I        | njection (HCI)                                   |      |    |     |                   | 14   |

|   |      | 3.4.1 Condu          | active Hot-Carrier Injection in nMOSFETs         |      |    |     |                   | 15   |

|   |      | 3.4.2 Condu          | active Hot-Carrier Injection in pMOSFETs         |      |    |     |                   | 17   |

|   |      | 3.4.3 Non-C          | Conductive Hot-Carrier Injection in nMOSFETs and | d pl | ИO | SFE | $\mathrm{CT}_{5}$ | s 18 |

|   | 3.5  | Aging Effect         | Modeling                                         |      |    |     |                   | 18   |

|   |      | 3.5.1 Semi-          | Empirical Models                                 |      |    |     |                   | 20   |

|   |      | 3.5.2 Comp           | lex Models                                       |      |    |     |                   | 22   |

|   |      | 3.5.3 Relax          | ation Model                                      |      |    |     |                   | 23   |

|   | 3.6  | Circuit Relia        | pility Simulation                                |      |    |     |                   | 25   |

|   | 3.7  | Reliability Te       | sting                                            |      |    |     |                   | 26   |

|   | 3.8  | End-of-Lifetin       | ne Use Cases                                     |      |    |     |                   | 27   |

|   | 3.9  | Trend                |                                                  |      |    |     |                   | 28   |

| CONTENTS | iv |

|----------|----|

|          |    |

|   | 3.10 | Summ    | nary                                                    | 31 |

|---|------|---------|---------------------------------------------------------|----|

| 4 | Dev  | vice Ag | ging in Circuit Operation                               | 32 |

|   | 4.1  | Digita  | l and Analog Circuit Operation                          | 32 |

|   |      | 4.1.1   | Circuit Design Properties                               | 33 |

|   |      | 4.1.2   | Operation Conditions                                    | 34 |

|   |      | 4.1.3   | Impact on Device Characteristic                         | 38 |

|   |      | 4.1.4   | General Impact on Circuit Characteristic                | 43 |

|   |      | 4.1.5   | MOS Varactor Aging Behavior Model: A Case Study         | 43 |

|   | 4.2  | Advar   | nced Analog Related Aging Tests                         | 46 |

|   |      | 4.2.1   | Open Analog Related Device Aging Topics                 | 46 |

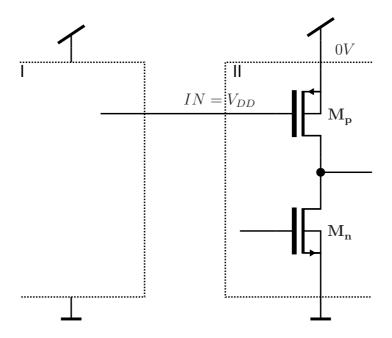

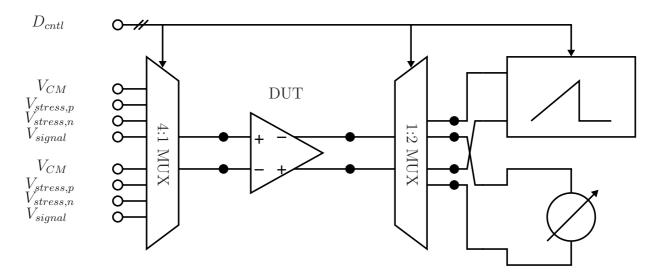

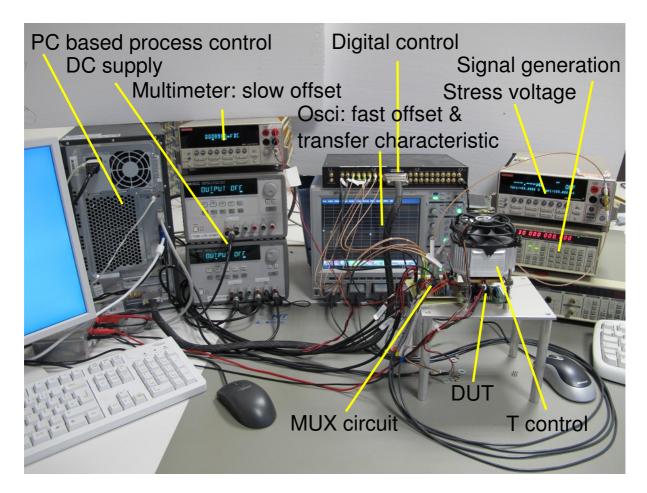

|   |      | 4.2.2   | Custom Test Circuit                                     | 47 |

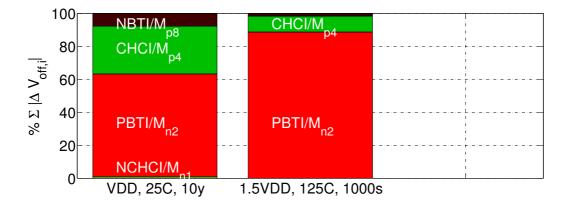

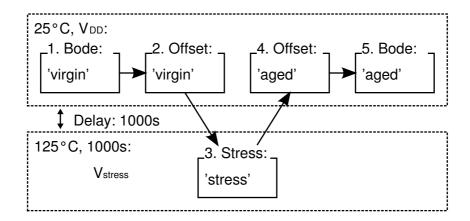

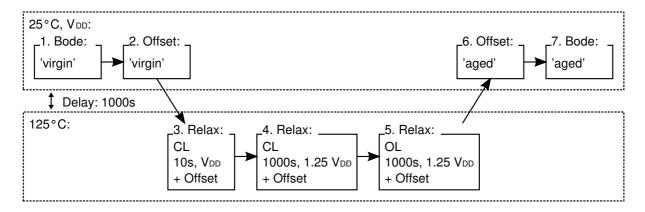

|   |      | 4.2.3   | Stress Test Approach                                    | 48 |

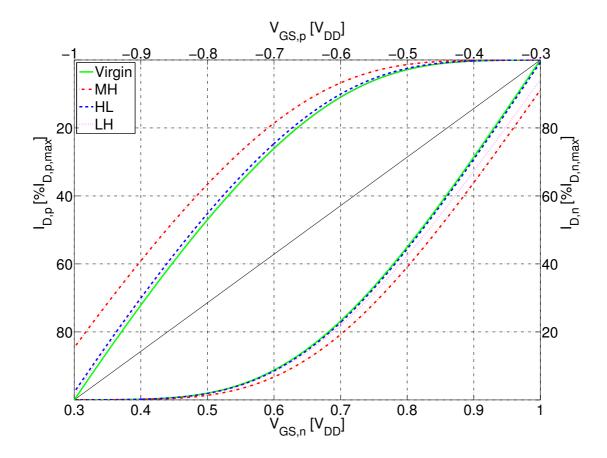

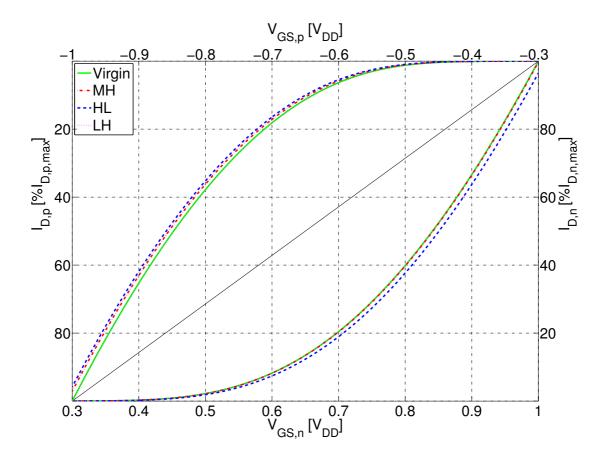

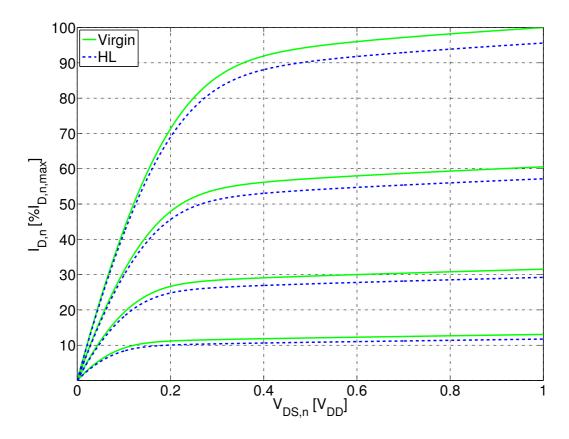

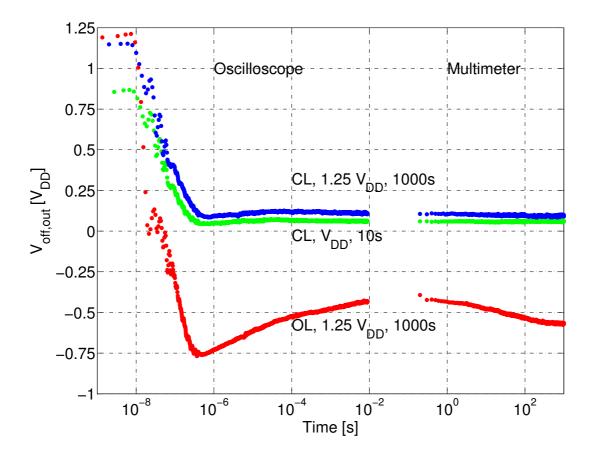

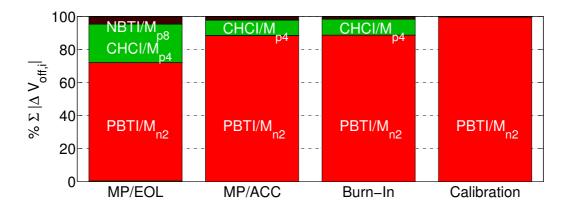

|   |      | 4.2.4   | Stress Test Evaluation                                  | 51 |

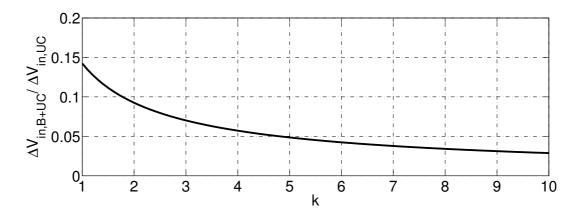

|   |      | 4.2.5   | Advanced Stress Test Evaluation                         | 59 |

|   | 4.3  | Summ    | nary                                                    | 64 |

| 5 | Cur  | rent N  | Mirrors and Reference Circuits                          | 66 |

|   | 5.1  | Basics  |                                                         | 66 |

|   | 5.2  | Curre   | nt Mirror Fundamentals                                  | 66 |

|   |      | 5.2.1   | Circuit Topology                                        | 66 |

|   |      | 5.2.2   | Design Fundamentals                                     | 67 |

|   |      | 5.2.3   | Operation Conditions                                    | 68 |

|   | 5.3  | Curre   | nt Mirror Aging Model                                   | 68 |

|   |      | 5.3.1   | Analytical Mismatch Derivation                          | 68 |

|   |      | 5.3.2   | Model Evaluation                                        | 70 |

|   | 5.4  | Refere  | ence Circuit Case Study: Self-Biasing Current Reference | 75 |

|   |      | 5.4.1   | Circuit Fundamentals                                    | 75 |

|   |      | 5.4.2   | Aging Behavior                                          | 76 |

|   |      | 5.4.3   | Transfer to General Reference Circuits                  | 77 |

|   | 5.5  | Summ    | nary                                                    |    |

| 6 | Am   | plifier | S S                                                     | 79 |

|   | 6.1  | Circui  | t Fundamentals                                          | 79 |

CONTENTS

|   |     | 6.1.1          | Amplifier Basics                                            |

|---|-----|----------------|-------------------------------------------------------------|

|   |     | 6.1.2          | Circuit Topologies                                          |

|   |     | 6.1.3          | Design Fundamentals                                         |

|   |     | 6.1.4          | Operation Conditions                                        |

|   |     | 6.1.5          | Circuit Aging and Affected Performance Parameters           |

|   |     | 6.1.6          | Aging Countermeasures                                       |

|   |     | 6.1.7          | State-of-the-Art Differential Miller Amplifier              |

|   | 6.2 | Ampli          | fier Aging Model                                            |

|   |     | 6.2.1          | Analytic Model Derivation                                   |

|   |     | 6.2.2          | Model Evaluation: Two Stage Miller Compensated Amplifier 92 |

|   | 6.3 | Stress         | Testbench                                                   |

|   | 6.4 | Advar          | aced Circuit Level Aging Approaches                         |

|   |     | 6.4.1          | Accelerated Circuit Level Aging For Test                    |

|   |     | 6.4.2          | Effect Recovery Measurements                                |

|   |     | 6.4.3          | Aging Suppression and Calibration Approach                  |

|   | 6.5 | Summ           | ary                                                         |

| 7 | IC  | Oscilla        | ators 115                                                   |

| 1 | 7.1 |                | t Fundamentals                                              |

|   | 1.1 | 7.1.1          | VCO Performance Characteristics                             |

|   |     | 7.1.1          | Design Fundamentals                                         |

|   |     | 7.1.2          | Exemplary Circuit Topologies and Design Flow                |

|   |     | 7.1.3          |                                                             |

|   |     |                | Circuit Operation induced Device Aging                      |

|   |     | 7.1.6          | State-of-the-Art LC-VCO                                     |

|   | 7.2 |                | oltage Controlled Oscillator Aging Model                    |

|   | 1.4 | 7.2.1          | Analytic Model Derivation                                   |

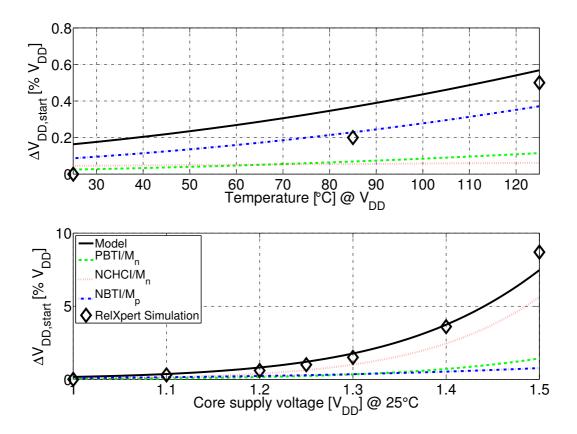

|   |     | 7.2.1          | Model Evaluation                                            |

|   | 7.3 |                | Testbench         127                                       |

|   | 7.4 |                | erated Circuit Level Aging For Test                         |

|   | 1.4 |                |                                                             |

|   |     | 7.4.1<br>7.4.2 | Aging Acceleration for LC-VCOs                              |

|   |     | 7.4.2          | Aging Use Case and Derivation of Stress Conditions          |

|   |     | 7.4.4          | Concept Evaluation                                          |

|   |     | 1.4.4          | Concept Evaluation                                          |

|              | 7.4.5 Model Prediction to Future LC-VCO Implementations | . 133 |

|--------------|---------------------------------------------------------|-------|

|              | 7.5 Summary                                             | . 134 |

| 8            | Conclusion                                              | 136   |

| Pι           | ublications by the Author                               | 150   |

| $\mathbf{A}$ | bbreviations                                            | 152   |

| Sy           | ymbols                                                  | 154   |

| A            | cknowledgment                                           | 157   |

## Chapter 2

## Introduction

#### 2.1 Motivation

Since the early days of microelectronics, integrated MOSFET (Metal Oxide Semiconductor Field Effect Transistor) technology has been continuously advanced by dimension shrink. Via the equivalent scaling of relevant processing parameters - channel area, oxide thickness and supply voltage - the fundamental device characteristic keeps the same with less area and power consumption. This general feature forms the basis of today's triumph of microelectronics and the initiation of the information era.

But CMOS (Complementary Metal Oxide Semiconductor) - the processing of n- and ptype MOSFETS on one chip - technology scaling has to face some inheritable problems like device noise and process fluctuations, that are given by semiconductor physics, processing imperfections and its atomic limitations. For example, the circuit relevant SNR (Signal to Noise Ratio) reduces for every technology step as voltage headroom is reduced with decreased supply voltage, but device noise contributions remain constant. Since the 0.1 um regime, CMOS processing migrates to the non-constant field scaling approach, by keeping the supply voltage at higher levels than would be required by the scaling factor, while all other parameters are scaled in the usual way. Here, raised electric fields in MOS devices are accepted at the cost of increased wearout, thus worsening device reliability but maintaining sufficient SNR. At the same time, higher integration rates with increased chip complexity demand for an enhanced device reliability to maintain a stable and reliable system, which has to be further provided by the CMOS processing. In the past, this was achieved by the continuing optimization of the chip processing, but the gap between the optimization window and limiting semiconductor physics reduces and device aging mechanisms come to the fore.

Condensed operation of MOSFET devices at only slightly reduced supply voltages further leads to increased on-chip operation temperatures, that even worsen device we arout. On the other hand, reduction in voltage headroom increases circuit sensitivity towards device aging. Advanced CMOS processing options like the inclusion of novel high- $\kappa$  materials into the MOS gate stack lowers gate leakage, but further debuts device aging effects that were nonexistent in classic  $SiO_2$  or SiON based CMOS technologies. The general shrink of channel length further induces novel aging effects, that even occur for switched off devices. Increased circuit sensitivity and growing appearance of aging effects in magnitude and number involve the reliability topic as an emerging concern in today's and future CMOS microelectronics [1, 2].

The impact of device wearout on circuit level was only rudimentary studied in the past, as occurring minor device parameter drifts were covered by design techniques like guard banding or mitigated by the operation in safe operation area. Contrary to the inherently robust digital circuits, where device wearout mainly leads to an increase of switching delay, analog circuitry is more sensitive towards a change of device characteristics like drive current, transconductance or noise behavior. The requested compliance of numerous circuit performance specifications to maintain proper system functionality makes reliability proofs for analog circuits more challenging. With the increased appearance of device aging effects in advanced CMOS technologies, their impact on circuit level demands for future research effort [3]. But also circuit level reliability measurement proofs arise as a challenging task, as an accelerated stress methodology to exactly reproduce equivalent end-of-lifetime states is still missing.

### 2.2 State-of-the-Art in Circuit Reliability Research

Previous circuit design mostly treated device aging as a side effect, that is covered by design margins applied for balancing PVT (Process Voltage Temperature) variations. Nowadays, device aging obtained an individual status as growing source of device variability in the extension to PVTA (Process Voltage Temperature Aging) variations. Growing interest on device degradation lead to several studies on the impact of device aging on circuit level. For digital logic circuits the general aging induced weakening of the device characteristic increases logic gates' switching delay and so induces a time dependent degradation of the data evaluation. This increase of propagation delay can lead to a time dependent violation of timing constraints in the critical path and so to failure of the circuitry [4, 5, 6]. Several detection and sensing approaches, for example using replica circuits to provide a kind of aging odometer [7], are developed and countermeasures are proposed [8]. A general approach to detect and compensate for PVTA variation induced logic errors is treated in [9]. Another relevant field of research is the digital SRAM (Static Random Access Memory), as reliable data storage has to be guaranteed with minimum feature size devices for millions of cells. Reliability investigations revealed, that device degradation in the asymmetric storage state varies SRAM cell stability [10, 11]. Due to the minimum feature size devices, process variations and variations in the degradation effect as well play an important role for the reliability of the storage system. Transient components in device degradations additionally include a time dependent component for the cell stability [12].

For analog and mixed-signal circuits, performance characteristics and thus device aging impacts are more complex [13]. Especially for circuit designs in advanced high- $\kappa$  CMOS nodes, the aggravated device aging demands for novel and detailed studies [14]. For analog circuits, a most essential constraint is device matching, that can be changed by the device degradation [15, 16] and can be seen as another source of variation additional to

process variations [17, 18]. The investigation of Agostinelli on a differential amplifier revealed that asymmetric stress operation induces device mismatch and thus induces circuit offset [16]. In the study on selected amplifiers of Martin-Martinez, variability is identified as the major concern for advanced CMOS technologies, which is accompanied by aging induced drift contributions. Variability in the aging effect itself was found to be of minor concern. The study further reveals that aging impacts amplifier gain and GBW (Gain Band Width) dependent on the circuit topology [19]. A detailed investigation on the effect variability for the used devices as well as a general statement on aging sensitive topologies is still missing. In the fundamental work of Thewes, a state-of-the-art differential amplifier is used to study analog circuit reliability according to numerous aging effects. From the point of view of distinct circuit operation states, occurring device stress and resulting aging effects are determined. Aging effects are again expected to degrade circuit performance in offset, gain, noise and linearity. Here, BTI (Bias Temperature Instability) effects, induced by high oxide fields, are expected to arise as the most prominent challenges in future robust circuit design [20]. In the work of Kawasumi, HCI (<u>Hot-C</u>arrier Injection) is beneficially used to perform calibration of an SRAM sense amplifier [21]. With an automated reliability simulator, an ADC (Analog to Digital Converter) circuit is studied with respect to the impact of device aging by Yan [22]. Several countermeasures like device sizing for improved HCI degradation or a reduction of power consumption to reduce NBTI (Negative Bias Temperature Instability) aging are evaluated. Nevertheless, a deep understanding of the interaction between device degradation and circuit behavior is still missing.

In [23], Jha investigated the impact of NBTI on selected basic analog circuit blocks like current mirrors, amplifiers and a current-steering DAC (Digital to Analog Converter). The study showed that device aging impact strongly depends on the circuit topology. For the current mirror circuits for example, huge differences in general aging sensitivity can be seen. Investigations on amplifier circuits reveal large aging induced offset generation for open-loop comparator operation. Due to stable current biasing, transconductance of the circuit remains stable and further impact on performance parameters like gain or GBW are small. For the current-steering DAC, NBTI degradation is expected to induce considerable gain errors, but only minor impact on its linearity. This study shows that sensitivity of the analog circuit strongly depends on its configuration. However, universal rules for aging robust circuitry are not provided.

Further analog circuit types, that are in the focus of reliability investigations, are LC based VCO (Voltage Controlled Oscillator) circuits. This is mainly due to the high voltage swings during circuit operation [24, 25]. In his study, Lin revealed considerable VCO performance degradations related to HCI device degradation [26]. Sadat showed in [27] that degradation of active bridge devices impacts oscillation amplitude and thus the effective value of the tank capacitance, that further modifies oscillator Phase Noise and startup behavior. Current-reusing CMOS VCO designs are determined to be the most reliable oscillator topologies due to amplitude limitation by the voltage supply. In [28], Reddy reported a significant VCO Phase Noise degradation in the close-in region related to a NCHCI (Non-Conductive Hot-Carrier Injection) induced worsening in device flicker noise - a device characteristic, that is typically not considered in todays aging prediction models.

Several studies in the past years showed the increasing impact of device aging on analog circuit blocks and further brought up the most critical analog circuit types. Nevertheless, a throughout and universal study performed on state-of-the-art analog circuit designs, providing insight into the mechanisms of the circuit related impact of device aging, is still missing. Analog circuit related device aging taking into consideration typical device dimensions and operation states has to be investigated in detail for advanced CMOS technologies, to reveal analog related degradation behavior as well as expected variations of the aging mechanisms. Selected circuit designs have to be investigated with respect to their general aging sensitivity to establish approaches for future robust circuit designs. Novel circuit aging modeling approaches, expanding results from circuit reliability simulations, will provide deep understanding of device aging and circuit interaction and will break new ground for aging countermeasures and circuit stress testing as well.

#### 2.3 Contributions of this Work

In this work a detailed overview over major device aging effects, leading to parametric drifts of device characteristics, but not to a hard destruction of the device is provided. Most recent findings on distinct effect physics and resulting aging prediction model approaches are discussed. Options for consideration of device degradation in classic circuit simulations are reviewed with respect to analog circuit simulation suitability.

Device aging for typical analog operation scenarios for an advanced CMOS process technology is studied by simulation and stress measurements. In doing so, analog related device aging - not entirely covered by state-of-the-art modeling - is investigated in detail, taking into consideration typical operation states, device dimensions and analog relevant effect properties. Operation modes like accumulation, which are not considered so far and potentially occur during circuit standby, are shown to be another significant reliability issue. Further investigations on aging effect variability as well as transient recovery reveal the need for novel aging models, that are close to the basing physics. Additionally, it is shown that degradation effects can be beneficially used also for passive reliability improvement.

Throughout investigations on device aging impact on a wide area of analog circuit building blocks are the foundation for a general overview of major circuit aging monitors and the behavior dependent on the operation state. For instance, current mirror circuits experience current mismatch, amplifiers offset and oscillators power degradation. Further case studies on distinct device and circuit types like varactors and reference generation circuits showed a minor impact of device wearout.

Circuit level aging is very complex, due to the simultaneous interaction of distinct device degradation effects and distinct dominant effects are not per se detectable. A general methodology to accurately predict aging on circuit level is performed via fully analytic modeling of circuit behavior, that further provides a deep insight into major effect contributions. This approach allows to derive further aging related design concepts and to easily account for circuit level degradation in future CMOS process technologies.

Via circuit degradation models, a methodology to accurately determine end-of-lifetime equivalent circuit states for accelerated stress test is developed and validated via mea-

surement for selected circuit types. Furthermore, customized circuit type specific stress testbenches are developed and described providing the ability to stress and measure circuit performance in one test setup. This novel approach allows to use analog circuits' signal sensitivity for further aging effect characterisation, like device flicker noise degradation in oscillator Phase Noise behavior or short-time recovery in fast amplifier circuits. Design related aging countermeasures for reliable analog circuit operation are proposed and evaluated. Furthermore, a novel method to suppress device aging and simultaneously use the induced device parameter drift for circuit calibration is proposed and verified via measurements. From the overall findings and circuit investigations, guidelines for design of reliable analog circuits are established.

The throughout and general investigation on the complex impact of device degradation in state-of-the-art analog circuitry provides together with the proposed circuit aging modeling, stress test evaluations and countermeasures a novel and fundamental basis to handle the emerging reliability topic for analog circuit design.

## Chapter 3

## **Aging Physics**

### 3.1 CMOS Device Wearout

As most technical products, also integrated CMOS devices suffer from wearout due to their usage in electronic devices. High integration in today's ICs (Integrated Circuits), with billions of MOS transistors on one die, demands MOS (Metal Oxide Semiconductor) insulator thickness of a few nanometers between the controlling gate and the channel. Electric fields across the oxide reach MV/cm although operating in the 1V regime. Those lead to a time dependent wearout of insulators' properties inducing changes in the device characteristics or in worst case to its breakdown. As mentioned in 2.1, technology scaling by inducing non-constant field scaling and inclusion of new materials in the gate stack worsens this wearout from technology node to node.

Aging mechanisms can be separated in two groups: mechanisms leading to drift of device characteristics, but not to an immediate malfunction of the transistor - the so called *non-destructive* aging mechanisms, including BTI and HCI effects. And the *destructive* mechanisms like TDDB (<u>Time Dependent Dielectric Breakdown</u>)[29, 30] leading to a permanent malfunction of the device. Precursors to the TDDB are the SBD (<u>Soft Breakdown</u>) effects inducing a temporary breakdown of the device. After stress removal, device is working again.

Our investigation on analog circuit aging addresses the *non-destructive* aging mechanisms, as those are able to change circuit behavior during lifetime operation. In advance to a dielectric breakdown a huge amount of parameter drift occurs, also acting as a precursor to the hard breakdown. From the system point of view it is not only the hard breakdown of an incorporated device leading to malfunction, but also drifts in performance specifications of the analog circuit can lead to failure of the overall system.

## 3.2 Impact on Device Parameters

All non-destructive aging mechanisms have in common that insulator wearout is due to inclusion of charge into the insulator region. This additional charge changes device

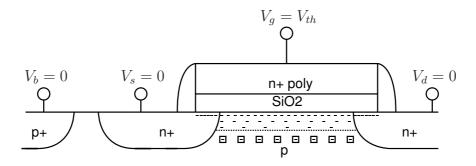

characteristic in several ways. As derived in lots of semiconductor textbooks, threshold voltage  $V_{th}$  of an exemplary nMOS (see fig. 3.1) with zero Bulk-Source voltage  $V_{BS} = 0$  is defined as the inversion mode Gate voltage where electron (minority carrier) density in the inversion region is equal to hole (majority carrier) density of the bulk in thermal equilibrium [31, 32].

The physical representation of the threshold voltage condition is given by

Fig. 3.1: nMOS: threshold voltage virgin device

$$V_{th} = V_{FB} + 2\Phi_F + \gamma_n \sqrt{2\Phi_F} \tag{3.1}$$

with  $V_{FB}$  the flatband voltage,  $\Phi_F$  the Fermi level from intrinsic Fermi level and  $\gamma_n$  the Body factor for a nMOSFET, that is dependent on the bulk doping and the dielectric constant of the insulator.

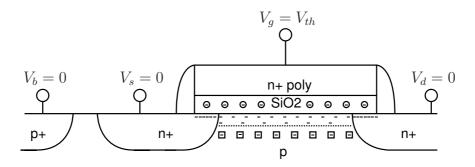

A uniformly distributed charge  $Q_{deg}$  in the interface to the insulator, as depicted in fig.

Fig. 3.2: nMOS: threshold voltage degraded device

#### 3.2, would shift the flatband voltage to

$$V_{FB} = \Phi_{MS} - \frac{Q_{deg}}{C_{oxide}} \tag{3.2}$$

with  $\Phi_{MS}$  the workfunction difference between gate material and bulk and  $C_{oxide}$  the gate oxide capacitance. Depending on the amount of generated charge,  $V_{FB}$  and so  $V_{th}$  is shifted by

$$\Delta V_{th,n} = \Delta V_{FB} = -\frac{Q_{deg}}{C_{cride}}.$$

(3.3)

Equation (3.3) also shows that the direction of the  $V_{th}$  shift depends on the polarity of the generated charge.

Furthermore, induced oxide charges also impact field dependent effective channel mobility  $\mu_{eff}$ . Equation (3.4) shows the relation of  $\mu_{eff}$  with respect to device operation condition.

$$\mu_{eff} = \frac{\mu_0}{1 + \Theta(V_q - V_{th,n})} \tag{3.4}$$

with  $\mu_0$  the low field surface mobility,  $\Theta$  the mobility degradation coefficient and  $V_g$  the gate voltage. Equation (3.4) reveals a direct relation of  $\mu_{eff}$  to a drift in threshold voltage [33]. But also  $\mu_0$  can be affected by oxide charges at the  $Si-SiO_2$  interface acting as Coulomb scattering centers and changing the interface roughness and hence  $\mu_0$  and  $\Theta$  [34]. The often discussed degradation of further device parameters as drain current  $I_D$ , transconductance  $g_m$ , subthreshold swing SS or MOS C-V characteristic can be related to the drift of basic MOS parameters  $V_{th}$  and  $\mu_0$ . These general impacts of device wearout were derived for an exemplary nMOS device, but are also valid for the pMOS counterpart.

## 3.3 Bias Temperature Instability (BTI)

NBTI for pMOS as well as PBTI (<u>Positive Bias Temperature Instability</u>) for nMOS transistors are derived from the typical inversion mode operation of CMOS devices and their degradation behavior under elevated temperatures. Both effects lead to a general weakening of the transistor characteristic. BTI degradation is strongly dependent on the oxide field given by eq. (3.5) for strong inversion,

$$F_{el,ox} = \frac{V_g - V_{FB} - 2\Phi_F}{t_{ox}} \tag{3.5}$$

with  $V_{FB}$  the flatband voltage,  $\Phi_F$  the Fermi Potential defined by the well doping and the lattice temperature and  $t_{ox}$  the insulator thickness. As shown by eq. (3.5),  $V_g$  and  $t_{ox}$  are key parameters for the BTI degradation.

BTI effects, especially the NBTI in pMOS transistors, were already observed in the early days of MOSFET development [35]. In this decade NBTI was not concerned as a major reliability issue as impact on the formerly buried channel with n+ poly gate for the pMOS was small. Due to constant field scaling in CMOS technology development, that means a similar scaling of  $V_g$  and  $t_{ox}$ , NBTI was well controlled. Changeover to surface channel p+ poly gate pMOSFET increased the NBTI sensitivity. Particularly, the introduction of non-constant field scaling in sub-0.1 $\mu$  CMOS technologies, typically keeping or slightly decreasing  $V_g$  but scaling  $t_{ox}$  in the classic manner, enhanced NBTI as one major degradation mechanism. A corresponding PBTI for nMOS transistor was negligibly small for  $SiO_2$  based oxides, but emerged with the introduction of high- $\kappa$  materials in advanced CMOS technologies also for the nMOS transistor [36].

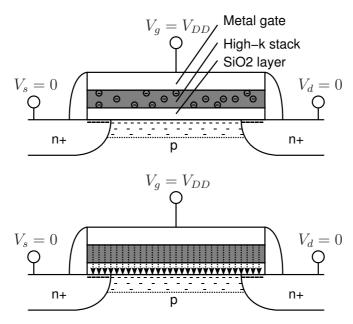

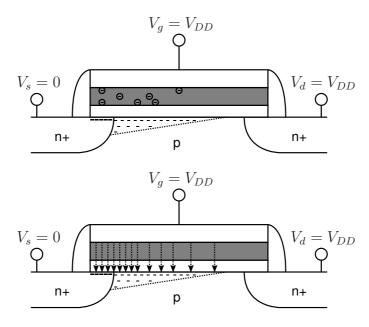

Fig. 3.3: pMOS in triode operation: NBTI stress generated defects and arising electric field under NBTI stress

#### 3.3.1 NBTI in pMOSFETs

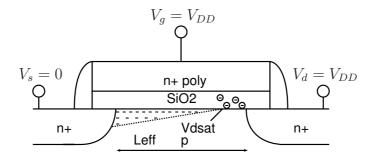

Figure 3.3 shows the inversion mode NBTI stress condition and the resulting oxide degradation for an exemplary pMOSFET - the transistor's deep triode region with zero voltage drop over the channel. Source, Drain and Substrate are connected to ground and  $V_g$  is set to a high negative value inducing an inversion layer in the n-well and an accumulation layer in the Source and Drain overlap regions. The electric field in the insulator on the inverted channel is given by eq. (3.5). Under high  $F_{el,ox}$ , oxide quality degrades by the trapping of charge. Insulator degradation also happens in the Source/Drain overlap regions, but with minor impact due to the distance to the controlled inversion channel. Fig. 3.4 shows the situation for a pMOS device in saturation region. Also in this operation mode NBTI degradation occurs, but due to the decreasing electric field from the Source to the Drain region with smaller total degradation [34].

Lots of literature on NBTI and its involved mechanisms for differing CMOS gate stacks is available. Due to strong sensitivity towards processing and included materials, lots of differing degradation numbers and effect explanations exist. The general accepted mechanisms are the generation of *interface states* at the substrate oxide interface and the electric activation of *oxide charges*, that is due to the activation of pre-existing defects or generation of new defects in the insulator [37]. According to one theory, an interface state is created by the release of hydrogen saturating an open Si bond at the substrate oxide interface. The remaining *dangling bond* is an electrically active defect with an energy distribution throughout the Si bandgap. It can be occupied by an electron or hole, but for pMOS in inversion mode it is positively charged [38]. The electric field induces a diffusion of the remaining hydrogen through the insulator. As this interface state generation process was believed to be the dominant NBTI contributor, the widely-used RD (Reaction Diffusion) model was developed for NBTI prediction [39]. More recently, oxide

Fig. 3.4: pMOS in saturation operation: NBTI stress generated defects and arising electric field under NBTI stress

charges were believed to be dominant to NBTI. These traps are neutral when discharged and are positively charged when occupied by holes. Former modeling explained positive oxide charge is due to trapping of  $H^+$  from the RD process, but recent findings revealed that hole traps and their precursors already exist in the oxide before stress is applied [40].

NBTI recovery was controversially discussed for long times, but its investigations revealed a deeper understanding of NBTI degradation mechanisms. As recovery immediately sets in when stress is removed, the time delay between stress and aging monitor measurement is very important. This undefined delay in published NBTI data is also one origin of the lack in NBTI understanding. In recent years a lot of effort was performed measuring degradation during stress to find the whole amount of contributing effects [41, 42, 43, 44]. Early understandings divided NBTI characteristic into two components, a recovering one and a permanent part. Controversial results assigned effect recovery to passivation of interface traps [45] or hole detrapping [42]. Also investigations for enhanced recovery under accumulation mode did not reveal a distinct recovery origin [46, 47]. Reisinger's ultra-fast  $V_{th}$  measurement method to monitor recovery after stress, revealed for small dimension devices a stepwise recovery curve indicating the discharge of single defects with differing contributions in step size, which can be related to the random position of channel dopants and insulator defects. In a large area device this single defect recovery is masked by the huge number of defects and the small impact of each defect recovery to the overall device  $V_{th}$ , leading to the classic  $\log(t)$  NBTI recovery behavior, which is incompatible with the RD model [48]. Defect relaxation behavior was related to the model of low frequency noise/flicker noise or its manifestation as RTN (Random Telegraph Noise) and extended to the BTI timing range with individual capture and emission times for each defect [49, 50, 48]. With the adapted RTN characterisation technique TDDS (<u>Time Dependend Defect Spectrocopy</u>) from Grasser, it was shown that general BTI is due to a thermally activated capture and emission of holes and electrons in oxide traps - called SOT (Switching Oxide Traps) [40, 51]. Capture and emission time constants are vastly distributed from nanoseconds to months or even longer. Investigations revealed that metastable states of these defects contribute an additional noise portion and scaling to nanometer devices can lead to very large induced variations due to high defect step sizes of a very small number of defects per device.

Changing the insulator materials from  $SiO_2$  to SiON or high- $\kappa$  stacks also changes the NBTI degradation. For SiON devices nitrogen portions should be located rather to the Gate/insulator than to the substrate/insulator interface for improved NBTI degradation [38]. High-k based gate stacks also show similar NBTI degradations compared to  $SiO_2$  and SiON data [52]. Fernandez showed that NBTI is strongly DF (Duty Factor) dependent, but shows a flat AC degradation behavior up to the GHz range [53], which is in line with SOT model from Grasser. From recent findings, Kaczer proposes to migrate to SiGe buried channel pMOSFETs to guarantee limited NBTI/pMOS degradation in future CMOS technology nodes [37].

#### 3.3.2 PBTI in nMOSFETs

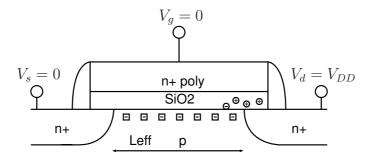

Corresponding to pMOSFET's NBTI, a PBTI arise in nMOSFETs in inversion operation. PBTI degradation was negligibly small in  $SiO_2$  and SiON technologies, but arises with similar orders of magnitudes in high-k technologies. Fig. 3.5 shows the inversion

Fig. 3.5: High- $\kappa$  nMOS in triode operation: PBTI stress generated defects and arising electric field under PBTI stress

mode stress condition and its degraded insulator in deep triode region for an exemplary high- $\kappa$  nMOS. Contrary to classic pMOS/NBTI, oxide degradation occurs in the high- $\kappa$  portion of the Gate stack [36]. Due to intermediate  $SiO_2$  layers at the substrate insulator interface, nMOS/PBTI degradation is located in a certain distance from the inversion

channel, thus mainly impacting threshold voltage  $V_{th}$  with almost no effect on channel mobility  $\mu_0$  [54]. Similarly to NBTI/pMOS degradation, also PBTI/nMOS shows a concentrated degradation near the Source in saturation operation resulting in a reduced total degradation compared to the deep triode region operation (see fig. 3.6).

As nMOS/PBTI in high- $\kappa$  processes compared to pMOS/NBTI is a very new type of

Fig. 3.6: High- $\kappa$  nMOS in saturation operation: PBTI stress generated defects and arising electric field under PBTI stress

degradation mechanism and due to the controversial discussion and explanation for the classic pMOS/NBTI, most BTI related investigations concentrate on a deeper understanding of pMOS/NBTI. Nevertheless, there is a general consensus that nMOS/PBTI degradation is due to charge trapping in the high- $\kappa$  or related capping layers [55, 56, 57, 36]. High- $\kappa$  CMOS processing - especially the gate stack with its specific arrangement of interface and capping layers - is a very confidential matter of semiconductor companies. Due to specific processing, differing nMOS/PBTI degradation results are available. Some investigations report a PBTI turnover phenomenon - an enhancement or weakening of the nMOS characteristic as a function on time depending on the bias and temperature stress condition. This observation indicates a multiple polarity defect trapping [58, 59]. Recent results for  $HfO_2$  based high- $\kappa$  processes linked the major parts of PBTI degradation to electron trapping at oxygen vacancies [37]. Early investigations on nMOS/PBTI tried to model PBTI degradation with an adapted RD explanation from NBTI modeling, but neglected PBTI relaxation phenomena [58]. nMOS/PBTI relaxation is similar to pMOS/NBTI behavior, showing defect relaxation in a vast timescale from sub-microseconds to months. The promising SOT approach also fits well for PBTI degradation, its relaxation behavior and AC voltage stress degradation dependency [40, 55]. A possible option to reduce nMOS/PBTI degradation in  $HfO_2$  based processes is the inclusion of group III elements to passivate oxygen vacancies [60].

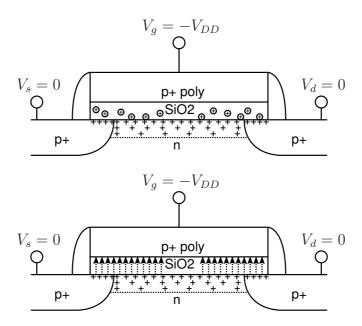

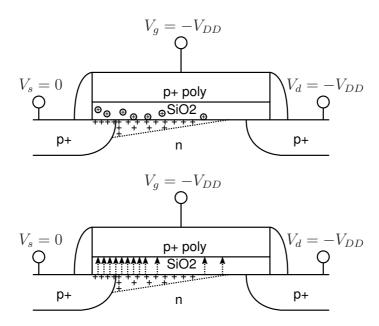

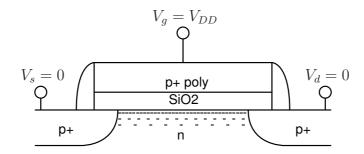

#### 3.3.3 PBTI/pMOS and NBTI/nMOS

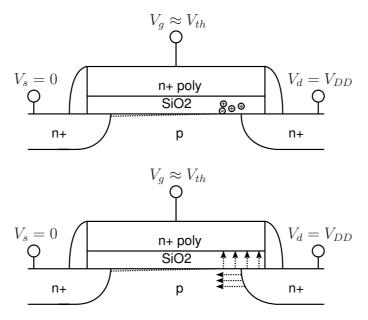

The accumulation mode is very uncommon for CMOS devices, as this operation does not exhibit a Gate controlled current flow from the Drain to the Source node and requires a reverse sign of the Gate to substrate voltage. In classic CMOS digital logic, accumulation mode does not appear, but can arise in analog circuits. Due to its rarity, accumulation mode aging is rated as a minor reliability issue by the device reliability community and only small numbers of investigations exist.

Fig. 3.7 and fig. 3.8 depict exemplary SD MOSFETs in accumulation operation. Negative

Fig. 3.7: nMOS in accumulation NBTI stress mode

Fig. 3.8: pMOS in accumulation PBTI stress mode

Gate voltage for the nMOS and positive voltage for the pMOS induce an electric field over the oxide and majority carriers form an accumulation layer under the Gate. As shown in [42] and [61], also accumulation mode causes device degradation. A detailed investigation on NBTI aging results for equal negative voltage bias on nMOS and pMOS devices is given in [38]. Proposed explanations for the differing degradation magnitudes are related to different surface potentials and its dependence on interface traps charge, differing hydrogen diffusion or the different work functions for pMOS and nMOS. Accumulation mode is still used in BTI relaxation measurements to accelerate defect recovery and separate between distinct defects [62]. Nevertheless, involved microscopic mechanisms and detailed impacts on device characteristic are poorly understood.

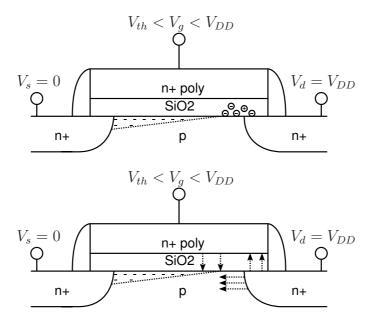

#### Hot-Carrier Injection (HCI) 3.4

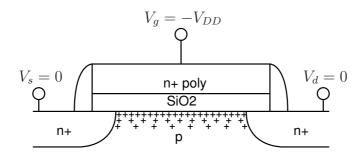

Hot-Carrier degradation affects both transistor types, nMOSFETs and pMOSFETs. It is the corresponding degradation effect to BTI where a high vertical electric field induces insulator wearout. For HCI it is the lateral electric field causing the degradation, so it arises for high Drain-Source voltages  $V_{DS}$  in combination with short Gate lengths L. In contrast to BTI degradation, HCI induces an asymmetric insulator wearout concentrated in the Drain region and thus makes degradation modeling more challenging. The name hot-carrier is historically grown. It describes the acceleration of carriers under an electric field gaining kinetic energy higher than the lattice in thermal equilibrium: these carriers are called hot. Hot carriers exhibit enough energy to induce impact ionisation, generation of interface states or even surmount the insulator barrier and generate oxide defects or get trapped [63]. Injection rates are typically measured via substrate current  $I_B$ , induced by impact ionisation, or Gate current  $I_G$ . Only a small part of the hot carriers get trapped and contribute to the intrinsic HCI degradation. A sufficient high lateral electric field for hot carrier generation emerges in MOSFET saturation region between channel pinch-off and drain junction. Hot carrier degradation in this operation is called CHCI (Conductive Hot-Carrier Injection). The CHCI generation condition is given in fig. 3.9 for an exemplary nMOS device. The degradation generating lateral electric field is generally related to the device channel length  $L_{eff}$  and the voltage difference between the drain node and the pinch-off point. Voltage stress conditions are more complicated for HCI than for the BTI effects as the lateral field depends on both, the Drain-Source voltage  $V_{DS}$ and the channel controlling Gate-Source voltage  $V_{GS}$ , defining the pinch-off point with  $V_{DSAT} = V_{GS} - V_{th}$  [32]. Furthermore,  $V_{GS}$  to  $V_{DS}$  relations control directions of the oxide field in the drain region and so the polarity of defect trapping. CHCI degradation can generate different polarities of charge at the same time. The measured total degradation is defined by the dominant effect or the resulting combination of all generated defects.

Hot-Carrier degradation became a major reliability issue for nMOS devices in the late

Fig. 3.9: nMOS in saturation inducing CHCI degradation

1970s and a lot of research was conducted in the 1980s. In these days the commonly used LEM (<u>Lucky Electron Model</u>) was developed, which is still used in lots of reliability simulation tools [64]. It provides the correct prediction of CHCI degradation down to the  $0.25\mu m$  range. With further scaling the LEM reaches its limitations and is no longer valid to describe measured hot carrier degradations. For example, for  $V_{DS} < 1.3V$ , LEM does not predict impact ionization or hot carrier damage anymore, although both are proven by measurements. To describe hot carrier behavior for the nanoscale regime, the EDM (Energy Driven Model) was proposed, including further acceleration effects like electron-electron scattering [65]. For extremely short channel lengths of a few 10nm a NCHCI emerges between Source and Drain junction even for switched-off devices caused by hot-carriers in the sub-threshold current (see fig. 3.10).

HCI counteractive process developments - generally known as drain engineering - reduce

Fig. 3.10: nMOS in off-state inducing NCHCI degradation

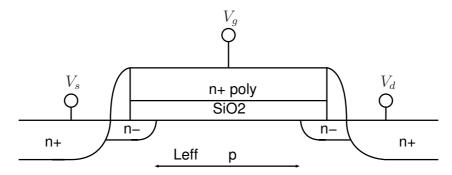

electric fields in the Drain region and result in well controlled CHCI degradations. The commonly used LDD (<u>Lightly Doped Drain</u>) technique (see fig. 3.11) reduces peaks in the lateral electric field via inclusion of low doped n- regions at the Drain and Source junction, but at the expense of higher Drain-/Source resistance [66].

One challenging part of hot carrier stress characterisation is the simultaneous generation of BTI induced degradation - especially at high temperatures - and their further separation. Shifts of peak CHCI degradations to high  $V_{GS}$  aggravates BTI contributions, making hot carrier characterisation more challenging. Similar to BTI measurements, effect recovery was also observed in CHCI investigations, but is mostly related to BTI included components [67, 68].

Fig. 3.11: Cross-section of an exemplary LDD nMOSFET

### 3.4.1 Conductive Hot-Carrier Injection in nMOSFETs

CHCI degradation for  $SiO_2$  nMOSFETs can be separated in three regimes depending on the gate bias  $V_{GS}$  and the resulting oxide field condition in the Drain region -  $V_{DS}$  is expected to be high. In all regimes hot carriers generate interface states with a peak at  $V_{GS} = \frac{1}{2}V_{DS}$ . Their impact on device characteristic interfere with the other parameter shifting mechanisms. For low  $V_{GS} \approx V_{th}$  the oxide field in the Drain region assists hole trapping as can be seen in fig. 3.12. In the mid-range  $V_{th} < V_{GS} < V_{DS}$  hole and electron

Fig. 3.12: nMOSFET CHCI with  $V_{GS} \approx V_{th}$  and  $V_{DS} = V_{DD}$

Fig. 3.13: nMOSFET CHCI with  $V_{th} < V_{GS} < V_{DS}$  and  $V_{DS} = V_{DD}$

injection interfere and partially compensate (see fig. 3.13). For high  $V_{GS} \approx V_{DS}$  electron injection forms the major part (see fig. 3.14). For recent technologies the role of the charge injection drops and interface state generation becomes the dominant mechanism [63]. Furthermore, scaling shifts the interface state generation peak to  $V_{GS} = V_{DS}$  due to

Fig. 3.14: nMOSFET CHCI with  $V_{GS} = V_{DS}$  and  $V_{DS} = V_{DD}$

energy related 'short channel' effects, like increased electron-electron scattering [69]. Changeover to high- $\kappa$  gate materials does not change the intrinsic nMOS/CHCI behavior, but due to peak value shifts to the high  $V_{GS}$  range additional PBTI components arise, that have to be separated from the intrinsic CHCI effect [70].

### 3.4.2 Conductive Hot-Carrier Injection in pMOSFETs

CHCI situation for classic  $SiO_2$  pMOSFETs is very similar to the nMOS degradation, but with differing mechanism contributions. As electric fields are only inverse to the nMOS, a schematic visualisation is omitted. For pMOS major CHCI contributions are related to generated interface states peaking at  $V_{DS} = V_{GS}$ . For high  $V_{DS}$  and  $V_{GS} \approx V_{th}$ , electron trapping is induced in the Drain region by filling of pre-existing defects in the oxide. For recent technologies this is more and more reduced as thin oxides are less sensitive for electron trapping. In the region  $V_{GS} < V_{th}$ , hot holes become the dominant mechanism inducing hole trapping in the oxide and the generation of interface states [63].

Device scaling further emerges a secondary effect that gets dominant for DC stress conditions. The so-called LSHA (<u>Local Self-Heating Activated</u>) NBTI is an local enhanced NBTI degradation due to self-heating at the Drain side under CHCI stress conditions [71, 72]. A distinct model for the LSHA effect does not exist until today due to the lack of understanding of the involved self-heating time constants.

Early investigation on pMOS/CHCI for high- $\kappa$  technologies showed an increased device degradation, but with similar  $V_{GS}$  and  $V_{DS}$  behavior compared to ultra-short  $SiO_2$  counterparts. Larger degradation is related to the lower quality of the interfacial oxide layer [68] and should be improved during further process development.

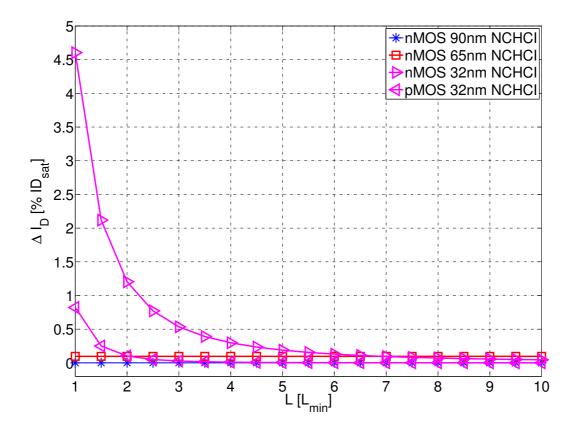

# 3.4.3 Non-Conductive Hot-Carrier Injection in nMOSFETs and pMOSFETs

NCHCI or off-state degradation occurs for a switched-off MOSFET, that means  $0 \le |V_{GS}| < |V_{th}|$  and high  $|V_{DS}|$ . The NCHCI scales with the gate length and arise as a significant reliability issue in nanoscale technologies [73]. Surprisingly, there exists only a small number of published investigations on this emerging topic. The source of the observed degradation is the gate length dependent channel leakage current. Drain diode leakage current has proven to have minor impacts [74]. For both device types oxide degradation occurs in the drain region [74, 75]. In [76], Muehlhoff reported for nMOS devices hole trapping in the middle of the channel and electron trapping near the Drain, dependent on the oxide thickness. For thin oxides the hole trapping mechanism disappears. In contrast, Hofmann reports interface state generation and electron trapping resulting in a negative charge buildup [75]. But also for pMOS transistors under off-state stress electron trapping is reported leading to a current increase [74].

The NCHCI investigations and their differing results show the typical aging effect individuality of measured device degradations. Their involved mechanisms and contributions are strongly related to the investigated CMOS process technology and result in individual aging behavior. So, a very general assignment of device wearout to an inducing mechanism can not be performed and has to be investigated for each CMOS process individually.

## 3.5 Aging Effect Modeling

Aging effect modeling can be divided into two fields: the aging effect degradation prediction and the subsequent integration for circuit simulators. Aging prediction models try to map aging physics in more or less complex model equations depending on the aging stress parameters voltage V or current I, temperature T and time t as well as further technology or design related parameters like equivalent oxide thickness  $t_{ox}$  or device dimensions W and L.

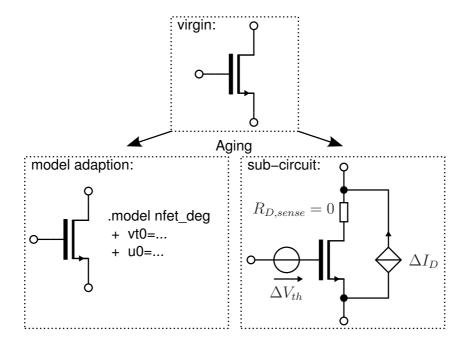

For circuit level reliability simulations, the evaluated parameter shifts have to be integrated into classic circuit simulator netlist descriptions. The two common state-of-the-art approaches are depicted in fig. 3.15. For the first one, evaluated degradation for each device in the circuit is mapped in an individually adapted model card. The second approach bases on the usage of an individual sub-circuit to reproduce degraded device characteristic via the two additional sources mapping a  $\Delta V_{th}$  and a  $\Delta I_D$ . The inserted  $R_{sense} = 0\Omega$  resistor is used to sense the Drain current to control the feedback current source. The sub-circuit approach is limited to a general shift on the x-axes  $(\Delta V_{th})$  and an adaption of the current slope  $(\Delta I_D)$  of the transistor characteristic. Compared to the model card adaption approach, a sub-circuit model provides less degrees of modeling freedom in terms of the number of affected MOSFET parameters. On the other hand it provides a more simple and comprehensible way of simulation level inclusion for the circuit designer. The given implementations in fig. 3.15 only support permanent degradations. Contrary to the

Fig. 3.15: Device aging modeling approaches for circuit simulation: device model card adaption or sub-circuit model.

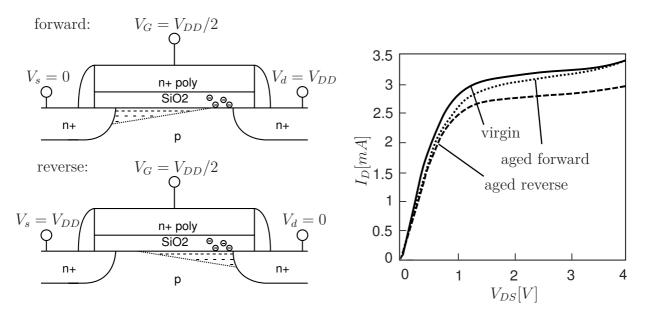

sub-circuit model, the model card adaption approach is strictly limited to permanent drifts, whereas the sub-circuit can be easily extended to support for both permanent as well as transient recovering parts of degradation effects. Especially for the BTI effects (see sec. 3.3.1 and 3.3.2), those recovering contributions can form major parts of the overall parameter drifts. For advanced effect modeling, recovery has to be considered in the circuit level models, which is only supported by an adapted sub-circuit approach. Another challenging topic in circuit level modeling is the consideration of locally confined degradations, as generated by HCI aging. Fig. 3.16 sketches for an exemplary nMOS, CHCI impact on the output characteristic  $(I_D/V_{DS})$  in dependence of the current bias direction. For the forward case, stress and characterisation were biased in the same direction. For the reverse biasing, Drain and Source nodes were swapped. CHCI degradation in forward biasing degrades Drain current and the slope of the output characteristic, acting as another increase of channel length modulation factor  $\lambda$ . In reverse bias, the same CHCI generated charge impacts the fully inverted channel leading to the classic  $V_{th}$  or  $I_D$  shift. As shown in this example, a throughout correct circuit level aging modeling can arise as a challenging task. In the majority of cases, circuit level models are kept simple due to complexity reasons.

In general, circuit reliability simulations may end up in large and overloaded simulation runset files, as for each incorporated device an individual model card or sub-circuit model has to be included into the simulation netlist. For AgeMOS<sup>TM</sup> compatible models, degradation is an integral part of the model card and can be considered by providing corresponding aging parameters, solving the problem of replacing thousands of transistors by individual degraded model cards or sub-circuit models [77]. Nevertheless, recovery effects are still neglected by this approach.

Fig. 3.16: Exemplary CHCI/nMOS degradation measurements and its impact on forward or reverse nMOS operation [63].

#### 3.5.1 Semi-Empirical Models

The most simple way for aging prediction are the *semi-empirical* aging models, that are typically provided by the technology related DM (<u>Design Manual</u>). A very general version of this model type is also given in the JEDEC standard [3]. Semi-empirical models are widely used in circuit reliability investigations, especially if diverse aging effects in the circuit are considered [10, 23, 22, 14]. These models base on general effect related physical assumptions, and are further fitted to stress measurement data.

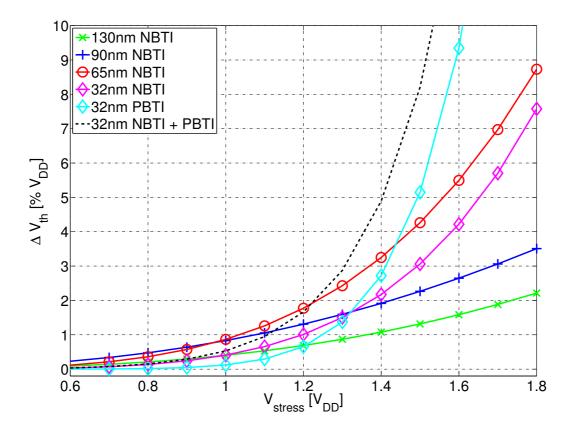

The semi-empirical BTI model predicts degradation as a drift in threshold voltage  $\Delta V_{th}$ , that is directly related to the generated charge in the MOSFET insulator (eq. (3.3)). The BTI induced drift is given by eq. (3.6)

$$\Delta V_{th} = A \cdot \left(\frac{V_{GS}}{t_{ox}}\right)^m \cdot e^{\left(\frac{\Delta E}{kT}\right)} \cdot L^{\alpha} \cdot W^{\beta} \cdot t^n, \tag{3.6}$$

with the common known stress parameters:  $V_{GS}$  the Gate-Source voltage, T the temperature and t the stress time.  $\Delta E$  represents the thermal activation energy and k the Boltzmann constant, exhibiting an Arrhenius type temperature behavior. The factor A is a process related prefactor. Exponent m denotes the power law sensitivity towards arising oxide electric fields given by  $(\frac{V_{GS}}{t_{ox}})$ , with  $t_{ox}$  the oxide thickness. m is process dependent and has to be adjusted to the CMOS process. It is typically in the rage of 2 < m < 10 for current CMOS technologies. In the past,  $V_{GS}$  sensitivity was also often modeled with an exponential behavior [78, 23]. BTI effects prove to be inherently dimension independent, as in its worst case scenario in deep triode region, BTI degradation occurs equally distributed over the insulator area. Factor  $(L^{\alpha} \cdot W^{\beta})$ , with L the gate length and W the width, represents a correction for minimum size devices to consider for boundary effects. Exponents  $\alpha$  and  $\beta$  are typically much smaller than 1. The time exponent n is typically in the range of 0.15-0.3, inducing the sub-linear or saturating degradation behavior for

linear time scales [42, 23, 22]. This time exponent n is of special interest, as it major impacts the degradation end-of-lifetime extrapolation quality [79]. The model equation in (3.6) is valid for NBTI/pMOS as well as for PBTI/nMOS in high- $\kappa$  technologies each with its individual parameter set.

Equation (3.6) only allows aging evaluation of one single stress condition (V, T, t). A change of one of the stress parameters during evaluation is not supported. To account for realistic stress with time varying stress conditions arising in circuit operation, an auxiliary variable AGE has to be defined:

$$AGE_{BTI} = \sqrt[n]{\Delta V_{th}}$$

$$= \sqrt[n]{A \cdot (\frac{V_{GS}}{t_{ox}})^m \cdot e^{(\frac{\Delta E}{kT})} \cdot L^{\alpha} \cdot W^{\beta}} \cdot t.$$

(3.7)

$AGE_{BTI}$  implies a linear behavior in time and supports the consideration of individual stress periods by adding up  $AGE_{BTI,i}$  values and calculate via eq. (3.7) the total threshold voltage drift.

$$AGE_{BTI,total} = AGE_{BTI,1}(V_1, T_1, t_1) + AGE_{BTI,2}(V_2, T_2, t_2) + \dots$$

(3.8)

$$\Delta V_{th,total} = (AGE_{BTI,total})^n \tag{3.9}$$

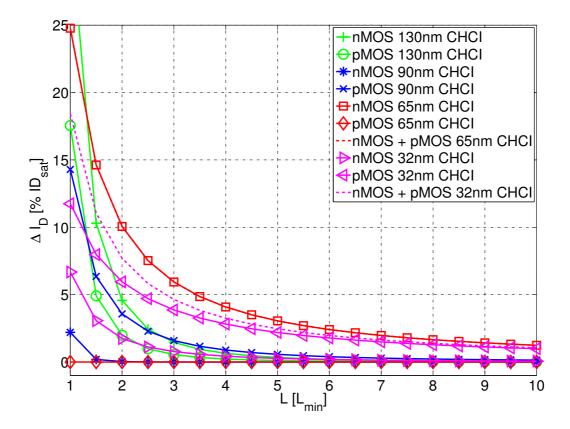

According to this general concept, circuit reliability simulators like RelXpert<sup>TM</sup>predict device degradation under transient voltage stress [77]. Also here, the accurate derivation of the time exponent n is of major importance to correctly predict device aging. A similar model equation for HCI aging prediction is given by

$$D_{HCI} = B \cdot V_{DS}^p \cdot e^{\left(\frac{\Delta H}{kT}\right)} \cdot L^{\delta} \cdot t^q. \tag{3.10}$$

Also for HCI, classic stress parameters,  $V_{DS}$  as the Drain-Source stress voltage, T the temperature and t the stress time mainly determine degradation. Temperature behavior is modeled as Arrhenius law with  $\Delta H$  the activation energy and k the Boltzmann constant. B is the process related prefactor. Exponent p denotes voltage sensitivity and is also process related. Gate length dependency is given by  $L^{\delta}$ , with  $\delta \approx [-4; -2]$ . The time exponent q is larger than for BTI and is in the range of 0.2-0.5 [22]. Depending on the model implementation HCI aging is considered as a drift in Drain current

$$\frac{\Delta I_D}{I_D} = D_{HCI} \tag{3.11}$$

or as

$$\frac{\Delta I_D}{I_D} = x \cdot D_{HCI}$$

and  $\Delta V_{th} = y \cdot D_{HCI}$ . (3.12)

with 0 < x < 1 and 0 < y < 1, separating HCI degradation into the  $\frac{\Delta I_D}{I_D}$  and the  $\Delta V_{th}$  contributions. This general HCI model is used for CHCI and NCHCI in nMOS and pMOS transistors, each with an individual parameter set.

To consider for time varying voltage stress, a corresponding  $AGE_{HCI} = \sqrt[q]{D_{HCI}}$ , similar

to eq. (3.7) can be defined to support aging integration ability over time.

Circuit level inclusion is typically performed with a sub-circuit model, as BTI and HCI models output  $\Delta V_{th}$  or  $\frac{\Delta I_D}{I_D}$  - the two parameters of the sub-circuit model. Thereby, BTI and HCI degradation are modeled as independent effects, so both aging contributions should be added and combined in the circuit level model.

Semi-empirical models suffer from a few drawbacks that mainly affects the modeling accuracy. Equations (3.6) and (3.10) only consider a 1-dimensional stress voltage dependency - for BTI degradation a  $V_{GS}$  and for HCI a  $V_{DS}$  dependency. As discussed in sec. 3.3, BTI degradation is mainly driven by the vertical electric field, thus by  $V_{GS}$ . But the lateral field, given by  $V_{DS}$ , determines device operation region and electric field distribution over the channel. For this reason,  $V_{DS}$  also impacts total BTI degradation. A corresponding  $V_{GS}$  dependency for HCI effects as discussed in sec. 3.4 is also omitted for the HCI model equation. The general aim of the semi-empirical models is to cover degradation for worst case aging conditions. Another point is the disregard of recovering phenomena, especially for BTI effects. Evaluated degradation is predicted in a fixed, permanent magnitude without indication of ongoing relaxation behavior. Furthermore, the considered recovery state during the model extraction measurement, thus the delay between stress and characterisation measurement is not defined nor denoted. In the end, semi empiric models are limited to two degradation variables  $\Delta V_{th}$  and  $\frac{\Delta I_D}{I_D}$ , further reducing modeling quality.

The big plus of the semi-empirical models are their simplicity and dependency of easy accessible stress parameters on circuit level. They prove to be very useful for circuit level inclusion or, as will be shown later, to develop general circuit aging behavioral models. They also provide the possibility to determine effect acceleration according to the stress conditions (V,T,t).

## 3.5.2 Complex Models

More sophisticated degradation prediction models are incorporated into automatized reliability tools like Cadence RelXpert<sup>TM</sup> [77] or Synopsys HSIM<sup>plus</sup> MOSRA<sup>TM</sup> [80, 81]. Both tools further support the historically grown 'lifetime' approach. Basing on an individual circuit related aging limit, e.g.  $10\%~I_D$  degradation, the reliability simulator predicts the 'lifetime' of aging effects in each device when this degradation limit will be reached for the given voltage and temperature stress conditions. 'Lifetime' prediction can be considered as a parent approach to parameter drift inclusion into an aged netlist.

Advanced BTI aging prediction models are very similar to the semi-empirical model equation in sec. 3.5.1. Further enhancements consider an additional  $V_{DS}$  dependency on the overall BTI degradation.

Particularly for HCI prediction, advanced models, basing on the LEM [64] approach, are incorporated into reliability simulators. LEM models forecast degradation from a certain rate of substrate or gate current. HCI aging for nMOS devices is predicted via

$$D_{HCI,nMOS} = \left(\frac{I_{DS}}{H \cdot W} \left(\frac{I_{SUB}}{I_{DS}}\right)^m \cdot t\right)^n, \tag{3.13}$$

with  $I_{DS}$  the Drain-Source current of the device, W the gate width and t the stress time. H is a process related constant. Exponents m and n denotes the acceleration factor and the reaction rate.  $I_{SUB}$  monitors the impact ionization rate and is related to the lateral electric field, thus depends on bias conditions  $V_{GS}$  and  $V_{DS}$  as well as device channel length.  $I_{SUB}$  is derived according to the relations given in [82]. For pMOS devices an additional Gate current component is used for aging prediction, as  $I_G$  proves to be a more suitable HCI monitor [82],

$$D_{HCI,pMOS} = \left(X \cdot \frac{1}{H_G} \left(\frac{I_G}{W}\right)^{m_G} \cdot t + (1 - X) \frac{I_{DS}}{H \cdot W} \left(\frac{I_{SUB}}{I_{DS}}\right)^m \cdot t\right)^n \tag{3.14}$$

X denotes a weighting coefficient in the range of [0;1],  $H_G$  a process related constant and exponent  $m_G$  the acceleration factor. Gate current  $I_G$  is further related to  $I_{SUB}$ , bias conditions and oxide thickness. The overall derivation of  $I_G$  can be found in [82]. Further developments of these models incorporating approaches regarding HCI in nanoscale CMOS processes are given in [83, 84].

HCI aging for time varying stress voltage and current waveforms, that typically occur during circuit operation, can be similarly considered via the integrable AGE approach introduced in sec. 3.5.1.

As the use of complex HCI models demand for elaborate derivations of variables monitoring  $I_{SUB}$  and  $I_{G}$ , these model types are typically incorporated and limited to reliability simulator tools. The big plus to perform a more accurate aging prediction due to a elaborate stress bias modeling is clouded by the reduced insight for circuit's aging critical operation points. Here, semi-empirical models with their direct relation to basic design parameters provide a better understanding for design level countermeasures.

#### 3.5.3 Relaxation Model

The introduced models in sec. 3.5.1 and 3.5.2 generally represent degradation as a permanent drift of MOSFET parameters. As already discussed in sec. 3.3.1 and 3.3.2, especially BTI effects exhibit a pronounced recovery behavior when stress conditions are removed, yielding to a transient variation of the induced parameter drifts.

The approach from Huard [10] divides NBTI/pMOS degradation in two independent components: one permanent part, that is related to the generation of interface states and fixed positive charge and a relaxing part due to charge trapping and detrapping. The investigation revealed, that each of these parts exhibit their own voltage and temperature dependency and two separate models for both contributors are derived. Indeed, this approach provides the opportunity to distinguish between two contributing parts, but does not provide information how to model the relaxation behavior in circuit level simulation. Another open point is how to segment NBTI effect recovery, coming along with vast time constants, into a recovering and permanent contributor.

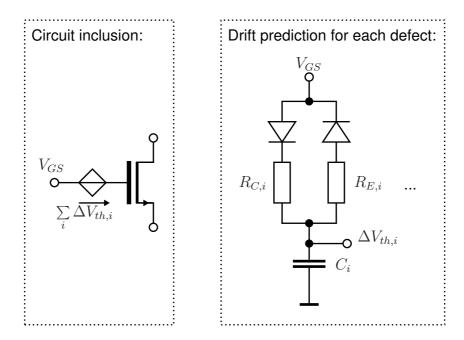

Basing on the SOT approach [40] (see sec. 3.3.1), a general sub-circuit BTI degradation model, reproducing the trapping and detrapping of individual oxide defects was proposed by Kaczer and Reisinger [50, 48]. The implementation is similar to the charge trapping approach from Fulde [85], but covers larger time domains. As depicted in fig. 3.17, the

Fig. 3.17: SOT general BTI model considering loading and deloading of single oxide defects

sub-circuit reproduces via two distinct paths for loading and deloading with its individual time constants, the capture and emission of individual defects in the oxide in dependence of the given bias stress  $V_{GS}$ . Missing temperature activation is proposed to be modeled by a temperature related change in defects capture and emission paths by shifting the values  $R_{C,i}$  and  $R_{E,i}$ . The probability of the defect charging state and its average contribution to the overall  $\Delta V_{th}$  drift is given by the voltage condition  $\Delta V_{th,i}$  at the capacitor. For large area devices, lots of defects have to be considered resulting in unreasonable number of defect models. Here, a clustering to limit the number of sub-circuit branches has been proven to provide adequate results. Comparisons of simulations and measurements revealed a very accurate aging prediction for AC stress conditions as well as classic effect relaxation after stress [48]. Regarding minimum size devices incorporating a denumerable number of defects each with individual drift contributions, this method provides a powerful ability to account for arising BTI effect statistics. Further developments of the SOT approach are given in [86, 87, 61]

The model combines aging prediction and circuit level inclusion in one approach and uses the circuit simulator to solve the trapping and detrapping behavior. Beside the accurate aging effect prediction, it suffers from an unreasonable increase in simulation complexity for circuits with large numbers of devices. Here, a preceding more general examination via semi-empiric or complex models to find the most dominant aging contributors would be suitable. In a subsequent step the relaxation model should be included for main contributors. This would result in a more efficient aging simulation. The main drawback of the relaxation model method results from the direct inclusion in the circuit simulation. As will be discussed in section 3.6, the missing end-of-lifetime extrapolation ability would end-up in unreasonable large simulation times to reach this aging point. Future implementations of this approach demand for an extrapolation ability to be able to simulate

circuits regarding all recovering effects for end-of-lifetime conditions.

## 3.6 Circuit Reliability Simulation

The consideration of device aging in SPICE based circuit simulators has to deal with the fact of widespread time domains of circuit simulation and device aging. Whereas transient circuit simulations typically cover timing periods of  $\mu s$  or ms with discrete timing step sizes in the sub-ns range, the classic device aging period is the whole circuit lifetime in the range of several years. Direct inclusion of device aging effect prediction into circuit simulations would result in out of scale simulation runtime and proves to be unfeasible for circuit designers.

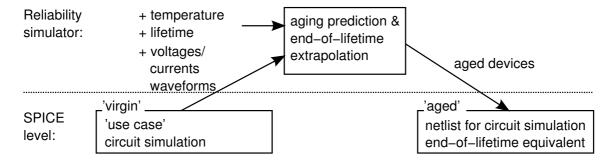

A more sophisticated approach is the aging effect extrapolation basing on a representative circuit operation condition. Separate device aging prediction allows to create a circuit netlist to simulate performance in an 'aged' condition. This approach can be performed manually or by automated reliability tools like RelXpert<sup>TM</sup>[77]. Fig. 3.18 depicts the general approach of the reliability simulator RelXpert<sup>TM</sup>. Here, a representative circuit operation simulation is used to predict arising voltage and current stress on the incorporated devices. According to the simulated voltage/current waveforms, the given temperature and the corresponding age of the circuit, the reliability simulator predicts device aging and extrapolates to the given lifetime. In a second step, an 'aged' netlist, representing the degraded circuit, is output for further simulations on the degraded circuit. Major attention should be turned to the operation voltage/current simulation to cover typical 'use-case' or 'worst-case' operation scenarios.

For the manual approach, aging prediction and generation of the 'aged' netlist has to

Fig. 3.18: Basic concept to embed device aging into spice circuit simulations

be performed individually for each device 'by hand'. This can be handled for circuits incorporating only few transistors, but gets time-consuming for circuits with more than 20 degrading devices. Furthermore, manual aging prediction models are limited to DC voltage/current operating states or pulsed stress waveforms, that can be predicted by the  $\frac{t_{on}}{t_{on}+t_{off}}$  ratio - the so called Duty Cycle. Duty Cycle compatible waveforms typically arise in digital logic circuits, but are not sufficient to map the complex transient analog circuit operation. This limits the reasonable usage of the manual approach to DC operation for analog circuits.

The pro of automatized reliability tools is the ability to include reliability investigation in the common circuit design flow. This provides circuit designers a reliability proof of the circuit design without being an expert in device aging mechanisms. As these tools typically evaluate circuit aging in one distinct point in the aging parameter space (V,T,t), investigation regarding the circuit aging behavior in dependence of stress parameters are getting time-consuming. Here, a more sophisticated method would be an analytical approach using the semi-empirical models. Furthermore, semi-empirical models offer the possibility to derive stress conditions for accelerated degradation testing.

## 3.7 Reliability Testing

The major challenge of reliability testing consists in the practically unaccessible wearout or breakdown state far ahead in future, that is typically in the range of several years of operation. To fulfill proper process qualification in conjunction with short time-to-market constraints, reliability studies are typically run in a *stress* environment to *accelerate* wearout or breakdown effects in their temporal behavior. In the majority of cases an operation under elevated temperature or supply voltage or a combination of both stress parameters is used to accelerate the distinct effect. Stress tests are also employed to derive general physical behavior of degradation effects by running tests with varying stress parameters [1].

The common approach to accelerate a distinct mechanism in time is to find, e.g. for BTI degradation, a corresponding  $V_{GS,stress}$  and  $T_{stress}$  according to the end-of-lifetime operation state with  $V_{GS,EOL}$  and  $T_{EOL}$ , generating equal device wearout:

$$\Delta V_{th,stress} \left( V_{GS,stress}, T_{stress}, t_{stress} \right) = \Delta V_{th,EOL} \left( V_{GS,EOL}, T_{EOL}, t_{EOL} \right)$$

(3.15)

To fulfill (3.15), model equation (3.6) can be used to derive stress conditions for the accelerated test. A general definition for aging effect acceleration in time is defined by the AF (<u>A</u>cceleration <u>F</u>actor). Derivations of AF's for BTI and HCI degradation are given in [3]. For the exemplary BTI mechanisms,  $AF_{BTI}$  between a stress state and a user-defined operation UC (<u>Use Case</u>) can also be evaluated via eq. (3.6) and results in

$$AF_{BTI} = \frac{t_{UC}}{t_{stress}}$$

$$= \sqrt[n]{\left(\frac{V_{GS,stress}}{V_{GS,UC}}\right)^m \cdot e^{\left(\frac{\Delta E}{k}\left(\frac{1}{T_{stress}} - \frac{1}{T_{UC}}\right)\right)}}.$$

(3.16)

It is obvious from eq. (3.16) that proper effect acceleration demands for a throughout physical understanding of the accelerated defect. An important characteristic of reliability testing, that has to kept in mind, is: the longer the stress durations, the smaller stress voltages and stress temperatures have to be chosen. Short stress times demand for high stress voltages and temperatures that further debut new defect mechanisms, overlying with the primary wearout mechanism and distort the degradation result. A general rule for proper stress testing can be quoted: the more time spending, the smaller the acceleration stress conditions and the better the accelerated test maps the end-of-lifetime use

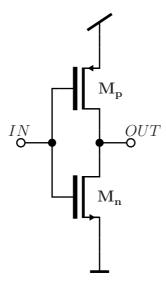

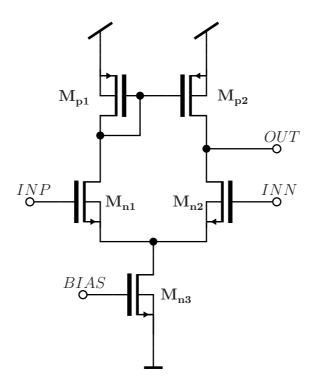

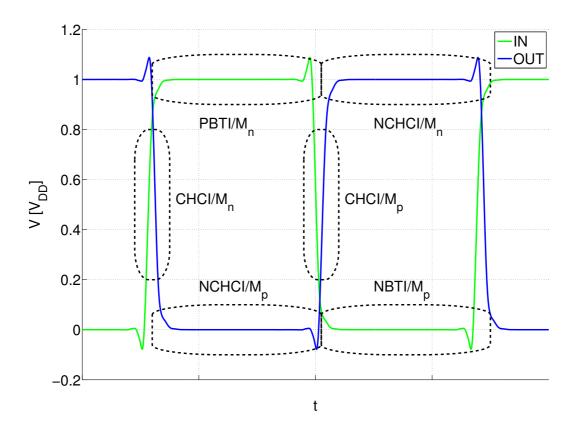

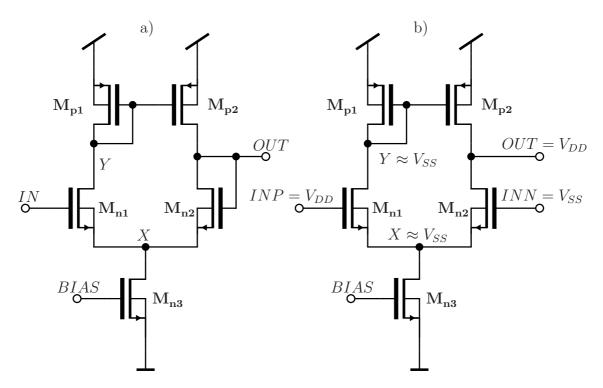

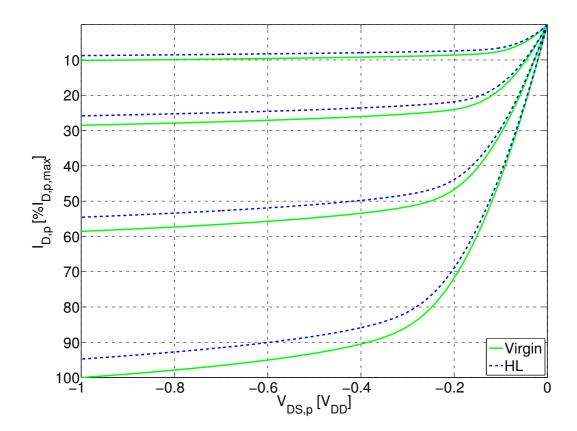

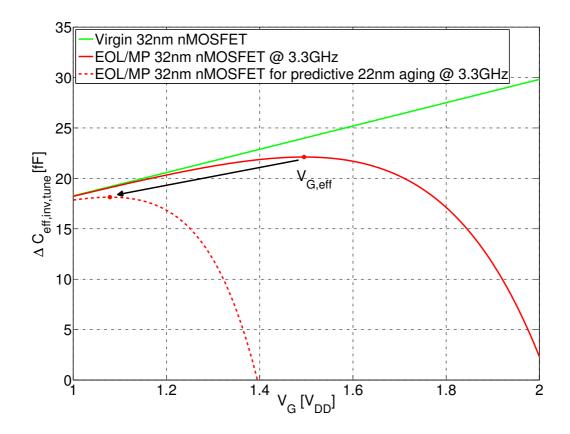

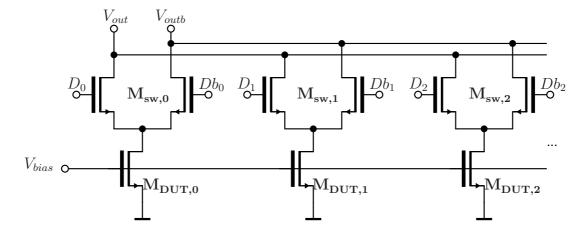

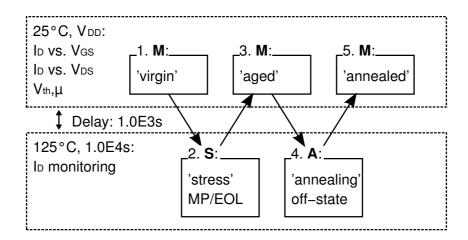

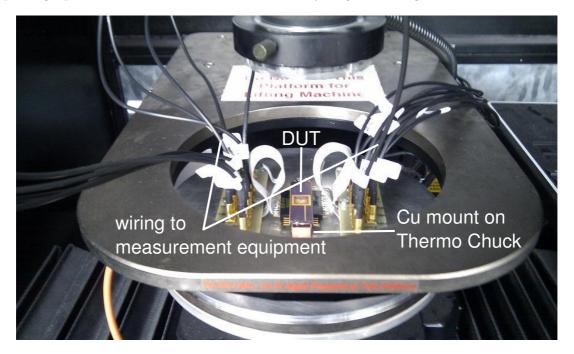

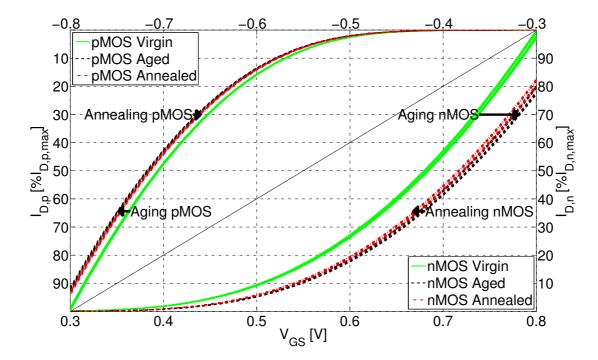

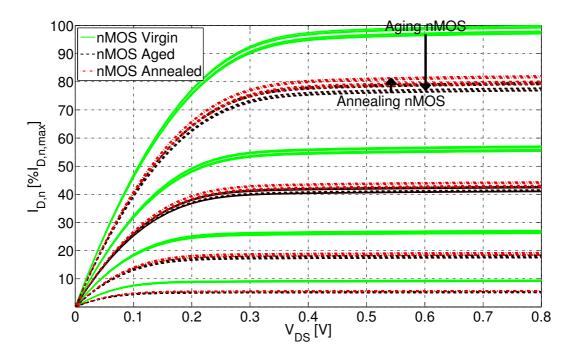

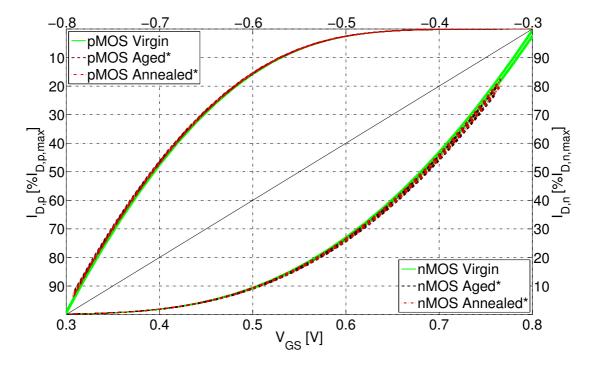

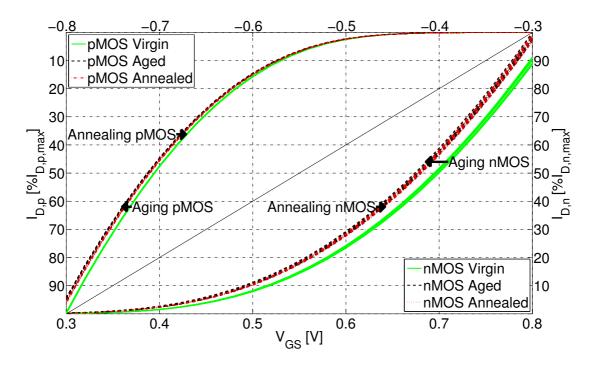

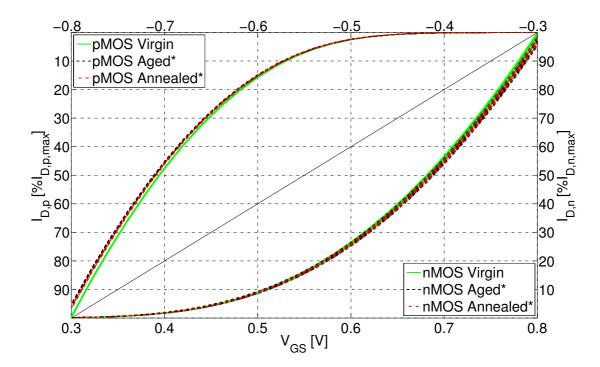

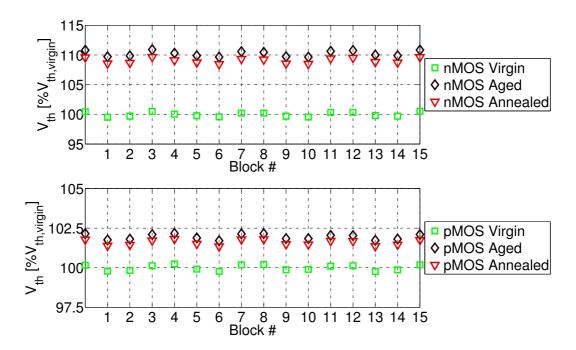

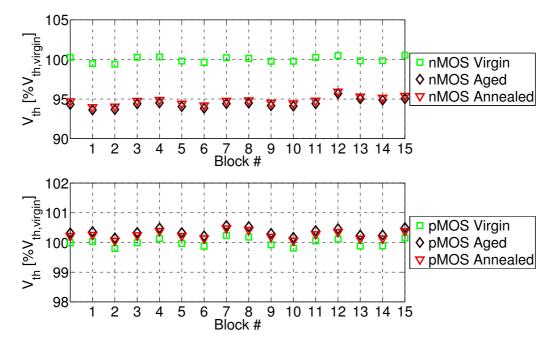

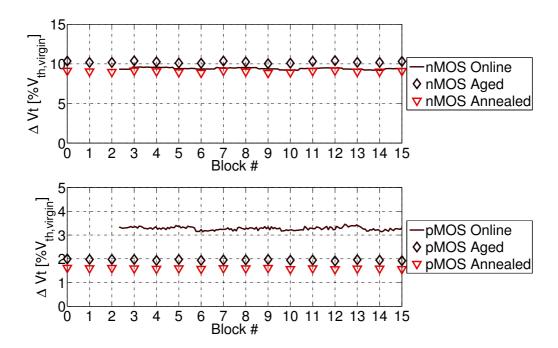

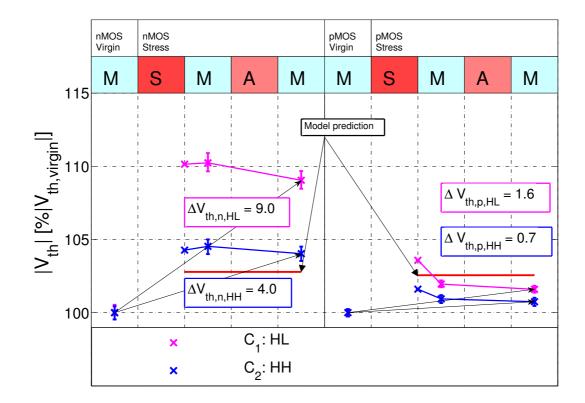

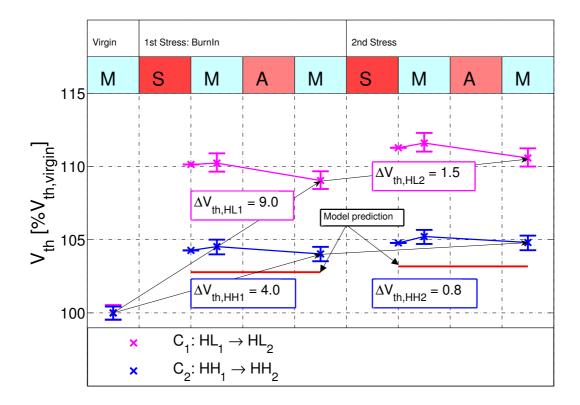

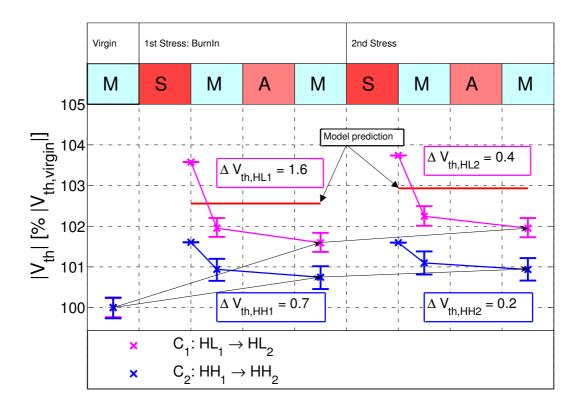

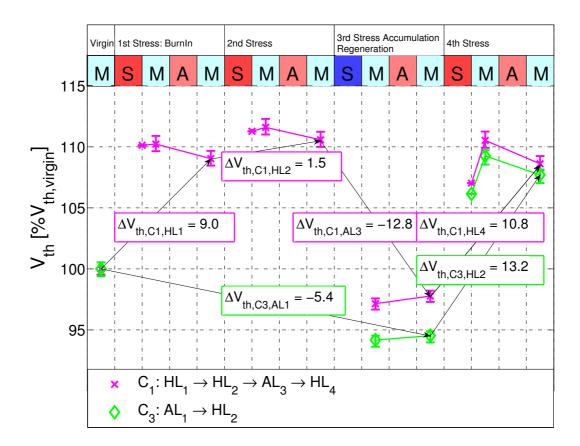

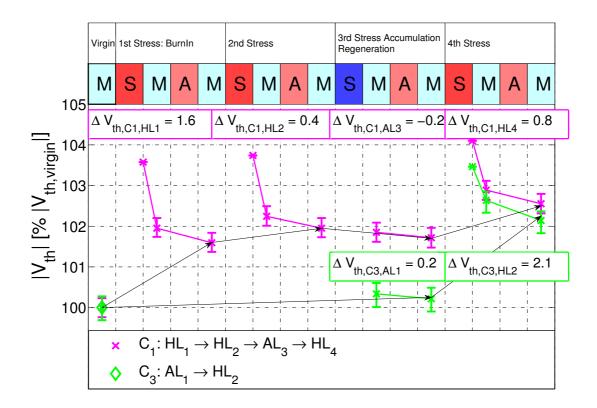

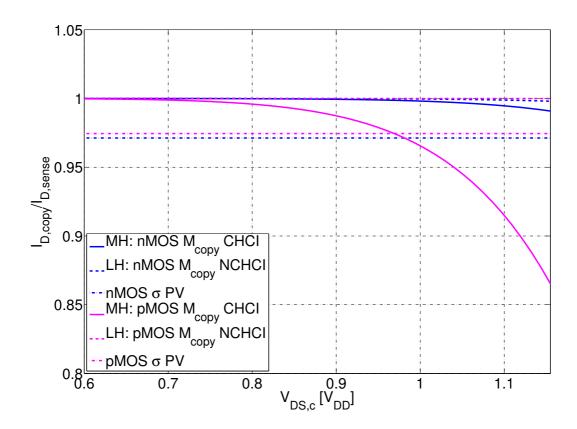

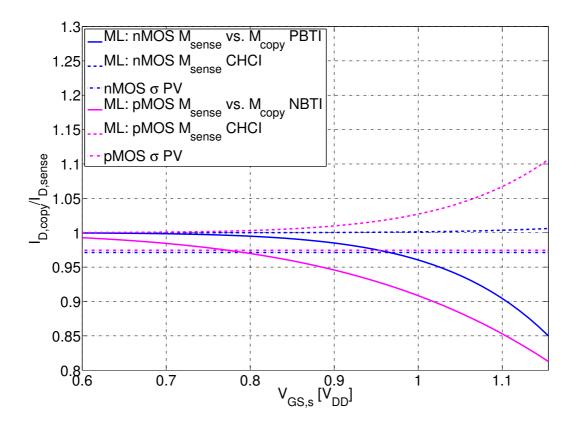

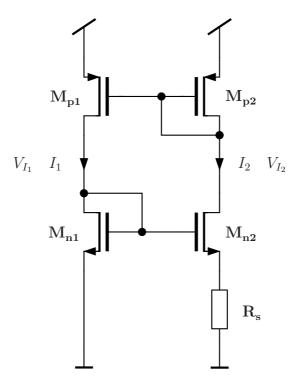

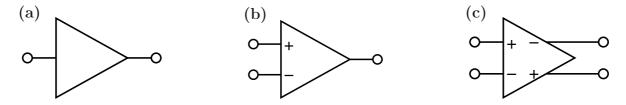

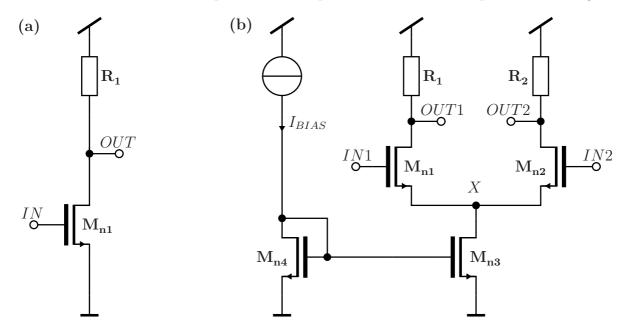

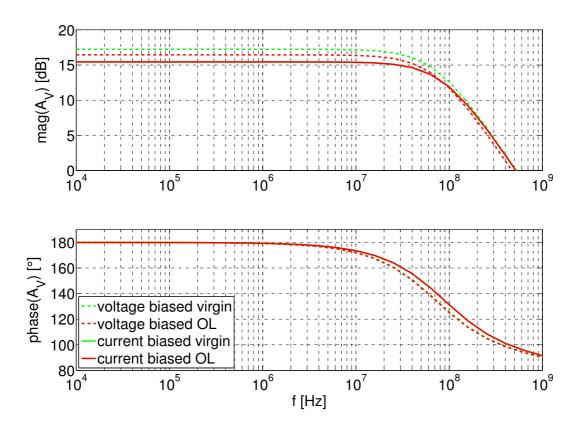

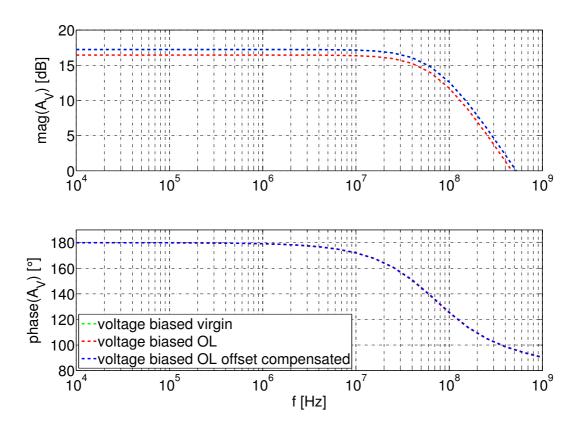

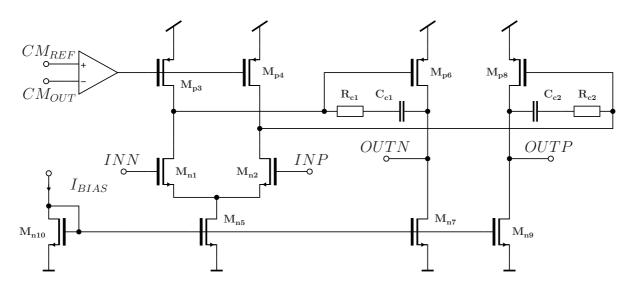

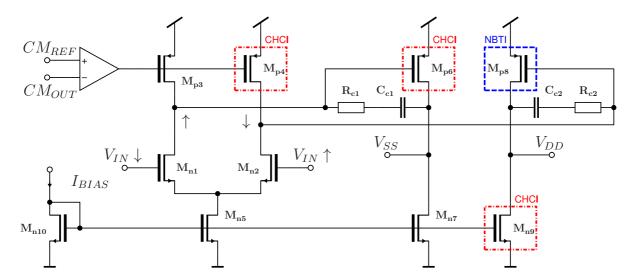

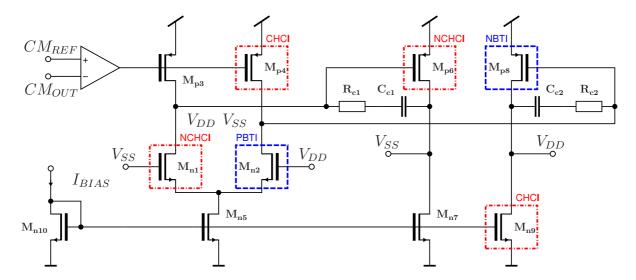

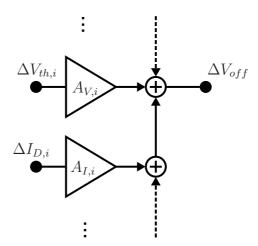

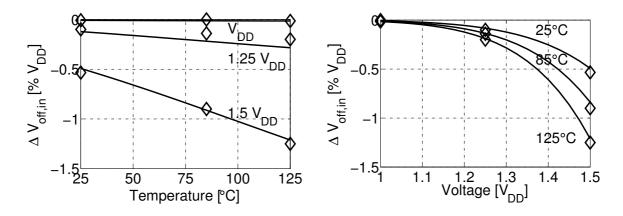

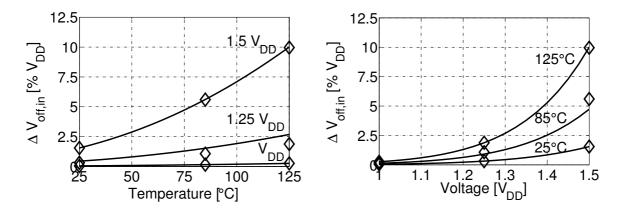

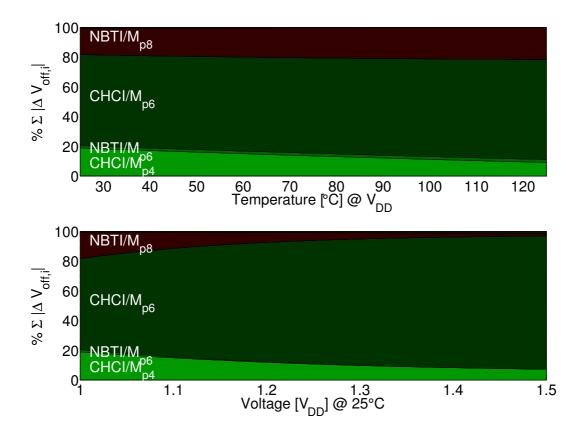

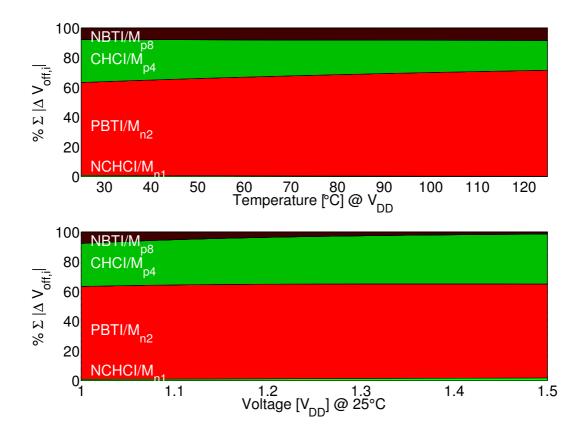

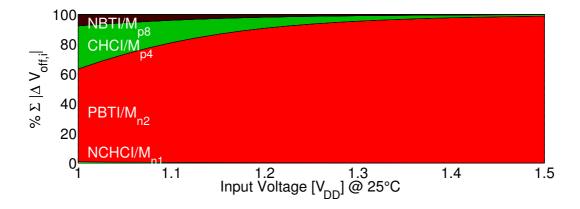

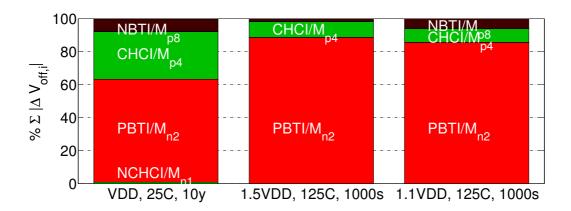

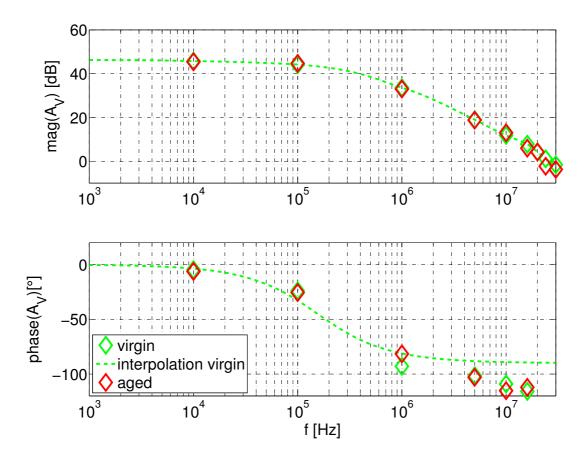

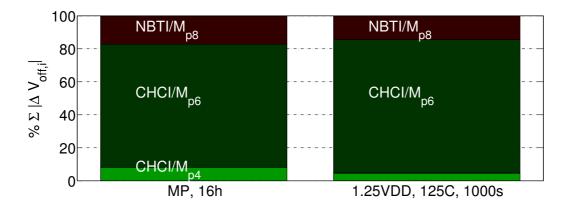

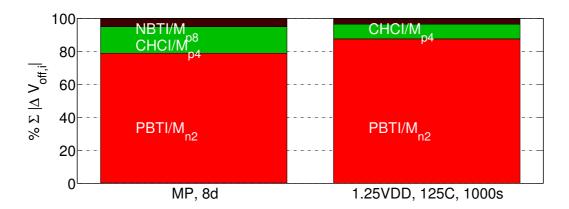

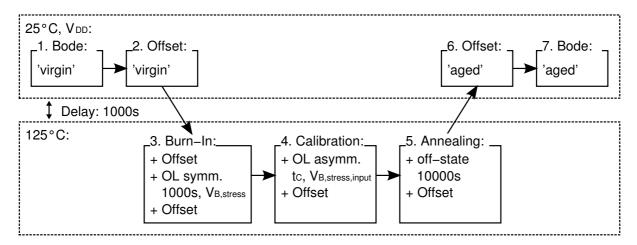

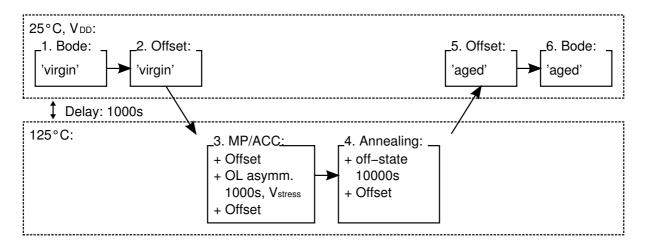

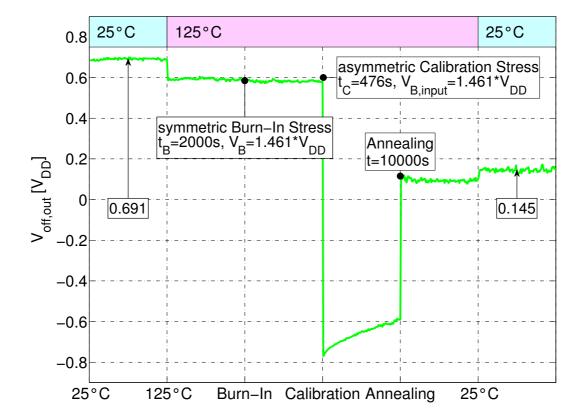

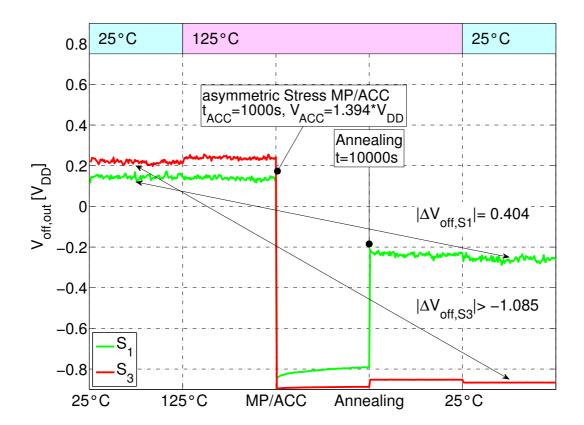

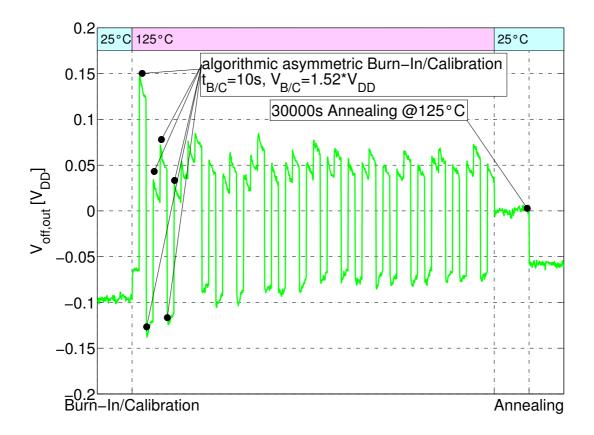

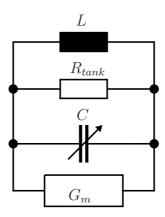

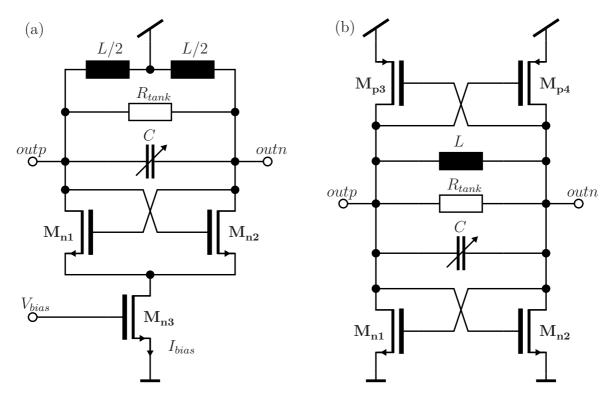

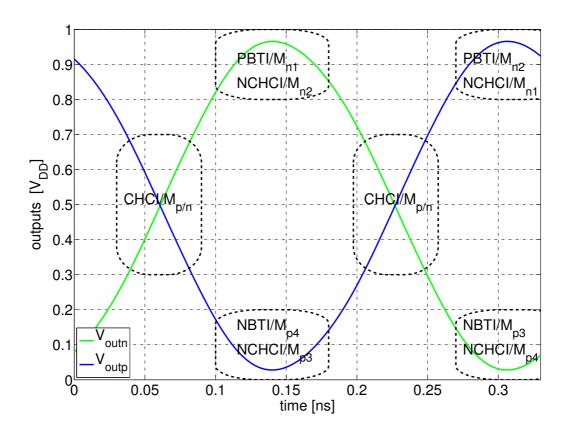

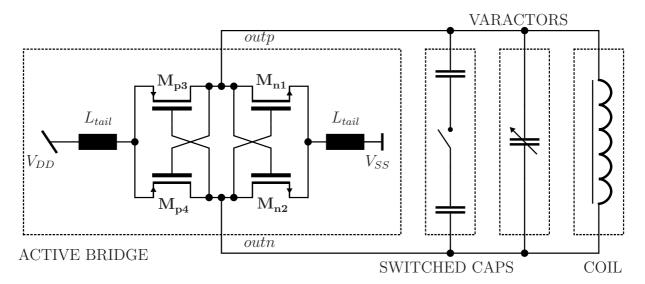

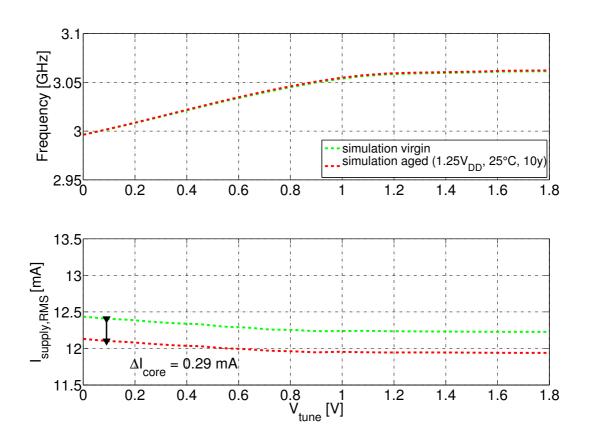

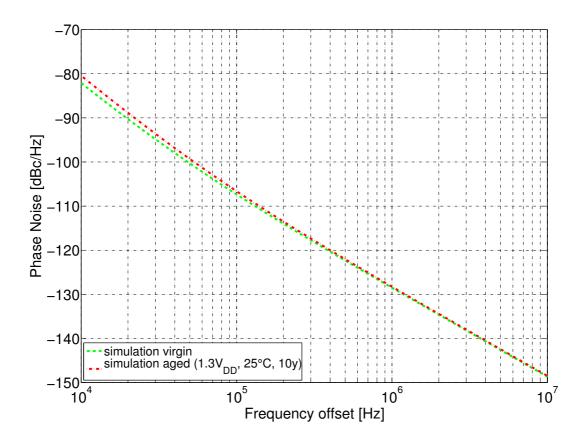

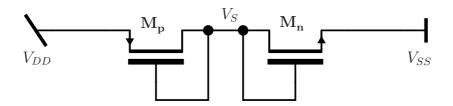

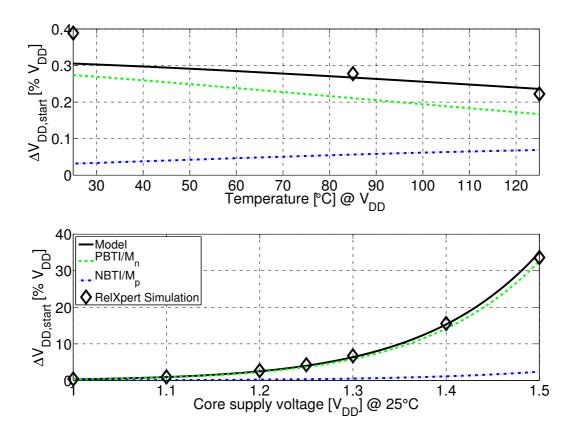

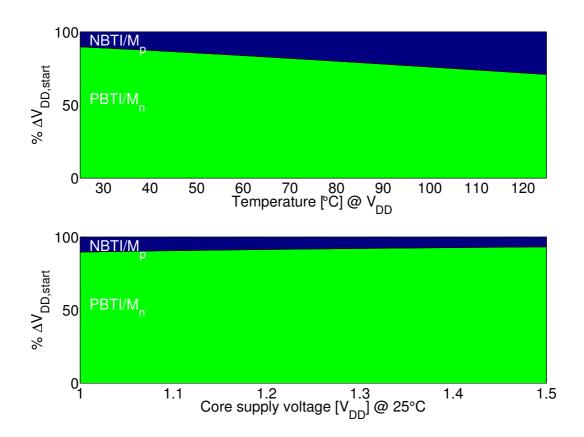

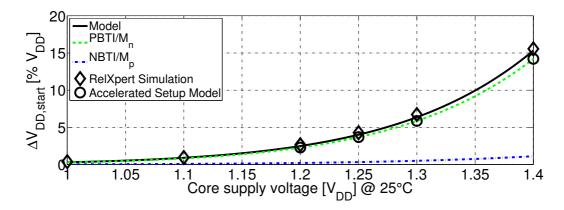

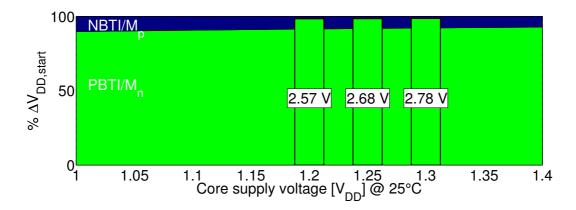

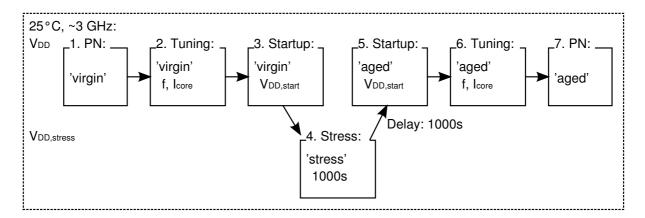

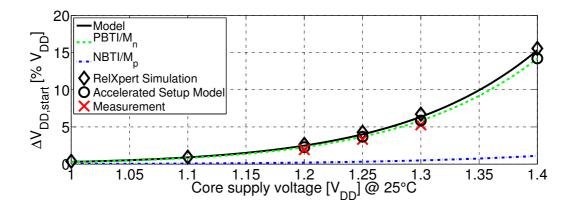

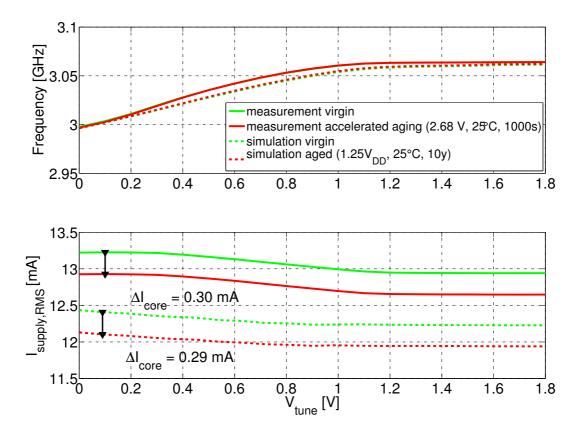

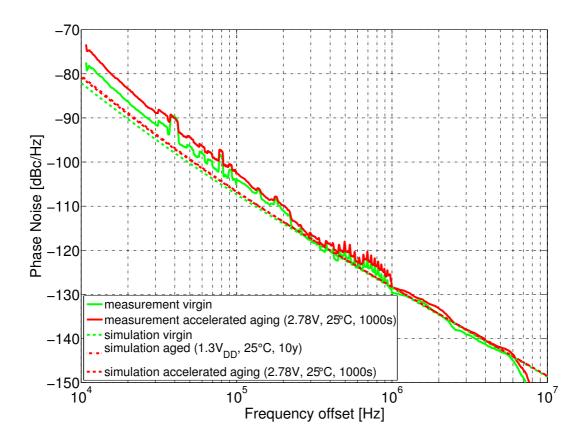

case.