# TECHNISCHE UNIVERSITÄT MÜNCHEN

#### Lehrstuhl für Realzeit-Computersysteme

## **Models and Interfaces for Distributed Control Systems**

#### Matthias Kauer

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Gerhard Rigoll

Prüfer der Dissertation: 1. Prof. Dr. Samarjit Chakraborty

2. Prof. Anuradha M. Annaswamy, Ph.D.

Die Dissertation wurde am 24.03.2016 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 17.08.2017 angenommen.

# **Abstract**

The goal of this thesis is to bridge the gap in digital control systems between high-level domain models for physical dynamics and implementation platforms. To that end, suitable interfaces linking physical and platform behavior are proposed for two setups. In the first, these interfaces improve guaranteed control performance under constrained communication. In the second, fast simulation and optimization are achieved for a class of switching-actuated systems.

Automatic control, the context of this work, is concerned with the regulation of dynamical systems. A control algorithm periodically adjusts a system's input signal to ensure a certain output behavior. These algorithms are typically designed in isolation, with a number of idealistic assumptions about their environment. Such assumptions include infinite numerical precision and zero delays on the hardware platform, as well as mathematically convenient input signals. Although approximately satisfied in many cases, they are not sufficiently analyzed in others.

Combining the design of control algorithms and their implementation platforms is challenging because their respective models deal with very different phenomenons. System descriptions and control algorithms typically express dynamics in continuous time, using differential equations. Digital platforms have many discrete aspects and comprise processor architectures, scheduling strategies and communication protocols, among other things. Interfaces are hence required that describe or abstract the behavior of the physical side in a form that can be taken into account during the design process of the digital side and vice versa.

Developing suitable and expressive interfaces that enable a co-design of control algorithm and digital platform is the focus of this thesis. To that end, we study two different setups. The first deals with the effects of communication delay on the control performance of quickly evolving systems. There, the requirements of each control algorithm are typically expressed as a combination of period and deadline. This is rather rigid and the more flexible interface introduced here leads to designs with higher guaranteed performance on identical hardware. The second setup considers charge transfer within battery packs. Each of the many individual cells in such a pack behaves somewhat differently, yet the aggregate charge is determined by the minimum charge among cells in the pack. For this reason, transferring charge and thus balancing cells improves efficiency. Because these transfers are actuated by frequent discrete switching, abstracting interfaces are crucial for efficient quantitative models. Both models and interfaces are proposed in this dissertation.

Communication and computation delay, as studied in the first setup, is the main link between rapidly changing dynamical systems and their implementation platform. This delay becomes non-negligible in complex distributed platforms that have been introduced to cope with the growing number of control applications. The systematic design processes, which have been and are being developed for larger systems, do still not include delay interaction in adequate detail,

however. As delay affects control performance while timing requirements also affect platform design in return, a co-design of control algorithm and implementation platform can improve the overall process quality and dramatically reduce testing efforts.

This is the promise of the *Cyber-Physical System* (CPS) paradigm. It is different from previous approaches like networked control systems where the implementation platform (or the network) is assumed to be fixed. By default, timing requirements are specified in terms of strict deadlines. These are formed with respect to the worst case which only rarely occurs. Designing towards that interface hence leads to guaranteed, but not necessarily to sufficient performance. The design framework presented here allows and quantifies occasional deadline misses with their effects on the physical system using formal verification. It can thus use shorter deadlines and ultimately achieves better performance guarantees. To make the approach comprehensive, automata-theoretic models for fixed priority scheduling are advanced to yield conservative results even with non-preemptive behavior. A delay-aware fault-tolerant control strategy further improves guaranteed performance.

In the second setup, internal charge transfer increases battery pack efficiency because usable charge is maximized when the charge of all cells is in balance. In this process, also referred to as active cell balancing, network timing is less critical because it is slow compared to the network and other control applications like anti-lock braking. Its actuation, however, intersects digital and analog behavior in a challenging way. Charge is transferred most efficiently by rapidly switching transistors that connect a temporary energy storage element, like an inductor, to the sender and receiver cell in alteration. This switching leads to non-differentiable transitions between the sender and receiver phase, interfering with common simulation techniques and strategy design. Often, it is hence entirely abstracted away in a lossy way. By contrast, the thesis at hand preserves detail and improves speed by deriving closed-form expressions for the individual transfer phases of a transmitting cell pair. This proposed reformulation leads to 1000 times faster simulation and lossless interfaces that specify long-term actuation. To evaluate transfers beyond minutes, this work consequently develops formulations that enable optimization techniques and speed up the aforementioned phase-based simulation by additional orders of magnitude.

The discussed setups share a number of characteristics. In particular, they treat digital control systems with a semantic gap between models for the physical dynamics and the implementation platform. The solutions we propose towards modeling, controlling, and optimizing them rely on the developed interfaces that bridge this gap. It is worth mentioning how these approaches relate to contributions in the domain of hybrid systems. These include both continuous and digital behavior in one monolithic model, limiting the system size. In timing analysis, the number of discrete states that model network behavior is prohibitively large for hybrid model checking tools. In case of active cell balancing, a hybrid model corresponds to the initial slow simulation we start out with. The techniques developed in this thesis integrate communication and actuation aspects tightly, improving accuracy and hence performance compared to state-of-the-art methods, while ensuring computational efficiency.

# Kurzfassung

Das Ziel dieser Arbeit ist die Lücke zu schließen zwischen abstrakten, domänenspezifischen Modellen für physikalische dynamische Systeme und für Implementierungsplattformen. Zu diesem Zweck schlägt diese Arbeit geeignete Schnittstellen vor, die physikalisches und digitales Verhalten in zwei Aufbauten verbinden. Im ersten Aufbau führen diese Schnittstellen zu verbesserter garantierter Regelungsleistung unter eingeschränkter Kommunikation. Im Zweiten werden schnelle Simulation und Optimierung erreicht für eine Klasse von Systemen, die durch digitales Schalten gesteuert werden.

Die Regelungstechnik, die den Kontext für diese Arbeit bildet, beschäftigt sich mit der Regulierung von dynamischen Systemen. Ein Regelungsalgorithmus passt die Eingangssignale eines Systems periodisch an, um ein bestimmtes Ausgangsverhalten zu gewährleisten. Diese Algorithmen werden üblicherweise isoliert entworfen, mit verschiedenen idealisierenden Annahmen über ihre Umgebung. Zu diesen Annahmen gehören unendliche numerische Präzision und null Verzögerung auf der Hardwareplattform, aber auch mathematisch vorteilhaft gewählte Eingangssignale. Wenngleich solche Annahmen in vielen Fällen annähernd erfüllt sind, werden sie in anderen Fällen nicht ausreichend untersucht.

Das Design von Regelungsalgorithmen und ihren Implementierungsplattformen zu kombinieren ist schwierig, weil ihre jeweiligen Modelle mit sehr unterschiedlichen Phänomenen befasst sind. Systembeschreibungen und Regelungsalgorithmen drücken typischerweise die Dynamik in kontinuierlicher Zeit aus unter Verwendung von Differenzialgleichungen. Digitale Plattformen haben viele diskrete Aspekte und beinhalten unter anderem Prozessorarchitekturen, Schedulingstrategien und Kommunikationsprotokolle. Es werden daher Schnittstellen benötigt, die das Verhalten der physikalischen Seite in einer Form beschreiben oder abstrahieren, die während des Designprozesses für die digitale Seite berücksichtigt werden kann und umgekehrt.

Die Entwicklung geeigneter und ausdrucksstarker Schnittstellen, die ein Co-Design von Regelungsalgorithmus und digitaler Plattform ermöglichen, steht im Fokus dieser Dissertation. Zu diesem Zweck werden zwei verschiedene Aufbauten untersucht. Der erste beschäftigt sich mit den Effekten von Verzögerung bei der Kommunikation auf die Regelungsleistung von Systemen mit schnellem Eigenverhalten. Dort werden die Anforderungen jedes Regelungsalgorithmus typischerweise als Kombination von Periode und Deadline ausgedrückt. Das ist eher starr und die flexiblere Schnittstelle, die hier eingeführt wird, ermöglicht Designs mit höherer garantierter Leistung auf identischer Hardware. Der zweite Aufbau betrachtet Ladungstransfers innerhalb von Batteriepacks. Jede der vielen individuellen Zellen in einem solchen Pack verhält sich leicht anders, während die Gesamtladung bestimmt wird durch die Minimalladung unter den Zellen des Packs. Aus diesem Grund erhöhen Transfers und der so erzeugte Ladungsausgleich die Effizienz. Weil diese Transfers durch rapides, diskretes Umschalten getrieben werden, sind abstrahierende Schnittstellen entscheidend für die Erstellung von effizienten, quantitativen Modellen. Sowohl Modelle als auch Schnittstellen werden im Rahmen dieser Arbeit vorgeschlagen.

Verzögerungen bei der Übertragung oder bei der Berechnung, wie sie im ersten Aufbau untersucht werden, sind die Hauptverbindung zwischen sich schnell wandelnden dynamischen Systemen und ihrer Implementierungsplattform. Diese Verzögerung kann nicht mehr vernachlässigt werden bei komplexen,

verteilten Plattformen, welche eingeführt wurden, um mit der wachsenden Anzahl von Regelungsanwendungen umzugehen. Die systematischen Designprozesse, welche für große Systeme entwickelt wurden und werden, behandeln allerdings weiterhin nicht den Einfluss von Verzögerung in angemessenem Detail. Da Verzögerung die Regelungsleistung beeinflusst während Timinganforderungen umgekehrt auch das Plattformdesign beeinflussen, kann ein Co-Design von Regelungsalgorithmus und Implementierungsplattform die Prozessqualität insgesamt verbessern und den Testaufwand stark reduzieren.

Das ist das Versprechen des *Cyber-Physical System* (CPS) Paradigma. Es unterscheidet sich von früheren Ansätzen wie vernetzten Regelungssystemen, wo die Implementierungsplattform (oder das Netzwerk) als fest angenommen werden. Standardmäßig werden Timinganforderungen als strikte Deadlines angegeben. Diese werden gebildet mit Bezug auf den ungünstigsten Fall, welcher nur äußerst selten auftritt. Auf diese Schnittstelle zu designen führt daher zu garantierter, aber nicht notwendigerweise zu ausreichender Performance. Das Designframework, das hier vorgestellt wird, lässt gelegentliche Zeit-überschreitungen zu und quantifiziert sie mitsamt ihren Auswirkungen auf das physikalische System mit formaler Verifikation. Es kann daher kürzere Fristen verwenden und schlussendlich bessere Leistungsgarantien erreichen. Um den Anwendungsbereich für diesen Ansatz zu erweitern, werden automatentheoretische Modelle für Scheduling mit festen Prioritäten vorangebracht, so dass sie konservative Ergebnisse liefern auch wenn Nachrichten nicht unterbrochen werden können. Eine fehlertolerante Regelungsstrategie, die sich Verzögerungen bewusst ist, erhöht die garantiere Leistung weiter.

Im zweiten Aufbau erhöhen interne Ladungstransfers die Effizienz eines Batteriepacks, weil die nutzbare Ladung maximal wird, wenn alle Zellladungen ausgeglichen sind. In diesem Prozess, der auch als Active Cell Balancing bezeichnet wird, ist das Timing des Netzwerks weniger entscheidend, da er langsam ist verglichen mit dem Netzwerk und anderen Regelungsanwendungen, wie einem Antiblockiersystem. Seine Betätigung kreuzt allerdings digitales und analoges Verhalten auf herausfordernde Weise. Ladung wird am effizientesten übertragen durch schnell umschaltende Transistoren, die einen temporären Energiespeicher, wie eine Spule, abwechselnd mit Sender- und Empfängerzelle verbinden. Dieses Umschalten führt zu nicht-differenzierbaren Übergangen zwischen der Sender- und der Empfängerphase und behindert gängige Simulationsmethoden wie auch den Strategieentwurf. Es wird daher oft einfach wegabstrahiert auf verlustbehaftete Weise. Im Gegensatz dazu erhält die vorliegende Dissertation die Details und verbessert die Simulationsgeschwindigkeit, indem sie geschlossene Ausdrücke für die einzelnen Transferphasen herleitet. Diese vorgeschlagene Umformulierung ermöglicht 1000 mal schnellere Simulation und verlustfreie Schnittstellen, welche die Langzeitoperation spezifizieren. Um Transfers zu evaluieren, die über Minuten hinaus gehen, entwickelt diese Arbeit anschließend Formulierungen, die Optimierung ermöglichen und den erwähnten phasenbasierten Simulationsansatz um weitere Größenordnungen beschleunigen.

Die diskutierten Aufbauten teilen mehrere Eigenschaften. Insbesondere behandeln sie beide digitale Regelungssysteme mit einer semantischen Lücke zwischen den Modellen für die physikalische Dynamik und denen für die Implementierungsplattform. Die Lösungen, die zur Modellierung, Regelung und Optimierung vorgeschlagen werden, beruhen auf Schnittstellen, die diese Lücke überbrücken. Es soll auch erwähnt werden, in welchem Verhältnis diese Ansätze zu Beiträgen aus dem Bereich der hybriden Systeme stehen. Diese beinhalten sowohl kontinuierliches als auch digitales Verhalten in einem monolithischen Modell, was die Systemgröße beschränkt. In der Timinganalyse ist die Anzahl an diskreten Zuständen, die das Netzwerkverhalten modellieren, zu groß für hybride Model Checking Tools. Im Fall von Active Cell Balancing entsprechen hybride Modelle den initialen, langsamen Modellen, die hier verbessert werden. Die Techniken, die in dieser Dissertation entwickelt werden, integrieren Kommunikations- und Antriebsaspekte auf enge Weise und verbessern dadurch die Genauigkeit und somit die Performance im Vergleich zum Stand der Technik, während effiziente Berechnung gewährleistet bleibt.

# Acknowledgements

This thesis is the result of my work in the embedded systems group (RP3) of TUM CREATE, a research collaboration of Technische Universität München (TUM) and Nanyang Technological University funded by Singapore's National Research Foundation under the CREATE program.

Many people deserve my gratitude for their support. First, I would like to thank my advisor, Samarjit Chakraborty from the Institute for Real-Time Computer Systems (RCS) at TUM, for his advice during the past four years. I consider myself very fortunate to have received your insights and encouragement during our meetings. Furthermore, the collaborations and the research stay you initiated for me are invaluable. At the same time, I also highly appreciate the guidance I have received from Martin Lukasiewycz and Sebastian Steinhorst, the postdocs and team leaders in RP3. We collaborated on virtually all my undertakings and I learned a great deal from you about verification, optimization, and software engineering.

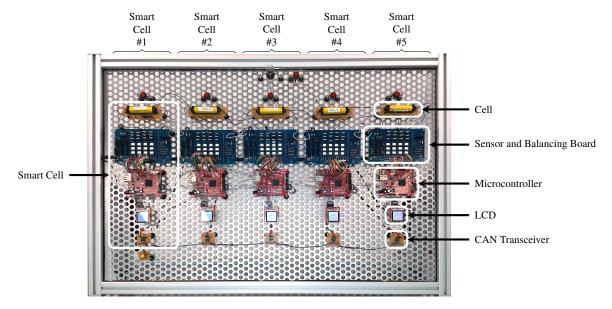

This work contains two major parts: distributed control systems and active cell balancing. With regard to the first part, I would like to thank Reinhard Schneider and Dip Goswami from RCS for answering my incessant questions about timing analysis, real-time calculus, and control systems. With regard to the second part, my gratitude goes to Swaminathan Narayanaswamy and Arne Meeuw from RP3. You have significantly enhanced my understanding of electrical circuits and embedded programming. Many of the experiments from this thesis would also not have been possible without the hardware you built.

My gratitude also goes to Damoon Soudbakhsh and Anuradha Annaswamy from the Active-Adaptive Control Laboratory at the Massachusetts Institute of Technology. During our collaboration which related to both parts, you have taught me a lot about control systems, improving my intuition as well as my understanding of techniques like linear matrix inequality design, adaptive control, or model-predictive control. Thank you also, Dr. Annaswamy, for hosting me in your group in fall 2014 and for being my second reviewer.

I am also fortunate for the colleagues I have had during the last years. Our laughs, technology discussions, and political rants have made the time more than enjoyable. A special note goes to Philipp Mundhenk, Florian Sagstetter, and Peter Waszecki. I hope we can stay in touch and meet for gaming, BBQ, or just a beer. A special thank you also goes to Martin Geier, for help with IT and enlightening Linux discussions, Martin Schäfer, who introduced me to RCS, and Benedikt Dietrich, for help with projects I supervised. Another big thank you is in order for the administrative staff at MIT, TUM CREATE, and at RCS. You have been very helpful and supportive.

Finally, I particularly thank my friends, my parents, Waltraud and Herbert, and my sister Judith for their love, support, and continuous encouragement.

# Contents

| Abstract |                   |                                                                                |    |  |  |  |

|----------|-------------------|--------------------------------------------------------------------------------|----|--|--|--|

| A        | Acknowledgements  |                                                                                |    |  |  |  |

| Ta       | Table of Contents |                                                                                |    |  |  |  |

| 1        | Intr              | Introduction                                                                   |    |  |  |  |

|          | 1.1               | Cyber-physical System (CPS) co-design                                          | 2  |  |  |  |

|          | 1.2               | Active Cell Balancing (ACB) design                                             | 6  |  |  |  |

|          | 1.3               | Contributions and organization                                                 | 9  |  |  |  |

|          | 1.4               | List of publications and awards                                                | 12 |  |  |  |

| 2        | Cyb               | er-physical System (CPS) Analysis                                              | 15 |  |  |  |

|          | 2.1               | Continuous dynamical systems                                                   | 16 |  |  |  |

|          | 2.2               | Communication hardware                                                         | 17 |  |  |  |

|          | 2.3               | Sampled-data systems                                                           | 20 |  |  |  |

|          | 2.4               | Quality of Control                                                             | 24 |  |  |  |

|          | 2.5               | Linear switched systems                                                        | 28 |  |  |  |

|          | 2.6               | Formally verifiable properties for switched systems                            | 29 |  |  |  |

| 3        | Mod               | leling Communication Platforms with Event Count Automata (ECAs)                | 35 |  |  |  |

|          | 3.1               | Event Count Automata (ECAs)                                                    | 35 |  |  |  |

|          | 3.2               | Event Count Automaton (ECA) networks                                           | 38 |  |  |  |

|          | 3.3               | Methods for evaluating Event Count Automata (ECAs)                             | 41 |  |  |  |

|          | 3.4               | Event Count Automata (ECAs) in the model checking tool SAL                     | 46 |  |  |  |

|          | 3.5               | Issues with naive Fixed-Priority Non-preemptive Scheduling (FPNS) models .     | 47 |  |  |  |

|          | 3.6               | Conservative Fixed-Priority Non-preemptive Scheduling (FPNS) models            | 50 |  |  |  |

|          | 3.7               | Evaluation of FPNS models using simulation                                     | 52 |  |  |  |

|          | 3.8               | Related work                                                                   | 55 |  |  |  |

| 4        | App               | lying ECAs for CPS Co-Design                                                   | 59 |  |  |  |

|          | 4.1               | Verification of real-life performance instead of deadlines in distributed CPSs | 59 |  |  |  |

|          | 4.2               | Fault-tolerant control design with delays under firm deadline assumption       | 64 |  |  |  |

|          | 4.3               | Related work                                                                   | 72 |  |  |  |

**x** Contents

| 5     | Qua                            | intitative Models for Charge Transfers in Active Cell Balancing (ACB) | <b>79</b> |  |  |

|-------|--------------------------------|-----------------------------------------------------------------------|-----------|--|--|

|       | 5.1                            | ACB: Motivation, design flow, and challenges                          | 80        |  |  |

|       | 5.2                            | Inductor-based charge transfer architectures                          | 84        |  |  |

|       | 5.3                            | Equivalent circuit modeling                                           | 86        |  |  |

|       | 5.4                            | Electrical battery models                                             | 89        |  |  |

|       | 5.5                            | ACB actuation interfaces                                              | 93        |  |  |

|       |                                | 5.5.1 Fixed timing actuation                                          | 94        |  |  |

|       |                                | 5.5.2 Current interface                                               | 96        |  |  |

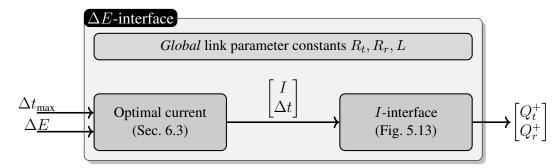

|       |                                | 5.5.3 Energy block interface with platform-determined current         | 97        |  |  |

|       | 5.6                            | Freewheeling phases & switching losses                                | 99        |  |  |

|       | 5.7                            | Transfer dynamics assuming constant voltage                           |           |  |  |

|       | 5.8                            | Large-scale Active Cell Balancing (ACB) simulation                    |           |  |  |

|       |                                | 5.8.1 Straightforward numerical solution                              | 105       |  |  |

|       |                                | 5.8.2 Iterative solution for transfer dynamics                        | 106       |  |  |

|       |                                | 5.8.3 Error-controlled, adaptive phase aggregation                    | 107       |  |  |

|       |                                | 5.8.4 Long-term charge transfer simulation with fixed timing          | 111       |  |  |

|       | 5.9                            | Related work                                                          | 117       |  |  |

| 6     | Opt                            | imizing Efficiency in Active Cell Balancing (ACB)                     | 123       |  |  |

|       | 6.1                            | Optimization-friendly charge transfer model                           | 123       |  |  |

|       | 6.2                            | Inductor optimization via Geometric Programming (GP)                  | 128       |  |  |

|       | 6.3                            | Optimal current for individual links                                  |           |  |  |

|       | 6.4                            | Charge routing problem                                                | 133       |  |  |

|       |                                | 6.4.1 Best case reference solution for charge routing                 |           |  |  |

|       |                                | 6.4.2 Constraint-driven charge routing                                |           |  |  |

|       |                                | 6.4.3 Routing case study                                              |           |  |  |

|       | 6.5                            | Related work                                                          |           |  |  |

| 7     | Con                            | clusions and Future Work                                              | 145       |  |  |

| Bi    | bliogi                         | raphy                                                                 | 149       |  |  |

| Li    | st of '                        | Tables                                                                | 163       |  |  |

|       |                                |                                                                       |           |  |  |

| Lı    | st of 1                        | Figures                                                               | 165       |  |  |

| Li    | List of Definitions & Theorems |                                                                       |           |  |  |

| Al    | Abbreviations Nomenclature     |                                                                       |           |  |  |

| No    |                                |                                                                       |           |  |  |

| Index |                                |                                                                       |           |  |  |

# Introduction

The regulation of dynamical systems using feedback mechanisms has a long history. The first application arguably dates back to ancient Greece where the flow in water clocks was regulated for improved accuracy. Starting with the industrial revolution in the 19th century, centrifugal governors were widely used to control the inflow of steam engines. Alongside further similar contributions, the mathematical formalization of the field also began at that time.

Even though methods for system analysis in time domain like the solution of Ordinary Differential Equations (ODEs) and stability concepts were known, the lack of computation power made them infeasible in practice. Frequency domain analysis, by contrast, makes it easier to characterize a system from external measurements and the arithmetics it involves remain tractable for computation by hand. This made it the method of choice at that time. Only the arrival and subsequent massive growth of computing devices has increased the focus on time-based methods over recent decades. Numerically efficient and stable techniques were devised to test system stability, design optimal input signals, and reconstruct unobservable system states, among other applications.

In addition to a dramatic expansion of system analysis techniques, digital devices have also led to new actuation and controller implementation methods. By introducing computation power into the system itself, the class of digital control systems provides a lot of new options to the strategy designer. The main advantage is that calculation steps can be freely chosen and no longer require individual physical components that represent them. Digital actuation, on the other hand, significantly increases the efficiency of, e.g., electric motors or power supplies. While the addition of digital devices creates size, efficiency, and flexibility benefits over previous analog or mechanical implementations, the so-created interaction also changes the system behavior and may require adjustments in the design techniques.

Combining the behavior of digital implementation platform and physical control process into one holistic model is difficult because their respective models deal with very different phenomenons. The dynamics of the control process are typically expressed in continuous time,

using differential equations. In the digital platform, on the other hand, topics like processor architecture, scheduling strategy and communication protocol contain many discrete aspects. During the design process of the physical side, the behavior of the digital side must hence be abstracted according to a suitable interface and vice versa.

The selection of interfaces for digital control design involves a trade-off between modeling accuracy, validity area, and speed. In this context, the thesis at hand develops interfaces that are more expressive than the state of the art and hence lead to better designs but also remain computationally efficient to enable rapid iteration and optimization during the design phase. With this goal, we investigate two different setups. The first (Section 1.1) deals with the effects of communication delay on the control performance of quickly evolving systems. As the number of control applications keeps growing, the digital implementation platforms become increasingly distributed, creating contention on shared buses and processors. This calls into question several standard assumptions about the computation behavior and complicates the design task for the implementation platform. The second setup (Section 1.2) considers switching actuation and analyzes a family of circuits that transfer charge within battery packs for improved performance. In contrast to paradigms where switching is undesired, switching-actuated systems are controlled by adjusting the, typically brief, time periods for which they maintain certain discrete configurations. Charge transfer is particularly challenging since the averaging approach, which is typically employed to circumvent non-differentiable transitions and the associated modeling difficulties, becomes inaccurate as internal states evolve. These challenges are summarized in Table 1.1.

CPS co-design (Section 1.1) Charge transfer (Section 1.2) Physical Fast control process Cells with transfer circuitry Digital Controller-implementing hardware Actuation by transistor switching Challenge Delay not negligible and varying Input via timing variation Timing specification Conversion: current ↔ timing Interface Cannot model platform character-Conversion is voltage- and thus Gap istics, i.e., causes for delay state-dependent

Table 1.1: Overview of challenges

Both setups deal with a semantic gap between models for the physical dynamics and the behavior of a digital device. This gap interferes with accurate analysis of the system as a whole. Several approaches that lead to tighter integration for better performance, faster simulation at virtually identical accuracy, and efficient optimization are developed in the context of this thesis. Section 1.3 details how these contributions and the publications they have led to form the remainder of the work at hand.

## 1.1 Cyber-physical System (CPS) co-design

In digital control, a computing device is used as system controller to calculate input signals at runtime. Inexpensive microcontrollers are typical for this role, but Application-Specific In-

tegrated Circuits (ASICs) or desktop computers are also reasonable depending on the performance requirements. The controller in such a setup periodically evaluates the sensor values describing the system state and subsequently calculates the input signals for actuation at runtime. Forgoing analog components in that way provides many benefits, but it may also require certain adjustments to the analysis methods.

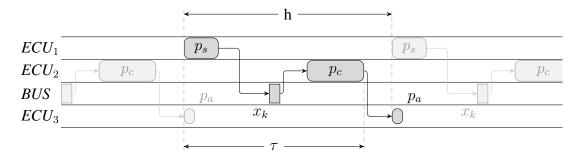

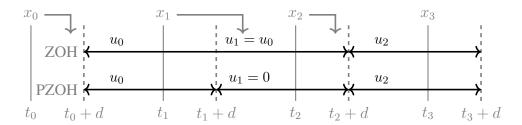

The controller cannot compute input signals continuously as that would correspond to infinite frequency. For this reason, input signals in digital control typically remain constant for a certain period; a case of digital control with a different actuation abstraction is discussed in Section 1.2. The standard periodic behavior of the computation suggests a transformation of the mathematical models that describe the physical world for easier analysis. Instead of calculating the continuous-time dynamics of such a digital control system directly, it is common to consider them only with respect to the discrete time steps that are implicitly defined by the sampling period of the controller. Many previous results for system analysis and design have been adjusted to systems described in this way, so-called discrete-time systems.

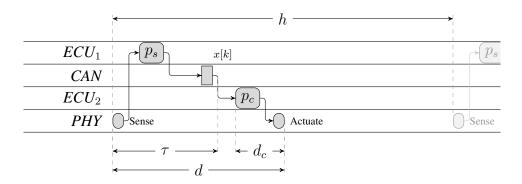

When the digital control framework was formed, ideal circumstances in military applications, space missions, and avionics have justified a number of idealistic assumptions about the underlying computation platform. The most common of these assumptions are negligible computation times, infinite numerical precision as well as zero communication delays between sensor, controller, and actuator. With a dedicated controller that has direct access to sensors and actuators, such assumptions are approximately satisfied and small deviations are unlikely to produce large errors. Such setups are expensive and increasingly rare, however, as digital control systems have become ubiquitous, even in cost-sensitive industries like automotive, home automation, and energy storage. In these industries, computation power is more limited and control applications are implemented in a distributed fashion. Each Electronic Control Unit (ECU) typically handles many control tasks and no longer has direct access to sensors and actuators. Instead, sensor readings are sent over a network, processed by one or more ECUs along the way, before finally arriving at the actuator. In such an implementation environment, some simplifying assumptions become difficult to satisfy in practice. The most important of these is non-negligible delay introduced by contention on shared communication and sometimes computation resources.

A modern design flow must account for this constrained environment and simultaneously handle the vastly increased number of control applications and the ensuing complexity. Cars from 2013, for instance, ship with around 100 million lines of code [139], roughly 5 times more than the LINUX kernel in June 2015 [105]. Notwithstanding that this comparison may be misleading because car software is made up of components that probably include the LINUX kernel, cars have come a long way. "Even low-end cars now have 30 to 50 ECUs embedded in the body, doors, dash, roof, trunk, seats, and just about anywhere else ... [In 1981,] GM was ... executing about 50 000 lines of code across its entire domestic passenger car production." [42]. The formerly hand-crafted code that runs on these ECUs is mostly auto-generated today by graphical frameworks that model the signal flow. This creates an additional layer of abstraction that must be reasoned about.

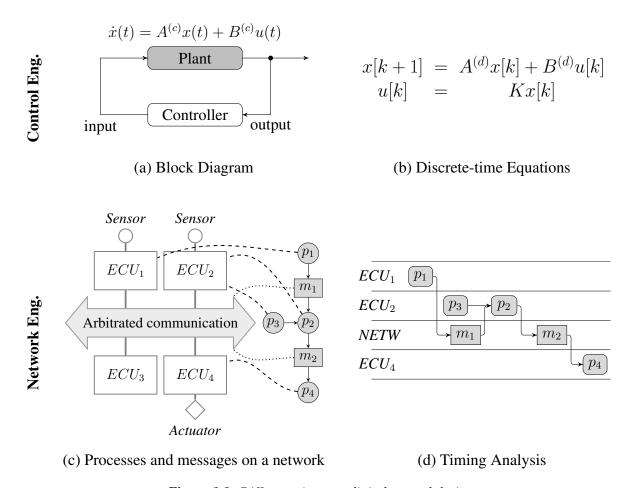

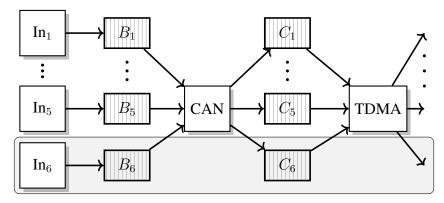

To deal with the growing complexity, different abstractions are used to analyze individual subsystems. A control engineer would typically start by considering the block diagram of a control problem. An example of such a diagram which helps to focus on the relations between

subsystems, is shown in Fig. 1.1(a). In this perspective, the engineer first models the so-called *plant*, consisting of the physical process to be controlled and an actuator. The plant is described in time domain by a standardized ODE system, the so-called *state space representation*. While there are alternatives like transfer functions, this form has advantages when analyzing systems with multiple in- and outputs or with nonlinear behavior, justifying its increasing general popularity. More importantly for the work at hand, this representation makes reasoning about timing analysis and delay issues more natural. To obtain such a mathematical representation, the plant is usually analyzed according to fundamental mechanical and electrical principles in bottom-up fashion. As an alternative, semi-automated or guided system identification [118] procedures are available that yield sufficiently accurate results in many circumstances.

Once a suitable plant description is available, the engineer deals with equations for control law design and discrete-time transformation as in Fig. 1.1(b). These operations can be performed in any order as long as sampling period and delay remain small compared to the change rate of the plant. During control law design, engineers search for a mapping, often a gain matrix K, between system state and input signal. This mapping, the control law, defines an action for each possible state. To find it, many techniques have been established, guaranteeing various properties for different system classes. The Linear Quadratic Gaussian (LQG) framework [11], for instance, minimizes a quadratic cost function using only a gain matrix and no optimization at runtime. To transform the continuous system to its discrete version, a fixed delay and sampling period are utilized as discussed earlier in this section. During this phase of control application design, the underlying hardware platform is hence typically taken into account according to this interface specifying period and maximum delay.

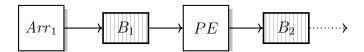

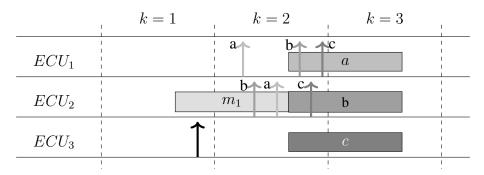

The network engineer, on the other hand, considers the dependency chain formed by the computer processes and messages that implement the corresponding control application shown in Fig. 1.1(c). He or she distributes the elements of this chain on a network of ECUs and communication links or buses. Once the computation cost of a process is established, it corresponds to a specific time requirement depending on the power of the selected ECU. Similarly, the size of a message implies the time it needs to be transmitted over a certain communication bus. With this knowledge, each process / message chain distribution corresponds to a timing diagram as in Fig. 1.1(d). Such a diagram details how the message timing and in particular how the end-to-end or sensor-to-actuator delay behaves. Several frameworks have been devised to find analytic bounds for the timings in such a network. Real-time Calculus (RTC) [178], for instance, applies a mathematical convolution at each processing element to a stream with given arrival behavior and obtains worst-case delays and backlog in this way, among other properties.

While distributing the elements of control applications in the network, the dependency of the processes, the location of sensors and actuators, as well as the timing specifications must be observed. This is a large set of complex conditions, but it may still leave significant flexibility. If the network is not fixed yet, one may be interested in its topology and its components. Even on a fixed network, process distribution, priority assignment, and other parameterizations remain complicated, yet relevant questions. Searching for an optimal network according to metrics like price, volume, or extensibility given such a set of constraints is commonly referred to as Design Space Exploration (DSE). There are many DSE techniques, relying on methods like integer programming, boolean satisfiability, or evolutionary algorithms [71].

In most network design endeavors, the control application requirements are considered as

Figure 1.1: Different views on digital control design.

period / deadline specification. This specification matches the period / maximum delay description that abstracts the hardware platform during control design. There are several issues with this interface. Often, a very low sampling period is selected along with an ideal zero delay to achieve great performance during simulation. Sampling too often wastes computation and communication resources, however. More importantly, zero delay cannot be obtained in practice. A lengthy and costly test phase is then required to analyze the real behavior and guarantee the safety of a system. If the specification is selected to be more achievable, it may forgo control performance without leading to a real benefit on the network side.

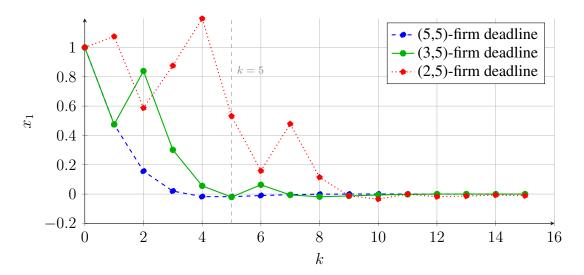

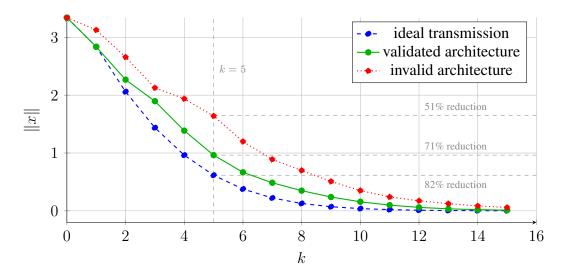

Instead of a design process that is driven by either network or control requirements, the *Cyber-physical System (CPS)* paradigm aims for an integration of both sides and ideally a *codesign of control law and hardware platform*. Even in such a general setting, the interface itself may hide optimal solutions from the design process, however. This is the case when specifying only period and maximum delay. As the average is typically smaller than the worst-case delay in complex networks, operating a control application with shorter deadline and some timeouts often leads to improved control performance.

Since a fully holistic co-design with one model that includes detailed network and plant

behavior together remains infeasible, all interfaces must strike a balance between design speed and abstraction level. The computing power for off-line analysis has grown tremendously, however, bringing tools within reach that were infeasible only a decade ago. One such tool that is well-suited for the analysis of worst-case behavior is model-checking [12] as commonly applied in the area of digital circuit design.

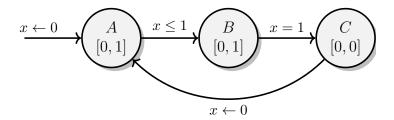

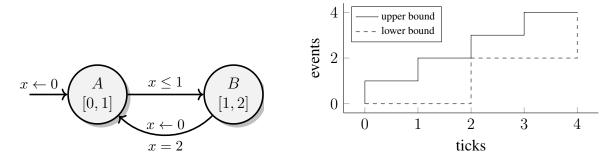

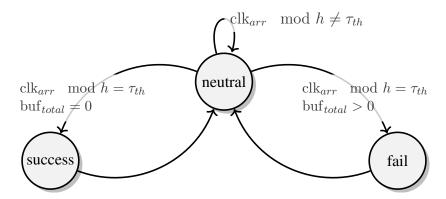

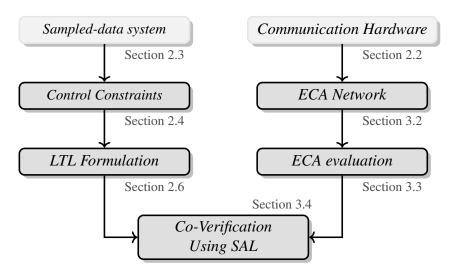

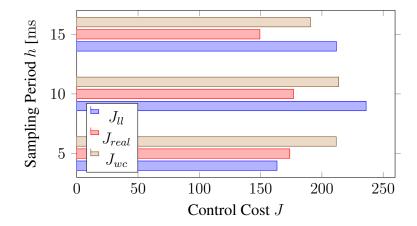

In the first part of this thesis, we investigate how model-checking can support the co-design goals of the CPS paradigm. For this purpose, we mainly deal with an extension of the aforementioned RTC timing analysis framework that is based on model-checking, the Event Count Automaton (ECA) framework. Originally devised to analyze buffer requirements and delay under state-dependent scheduling behavior, it is also well-suited to treat sporadic deadline misses. On the control engineering side, we analyze the resulting performance on platforms whose behavior is guaranteed via ECA evaluation. As a further step, we then look for strategies that specifically rely on this interface of behavior guarantees. These approaches provide a tighter integration than state-of-the-art interfaces and can hence often improve the resulting control performance in a co-design setting.

## 1.2 Active Cell Balancing (ACB) design

Another challenge for CPS design are digital actuation schemes. In contrast to the timing-based interaction described in Section 1.1, these schemes may require special care even for physical processes that evolve much slower than any potential network delay. As a case where standard analysis is not sufficient, this part discusses charge transfer circuits for balancing battery packs at high frequency.

The background of these circuits is the dramatic proliferation of Electrical Energy Storage (EES) and the various applications it enables that occurred in the post-millennial years. Laptop sales now exceed those of desktop computers; smartphones and tablets have their own success stories. At the same time, there is a growing interest in Electric Vehicles (EVs) as well as residential EES. This interest is part of a general desire for clean energy and transportation arguably motivated by peak oil discussion, high fuel prices, and environmental concern. An EV may completely rely on electrical energy for zero local emissions or use it to improve the combustion engine's efficiency. Residential EES mainly aims to smoothen the non-homogeneous output of renewable power sources and to increase independence from the regional power grid.

While some applications favor other technologies like super-capacitors or fuel cells, most store electrical energy in Lithium-Ion (Li-Ion) battery cells because of their high energy density. When the electrodes of such a rechargeable cell are connected, an electrochemical reaction causes an electrical current to flow. The voltage that Li-Ion cells can achieve during this discharge process is around 4 V, limited by the cell chemistry. To form the basis for a wide range of applications, many cells are hence typically connected in series and in parallel. While cells in parallel connection inherently reach an equilibrium and can be considered as electrical unit, the charging or discharging of serially connected cells must stop as soon as the first cell reaches its limit. Imbalances between these cells, caused by differences in capacity and internal resistance from production or by non-homogeneous cooling, hence reduce the effective capacity of the pack.

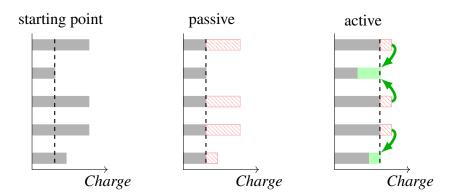

Figure 1.2: Variations in cell characteristics lead to imbalances over time, leaving some cells with excess charge above the current pack level (dashed). Passive balancing, which is the current standard because it can easily be implemented, simply discards local excess charge (hatched). Active balancing techniques instead transfer the surplus and thus achieve higher pack charge levels.

For applications that require high voltage, and thus many cells in series, imbalances are currently alleviated in two ways. First, cells with similar properties are clustered at production time to minimize deviations in capacity and internal resistance, e.g., by cell weight and volume. The deviations that are potentially avoided in this way exceed 5% [161]. This is not sufficient, however, since the properties of identical cells evolve differently over time, even under lab conditions [19]. Second, excess energy in individual cells is therefore dissipated using switchable resistors [82]. This technique, referred to as *passive balancing*, is easy to implement, but clearly not energy-efficient.

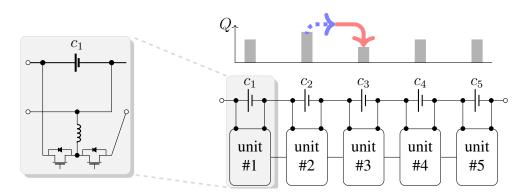

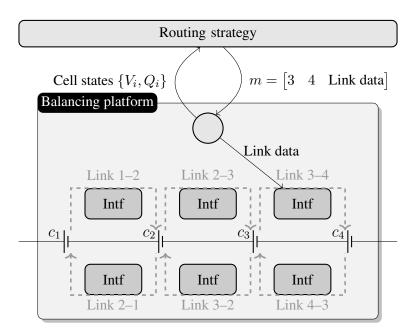

Alternatively, the excess charge can also be transferred to other cells. Fig. 1.2 illustrates schematically how this approach, referred to as *Active Cell Balancing (ACB)*, increases the usable energy of a battery pack and consequently its performance. While ACB can be implemented in numerous ways [32], the implementations can be grouped by the transfer mechanism they rely on. This mechanism is usually determined by the main circuit component or components that perform the charge transfer. For instance, capacitors can be connected in parallel to cells and charge or discharge them in this way. Such parallel connections lead to rather inefficient charge transfer, however. Alternatively, suitable shunting at runtime can create additional rest periods for cells with less charge. This approach balances the pack under load, but it leads to voltage fluctuation if not controlled and requires switches in the main series connection of the battery pack. Having switches there affects the efficiency during standard operation, however, which is usually not acceptable. The most efficient ACB implementations are built around inductors or transformers and actuated with switching signals in the kilohertz range.

To obtain a well-performing ACB application, several decisions, simulations, and optimizations are necessary. The following design flow summarizes the overall process.

- 1. Select transfer mechanism and define topology requirements.

- 2. Synthesize suitable circuit architecture including transistor switching scheme.

- 3. Determine size requirements and choose circuit components accordingly.

#### 4. Design control strategy.

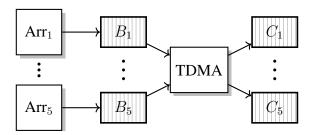

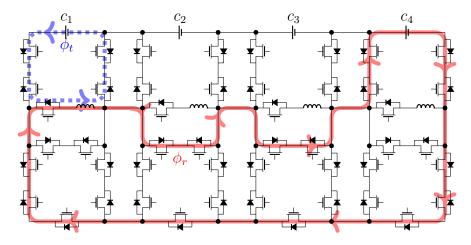

The first stage begins with the selection of the transfer mechanism. While there are several options, as just discussed, this thesis focuses on the class of inductor-based architectures for efficiency reasons. One then defines the topology of the circuit. This is mainly about the kind of transfers that the circuit shall be able to perform. Transferring only between adjacent cells may be sufficient in some cases; others may require transfers to non-adjacent or multiple cells. Another popular design has one cell always transfer to or from the whole pack. Further desirable properties include modularity and concurrency. Modularity helps when additional cells are added to a pack. Performing transfers concurrently, on the other hand, vastly reduces balancing time. If shorter balancing times are not required, concurrency can also lead to lower currents and consequently to higher efficiency in most cases.

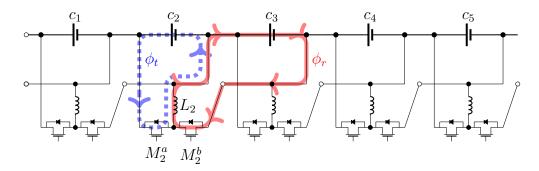

In the second stage, a circuit architecture is synthesized according to the specification from the first stage. For this purpose, a network of transistors is created to connect transferring components, like inductors, to cells. The transistors are then switched according to a scheme that defines their configuration in several recurring phases. This switching realizes the actual charge transfer. While this stage only deals with qualitative behavior and component parameters do not play a role yet, switching scheme and circuit architecture must be analyzed together for potential issues like short circuits or undesired cell discharging. Although the architecture can be designed by hand and verified in a standard circuit simulator, dedicated tools for faster verification and even automated synthesis are also emerging [123]. As an alternative to synthesizing, it is also often possible to utilize an existing architecture from the literature, such as the inductor-based circuit for transfers between adjacent cells from [103].

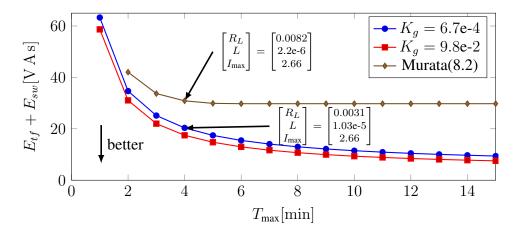

The third stage deals with component selection or design in the circuit architecture obtained so far. The numerous, not necessarily identical transistors and most importantly the inductor determine under which scenario a circuit performs best. In the fourth stage, control strategies for the actuation at runtime are devised. Depending on charge distribution in the pack and available time, different current rates and transfer sequences may be beneficial. To justify decisions in these two stages, the system behavior must now be treated quantitatively. General purpose circuit simulators may be used for ACB evaluation, but they have drawbacks like low flexibility and long computation times, among other things. It is hard to implement sophisticated strategies in a circuit simulator because state information is hard to aggregate and many mathematical operations are not readily available. Similarly, many efficient optimization techniques are impossible because they require access on the equation level. Even simulation may become unacceptably slow for larger systems or longer time frames. The high-frequency switching that actuates the charge transfers leads to correspondingly small steps in the simulator. A balancing strategy, on the other hand, may have to be evaluated over several hours and therefore require millions of steps. In this area, switching details are hence often abstracted away, e.g., by averaging. While this leads to simple formulations, it also creates a modeling gap with additional relative errors of several percent points. On the other hand, faster simulation and mathematical programming techniques are also possible in a lossless fashion by directly looking at fundamental electrical principles, like Kirchhoff's laws. This provides more insight and direct access to equations of the transfer dynamics.

Even though this work contains contributions to the second stage, its focus is on the third

and fourth stage. It develops quantitative models that apply to the large class of inductor-based charge transfer circuits, pursuing two main goals. The first is accurate, but fast simulation of ACB. The second is optimization of ACB using mathematical programming. Although more complex than in Section 1.1, a transformation to discrete-time helps to identify actuation interfaces that formalize the long-term system behavior. The contributions to both goals build on this interim result as these interfaces lead to further important reformulations.

## 1.3 Contributions and organization

After introducing the background information from CPS co-design and ACB design in the previous sections, this section discusses the results of the thesis at hand. After listing contributions, it explains the organization of the remaining chapters, detailing in particular how they relate to previous publications of the author.

The main contributions of this work are summarized as follows.

- Integration of the Event Count Automaton (ECA) timing analysis framework into Cyberphysical System (CPS) design, creating an interface that allows direct verification of control performance for distributed linear systems from within the timing analysis.

- Development of a fault-tolerant control strategy design that uses the information about the implementation platform from ECA analysis in a Linear Matrix Inequality (LMI) formulation to yield an improved design under limited network resources.

- Addition of Fixed-Priority Non-preemptive Scheduling (FPNS) to the ECA framework, handling issues with priority inversion and the ensuing message blocking.

- Investigation and advancement of models for charge transfer dynamics, proposing a total of 3 models that are no longer anchored to the natural switching phases in the microsecond range and can hence be used for accurate, but rapid long-term simulation (speedup of 5 orders of magnitude compared to standard simulation) or mathematical programming.

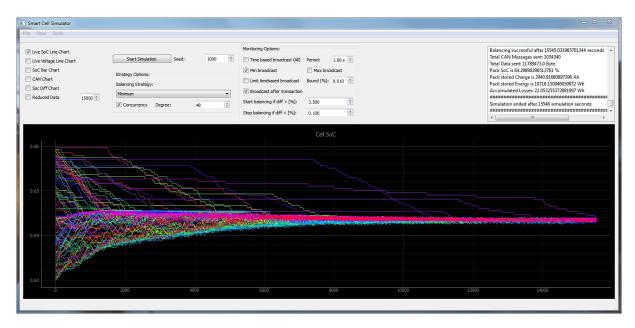

- Development of a PYTHON library with C++ back end that implements the aforementioned transfer models used, for instance, in the distributed balancing co-simulator of the author's research group.

- Application of the models for optimal design of inductors for charge transfer architectures using Geometric Programming (GP), formalization of high-level actuation interfaces as well as design and evaluation of efficient charge routing strategies.

This thesis is organized in 7 chapters. The current chapter gives an overview of the environments it aims to improve, CPS co-design with a focus on delay effects as well as ACB design with switching actuation. By describing the current situation and challenges, it provides context for the contributions of the work. The contributions themselves are explained in greater detail in the remainder of the thesis which is structured as follows.

Chapter 2 provides background information on CPS analysis. It summarizes the standard approach for describing physical processes in control applications which we require for delay

analysis, the so-called state space representation. This representation exists in continuous-time and discrete-time form. The latter arises when a digital device senses or actuates a physical process, turning the overall setup into a sampled-data system. After describing the transformation from continuous- to discrete-time form, the chapter goes over the standard properties and performance measures for control applications. As we are interested not only in messages that arrive with delay, we then treat switched systems which are necessary to model messages that do not arrive at all. The chapter ends with an explanation of standard properties or variations thereof which are compatible with formal languages for model-checking. This content is included as reference; the contributions from the following chapters build upon this foundation in many cases.

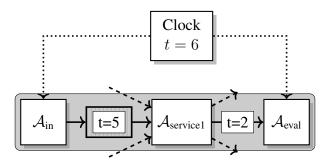

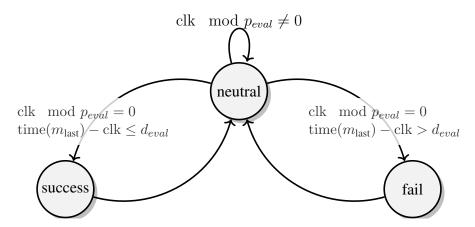

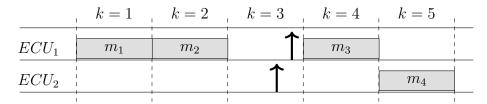

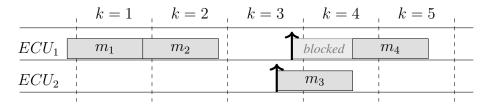

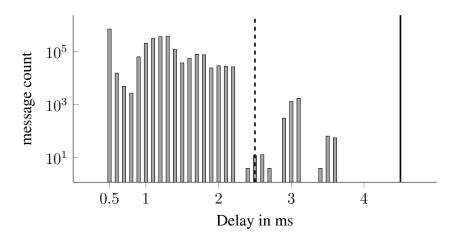

Chapter 3 introduces the Event Count Automaton (ECA) framework, an approach for timing analysis of communication and computation networks. It first describes the two automaton types this framework employs, the service and the arrival ECA, both formally and with examples. The chapter then shows how multiple ECAs can be combined to form a network by connecting them using in- and output buffers. Modeling a hardware platform, such an ECA network can then be analyzed with model checking tools for various properties, like maximum delay. Although other tools are also suitable, this thesis relies exclusively on SAL [54] for model-checking. To give an impression of ECA analysis in practice, the chapter thus includes some code snippets from the Scheme-like, functional programming language utilized in SAL. Following the basic introduction of the ECA framework, an extension of its semantics is then shown to model FPNS in this paradigm. Unlike for time-triggered scheduling protocols that directly map to the slots of a discrete-time automaton like an ECA, a model for FPNS is not straightforward. Since the non-interruptible transmissions can begin not only at slot transitions but also within slots, the resulting communication behavior may depend on intra-slot arrival times that cannot be tracked using discrete-time automata. The modeling approach described here treats the bus in a conservative way to capture problematic behavior like priority inversion that a straightforward implementation would miss. The FPNS model and the corresponding extension of the ECA semantics have been originally presented in [92].

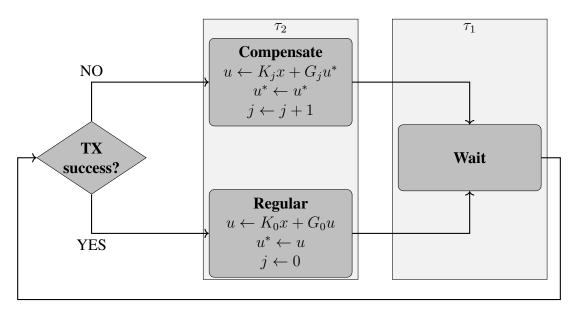

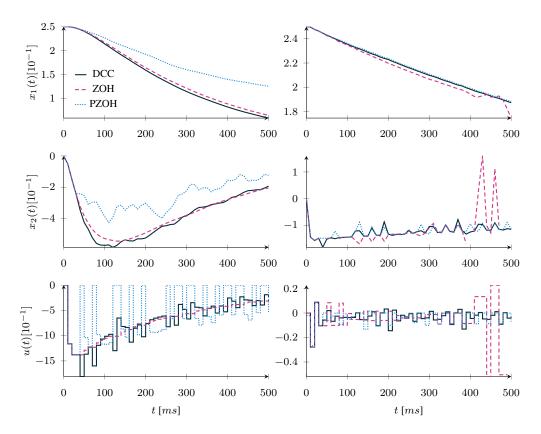

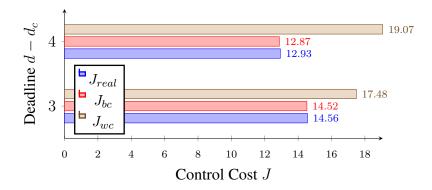

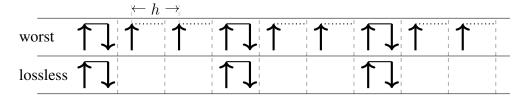

Chapter 4 describes two applications of the ECA framework in the CPS setting. Both applications utilize the fact that the worst-case delay in complex hardware platforms only rarely occurs. Since feedback control systems are inherently robust to a certain number of communication faults, they may not require the hardware over-provisioning a worst-case design entails. For this reason, the applications build on an interface that allows individual messages to miss their deadlines according to specified amounts or patterns. In the first application, this interface is used to implement given control applications with certain performance requirements on a hardware platform. To that end, the performance requirements are analyzed to find the tolerable patterns of deadline misses in a form that model-checking tools can treat. These patterns are subsequently verified on a hardware platform modeled by ECAs. This approach typically leads to specification-conform designs with higher bus utilization and hence reduced costs. The second application aims to improve control performance given a certain hardware platform. For this purpose, a fault-tolerant control strategy design is proposed that builds upon the same ECA-verified interface. Using a LMI formulation solved via mathematical programming, the approach finds a controller that takes into account the recent communication faults at runtime to generate an improved input signal. This design fulfills exponential stability, a common control

performance requirement, by construction. A description of these applications has appeared in [91] and [90], respectively.

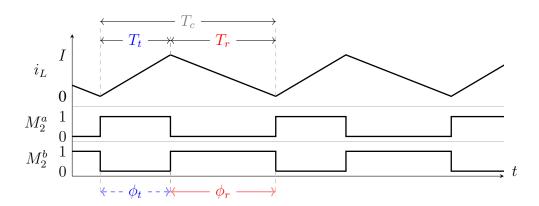

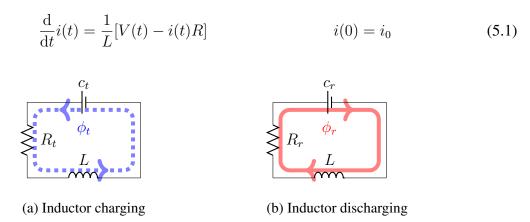

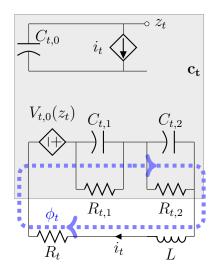

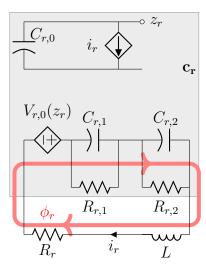

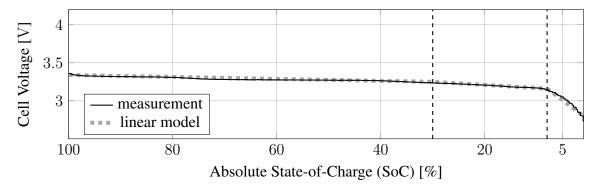

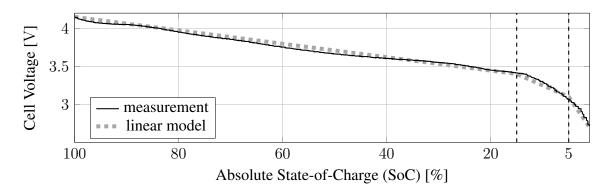

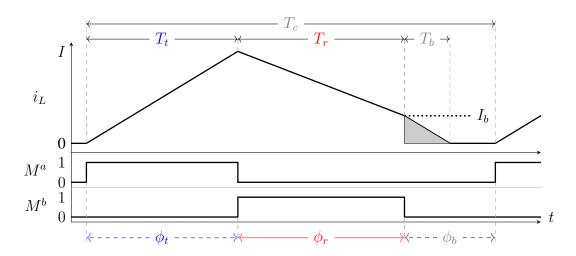

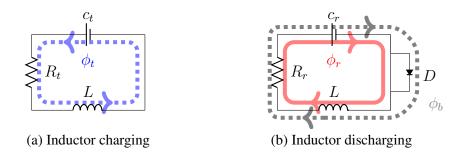

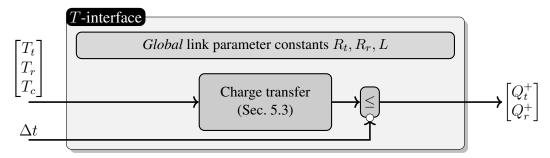

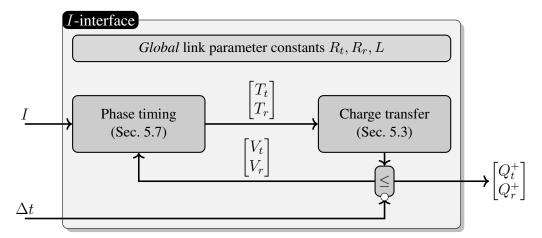

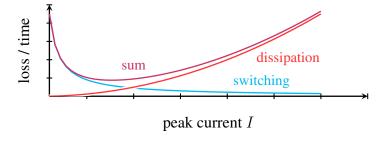

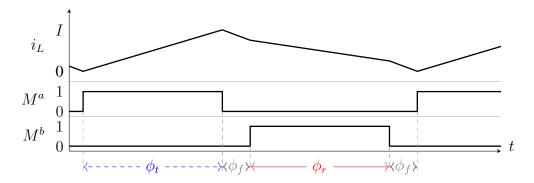

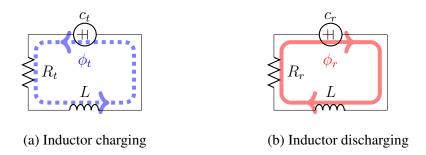

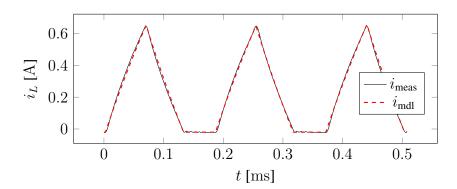

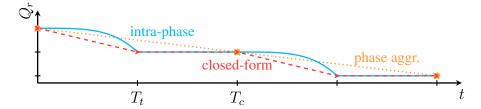

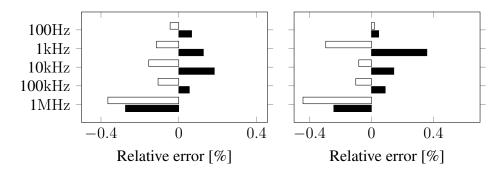

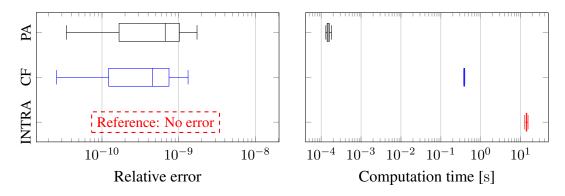

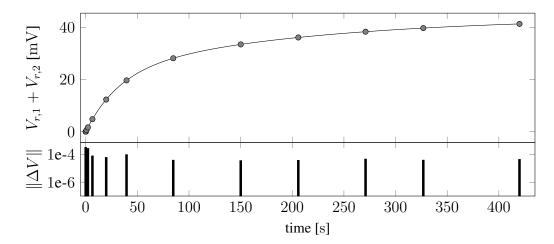

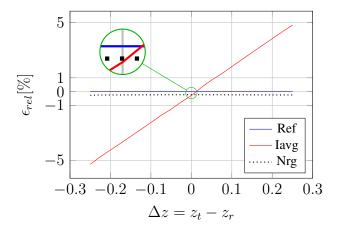

Chapter 5 discusses quantitative models for inductor-based Active Cell Balancing (ACB). It begins by presenting a selection of circuit architectures from this class of charge transfer circuits with switching actuation and explains the fundamental operating principles. These circuits charge an inductor from one cell, then change the configuration of their routing switches and discharge the inductor into another cell. Each configuration transition leads to a non-differentiable change in the transfer dynamics which is challenging for standard simulation techniques and unwieldy for actuation strategy design. A numerical solver for such dynamics commonly operates with an adaptive step size approach, aiming to make only few, large steps as long as an associated error estimate fulfills its specification. The non-differentiable transitions force such solvers to make multiple steps for each configuration change. This is slow because switching occurs in the microsecond range while balancing operations may last for several hours and hence require millions of steps over hours of computation time. Many models that are computationally cheaper, on the other hand, are also simple, ignoring transistor switching effects, the evolution of voltages, or the parasitic reactions in the involved battery cells. Nevertheless, many improvements are possible, both towards accurate yet fast ACB simulation and more natural actuation interfaces. The improvements developed here build on an equivalent circuit modeling approach that abstracts nonlinear circuit components and treats each switch configuration, or phase, as individual ODE. These ODEs have closed-form solutions under virtually all parameterizations and can thus be converted to a recurrence relation, similar to the discrete-time form of the state space representation in digital control.

This discrete recurrence relation is still too slow for large-scale simulations but it enables high-level actuation interfaces and subsequently two rapid simulation models, each with its own advantages. The first, most precise, and most versatile model uses error control techniques to take large steps in the discrete recurrence relation. In this way, it remains compatible with various common battery models and application interfaces. The second approach achieves even faster simulation times by solving the recurrence relation in closed form, assuming an actuation interface that leaves switching periods constant for many iterations. One charge transfer architecture with detailed switching scheme and the equivalent circuit approach has been published in [88]. The first simulation model has been submitted to IEEE Transactions on Computeraided Design of Integrated Circuits and Systems in January 2016. The second model forms an integral part of the co-simulator published in [166].

Chapter 6 builds on the developed transfer models to evaluate and improve the performance of ACB operation in three aspects: inductor design, local operating current, and routing strategies. To that end, it describes a transfer model that caters specifically to optimization and accepts some mathematical transformations with accuracy loss in unlikely operating regions. It then details a GP that can be used to design an optimal inductor for an ACB circuit. Although this program also deals with the operating current, the computation is too involved to be performed at runtime. The chapter hence goes on to discuss a closed form solution for the optimal current and a best-case Linear Programming (LP) formulation for the charge routing problem. The former is now accessible to virtually any computing device, the latter can be efficiently solved on contemporary personal computers. The LP result is a reference value, indicating what a routing strategy can achieve, and a set of transfers that attain this value assuming ideal

voltages in all participating cells. As heuristic routing strategies without concurrent transfers almost achieve this value already, we then investigate the main constraints from the LP to find a strategy that parallelizes more naturally and remains suitable for implementation on embedded devices. Several heuristic routing strategies have been introduced in the papers that make up Chapter 5. Inductor optimization has been presented in [89].

In Chapter 7, we summarize the results and conclude this work. We reevaluate the proposed techniques in a bigger picture and suggest conditions to double-check before resorting to involved CPS design or ACB over simpler alternatives. Future research endeavors are motivated by pointing out potential and risk of the presented interfaces in the DSE context, the options for even more accurate charge transfer models, and rarely explored benefits of ACB.

## 1.4 List of publications and awards

The contributions to Cyber-physical System (CPS) co-design and the Event Count Automaton (ECA) framework from this thesis have appeared in the following publications:

- Matthias Kauer, Sebastian Steinhorst, Dip Goswami, Reinhard Schneider, Martin Lukasiewycz, Samarjit Chakraborty. "Formal Verification of Distributed Controllers using Time-Stamped Event Count Automata". In: Proceedings of the 18th Asia and South Pacific Design Automation Conference (ASP-DAC 2013).

- <u>Matthias Kauer</u>, Sebastian Steinhorst, Reinhard Schneider, Martin Lukasiewycz, Samarjit Chakraborty. "Automata-Theoretic Modeling of Fixed-Priority Non-Preemptive Scheduling for Formal Timing Verification". In: Proceedings of the 19th Asia and South Pacific Design Automation Conference (ASP-DAC 2014).

- <u>Matthias Kauer</u>, Damoon Soudbakhsh, Dip Goswami, Anuradha M. Annaswamy, Samarjit Chakraborty. "Fault-Tolerant Control Synthesis and Verification of Distributed Embedded Systems". In: Proceedings of the Conference on Design, Automation and Test in Europe (DATE 2014).

The contributions to architectures, models, and optimization for Active Cell Balancing (ACB) have appeared in the following publications:

- Matthias Kauer, Swaminathan Narayanaswamy, Sebastian Steinhorst, Martin Lukasiewycz, Samarjit Chakraborty, Lars Hedrich. "Modular System-Level Architecture for Concurrent Cell Balancing". In: Proceedings of the 50th Design Automation Conference (DAC 2013).

- Matthias Kauer, Swaminathan Narayanaswamy, Sebastian Steinhorst, Martin Lukasiewycz, Samarjit Chakraborty. "Many-to-Many Active Cell Balancing Strategy Design".

In: Proceedings of the 20th Asia and South Pacific Design Automation Conference (ASP-DAC 2015).

- Matthias Kauer, Swaminathan Narayanaswamy, Martin Lukasiewycz, Sebastian Steinhorst, Samarjit Chakraborty. "Inductor Optimization for Active Cell Balancing using

*Geometric Programming*". In: Proceedings of the Conference on Design, Automation and Test in Europe (DATE 2015).

- Sebastian Steinhorst, <u>Matthias Kauer</u>, Arne Meeuw, Swaminathan Narayanaswamy, Martin Lukasiewycz, Samarjit Chakraborty. "Cyber-Physical Co-Simulation Framework for Smart Cells in Scalable Battery Packs". To appear in: ACM Transactions on Design Automation of Electronic Systems (TODAES).

- <u>Matthias Kauer</u>, Swaminathan Narayanaswamy, Sebastian Steinhorst, Samarjit Chakraborty. "Rapid Analysis of Active Cell Balancing Circuits". Under Submission.

The following publications are related to the topic of this thesis, but not a direct part hereof:

- Martin Lukasiewycz, Sebastian Steinhorst, Florian Sagstetter, Wanli Chang, Peter Waszecki, <u>Matthias Kauer</u>, Samarjit Chakraborty. "Cyber-Physical Systems Design for Electric Vehicles". In: Proceedings of the 15th Euromicro Conference on Digital System Design (DSD 2012).

- Dip Goswami, Martin Lukasiewycz, <u>Matthias Kauer</u>, Sebastian Steinhorst, Alejandro Masrur, Samarjit Chakraborty, S Ramesh. "Model-Based Development and Verification of Control Software for Electric Vehicles". In: Proceedings of the 50th Design Automation Conference (DAC 2013).

- Martin Lukasiewycz, Sebastian Steinhorst, Sidharta Andalam, Florian Sagstetter, Peter Waszecki, Wanli Chang, <u>Matthias Kauer</u>, Philipp Mundhenk, Suhaib A. Fahmy, Shreejith Shanker, Samarjit Chakraborty. "System Architecture and Software Design for Electric Vehicles". In: Proceedings of the 50th Design Automation Conference (DAC 2013).

- Peter Waszecki, <u>Matthias Kauer</u>, Martin Lukasiewycz, Samarjit Chakraborty "*Implicit Intermittent Fault Detection in Distributed Systems*". In: Proceedings of the 19th Asia and South Pacific Design Automation Conference (ASP-DAC 2014).

- Swaminathan Narayanaswamy, Sebastian Steinhorst, Martin Lukasiewycz, <u>Matthias Kauer</u>, Samarjit Chakraborty. "Optimal Dimensioning of Active Cell Balancing Architectures". In: Proceedings of the Conference on Design, Automation and Test in Europe (DATE 2014).

- Sebastian Steinhorst, Martin Lukasiewycz, Swaminathan Narayanaswamy, <u>Matthias Kauer</u>, Samarjit Chakraborty. "Smart Cells for Embedded Battery Management". In: Proceedings of the 2nd International Conference on Cyber-Physical Systems, Networks, and Applications (CPSNA 2014).

- Sebastian Steinhorst, Zili Shao, Samarjit Chakraborty, <u>Matthias Kauer</u>, Shuai Li, Martin Lukasiewycz, Swaminathan Narayanaswamy, Muhammad Usman Rafique, Qixin Wang. "Distributed Reconfigurable Battery System Management Architectures". In: Proceedings of the 21st Asia and South Pacific Design Automation Conference (ASP-DAC 2016).

• Swaminathan Narayanaswamy, <u>Matthias Kauer</u>, Sebastian Steinhorst, Martin Lukasiewycz, Samarjit Chakraborty. "Modular Active Charge Balancing for Scalable Battery Packs". Under Submission.

In addition, the work performed for this thesis has led to the following awards.

- *HiPEAC Paper Award*, 2013: Recognition for European contributions at conferences where Europe is not strongly represented.

- A. Richard Newton Young Student Fellow Program, 2013: Travel grant for  $\approx 50$  students at Design Automation Conference in Austin, TX

- Global Young Scientists Summit, 2014: Discussion opportunity with eminent technology leaders

- ACM SIGDA CADathlon 2014 at International Conference On Computer Aided Design (ICCAD): ECA modeling paper [92] was selected as functional verification problem.

2

# Cyber-physical System (CPS) Analysis

Cyber-physical Systems (CPSs) are a symbiosis of a dynamical system that is implemented on and thus interacts with a digital platform. The textbook example for this is the inverted pendulum experiment where a rod of a certain length has to be kept upright by moving its base in the plane. The strategy for these movements is programmed into a computer or a small microcontroller, depending on the setup, and together, they form a larger system that is referred to as CPS.

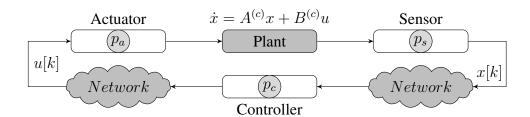

Depending on the focus of the analysis, such systems are also referred to as digital control systems or networked control systems. The former are the earliest variant and deal with the issues of periodic sampling as well as fixed delay; the latter add a fixed network into the analysis which is typically considered random in nature. The CPS paradigm expands on this, ultimately aiming for a co-design of network, or platform, and control system.

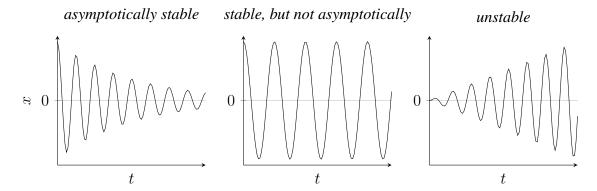

Although they have an individual focus, the underlying theory of the aforementioned approaches overlaps significantly. This chapter introduces the major results from literature that the later parts of the thesis rely on. It first presents general forms of dynamical systems (Section 2.1) and the communication hardware (Section 2.2) that is commonly used to implement them in a distributed fashion. As soon as the digital impact becomes significant for its evolution, a system must be considered as sampled-data system (Section 2.3), typically in discrete time. Next, the chapter goes over the most relevant properties of a control system (Section 2.4). In order to account for message losses, in addition to delay, we then explore switched systems (Section 2.5). These systems evolve differently depending on discrete events like a successful message arrival. Unlike for switching actuation as discussed in Chapter 5, switching is considered adversarial here and assumed to arrive in the worst pattern. Finally, we explore which of the desirable control system properties can be applied to switched systems and expressed in a form that is compatible with model checking (Section 2.6). In this way, control system analysis can be combined with the model checking-based timing analysis from Chapter 3; this combination is the topic of Chapter 4.

## 2.1 Continuous dynamical systems

A system is first of all an entity formed by interacting components that are in some way separated from the rest of the world. Across its boundaries, the system interacts with its surroundings via established input and output signals. For dynamical systems described in mathematical terms, one very general formulation is

$$\dot{x} = f(x, u). \tag{2.1}$$

Here, x is the state vector that a control engineer attempts to influence via input vector u. If f is not benign in some sense, very few statements can be made about such systems in general (see textbook [93] for reference). Nevertheless, this form already makes an assumption of causality. The system is only affected by its input. The input device, on the other hand, is not affected by the system unless explicitly modeled.

Since the most general form is hard to reason about, researchers have mostly dealt with less general versions. The most popular paradigm is that of Linear Time-invariant (LTI) systems. While LTI systems cannot describe all applications, they do cover the basic properties for virtually all systems. When evaluating a control system, the first property that comes to mind is usually *stability* (see Section 2.4). Informally speaking, one wonders whether the system can possibly drive itself and accelerate out of control. This question is directly linked to an equilibrium or working point  $x_e, u_e$  with  $f(x_e, u_e) = 0$  that can be used for linearization. By defining new coordinates around this point  $\Delta x = x - x_e$ , the system can be described linearly and becomes much easier to analyze. With continuous system matrices

$$A^{(c)} = \left[\frac{\partial f}{\partial x}\right]_{x_e, u_e} \qquad B^{(c)} = \left[\frac{\partial f}{\partial u}\right]_{x_e, u_e}$$

and re-setting  $x = \Delta x$ , i.e., considering only the new coordinate system, one arrives at a general form for LTI systems.

$$\dot{x}(t) = A^{(c)}x(t) + B^{(c)}u(t)$$

$$y(t) = C^{(c)}x(t)$$

(2.2)

Besides linearization, this so-called *state space representation* expands upon (2.1) by introducing output vector y. y can model that, in general, not all states, i.e., not all elements of x are measurable from the outside.  $A^{(c)}$ ,  $B^{(c)}$ ,  $C^{(c)}$  are called continuous system, input, and output matrix, respectively. They fully characterize the system behavior. The superscript  $^{(c)}$  distinguishes the continuous from the discrete version of the system, as examined in Section 2.3. It is often clear from the context which system description is meant and we can then simply refer to the matrices as A, B, C.

Converting to an LTI system is highly desirable since they come with a large number of formal results. For the context of this work, the most relevant properties that become verifiable and even designable are stability as well as quadratic costs for penalizing tracking error and input energy. Please refer to Section 2.4 for an overview.

The accuracy of a linear model rapidly decreases outside the working point, however. Caution is thus required when evaluating properties without taking the distance from the working point into account.

In addition, the form in Eq. (2.2) is only adequate to describe systems with negligible delay and continuous actuation. Contemporary systems are mostly implemented on distributed digital platforms, however (Section 2.2). This rules out continuous actuation because it would require continuously recomputing the input signal and hence needs infinite computing resources. In addition, contention on both computing and communication resources leads to waiting times. Whereas (2.2) assumes that a new input u(t) can be applied the moment x(t) occurs in the system, there is always a delay in reality. Consequently, we discuss in Section 2.3 the sampled-data system modeling which includes sampling periods and possibly non-negligible delay.

In certain cases, an additive disturbance term w(t) is included in the LTI state space representation from Eq. (2.2). This term is supposed to take both random noise inside the system as well as modeling errors into account. Many design approaches ignore these disturbance terms and rely on the inherent robustness of the control loop.

$$\dot{x}(t) = A^{(c)}x(t) + B^{(c)}u(t) + w(t)$$

$$y(t) = C^{(c)}x(t)$$

(2.3)

Typically, disturbance w(t) is assumed to be normally distributed, written  $w(t) \sim \mathcal{N}(0, \Sigma_c)$ . This choice is mostly driven by the desire to make algebraic techniques manageable. Questions about average performance in particular benefit from the normal distribution. When considering the worst case, the normal distribution is rarely chosen because its infinite support leads to infinitely bad performance bounds.

#### 2.2 Communication hardware

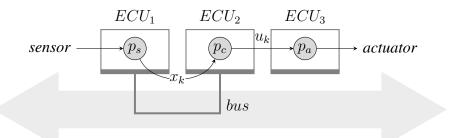

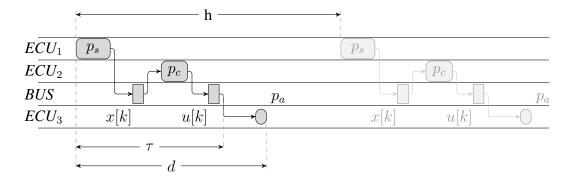

Distributed implementations of feedback control applications are common in many safety-critical domains like automotive and avionics. In this work, we consider setups where a feedback control application is implemented on multiple ECUs that communicate over a shared bus. As shown in Fig. 2.1, the sensing devices and the actuators are connected to different ECUs and the control algorithm uses feedback signals that are transferred via the shared bus system. While being transmitted over such a bus, feedback signals often get delayed due to contention by other messages, thereby resulting in a *sensor-to-actuator* delay.

Delay in a feedback control system has tremendous influence on its performance. It would thus be desirable to route all communication between the various ECUs directly. Such a fully connected mesh requires many wires, however, that are then under-utilized on average. The implied cost and extra weight almost always rule out this approach. Currently, the automotive industry and many others hence favor bus topologies. These require the least amount of cabling but also lead to more contention.

To keep a shared bus usable, access must be arbitrated in some way. The major paradigms are currently time-triggered and event-triggered arbitration.

**Time-triggered arbitration** The highest amount of predictability and reliability can be achieved by granting each application access to the bus in periodic fashion. To make this work, a fixed period of time is divided into slots. This period, referred to as *superframe* in many architectures, is typically in the low millisecond range. Each slot is then assigned to an application or

**Figure 2.1:** In distributed control applications, sensor task  $p_s$ , controller task  $p_c$ , and actuator task  $p_a$  are implemented on separate ECUs and communicate over a shared bus. While this allows for execution on specialized processors and often reduces the number of ECUs required overall, it also introduces delays.

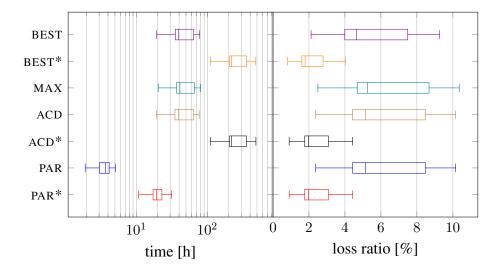

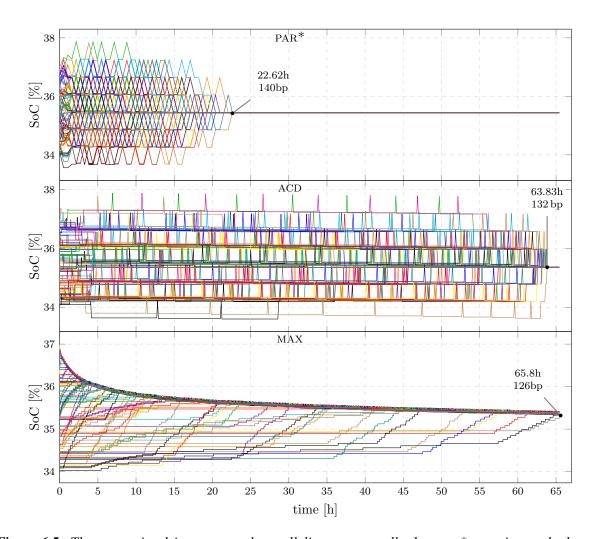

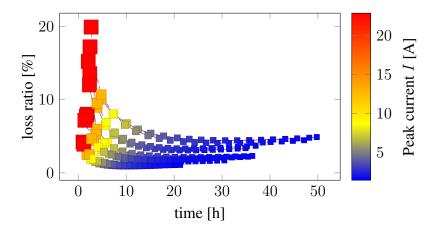

ECU. As time evolves, the participants access the bus one after another during their designated time slots. Once an entire cycle is completed, the procedure immediately starts again. Consider textbook [97] for reference.