# Software Deployment Analysis for Mixed Reliability Automotive Systems

KLAUS BECKER

# Institut für Informatik der Technischen Universität München

# Software Deployment Analysis for Mixed Reliability Automotive Systems

## **Klaus Becker**

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Prof. Dr.-Ing. Georg Carle

Prüfer der Dissertation:

1. Prof. Dr. Dr. h.c. Manfred Broy

2. Prof. Dr.-Ing. Jürgen Teich,

Universität Erlangen-Nürnberg

Die Dissertation wurde am 16.02.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 02.06.2017 angenommen.

# **Abstract**

Safety critical fault-tolerant embedded systems have to react properly on failures of internal system elements to avoid failure propagation and finally an external failure at the entire system boundary, being harmful to other systems, material or human beings in the environment. To inhibit failure propagation and ensure harm avoidance, failing system elements have to be isolated from the remaining system. As isolated elements become unavailable, the amount of available resources, like execution units or input data, decreases. This may cause that the system resources become insufficient to provide the entire initial set of functional features. However, it is often not allowed that the system stops its operation completely in such situations. Instead, the set of provided functional features of the system should be degraded gracefully to keep available at least a subset of the intended features. In this context, a system shall keep available those features as long as possible, that have the highest requirements according to safety, reliability and availability. For instance, features having a fail-operational requirement must be kept available, while other features may be allowed to get deactivated, resulting in a degradation of the available set of features.

In this thesis, we introduce an approach to formally analyze whether the design of a system adheres to all fail-operational requirements of functional features. We consider this in different scenarios of failing system elements, like failing execution units and failing software components. We address mixed criticality and mixed reliability automotive systems, comprising functional features having varying requirements to be fail-operational. Beside pure fail-operational features, we also consider degradable functional features, called fail-degraded features. As prerequisite for the analysis, we set up a formal model of the system, containing the functional features, possible feature degradations, the relationship of functional features to the software components that realize the features, the communication dependencies between software components, the hardware execution units, as well as the deployment of software components to execution units. For assumed failure scenarios, we provide a structural analysis of the necessary level of degradation in these scenarios by analyzing which subset of functional features can be kept available. As part of our analysis, we automatically synthesize valid deployments of software components to execution units, fulfilling the fail-operational requirements of all functional features in all failure scenarios, and minimizing the required level of degradation. We incorporate an adequate level of redundancy into the deployment, to enable failover mechanisms from an isolated software component to a redundant backup of that component, if this is necessary due to a fail-operational requirement. We set up formal constraints which describe valid redundant deployments of software components to execution units, as well as valid degradation scenarios and valid failover scenarios by describing valid reconfigurations of deployments. This means, we determine an initial deployment and analyze the changes of this deployment that may become required in different failure scenarios. The formal model, constraints and optimization objectives are described by linear arithmetic and logical operators. We use an SMT solver to get solutions for this model, serving as basis for our analysis. We show the applicability of our approach based on three examples from the automotive domain.

# Acknowledgements

First of all, I want to express my deep gratitude for Prof. Manfred Broy for his outstanding supervision of this thesis, supporting me with so many discussions and constructive review comments. It was always a pleasure to experience his style of open-minded research and guidance. I also thank Prof. Jürgen Teich for co-supervising my thesis.

I express a particular thank you to Michael Armbruster of Siemens AG, for inspiring many of the requirements that are analyzed in this thesis, for raising my interest in redundancy and fault-tolerance concepts, and responding fruitful feedback to the very early ideas about this work. Great thanks also goes to Bernhard Schätz and Sebastian Voss of fortiss Institute, supporting me in a lot of discussions and providing feedback to contents of this thesis.

I also would like to thank all the colleagues who worked together with me in the RACE project, for the very intensively cooperative work during the project and also discussing early ideas about this work, particularly again Michael Armbruster, Christian Buckl, Jelena Frtunikj, Cornel Klein, Ludger Fiege and Meik Felser, who were with Siemens AG or fortiss Institute during that time.

I also would like to thank my other colleagues of TU Munich and fortiss Institute, in particular Andreas Vogelsang, Maximilian Junker, Mario Gleirscher, Stefan Kugele, Denis Bytschkow and Vincent Aravantinos, for their interest, discussions and feedback around the work in this thesis.

A thank you also goes to Nikolaj Bjørner of Microsoft Research for his support by quickly fixing some issues in the Z3 SMT solver, revealed during the implementation of the introduced model and analysis approach.

The time as PhD candidate is not only about writing the thesis, but furthermore obtaining experiences in several other research topics and projects, which turn the time into a very enjoyable and beneficial time! I would like to thank Ernst Denert, Gero Scholz, Alois Zoitl and all the other people with which I worked together during my time as researcher at fortiss Institute, for sharing a lot of experiences and knowledge in many different areas.

Last but not least, the most important people who supported me so much during this time and missed me so often or tried to do not disturb me while writing, my wife Sandra and - at the end - our little cheerful son Jonas, I love you two.

# **Contents**

| 1 | Intr | duction                                                       | 1      |

|---|------|---------------------------------------------------------------|--------|

|   | 1.1  | Context                                                       | 1      |

|   | 1.2  | Problem Statement and Motivation                              | 1      |

|   | 1.3  | Research Questions and Contribution                           | 3      |

|   | 1.4  | Outline                                                       | 5      |

| 2 | Fun  | lamentals                                                     | 7      |

| _ | 2.1  |                                                               | ,<br>7 |

|   | 2.1  | 2.1.1 Dependability                                           | •      |

|   |      | 2.1.2 Dependability Threats                                   |        |

|   |      | 2.1.3 Dependability Attributes                                |        |

|   |      | 2.1.4 Dependability Means                                     |        |

|   |      | 2.1.5 Other Definitions related to Dependability              |        |

|   |      | 2.1.6 Redundancy and Replication Mechanisms                   |        |

|   | 2.2  | Foundations in Safety Engineering                             |        |

|   | 2.2  | Foundations in Software and System Quality Assurance          |        |

|   | 2.3  | Automotive Architectures and Standards                        |        |

|   | 2.4  | 2.4.1 Classical Automotive E/E Architectures                  |        |

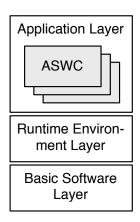

|   |      | 2.4.2 AUTOSAR                                                 |        |

|   |      |                                                               |        |

|   | 2.5  |                                                               |        |

|   | 2.5  | 11                                                            |        |

|   |      | 2.5.1 Software and System Architecture                        |        |

|   |      | 2.5.2 Safety and Fault-Tolerance Concept                      |        |

|   |      | 2.5.3 Application Development and RTE Configuration           |        |

|   | 2.6  | 2.5.4 Demonstrator Vehicles                                   |        |

|   | 2.6  | Avionic Architectures and Standards                           |        |

|   | 2.7  | Foundations in Satisfiability Solving and Optimization        | 3      |

| 3 | Rela | ted Work 4                                                    | 1      |

|   | 3.1  | Approaches to Design and Analyze Fault-Tolerant Systems       | _      |

|   |      | 3.1.1 Design and Analysis of Graceful Degradation             |        |

|   |      | 3.1.2 Design and Analysis of Reliability and Robustness       | 3      |

|   |      | 3.1.3 Design and Analysis of Availability                     | 1      |

|   |      | 3.1.4 Fault-Tolerant Scheduling for Mixed Criticality Systems | 1      |

|   |      | 3.1.5 Design of Structural and Behavioral Reconfiguration     | 2      |

|   |      | 3.1.6 Self-x Approaches                                       | 3      |

|   | 3.2  | Constraint Based Synthesis of Design Decisions                | 3      |

| 4 | Ana  | yzing Fail-Operational and Fail-Degrading Systems 65          | 5      |

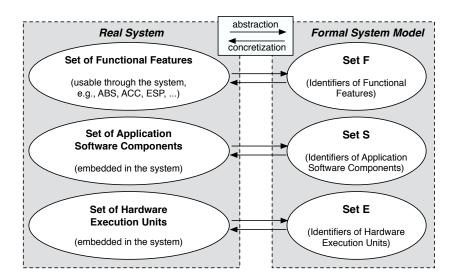

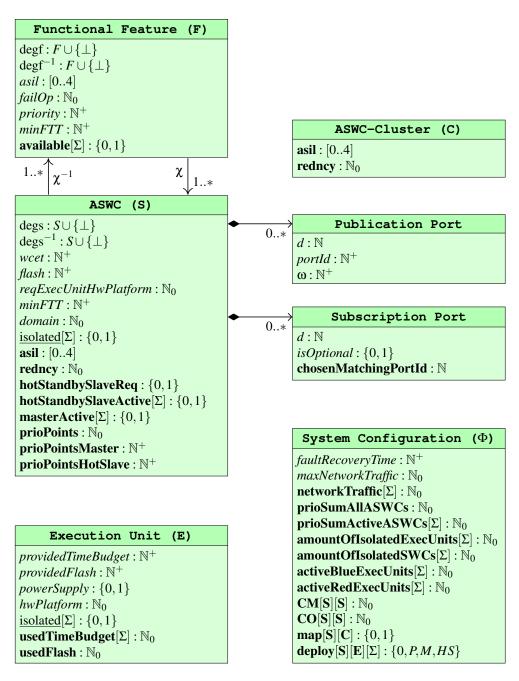

| - | 4.1  | Introduction to the Formal System Model                       |        |

|   |      | 4.1.1 Viewpoints                                              |        |

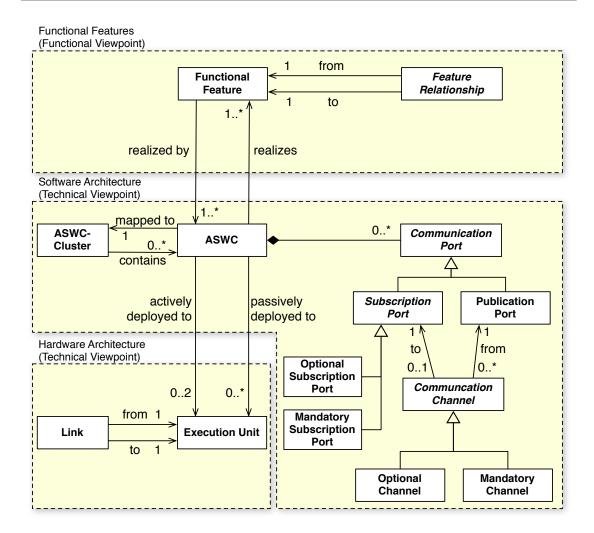

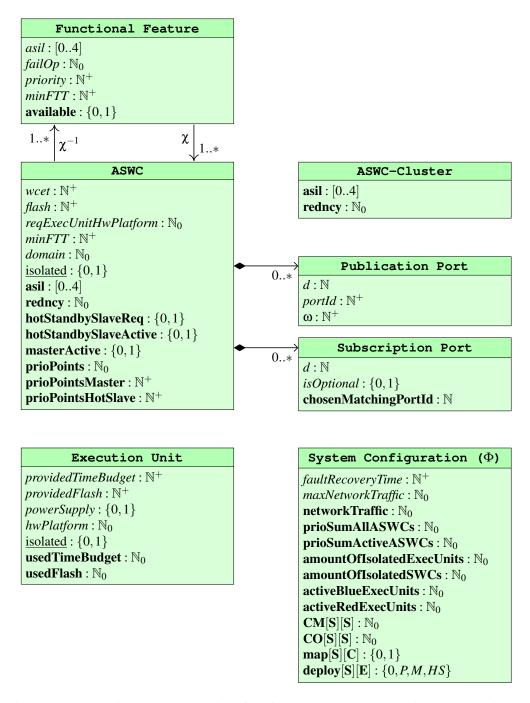

|   |      | 4.1.2 Meta-Model of Considered System Structure               |        |

|   |      | 4.1.2 Motivation and Ranafite of the Formal System Model      |        |

## CONTENTS

| 4.2  | Formal | System Model                                            |

|------|--------|---------------------------------------------------------|

|      | 4.2.1  | Functional Features                                     |

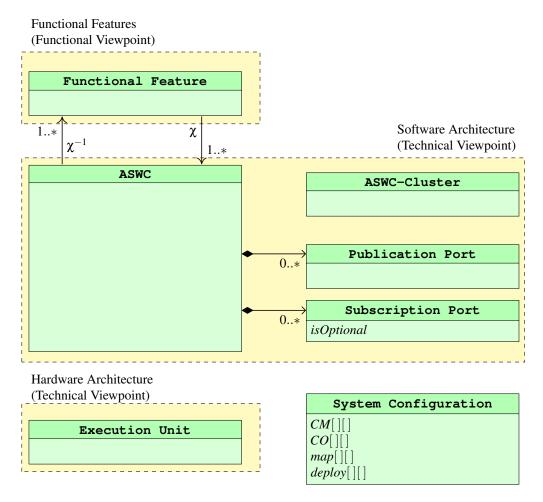

|      | 4.2.2  | Software Architecture                                   |

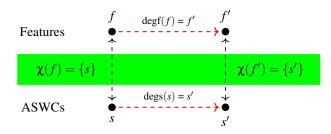

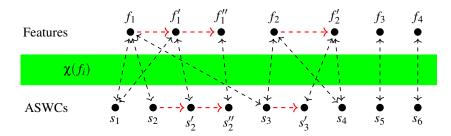

|      | 4.2.3  | Feature Realization                                     |

|      | 4.2.4  | Hardware Architecture                                   |

|      | 4.2.5  | System Configuration                                    |

|      | 4.2.6  | System Model                                            |

|      | 4.2.7  | Example for the Formal Definitions                      |

|      | 4.2.8  | Summary Overview of Formal Model Symbols                |

| 4.3  | Concer | ot Overview                                             |

| 4.4  | -      | ties of System Model Elements                           |

|      | 4.4.1  | Overview of Properties of Formal System Model           |

|      | 4.4.2  | Input Model Properties                                  |

|      | 4.4.3  | Solution Model Properties for Initial Deployment        |

|      | 4.4.4  | Solution Model Properties for Failure Scenarios         |

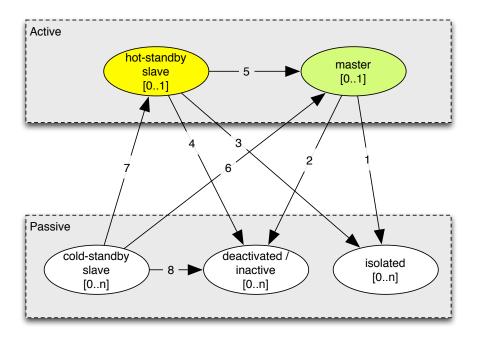

|      | 4.4.5  | States of ASWC Instances                                |

| 4.5  | Synthe | sis of Valid Redundant Deployments                      |

|      | 4.5.1  | Formal Constraints for Valid Redundant Deployments      |

|      | 4.5.2  | Examples                                                |

| 4.6  |        | is of Failure Effects                                   |

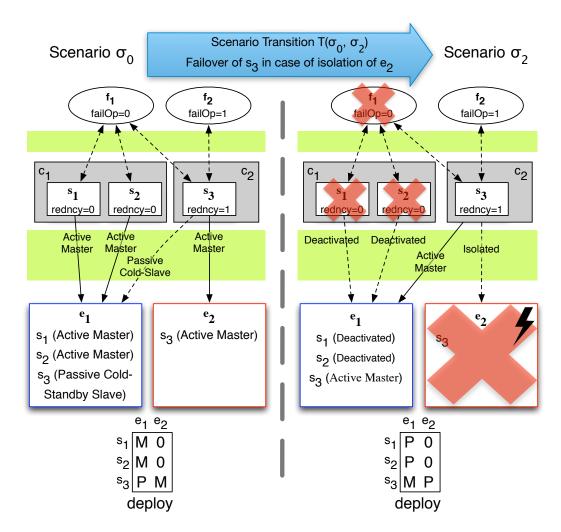

|      | 4.6.1  | Scenarios                                               |

|      | 4.6.2  | The Scenario Graph                                      |

|      | 4.6.3  | Extensions of Model Properties to Cover the Scenarios   |

|      | 4.6.4  | Procedure to Analyze the Scenario Graph                 |

|      | 4.6.5  | Formal Constraints for Valid Failovers and Degradations |

|      | 4.6.6  | Formal Constraints to Analyze Feature Availability      |

|      | 4.6.7  | Relaxation of Constraints to Localize Problems          |

|      | 4.6.8  | Example A – Basic Example                               |

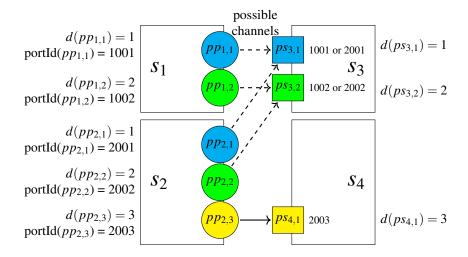

|      | 4.6.9  | Example B – Communication Channels                      |

|      | 4.6.10 | Size of the Scenario Graph                              |

| 4.7  |        | ting Degradations of Single Functional Features         |

| •••  | 4.7.1  | Assumed Design Principles for Feature Degradations      |

|      | 4.7.2  | Extension of the Formal System Model                    |

|      | 4.7.3  | Extended Overview of Properties                         |

|      | 4.7.4  | Formal Constraints for Feature Degradations             |

|      | 4.7.5  | Example C – Feature Degradation                         |

| 4.8  |        | ization of Optimization Objectives                      |

| 4.9  |        | ptions and Aspects that are out of Scope                |

| 1.,  | 4.9.1  | Out of scope                                            |

|      | 4.9.2  | Assumed properties of the system under analysis         |

| 4 10 |        | ations and Discussions about the Formal System Model    |

| 7.10 | -      | Functional Features                                     |

|      |        | Software Architecture                                   |

|      |        | Feature Realization                                     |

|      |        | Hardware Architecture                                   |

|      |        | System Configuration                                    |

|      | +.1U.J | 5y5tchi Conngulation                                    |

| 5  | Eval    | luation                                                             | 153 |

|----|---------|---------------------------------------------------------------------|-----|

|    | 5.1     | Discussion of Research Questions                                    | 153 |

|    | 5.2     | Limitations of the presented approach                               |     |

|    | 5.3     | Threats to Validity                                                 |     |

| 6  | Con     | clusions and Future Work                                            | 159 |

|    | 6.1     | Summary and Conclusions                                             | 159 |

|    | 6.2     | Out of Scope                                                        | 161 |

|    | 6.3     | Future Work                                                         |     |

|    |         | 6.3.1 Expand the set of considered design aspects                   | 162 |

|    |         | 6.3.2 Possible Future Work Extensions of our Approach               | 162 |

|    |         | 6.3.3 Evaluation of alternative solving and optimization strategies | 163 |

| A  | App     | pendix                                                              | 165 |

|    |         | Input Files of Examples                                             | 165 |

| Li | st of I | Figures                                                             | 175 |

| Li | st of T | Tables                                                              | 177 |

| Bi | bliogr  | raphy                                                               | 178 |

# CHAPTER 1

# Introduction

#### **Contents**

| 1.1 | Context                             | 1 |

|-----|-------------------------------------|---|

| 1.2 | Problem Statement and Motivation    | 1 |

| 1.3 | Research Questions and Contribution | 3 |

| 1.4 | Outline                             | 5 |

## 1.1 Context

Complex systems, like automobiles, airplanes or industrial automation systems, are nowadays realized by a huge amount of software, rather than using purely mechanical, electrical or hydraulical components like half a century ago. We call such systems to be software-intensive embedded systems, in which software based subsystems interact with the physical world using sensors and actuators to fulfill their intended service. An example is an anti-lock braking system (ABS) of a vehicle, which senses the wheel rotations and software decides about how to act on the brakes to keep wheels rotating and avoid slipping wheels. More and more of such software-based functional features become integrated into vehicles, like advanced driver assistance systems (ADAS) and automated/autonomous driving capabilities [115]. This means that the amount of software in such systems is growing and increasingly interconnected, leading to increasing complexity [216].

Many embedded systems operate in safety-critical environments, like in the automotive domain, avionics domain or industrial automation domain. Those systems have critical properties in a sense that unhandled malfunctions of system parts may lead to unacceptable harms to the system itself, to the physical system environment and even to the safety of human beings. Hence, it is very important that those malfunctions are detected and handled in a safe manner to avoid any form of harm. This thesis provides an approach to analyze such safety critical systems with respect to the set of functional features, that a system can still provide when it becomes affected by malfunctions.

### 1.2 Problem Statement and Motivation

Safety critical systems need to contain mechanisms to detect malfunctions of system parts and to react on these malfunctions properly such that no harm can occur with impact to material or life. In case software or hardware elements of a system fail, these elements have to be isolated from the residual system in order to avoid a failure propagation through the residual system, which potentially leads to a total system loss and harm.

In order to develop vehicles with automated or fully autonomous driving capabilities, such systems are becoming highly integrated and interconnected. The functionalities get more and more based on X-by-Wire control using electronics and software, rather than mechanical or hydraulic control components [47]. Examples are Fly-by-Wire in aircraft (e. g., in [360]) or Drive-by-Wire in vehicles (e. g., in [46]). As a disappearance of active assistance or autonomous driving features during their operation would be very dangerous causing harm, these features must be kept alive even in the presence of a malfunction of some system element [56] [331] [143]. Due to these safety reasons, fully autonomous X-by-Wire systems

must behave fail-operational, as fail-safe behavior would cause the loss of autonomy features, which may be harmful if the driver is not able to take over the control fast enough. Hence, X-by-Wire systems require a fail-operational implementation, fail-safe is not sufficient [203]. To ensure fail-operationality, such systems have to be established with redundant backup elements that can take over functionality, if another element fails [189]. Redundancy helps to establish error avoidance [276] and by this, to provide fail-operational systems. If a X-by-Wire system is desired to have no mechanical fallback backups of software enabled features, software based backups by redundancy mechanisms are important to ensure fail-operationality of that features. Beside software redundancy, also redundancy of execution hardware as well as sensors and actuators is required to handle electronic hardware failures [322]. But any form of redundancy is limited and costly. Hence, graceful degradation and fail-safe mechanisms have also to be taken into account simultaneously.

Furthermore, a trend is towards mixed-criticality systems [73], meaning that components with different levels of criticality are executed by the same hardware device in modern systems. It has to be guaranteed that errors of low critical components can never have negative impact on highly critical components.

But what should happen after a failure of a system element has been detected? Invalidating faulty data and going into a fail-safe state may cause the loss of functional features. This is not acceptable for critical features that require fail-operational behavior, meaning that those features must be kept alive even in the presence of failures of system elements, like hardware or software components. If a fail-operational feature gets affected by such a failure, the systems must be able to resume the feature without any service interruption. For instance, if a hardware failure of an execution unit has been detected, followed by an isolation of this execution unit from the remaining system, another execution unit. However, if system resources get lost due to isolations, the remaining system resources may become insufficient to provide the full set of functional features. Hence, the remaining resources should be used efficiently to keep available the most important features. The importance often corresponds to requirements about safety, reliability and availability. In these scenarios, keeping available some features requires to explicitly deactivate some other features, resulting in a *degradation* of the system.

The motivation of this thesis is to provide an approach to formally analyze a system with respect to needed degradations in failure scenarios, while ensuring the fulfillment of fail-operational requirements. In order to perform such an analysis, an initial deployment of software components to hardware execution units has to be determined, which fulfills a set of redundancy constraints. We aim in supporting the designer by automatically synthesizing such a valid initial deployment, as well as valid reconfigurations of the deployment for all failure scenarios. We want to analyze if deployments can be synthesized that enable the fulfillment of all fail-operational requirements of features by the current system design. We also want to analyze which subset of functional features has to be deactivated in certain failure scenarios, and which subset of features can be kept available, even if these features do not have fail-operational requirements. As the failure combinations and the reactions to failures can become quite complex, a manual analysis without technical support would be very time intensive, error-prone and inappropriate. An automated analysis during design time would give the system designer an early feedback about problems, helping to reduce costs by early design corrections, and providing evidence towards the fulfillment of different fail-operational requirements of the functional features of the mixed-reliability system.

We assume a given system safety concept that specifies redundancy mechanisms to be applied in the deployment, and specifies isolation and *failover* mechanisms to be used as reaction to detected failures. We aim at providing an automated analysis of the degradation scenarios, resulting from synthesizing a deployment with a minimal level of redundancy needed to ensure all fail-operational requirements.

Apart from analyzing the reaction to failing hardware or software components, another use-case of our approach is to analyze intended degradation scenarios, which are applied in order to save energy in a vehicular network. Such a planned deactivation of resources due to energy saving reasons leads as well to decreasing amount of available resources. Hence, degradations of system functionality should be taken into

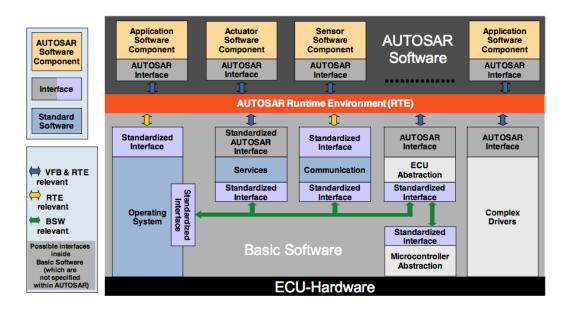

account. For instance, AUTOSAR [21] mentions the requirement that AUTOSAR shall support different standardized methods to degrade the functionality of an AUTOSAR system.<sup>1</sup> This is mainly motivated to save energy as energy efficiency is a major concern in vehicles [250]. Two main degradation strategies are specified in AUTOSAR: 1) Partial Networking and 2) ECU degradation in conjunction with Pretended Networking [225].

Although fault-detection, fault-handling, and energy-saving degradation have to be done at runtime of the system, it is desireable to be able to statically analyze at design time the current system design according to degradation scenarios that may happen at runtime. Particularly the mixed criticality and mixed reliability of the system requires to ensure runtime robustness and to provide static verification at design time for certification [29]. Providing such a static analysis approach to support the verification with focus on degradation and failover scenarios is the major motivation of this thesis.

# 1.3 Research Questions and Contribution

In this thesis, we tackle the following research questions and present respective contributions to address the questions.

**RQ1:** How to automatically calculate valid deployments of software to hardware, supporting the fulfillment of fail-operational requirements? The first research question of this thesis is how valid deployments of mixed critical software components onto hardware execution units can be automatically calculated, incorporating a given redundancy concept and applying an adequate level of redundancy. The redundancy is required to fulfill fail-operational requirements of functional features. Different levels of fail-operationality may be required. Hence, different levels of redundancy of software components are adequate. This results in a fault-tolerant system, whose functional features have *mixed reliability*. The question is how this can be modeled adequately and how appropriate deployments can be synthesized automatically?

Our approach and focus: We do not estimate predefined deployments, but instead we synthesize valid redundant deployments. In order to calculate a valid deployment, we setup a formal system model with formal deployment constraints, expressed with linear arithmetic and logical formulas, enabling an automated calculation of valid deployments that fulfill the constraints. Beside calculating deployments, we also calculate communication channels between the software components, based on component port specifications, opening a set of possible channels from which only a subset of channels is necessary to satisfy the specified subscription ports. This enlarges and influences the design space for the deployments.

Novelty of contribution: Calculating deployments by setting up a Constraint Satisfaction Problem (CSP) is itself nothing new, but so far not addressed in other work for the introduced kind of systems with mixed critical and mixed reliable functional features, having different required levels of fail-operationality, allowing to efficiently apply different levels of redundancy of software components, considering constraints for valid types of redundancy. In addition, we use the open design space of deployment and channel selection to optimize the synthesized architecture, for instance by preferring local communication channels during the deployment synthesis, reducing the network traffic between the execution units.

RQ2: How to formally analyze the ability to keep functional features available in scenarios of failing system elements, and decide about necessary degradations of the available feature set, incorporating necessary failovers to ensure fail-operational requirements? Our major research question is how a given system design, including its feature set and software architecture, can be formally analyzed with respect to the degradation of the set of functional features that can be kept available in scenarios of failing

system elements, and how functional features with fail-operational requirements can be kept available by applying *failover* mechanisms in such failure scenarios, using redundant backups of software components? This analysis shall be done in combination with the first research question, such that an initial deployment is synthesized that leads to applicable failover scenarios and a minimum level of *degradation* of available features. One sub research question is how to decide which software components are allowed to be explicitly deactivated, in case the available system resources become insufficient to execute all software components?

Our approach and focus: We consider failures of hardware execution units and failures of software components. To be able to analyze the effect of failing hardware or software to the set of available functional features, we formally describe the relationship between functional features and the software components, which realize these features. To decide about explicit deactivations, we establish a *quantitative metric* to estimate the intrinsic value of software components in order to decide about the sequence in which components (and thereby features) should be disabled when the system is not able to provide the full set of functional features anymore. We focus on an analysis on structural architecture level, without doing a behavior analysis.

Novelty of contribution: No existing approach considered a similar form of mixed criticality and mixed reliability fault-tolerant systems. There are existing approaches, providing quantitative metrics about the degree of *graceful degradation* of fault-tolerant systems (e. g., [314]), but the approach shown in this thesis has a novel combination of mixed criticality and mixed reliability (by different fail-operational requirements of functional features) and a system concept using global redundancy and failover mechanisms.

**RQ3:** How to formalize a given system design concept and the requirements related to the safety and fault-tolerance concept of that system to be able to apply the formal analysis to this type of system? In order to tackle the first two research questions, one prerequisite is the design of a formal system model that represents the hardware and software architecture of the system, as well as the relevant properties of the system elements. Applying a given safety and fault-tolerance concept with informal natural language descriptions of valid types of redundancy, valid failover mechanisms and valid degradation scenarios, the question is how to formally express these descriptions in form of formal constraints over the formal system model? The aim is to synthesize valid respectively optimal solutions in a mathematical fashion. This means, informal requirements have to be transformed into formal constraints over the elaborated formal model, expressing valid types of architectures and reconfigurations of it, to be applied in scenarios of failing system elements. To formally synthesize valid deployments and analyze failure scenarios for a system under analysis, this requires to formalize parts of the applied safety and fault-tolerance concept. The research question is how this can be done.

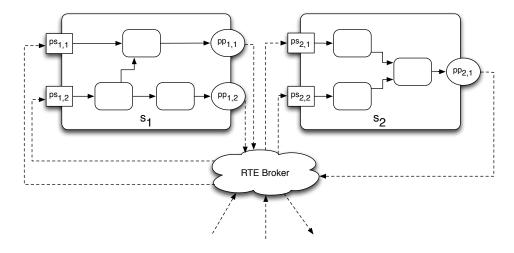

Our approach and focus: As example safety and fault-tolerance concept for embedded systems, specifying informal requirements for redundancy and failover mechanisms, we use the concept that was developed in the research project RACE. <sup>2</sup> For an introduction into the RACE platform concepts, see section 2.5.1. We formalize relevant aspects of the safety and fault-tolerance concept by formal constraints over the introduced system model. The constraints ensure that the solutions, calculated by an employed solver, represent failover and degradation scenarios that are valid according to the given informal requirements.

Novelty of contribution: No existing work has been found that provides a combined formalization of architecture concepts and requirements for valid redundancy, failover and degradation mechanisms to enable fault-tolerance in the above described manner.

<sup>&</sup>lt;sup>2</sup>The Project RACE (Robust and Reliant Automotive Computing Environment for Future eCars) was funded by the German Federal Ministry for Economic Affairs and Energy (BMWi) under grant no. 01ME12009 from 2012 to 2015, http://www.projektrace.de/en

**Further motivation for the presented approach:** Beside the three major research questions, motivating the approach introduced in this thesis, there are some sub-motivations that influence the introduced approach:

- Static analysis at design time: We tackle how dynamic failover scenarios that may happen at runtime

can be encoded into a formal model to be able to analyze these scenarios statically at design time.

Our work contributes to provide such an analysis, applicable during design time of a system. It is

not in focus to apply our approach during runtime of the system executed by the system itself, as this

changes the requirements with respect to the performance of calculating solutions and the workflow.

- Optimization objectives: Another question is how optimization objectives can be expressed based on

the formal system model, and be solved reusing existing technologies like for instance Satisfiability

Modulo Theories (SMT) or Mixed Integer Linear Programming (MILP) solvers? If necessary, also

partially contradicting optimization objectives should be expressible and solvable.

In this thesis, we express the tackled problem as a formal system model, using arithmetic and logical formulas, and use the model as input for an SMT solver, which calculates valid values of solution variables satisfying formalized constraints, serving as basis for our analysis, while optimizing some considered design objectives. We use an SMT solver with optimization facilities to do this.

## 1.4 Outline

The residual part of this thesis is structured as follows. Chapter 2 introduces the fundamental terminology which is present in the context of this thesis, as well as an overview over foundations in safety engineering and related architectures and standards of the automotive domain. Chapter 3 discusses the related work of this thesis. Chapter 4 contains the presentation of the contribution of this thesis, including our formal system model and the analysis approach for failure scenarios, which is evaluated in chapter 5. The conclusion and future work is shown in chapter 6. Additional material is contained in appendix chapter A.

# **Previously Published Material**

Parts of the contributions presented in this thesis have been published in the following papers directly related to this thesis: [39], [35], [38], [37], [40], [41].

- [39] Klaus Becker and Sebastian Voss. Towards Dynamic Deployment Calculation for Extensible Systems using SMT-Solvers. In First Open EIT ICT Labs Workshop on Cyber-Physical Systems Engineering (EIT CPSE), Trento, Italy, May 2013.

- [35] Klaus Becker, Michael Armbruster, Bernhard Schätz, and Christian Buckl. Deployment calculation and analysis for a fail-operational automotive platform. In 1st Workshop on Engineering Dependable Systems of Systems (EDSoS). arXiv:1404.7763, 2014.

- [38] Klaus Becker, Bernhard Schätz, Michael Armbruster, and Christian Buckl. A formal model for constraint-based deployment calculation and analysis for fault-tolerant systems. In 12th Int. Conference on Software Engineering and Formal Methods (SEFM), volume 8702, pages 205–219. Springer Lecture Notes in Computer Science (LNCS), 2014.

- [37] Klaus Becker and Bernhard Schätz. Deployment calculation and analysis for a fault-tolerant system platform. In 11th Dagstuhl-Workshop on Model-Based Development of Embedded Systems (MBEES), 2015.

- [40] Klaus Becker and Sebastian Voss. Analyzing graceful degradation for mixed critical fault-tolerant real-time systems. In 18th International Symposium on Real-Time Distributed Computing (ISORC), pages 110–118. IEEE, 2015.

- [41] Klaus Becker and Sebastian Voss. A formal model and analysis of feature degradation in fault-tolerant systems. In 4th Int. Workshop on Formal Techniques for Safety-Critical Systems (FTSCS), volume 596, pages 139–154. Springer Communications in Computer and Information Science (CCIS), 2015.

In addition, the author of this thesis authored or co-authored the following publications, which are indirectly related to this thesis in the form of project papers about the RACE project: [36], [318], [72].

# CHAPTER 2 Fundamentals

The following section 2.1 introduces definitions of the terminology that we use in this thesis. Section 2.2 shows a basic overview of safety engineering principles and how our approach is resided within these principles. Section 2.3 shows how the approach introduced in this thesis is placed in the field of software and system quality assurance techniques. Section 2.4 provides an overview over architectures and standards in the automotive domain, containing electrical/electronic bordnet architectures and software architectures, like AUTOSAR. Afterwards, section 2.5 gives an introduction about a novel fault-tolerant hardware and software architecture for vehicles, developed in the RACE project. Some properties of the RACE architecture are assumed in this thesis as basic properties of a system, which is aimed to be analyzable with the approach introduced in this thesis. Section 2.6 shows a very brief introduction to architectures and standards in the Avionic domain, like Aircrafts, and briefly discusses degradation concepts in this domain. Finally, section 2.7 gives a brief introduction into different problem solving technologies, like SMT solvers or linear programming (LP) algorithms.

### **Contents**

| 2.1 | Terms and Definitions                                  | 7  |

|-----|--------------------------------------------------------|----|

| 2.2 | Foundations in Safety Engineering                      | 23 |

| 2.3 | Foundations in Software and System Quality Assurance   | 24 |

| 2.4 | Automotive Architectures and Standards                 | 25 |

| 2.5 | The RACE Approach                                      | 30 |

| 2.6 | Avionic Architectures and Standards                    | 37 |

| 2.7 | Foundations in Satisfiability Solving and Optimization | 38 |

### 2.1 Terms and Definitions

In this section, we introduce the main terms and definitions which are related to the topic of this thesis as prerequisite to grasp the domain of this thesis. We focus on an overview over the definitions in the area of dependable embedded systems.

**System:** A system is a technical product, which is in most cases composed of various parts. Often the parts a grouped to subsystems, which can be designed, constructed and tested standalone. Subsystems can be hierarchically composed of further (sub-)subsystems of various types, such as mechanical, hydraulic, electric (analog) or electronic (digital). An example of a subsystem is a combustion engine block of a vehicle, composed of mechanical parts like piston, crankshaft, camshaft, valves, but also electrical and electronic parts like power lines and electronic control units (ECUs), containing software for fuel injection control, ignition control, and so on. The composition is done by interactions between the subsystems. The interactions are performed through *interfaces*. Each system or subsystem has a *boundary*, at which interfaces exist to interact with other systems or subsystems, or with human users. The electronic subsystems which are not directly recognized by human users are called *embedded systems*. In this thesis, we focus on systems which are composed in a large part of electric and electronic subsystems, like vehicles.

**Interface:** At the boundary of a system or a subsystem, there exist interfaces, over which nowadays mostly digital data is exchanged. We call the interfaces at the entire system boundary *external interfaces* of the system. We call the interfaces between the subsystems *internal interfaces*. In many embedded systems, physical sensors and actuators establish interfaces to interact with the physical environment of the system. Physical sensors are input interfaces, such as steering wheels or brake pedals, which transform physical information (movements, pressure, temperature, etc.) into digital data. Physical actuators do it vice versa, transforming digital data into physical actions at the output interfaces, such as force feedback at the steering wheel, servo of the steering rack, or hydraulic pump forcing brake piston movements. Also graphical user interfaces (GUIs) exist to interact with human users over displays. In this thesis, we define the system boundary (external interface) to be the sensors and actuators of the system, as well as the digital communication interfaces of the system, allowing to exchange data with other systems (e. g., car-to-x), or also with infrastructure in the Internet (cloud services). All interfaces, regardless of whether mechanical, hydraulic or digital (software), have to be well defined and matching to the interfaces of other systems or subsystems to which interactions are performed.

**Behavior:** The behavior of a system or subsystem is the transformation of inputs at its input interfaces to outputs at its output interfaces. When the internal transformation procedure is not considered, this is called the black-box behavior or I/O behavior [69]. For the user, the behavior of a system is recognized at the system boundary (external interface). If the system behavior is incorrect (deviation from the specified behavior) at the external interface, then bad things could occur like accidents, or at least not-amused users. If subsystem behavior becomes incorrect at internal interfaces, the question is if and how the entire system behavior is influenced by this at the external interfaces. A system should be able to detect incorrect behavior at internal interfaces and react in such a way that the behavior at the external interface remains correct, even if only in a reduced amount or reduced quality of service (see later introduced terms of *fault-tolerance* and *graceful degradation* in section 2.1.4, as well as *fail-x* in section 2.1.5).

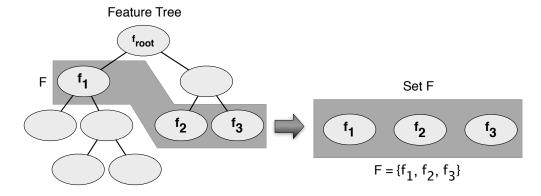

**Functional Feature:** The behavior at the external interface of a system is grouped to *functional features*. A functional feature is a behavior of a system, which can be used by a human being or another system. Each functional feature realizes at least one of the functional requirements, for which the system is designed for. A functional feature is realized by components of the system, either hardware components like hydraulic, mechanical or electrical elements, or software components that interact with the system environment by sensor/actuator interfaces. In this thesis, we focus on functional features that are realized by software components. Closely related terms to *functional feature* are the terms of *application*, *service* or just *function*, which could be also seen as synonyms somehow. For instance, [23] defines that a *service* delivered by a system is its behavior perceived by users at the system boundary (external interface).

Another kind of features are *non-functional features*, which are features that realize non-functional requirements of the system. Non-functional features ensure so called *non-functional properties*, which do not directly address things that users explicitly expect from the system, but however increase the quality of the system. Some of them are implicitly anticipated by users, like fault-tolerance, others are mostly not perceived by users, like maintainability [178].

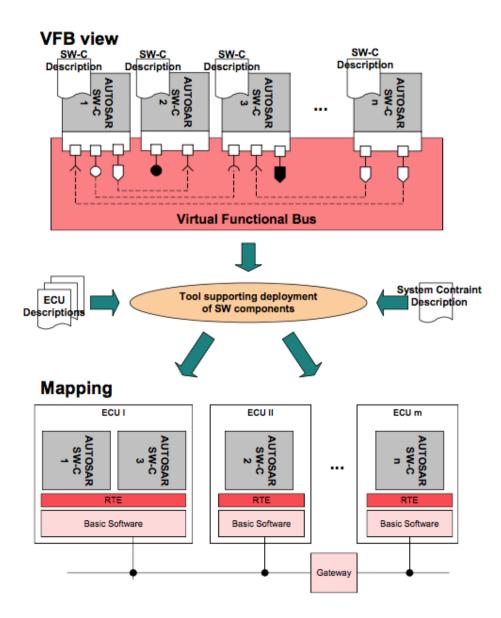

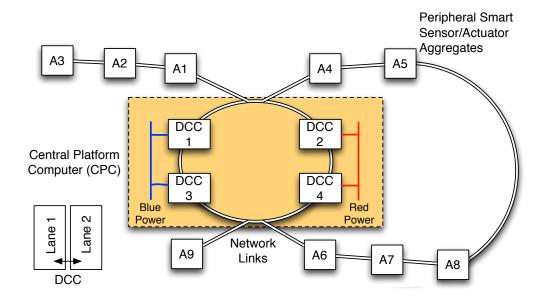

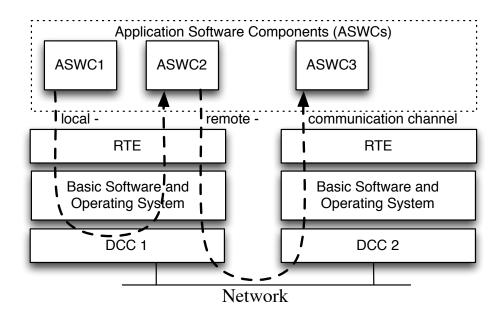

**Deployment:** In this thesis, we use the term *deployment* as the decision about which software components become executed on which hardware execution units (such as micro-controllers, electronic control units (ECUs), etc.). Hence, this decision defines which hardware unit will execute which software components later when the system is put into operation. Beside this software to hardware deployment, there exist also hardware to hardware deployment, like the decision about which sensors or actuators have to be attached to which distributed input/output units in a production plant [211]. A further kind of deployment is the physical deployment of hardware units to a physical location within the system, where the hardware

units have to be placed. Synonyms of the term *deployment* are the terms *allocation* (e. g., used in [156]), *assignment* (e. g., used in [187]), *mapping* (e. g., used in [302]), *binding* (e. g., used in [228]), *distribution* (e. g., used in [155]) and *placement* (e. g., sometimes used in [246]).

However, sometimes the term *deployment* is not understood as introduced above, but instead as the post-production activity [95] of installing software binaries into a system to make them available for use, like continuous redeployment techniques [16] to deploy software updates into a system. Automatic *deployment* plans as sequence of actions to create/delete components and channels in a system are researched in [219]. We do not use the term *deployment* in this manner in this thesis.

#### 2.1.1 Dependability

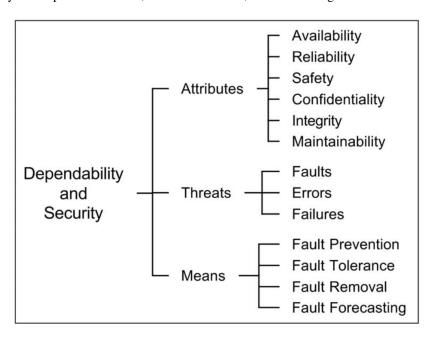

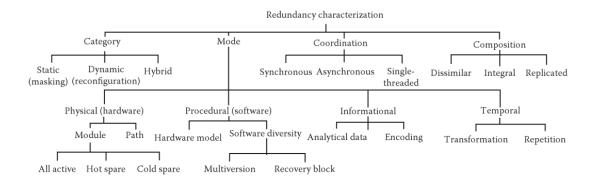

**Dependability:** In [217], *dependability* is defined as that property of a computer system such that reliance can justifiably be placed on the service it delivers. In this context, the service that a system delivers is its behavior as it is perceptible by its human or physical users. In [23], the *dependability* of a system is defined as the ability to avoid service failures that are more frequent and more severe than acceptable. Dependability encompasses *attributes*, *threats* and *means*, as shown in Fig. 2.1.

Figure 2.1: Dependability and its tree of attributes, threats and means [23]

The topic of this thesis is related to the mentioned threats; the attributes of availability, reliability and safety; as well as the means of fault tolerance.

Beside the shown dependability tree, other dependability trees are introduced, like the one in [108]. However, we apply the taxonomy of [23] in this thesis.

**Security:** Dependability and Security are strongly related, as weak security offers possibilities to attack the system and badly influence the dependability. Hence, some of the attributes are also related to security. Security will become more and more important, when vehicles become more and more interconnected [230]. However, we do not further consider security issues in this thesis.

# 2.1.2 Dependability Threats

Certain threats exist to any system, which may lead to unintended malfunctions and harm. The threats are:

**Failure:** In [175], failures are defined as termination of the ability of a system element to perform a function as required. Hence, a failure is a transition from correct to incorrect service of a system element or the entire system. Failures are classified in [175] into *common cause failures*, *cascading failures*, *dependent failures*, *independent failures* or *single/dual/multiple-point failures*. Furthermore, *systematic failures* and *random hardware failures* are distinguished in [175]. *Systematic failures* are related in a deterministic way to a certain cause, that can only be eliminated by a change of the design, manufacturing process, or other relevant factors. *Random hardware failures* are defined as failures that can occur unpredictably during the lifetime of a hardware element and that follow a probability distribution. In [23], service failures and dependability failures are distinguished. A *service failure* is an event that occurs when the delivered service deviates from correct service. A *dependability failure* occurs when the given system suffers service failures more frequently or more severely than acceptable.

Beside the above classification, in this thesis we distinguish the following kinds of failures:

- 1. *External Failure*: a failure of the entire system, recognizable at the systems external interface in form of a behavior that violates the specification.

- 2. *Internal Failure*: a failure of an element (subsystem) of a system, which does not affect the systems external interface directly. An internal subsystem failure must be handled, such that it does not propagate to the systems external interface and by this becomes an external failure. Hence, we treat an internal subsystem failure as an *error* (defined below) from the perspective of the whole system, which may lead to a failure of the whole system, if not handled appropriately.

**Error:** An *error* is a discrepancy between a computed, observed or measured value or condition, and the true, specified or theoretically correct value or condition [175]. An error is the part of the total state of the system that may lead to its subsequent service *failure* [23]. In [245], it is defined that an error remains an error as long as it is tolerable and until it becomes intolerable (a *failure*) or it vanishes.

**Fault:** A *fault* is the cause of an *error* and finally potentially of a *failure*. In [175], faults are defined as abnormal conditions that can cause an element or an item to fail. A fault cannot be directly detected at runtime by a system, only after the fault caused an error, which can be detected. Hence, a faulty state does not yet violate safety [245] and can be seen as tolerable, unless it causes an error. Different types of faults are defined in [23], which can be grouped to be *development faults*, *physical faults* or *interaction faults*. Moreover, there is a distinction between transient faults (appearing once for a short period of time), intermittent faults (aperiodically reappearing for short times) and permanent faults [321].

In this thesis, we focus not directly on faults, but on errors and failures that may either be caused by physical faults, which include all fault classes that affect hardware, or caused by systematic development faults of software components. We consider errors caused by intermittent or permanent faults being permanently handled by applying an isolation of the faulty system element from the residual system. The system may handle transient faults either also permanently by isolation, or by masking the once appearing erroneous value for instance by using a valid *last good known* value for a short period of time. We focus on the cases in which system elements become isolated permanently.

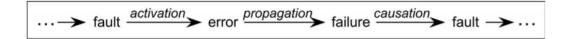

Figure 2.2: Chains of threats, from Fig. 11 in [23]

Fig. 2.2 shows how the introduced terms of faults, errors and failures are related to each other [23]. A fault is the cause of an error and an error may lead to a subsequent failure. However, the perspective onto the considered system element is important. As described above, an internal failure of a sub-element of a system is not equal to an external failure of the entire system. But a sub-element failure can be seen as entire system fault leading to an entire system error, which shall be detected and handled therewith the local sub-element failure does not propagate through other parts of the system, leading to an entire system failure.

In this thesis, we consider situations in which execution units of a system have random hardware failures, which got detected by an appropriate mechanism, followed by an isolation of the failed execution unit. Hence, an execution unit failure is an internal failure. It shall not lead to an external failure, but may lead to a reduction of the functionality recognizable at the external interface. This reduction of functionality is called degradation, respectively graceful degradation, introduced below in section 2.1.4.

With more focus on purely software based products, the above terminology is extended in [351] and [350] with the terms of

- Mistake: A mistake is a human action that produces a fault.

- Defect: Defects are the superset of faults and failures.

Related to the above terms are the following terms, all introduced in [175].

- Harm: Physical injury or damage to the health of persons.

- Hazard: Potential source of harm caused by malfunctioning behavior of an item. An item is a (sub-)system or array of (sub-)systems to implement a function at the entire vehicle level.

- Severity: Estimate of the extent of harm to one or more individuals that can occur in a potentially hazardous situation.

- Risk: Combination of the probability of occurrence of harm and the severity of that harm. In other

words, risk is characterized by the two properties of frequency of hazardous events and the severity

of hazardous events.

- Malfunctioning behavior: Failure or unintended behavior of a system or subsystem with respect

to its design intent. This means, a functional feature of the system deviates from its specification.

Hence, the behavior is wrong at the external system boundary.

- Failure Mode: Manner in which the hardware or software of a system or subsystem fails. In [264] defined as the manner by which a failure is observed, generally describing the way the failure occurs and its impact on equipment operation.

- Failure Effect: consequence(s) that a *failure mode* has on the operation, function, or status of a system or subsystem [264].

#### 2.1.3 Dependability Attributes

We focus on the attributes, which are related to the topic of this thesis.

**Safety:** *Safety* denotes the ability of a software system to avoid failures that will result in loss of life, injury, significant damage of property, or destruction of property [330]. In [23], safety is defined similarly as absence of catastrophic consequences on the users and the environment. The ISO 26262 defines **functional safety** as the absence of unreasonable risk due to hazards caused by malfunctioning behavior of electric/electronic systems [175]. In context of autonomous driving, [54] introduces **operational safety** as property or ability of a vehicle to be in a suitable operating condition or meeting acceptable standards for safe driving and transport. They define *operational safety* (also called *roadworthiness*) as a composition of the dependability attributes of safety, availability, reliability and maintainability.

**Reliability:** The *reliability* of a system or subsystem is defined as its continuity of correct service [23], or as measure of the ability to work completely failure-free for a certain length of time, or mission [207]. In [88], reliability is defined as the ability of a system to operate correctly according to its specification for a given time interval. [330] defines a software systems *reliability* as the probability that the system will perform its intended functionality under specific design limits, without failure, over a given time period.

In this thesis, we associate *reliability* to the required level of fail-operationality of functional features (see also definition of fail-operational in section 2.1.5). The higher the required fail-operational level is, the higher is the required reliability of a feature. As different features might have different fail-operational levels, we obtain a *mixed reliability* system.

**Availability:** A software systems *availability* is the probability that the system is operational at a particular time [330]. It is also defined as *readiness for correct service* [23]. An overview over more definitions of *availability*, as well as an approach to specify and analyze the *availability* of software intensive systems, is given in [186], mentioning that *availability* is defined as the ability of a system to operate without failure most of the time.

To obtain a quantitative metric for the availability, often the following definitions are used

- Mean time to failure (MTTF): average time from startup to a failure of a system. Typically used for systems, which cannot be repaired.

- Mean time between failures (MTBF): average time between two consecutive failures of a system. Typically used for systems, which can be repaired.

- Mean time to repair (MTTR): average time required to repair a failed system.

The availability A is defined as

$$A = \frac{MTTF}{(MTTF + MTTR)} \quad [145]$$

or

$$A = \frac{MTBF}{(MTBF + MTTR)} \quad [212][144]$$

In the latter definition of [212] [144], it is assumed that MTBF contains only the time in which a system is available (average uptime), but does not contain the repair time MTTR. Other approaches consider MTBF = MTTF + MTTR [117], what leads availability to become

$$A = \frac{(MTBF - MTTR)}{MTBF} \quad [117]$$

To handle this clash between two different definitions of MTBF, a mean time between down event (MTBDE) has been introduced for repairable systems as sum of the average uptime (MTBF) and the average downtime (MTTR), MTBDE = MTBF + MTTR.<sup>1</sup>

However, in this thesis we only consider a boolean  $\{0,1\}$  availability metric of functional features for certain points in time. As the formal model that we are going to introduce has no notion of time intervals, we do not consider the availability over a time interval, like the above mentioned availability metrics do it. Instead we allow to analyze a given situation like a degradation scenario, with respect to if a specific functional feature of a system can be kept available or if it has to be deactivated.

# 2.1.4 Dependability Means

**Fault-tolerance:** Fault-tolerance is the ability of a controlled system to maintain control objectives, despite the occurrence of a fault [53]. According to [330], a software system is fault-tolerant, if it is able to respond gracefully to failures.

In [245], *masking* and *non-masking* fault-tolerance are distinguished. While masking fault-tolerant systems mask the effects of faults (namely errors and failures) such that the effects are hidden from users, non-masking fault-tolerant systems do not hide the effects of faults from users and for instance reduced availability may be recognized. This is also related to static and dynamic redundancy, what we introduce later in section 2.1.6.

In [285], fault-tolerant systems are defined to be able to keep the system running at 100% of its designed functionality even in case of failures, while *self-healing* systems (cf. section 3.1.6) may operate with less than 100% functionality after a healing procedure. However, contradicting to this definition of [285], in [53] it is defined that degradation of control performance may be accepted for fault-tolerant systems. In this thesis, we define fault-tolerant systems to be able to apply graceful degradation, meaning that a reduced level of provided functional features can be acceptable in failure scenarios, but this has to follow certain constraints that we discuss later in chapter 4.

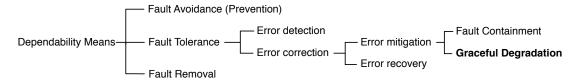

**Graceful Degradation:** In [300], graceful degradation is defined as a smooth change of some distinct system feature to a lower state as a response to an event that prevents the system from exhibiting that feature in its full state, often used to allow systems to survive errors or internal failures by removing their damaged parts. Graceful degradation is classified in the dependability means (cf. Fig. 2.1) as an error mitigation mechanism for error correction to establish fault tolerance [300], see Fig. 2.3.

Figure 2.3: Graceful Degradation classification into dependability means [300]

The degradation can be applied for instance in case of an internal failure of a system element. This means, graceful degradation is a concept to tolerate failures by reducing the functionality or the performance, rather than shutting down the system completely [313]. *Performance degradation* means to keep

<sup>&</sup>lt;sup>1</sup>http://www.weibull.com/hotwire/issue94/relbasics94.htm, last access April 5th, 2016

alive the same functionality, but with reduced performance. *Functional degradation* denotes a degradation of a system in such a manner that it continues to operate, but provides a reduced level of functionality rather than failing completely [280] [287]. In this thesis, we focus on functional degradation on a structural level.

Furthermore, beside the preferred initial behavior, gracefully degrading systems permit additional weakly consistent behaviors which are undesired, but tolerated and sufficiently close to the preferred behavior [163]. However, in this thesis we do not consider such behavior degradation, as the formal model that we are going to introduce has no notion of behavior of functional features or software components.

In [287], graceful degradation in *timeliness* and graceful degradation in *quality* is distinguished. Timeliness is the ability of a service to perform its required functions and provide its required responses within specified time limits. A degradation of timeliness is similar to performance degradation. Quality degradation is a degradation of a services correctness and/or how usable a service is [287], what is similar to functional degradation, to which we focus on.

Another definition is that graceful degradation is a resilient system's ability to survive disruptions originating from within or without while still carrying out its missions [91]. The ISO 26262 defines degradation as strategy for providing safety by design after the occurrence of failures [175] and that graceful degradation at the software level refers to prioritizing functions to minimize the adverse effects of potential failures on functional safety [176].

In [300], three patterns are introduced about how to smootly reach a lower system state. They distinguish an 1) *optimistic*, 2) a *pessimistic* and 3) a *causal* degradation pattern.

- 1) optimistic degradation pattern: remove only the failed system element

- 2) pessimistic degradation pattern: remove all system elements that are anyhow related to the failed element

- 3) causal degradation pattern: remove all system elements that strongly depend on the failed element

With respect to the patterns introduced in [300], in this thesis we consider degradations in form of a mixture of pessimistic and causal degradations, as we distinguish optional and mandatory communication channels between software components. If optional input data becomes unavailable, the receiving component can continue to operate. If mandatory input data becomes unavailable, the receiving component becomes deactivated (causal). However, we have no internal whitebox data-flow consideration of components, leading to the deactivation of the whole component if one single mandatory input data item is missing, although the residual input data might be sufficient to fulfill a subset of the specification (pessimistic).

#### In this thesis, we define graceful degradation as follows:

A degradation is graceful, if no fail-operational requirements are violated by a degradation, and if mixed-criticality functional features become deactivated sequentially by starting with the deactivation of the feature with the lowest criticality.

We focus on degradations that become necessary due to assumed failures of execution units or software components, forcing loss of non redundant components, or requiring deactivations of components due to insufficiency of input data or insufficiency of execution resources.

However, because we do not model the functional behavior of components by means of Input/Output data stream relations at component interfaces, as introduced for instance in [69], our approach does not include a notion of a *Quality of Service* (QoS) of functional behavior. This means, we do not analyze to which sense users do experience how the system behavior is influenced by degradations, and to which sense this is accepted by users as graceful or not.

#### 2.1.5 Other Definitions related to Dependability

Beside the above three dependability attributes, which are listed in [23], there exist certain more terms in the field of dependable systems, listed below.

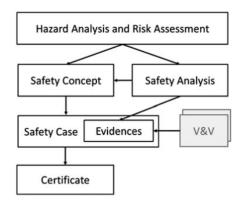

**Safety Case:** Argument that the safety requirements for an item are complete and satisfied by evidence compiled from work products of the safety activities during development [175].

**Resilience:** Resilience is the ability of a system to provide and maintain an acceptable level of service in the face of various faults and challenges to normal operation. Resilience can be considered as the flip side of vulnerability [86]. In [98], *dynamic resilience* is introduced as a system's capacity to respond dynamically by adaptation in order to maintain an acceptable level of service in the presence of impairments. They introduce *predictable dynamic resilience* as the capacity of a system to deliver dynamic resilience within bounds that can be predicted at design time. In this thesis, we contribute to analyze the predictable dynamic resilience of the system under analysis at design time.

**Survivability:** Survivability is a software systems ability to resist, recognize, recover from, and adapt to mission-compromising threats [330]. In other words, it is the capability of a system to fulfill its mission, in a timely manner, in the presence of attacks, failures, or accidents [112]. Survivability is very often seen in connection to graceful degradation. In [202], survivability is defined as how systems will degrade functionality in the presence of failures, as it is the degree to which essential functions are still available even though some part of the system is down [96].

Fault tolerance is often seen as a subset of survivability<sup>3</sup>, and survivability is often seen as a subset of resilience.<sup>4</sup>

**Robustness:** A software system is robust, if it is able to respond adequately to unanticipated run time conditions [330]. Robustness is usually associated with reliability and resilience [153].

**Fail-x:** There exist several ways on how to react to a failure at runtime. Below follows an introduction to the main concepts and terms, related to this thesis.

• Fail-Silent: A *fail-silent* node is a self-checking node that either functions correctly or stops functioning after an *internal* failure is detected [64]. Important here is the *internal* failure, which means that the node itself has not yet fail behavior at the external node interface, but a failure of an internal sub-element of the node is detected. An example is a micro-controller node that detects a data distortion failure of its internal random-access memory. A fail-silent node avoids that the internal failure becomes an external failure of that node, propagating to other nodes of the system. Instead, a fail-silent node stops sending actual data to other nodes or actuators in the occurrence of an internal failure. This avoids propagation of faulty data to the rest of the system. Also in [182], it is defined that after one (or several) failure(s), a fail-silent component exhibits quiet behavior externally (i.e., stays passive by switching off) and therefore does not wrongly influence other components. However, the state of the system at that moment in which it goes into fail-silent mode may be not safe. For instance, if the last outgoing data was forcing an actuator to accelerate, the actuator receives no data telling him that it shall stop to accelerate.

<sup>2</sup>https://wiki.ittc.ku.edu/resilinets/Definitions#Resilience

<sup>3</sup>https://wiki.ittc.ku.edu/resilinets/Definitions#Fault\_Tolerance

<sup>&</sup>lt;sup>4</sup>https://wiki.ittc.ku.edu/resilinets/Definitions#Survivability

- Fail-Safe: In case of an internal failure, a *fail-safe* system switches to a state that is considered safe in the particular context. No harm is caused in case of a failure. In [182], it is defined that after one (or several) failure(s), a fail-safe component directly reaches a safe state (passive fail-safe, without external power) or is brought to a safe state by a special action (active fail-safe, with external power). In the example of the acceleration actuator, this means that a fail-safe system ensures that a safe state is entered, meaning the actuator to stop the acceleration and most probably to stop the movement completely (but this depends on the system properties).

- Fail-Operational: In [53], a system is defined to be *fail-operational*, if it is able to operate with no change in objectives or performance despite of any single failure. This means, the system has to be able to tolerate at least one failure of a sub-component (internal failure) and stay operational without going into a fail-safe state and without suffer an external failure. For instance, fail-operational is required if no safe state exists immediately after a system component fails [182].

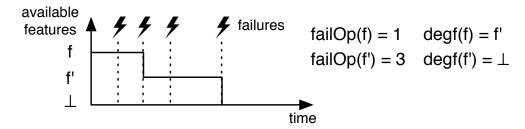

- In this thesis, we consider fail-operationality not dedicated to an entire system, but to the single functional features of the system. Hence, some functional features may be fail-operational, others not. Furthermore, we distinguish different levels of fail-operationality. A functional feature with a fail-operational level of x is required to continue operation after the first x failures of hardware or software components in the system. Afterwards, the feature is allowed to become disabled. In this thesis, we consider random hardware failures of execution units and systematic failures of software components as occurring failure types that have to be handled by the system to enable fail-operational features.

- Fail-Degraded: In this thesis, we consider systems in which only a subset of the functional features is required to behave fail-operational. However, the other features are allowed to be deactivated in case of failures of subsystems. This means that not the entire system is fail-operational, as some features might become deactivated, resulting in a degradation of the system. Such systems are called *fail-degraded* systems, like in [34].

Certain more terms exist in context to the above terms, like fail-passive, fail-secure, fail-fast, fail-halt, fail-stop, which we do not further introduce here.

In the context of Steer-by-Wire systems, a study of the Daimler AG [122] has shown that by fail-silent designed Steer-by-Wire systems, no functionalities with customer benefit can be realized, as already small changes in the steering ratio respectively small steering angle faults cannot be handled by the drivers and result in problems. A mechanical backup guarantees in that context no transition to the safe state. The conclusion of Daimler investigations is that an appropriate Steer-by-Wire system has to be designed *fail-tolerant* to make sure that the steering system will change directly to the safe state when failures occur (fail-safe). Thus Steer-by-Wire makes noticeable higher demands to the system concept as known driving dynamic systems (like anti-lock braking system (ABS) or electronic stability program (ESP)) and even Brake-by-Wire.

**Real-Time Scheduling:** A real-time computer system is a computer system, in which the correctness of the system behavior depends not only on the logical results of the computation, but also on the physical time when these results are produced [209]. This means, the timing has a huge impact on the dependability of a system. Real-time systems are categorized to be hard or soft, static or dynamic, preemptive or non-preemptive [209]. The latest time at which a task has to be finished is called the *deadline*. In hard real-time systems, a task which misses its deadline may cause a catastrophic failure. Think about an airbag which opens too late. However, hard real-time systems are not defined to be *fast* or *performant*, but instead they are defined to be *predictable* [74].

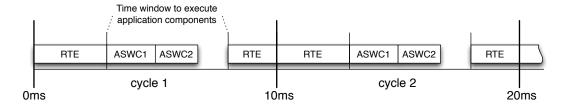

In this thesis, we assume a real-time system to use *logical execution times* (LETs), which abstracts from the actual execution time of a program on a physical implementation platform [200]. We assume a LET based model of computation, in which software components are scheduled in execution cycles of fixed cycle length. Input data for all components is captured at the beginning of the execution cycle and not modified anymore during the cycle, output data of all components is collected at the end of each cycle, not before. See section 2.5.1 for more details about this.

**Criticality Levels:** For the automotive domain, the ISO 26262 [174] defines different *Automotive Safety Integrity Levels* (ASIL) from QM (Quality Management) over ASIL A, ASIL B, ASIL C to ASIL D, where ASIL D denotes the highest criticality (see also section 2.4.3). In the Avionic domain, the DO-178B/DO-178C [288] defines *Design Assurance Levels* (DAL) from DAL E (no safety effect) over DAL D (minor), DAL C (major), DAL B (hazardous) to DAL A (catastrophic). Hence, without looking into details, the ISO 26262 level QM is comparable with DO-178C *DAL E*, and *ASIL D* is comparable with *DAL A*.

A system or subsystem is called to be *mission critical*, if a failure might prevent an operation or task from being performed, possibly preventing successful completion of the operation as a whole [284]. Mission criticality corresponds typically to the lower levels of the standards, like DAL D or DAL C (minor or major) for the avionic domain [284]. Typical examples of mission critical features are navigation/display or mission command and control subsystems.

A system or subsystem is called to be *safety critical*, if a failure could result in danger, injury or loss of human life [284]. Safety criticality corresponds typically to the higher levels of the standards, like DAL B or DAL A (hazardous or catastrophic) for the avionic domain [284], like flight and engine controls.

**Mixed Criticality:** A *mixed criticality* system has multiple distinct criticality levels [73], like the levels introduced above. This means, such a system provides functional features – and contains associated subsystems – that have different criticality levels. Those subsystems that have different criticality levels have to be separated from each other to avoid negative influence from less critical subsystems to high critical subsystems. One approach to handle different criticalities is to avoid interference by physical separation into multiple physical devices with clearly separated network connections.

However, if mixed criticality software components are executed by a single control unit, we talk about mixed criticality controllers. Mixed-criticality embedded controllers are gaining attention for instance in the automotive and avionics domain due to savings in cost, space, weight, heat and power [73] [261]. Also in [131] it is stated that future automotive E/E-architectures will consist of highly integrated domain-controllers, providing very high functional integration. This requires the support of the execution of application components with mixed criticality levels on the same controller [70]. Separation of the mixed criticality software on mixed criticality controllers is required, as introduced below.

**Separation by Partitioning on Mixed Criticality Controllers:** Having mixed criticality controllers, the mixed critical software components have to be separated from each other to avoid undesired influences between the different components. For this, mechanisms for spatial and temporal partitioning are required [292] (also called time and space-partitioning [261]), as offered by so called separation kernel operating systems [294], such as *PikeOS*<sup>5</sup> [190] or *EB tresos Safety*<sup>6</sup>. This ensures that 1) *spatial influence* by memory access to other components is avoided, as well as 2) *temporal influence* by deferring the execution of other components in the schedule is avoided.

**Fault Containment Regions and their Isolation:** Isolation is the mechanism to detach a system element that has an error or a failure from the residual system in order to avoid an entire system failure. To be

<sup>&</sup>lt;sup>5</sup>https://www.sysgo.com/products/pikeos-hypervisor

<sup>6</sup>https://www.elektrobit.com/products/ecu/eb-tresos/functional-safety

able to isolate system elements in a spatial and temporal manner, systems are often partitioned into independent so called *fault containment regions* (FCR) (e.g., [171]). Errors that appear within an FCR must be detected and isolated by error-detection mechanisms at the boundaries of the FCR such that the errors cannot damage the computational state in any other FCR. Hence, a containment region defines the border where fault propagation must stop [283]. The aim is that no single faulty FCR can knock out the whole safety-critical system [208]. Hence, isolations deal to achieve fault containment, as required for safety assurance [148].

As errors or failures have to be detected before they can be isolated, the procedure is also called *fault detection and isolation* (FDI) [168], although it should be called error- or failure-detection according to our terminology.

**Recovery:** Recovery is one form to ensure *reliability* [233]. Distinguished can be *error recovery*, enabled by recovery actions performed after an error has been detected [172], and *failure recovery* to recover from already occurred failures. A recovery action is performed to remove an error or a failure, or at least isolate the respective entity to avoid further propagation. In [102], *proactive recovery* is defined as periodically initialize replicas with a correct application state all non-faulty replicas have agreed on. This is useful to handle byzantine-faulty replicas by recovering replicas periodically independent of any failure detection mechanism [76]. We do not consider proactive recovery in this thesis. Instead, we consider *reactive recovery*, applied in fault-tolerant systems to handle detected errors. We refer to [265] for a further discussion about proactive and reactive recovery. One form of a reactive recovery action is a failover, see below.

**Failover:** A *failover* is a switch from an until now active but failed system element to a backup element that takes over the functionality. Without the failover mechanism, the functionality provided by the failed element would be either gone (if fail-safe or fail-silent), or even worse the system would run out of control. Hence, the failover mechanism is important to establish fail-operational behavior. A failover is performed automatically by the system, which is the difference to a *switchover* requiring manual user-interaction. In this thesis, we consider failovers between redundant identical or diverse software components in case of scenarios of failed hardware or software.

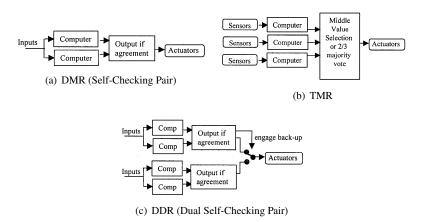

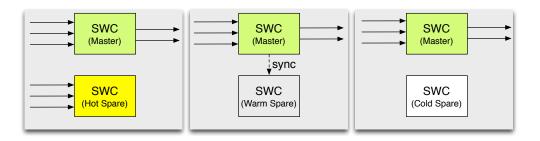

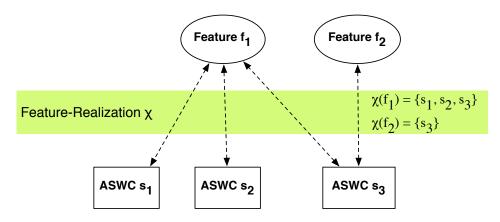

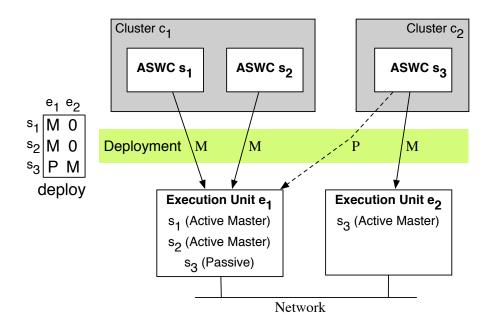

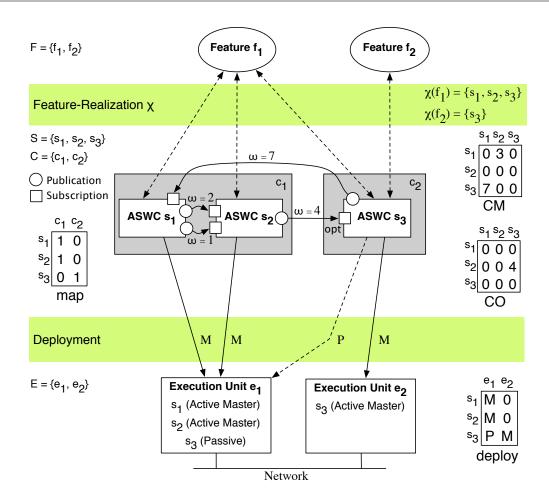

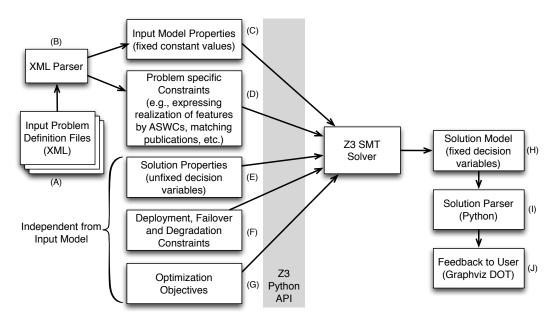

## 2.1.6 Redundancy and Replication Mechanisms