# Through Silicon Via Virtualization for Fault-Tolerant Multi-Protocol Interconnect in 3D-ICs

#### Felix Reinhard Miller

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

### **Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

#### Vorsitzender:

Prof. Dr.-Ing. Wolfgang Kellerer

#### Prüfende der Dissertation:

- 1. Prof. Dr. sc.techn. Andreas Herkersdorf

- 2. Prof. Dr.-Ing. Ulf Schlichtmann

Die Dissertation wurde am 14.09.2017 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 31.07.2018 angenommen.

### **Abstract**

Three dimensional integrated circuits (3D or stacked ICs) are manufactured by vertically stacking multiple conventional dies and subsequently creating high-performance communication links between the chip layers thus formed. Through-silicon-vias (TSVs) are the state-of-the-art method for creating such interconnects. Due to their dimensions (short length and large diameter) TSVs place only a small capacitive load on the driving circuitry and have small electrical resistance. Consequently, they can be operated at high clock frequencies. On the other hand, TSVs take up a large amount of chip area and are prone to manufacturing and run-time faults. This can lead to significant reductions in yield and reliability.

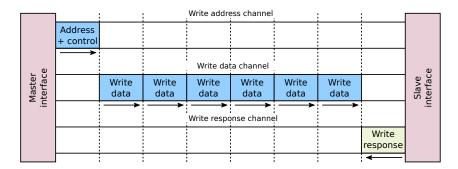

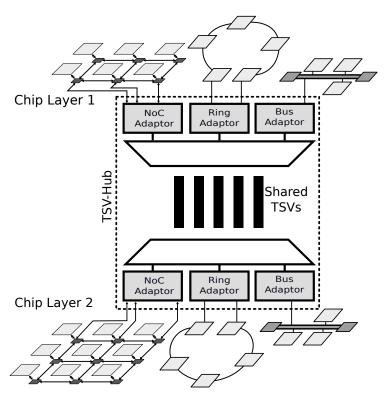

In this work, techniques are presented to reduce the number of TSVs required and to fully exploit the capacity of those deployed. To this end, the suitability of both conventional on-chip bus protocols and modern networks-on-chips (NoCs) for efficient vertical continuation is investigated. To fully exploit TSV bandwidth an approach involving multiplexing and the serialization of multiple virtual links is shown. Protocol adapters enable the transparent continuation of well-established on-chip communication standards. The TSV-Hub is presented, a configurable IP-Core with capabilities to terminate such protocols and implements the approach outlined above in order to significantly reduce TSV count. In addition, the TSV-Hub provides capabilities to improve resilience. Results are presented in form of a case study, where multiple links (based on the AXI protocol) are continued using a single TSV-Hub.

With 3D-ICs the number of functional modules in systems-on-chip (SoCs) will further increase compared to 2D chips. Already in 2D systems with high module counts, packet-switched on-chip networks are gradually replacing conventional buses as interconnect backbone since they are better scalable and more flexible. 3D-ICs additionally offer the possibility of manufacturing highly heterogeneous systems. For heterogeneous systems, it is important that the communication subsystem is specifically tailored to the requirements of the individual. IP-cores (application specific NoCs). Due to the very large design space, creating and optimizing such networks is a complex task and not feasible manually without undue effort. A synthesis algorithm is proposed which considers the physical properties of TSV-based links and bundles connections for a transparent continuation over a shared TSV array. A software tool has been implemented that, on the basis of formally

defined communication requirements, can synthesize an optimized 3D network. Such a network consists of conventional NoC components as well as TSV-Hubs for establishing vertical links. By way of example, the synthesis algorithm is outlined for a mobile communication SoC.

# Zusammenfassung

Dreidimensionale integrierte Schaltungen (3D-ICs) werden gefertigt, indem ungehäuste konventionelle integrierte Schaltungen gestapelt und durchsatzstarke Kommunikationsverbindungen zwischen den entstandenen Ebenen hergestellt werden. Bei der Herstellung dieser Verbindungen sind Siliziumdurchkontaktierungen, sog. TSVs (Through Silicon Vias), Mittel der Wahl. Aufgrund ihrer geometrischen Proportionen (geringe Länge bei relativ großem Durchmesser) erzeugen sie nur eine geringe kapazitive Last und weisen nur einen geringen elektrischen Widerstand auf. Dadurch lassen sie sich mit hohen Taktraten betreiben. Andererseits benötigen TSVs jedoch relativ viel Grundfläche und sind anfällig für Fertigungs- und Laufzeitfehler, was zu einem drastischen Abfall der Ausbeute und Zuverlässigkeit führen kann.

In der vorliegenden Arbeit werden Mechanismen vorgestellt, um die benötigte TSV-Anzahl zu reduzieren und die Performanz der vorhandenen TSVs maximal auszureizen. Dabei werden sowohl konventionelle Busprotokolle wie auch modernere paketbasierte Netzwerke (Networks-On-Chip / NoCs) hinsichtlich ihrer Fortsetzbarkeit untersucht. Um die vorhandene TSV-Bandbreite optimal auszunutzen wird ein Ansatz vorgestellt, der durch Multiplexen und Serialisieren mehrere virtuelle Verbindungen über eine gemeinsame TSV-Anordnung bereitstellen kann. Protokollumsetzer zu Standardprotokollen ermöglichen damit eine transparente Fortsetzung etablierter Protokolle. Vorgestellt wird der TSV-Hub, ein konfigurierbarer Funktionsblock (IP-Core), welcher verschiedene verbreitete Verbindungsprotokolle anbinden kann und durch o.g. Maßnahmen die benötigte TSV-Anzahl signifikant reduziert. Ferner stellt der TSV-Hub Mechanismen zur Erhöhung der Fehlertoleranz bereit. Ergebnisse werden anhand einer Fallstudie präsentiert, in welcher ein TSV-Hub zur Fortsetzung von mehreren Bus-Verbindungen, basierend auf dem Protokoll AXI eingesetzt wird.

Mit 3D-ICs wird die Anzahl funktionaler Module in Ein-Chip-Systemen (SoCs) weiter zunehmen. Bereits in 2D-Systemen mit vielen Modulen ersetzen paketbasierte Kommunikationsnetzwerke zunehmend konventionelle Bussysteme, da sie Vorteile hinsichtlich Skalierbarkeit und Flexibilität bieten. Darüber hinaus bietet die 3D-Technologie erweiterte Möglichkeiten zur Herstellung heterogener Systeme. In heterogenen Systemen ist es von Bedeutung, das Netzwerk speziell an die Kommunikationsanforderungen der einzelnen Komponenten anzupassen (applikationsspezifisches Netzwerk). Derartige Netzwerke zu erzeugen und zu optimieren ist

aufgrund des großen Suchraumes eine komplexe Aufgabe und manuell nicht mit vertretbarem Aufwand lösbar. Es wird ein automatisiertes Verfahren vorgestellt, das speziell die Eigenschaften von TSV-basierten Verbindungen berücksichtigt und Verbindungen bündelt, um diese über gemeinsame TSV-Anordnungen fortzusetzen. Mit einer im Rahmen dieser Arbeit entwickelten Software wird auf Grundlage formal definierter Kommunikationsanforderungen ein applikationsspezifisches Netzwerk synthetisiert. Ein solches Netzwerk besteht aus herkömmlichen NoC-Komponenten und aus TSV-Hubs zur Herstellung vertikaler Verbindungen. Exemplarisch wird eine Netzwerksynthese für ein SoC aus dem Bereich der mobilen Kommunikation beschrieben.

# Acknowledgements

First of all, I would like to express my sincere gratitude to my doctoral advisor and head of the Chair for Integrated Systems, Prof. Dr. Andreas Herkersdorf, for his guidance and for giving me the opportunity to work in such an interesting field. His scientific input and mentorship have been highly valued and have been essential for the successful completion of my research project and this thesis. I would also like to thank him for the great time at Nanyang Technological University, Singapore. Teaching there has been a fantastic experience for me.

I thank Prof. Dr. Ulf Schlichtmann for acting as co-examiner on the doctoral examination commission of this work.

Special thanks go to Dr. Thomas Wild for supporting me in many respects. Not only did he significantly contribute to my research project but he was also the first researcher from the institute I had the chance to work with in a student job. Back then and still today I was and still am impressed by his immense knowledge and his high-quality feedback.

Furthermore, I like to thank Dr. Daniel Llorente, my former master thesis advisor, for the great work we did together and for opening doors for me at the institute.

I would like to thank Prof. Dr. Walter Stechele for giving me the opportunity to work with him in the field of university teaching. This was a very valuable experience for me, both personally and professionally. I would also like to thank him for his scientific input and advice.

I thank Dr. Daniel Müller-Gritschneder and Dr. Vladimir Todorov from the chair of Electronic Design Automation for the great and fruitful discussions, the successful collaboration and for allowing me to built up on their work.

I am grateful to all partners of the NEEDS project for successful and productive meetings and the great work in general. I especially thank Artur Quiring from the Institute of Microelectronic Systems of the University of Hannover for the successful collaborations.

I thank all students who have contributed to the project, be it in form of bachelor and master theses, student jobs or seminar papers.

It is a pleasure for me to thank all my colleagues at the institute, especially the "Gschnack" group: David May, Gregor Walla, Michael Feilen, Michael Vonbun and Stefan Wallentowitz. Thanks for the fun and the great time we had together.

I like to thank Dr. Manuel Kuehner for his  $\slash\hspace{-0.6em}\mathbb{M}_{E}\hspace{-0.8em}X$  support and valuable input in general.

Last but not-least I would like to thank my family: My parents and my sisters for their support. I especially thank my sister Rosi for spending so many hours on proofreading the manuscript.

# Contents

| Lis | st of | Figures |                                                               | xiii |

|-----|-------|---------|---------------------------------------------------------------|------|

| Lis | st of | Tables  |                                                               | xvii |

| 1.  | Intro | ductio  | n                                                             | 1    |

|     | 1.1.  | Proble  | m Statement                                                   | 5    |

|     | 1.2.  | Thesis  | Contributions                                                 | 6    |

|     | 1.3.  | Thesis  | Structure                                                     | 8    |

| 2.  | Stat  | e of th | e Art                                                         | 9    |

|     | 2.1.  | 3D-Int  | egrated Circuits                                              | 9    |

|     |       | 2.1.1.  | Terminology                                                   | 12   |

|     |       | 2.1.2.  | Driving forces behind 3D-ICs                                  | 13   |

|     |       | 2.1.3.  | Manufacturing                                                 | 15   |

|     |       |         | 2.1.3.1. TSV Manufacturing                                    | 15   |

|     |       |         | 2.1.3.2. Wafer thinning and Chip Stacking                     | 16   |

|     |       | 2.1.4.  | Interposer based 3D-ICs (2.5D-Integration)                    | 16   |

|     |       | 2.1.5.  | Commercially available 3D-ICs                                 | 17   |

|     | 2.2.  | TSV-ba  | ased on-chip interconnect                                     | 21   |

|     |       | 2.2.1.  | TSV Delay Model                                               | 21   |

|     |       | 2.2.2.  | TSV Dependability                                             | 27   |

|     |       | 2.2.3.  | Efficient use of TSVs                                         | 31   |

|     | 2.3.  | 3D-Ne   | tworks-on-Chip                                                | 36   |

|     |       | 2.3.1.  | NoC Building Blocks and Structure                             | 38   |

|     |       |         | 2.3.1.1. Topology                                             | 38   |

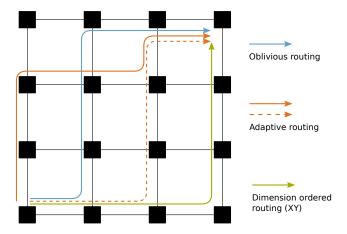

|     |       |         | 2.3.1.2. Routing and Deadlock Avoidance                       | 39   |

|     |       |         | 2.3.1.3. Network Interface                                    | 40   |

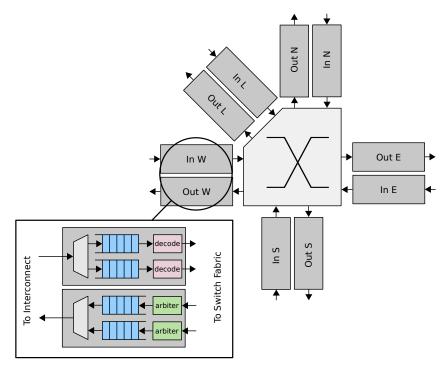

|     |       |         | 2.3.1.4. Router Architecture                                  | 41   |

|     |       | 2.3.2.  | Application Specific Networks-on-Chip                         | 43   |

| 3.  | TSV   | -Hub f  | or Virtualization of Inter-Layer-Links                        | 49   |

|     | 3.1.  | Efficie | nt Use of TSV Resources                                       | 51   |

|     |       | 3 1 1   | Serialization and Multiplexing of Data Streams over TSV Array | s 51 |

|    |      | 3.1.2. | Vertical Continuation of On-Chip Bus Protocols              | 55    |

|----|------|--------|-------------------------------------------------------------|-------|

|    |      |        | 3.1.2.1. Shared Media Buses                                 | 56    |

|    |      |        | 3.1.2.2. Multiplexed Buses                                  | . 56  |

|    |      | 3.1.3. | Channel based interconnects                                 | 66    |

|    | 3.2. | TSV-H  | ub Architecture and Implementation                          | . 70  |

|    |      | 3.2.1. | Concept                                                     | . 70  |

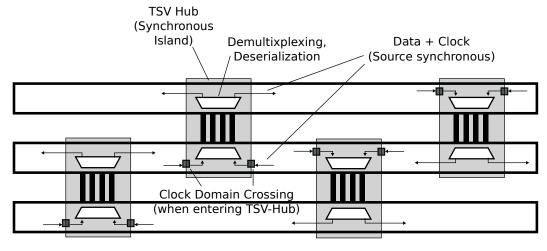

|    |      |        | 3.2.1.1. Clock Domains and Clock Distribution               | . 70  |

|    |      |        | 3.2.1.2. Fault Tolerance                                    | 71    |

|    |      | 3.2.2. | TSV-Hub Protocol Stack                                      | . 72  |

|    |      |        | 3.2.2.1. Physical Layer                                     | . 72  |

|    |      |        | 3.2.2.2. Virtual Link Layer                                 | . 74  |

|    |      |        | 3.2.2.3. Interconnect layer                                 | 81    |

|    | 3.3. | Experi | mental Results and Discussion                               | . 83  |

|    |      | 3.3.1. | Physical Layer                                              | . 83  |

|    |      |        | 3.3.1.1. Switch Boxes                                       | . 83  |

|    |      | 3.3.2. | Virtual Link Layer                                          | 90    |

|    |      |        | 3.3.2.1. Serialization                                      | 90    |

|    |      | 3.3.3. | Protocol Layer                                              | 90    |

|    |      |        | 3.3.3.1. AXI Case Study                                     | 90    |

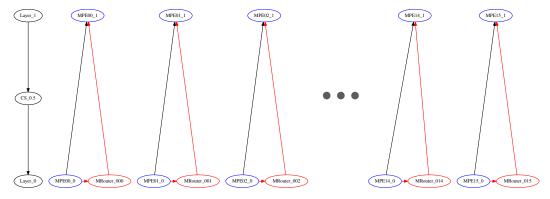

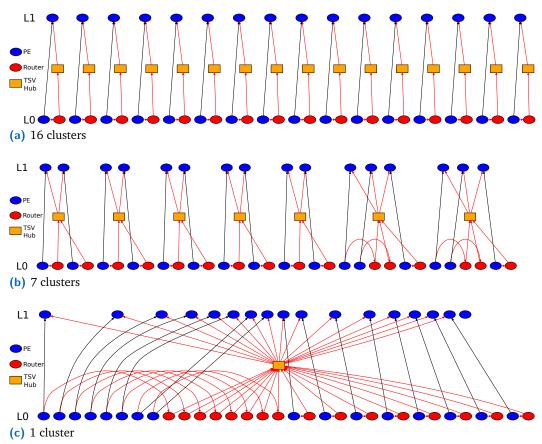

| 4  | TSV  | Prope  | erty Aware 3D-Network-on-Chip Synthesis                     | 97    |

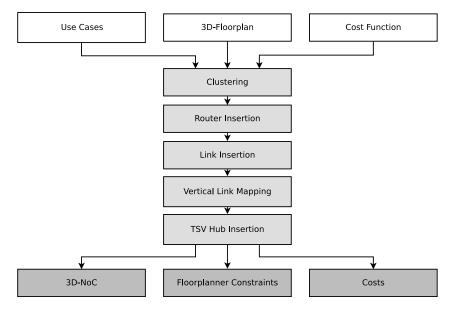

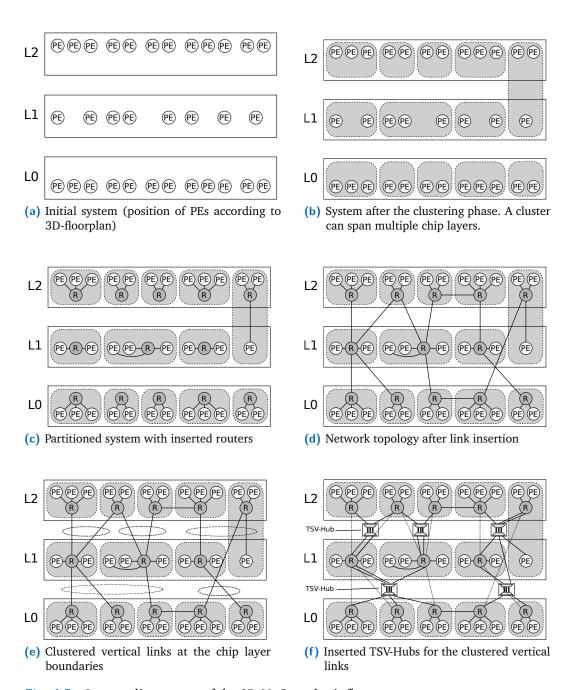

| ٠. |      | -      | ynthesis process                                            |       |

|    | 1.1. |        | Problem formulation                                         |       |

|    |      |        | Overview                                                    |       |

|    |      |        | Clustering and Router Insertion                             |       |

|    |      |        | Generation of NoC-Links                                     |       |

|    |      |        | Vertical Link Bundling and TSV-Hub-Insertion                |       |

|    |      |        | 4.1.5.1. Bandwidth correlation                              |       |

|    |      |        | 4.1.5.2. Spatial Distance of Link Crossing Points           |       |

|    |      |        | 4.1.5.3. Link Affinity                                      |       |

|    |      |        | 4.1.5.4. TSV-Hub Preliminary Placement                      |       |

|    |      |        | 4.1.5.5. Determining Optimal Number of Vertical Link Bundle |       |

|    |      |        | 4.1.5.6. TSV-Hub Configuration                              |       |

|    |      |        | 4.1.5.7. Algorithm Summary                                  |       |

|    | 4.2. | Synthe | esis Output                                                 |       |

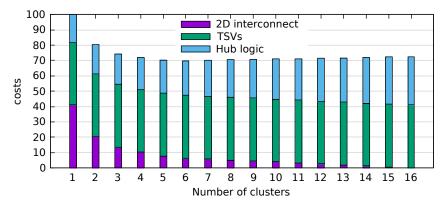

|    |      |        | mental Results                                              |       |

|    |      | -      | Complexity and Costs of Vertical Link Bundling              |       |

|    |      |        | Latency Analysis                                            |       |

|    |      |        | Case Study                                                  |       |

| _  | _    |        |                                                             |       |

| 5. |      |        | and Outlook                                                 | 131   |

|    | 5.1. | Summ   | ary of Contributions                                        | . 131 |

|    | 5.2. | Future Work                              | 133 |

|----|------|------------------------------------------|-----|

|    | 5.3. | Outlook                                  | 134 |

| Α. | Арр  | endix                                    | 137 |

|    | A.1. | TSV-Array Yield per Area Investment      | 137 |

|    | A.2. | TSV Sidewall Depletion Area              | 139 |

|    | A.3. | Markov Modeled on-off Traffic Generation | 141 |

# List of Figures

| 1.1. Evolution of transistor count and process nodes                | 1  |

|---------------------------------------------------------------------|----|

| 1.2. More Moore and More than Moore                                 | 3  |

| 1.3. 3D-Packaging vs. 3D-Integration                                | 4  |

|                                                                     | 10 |

|                                                                     | 11 |

| 2.3. Scaling of maximum interconnect length in a 3D-IC              | 14 |

| 2.4. Different approaches for TSV insertion in the fabrication flow | 15 |

|                                                                     | 18 |

| 2.6. Hybrid Memory Cube memory stack                                | 20 |

| 2.7. High Bandwidth Memory package arrangement                      | 20 |

| 2.8. TSV cross sections                                             | 22 |

| 2.9. Lumped RC circuit to model TSV behavior                        | 23 |

| 2.10. $R_{tsv}$ and $C_{tsv}$ with respect to TSV proportions       | 27 |

| 2.11. System yield with respect to TSV yield                        | 28 |

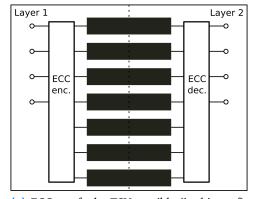

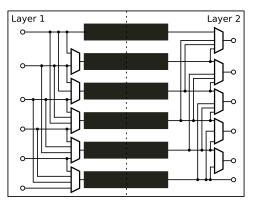

| 2.12. Comparison of methods for fault tolerance in TSV arrays       | 30 |

| 2.13. (De) serializer design of Pasricha et al                      | 33 |

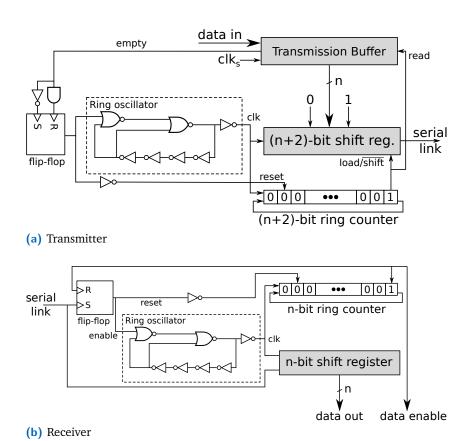

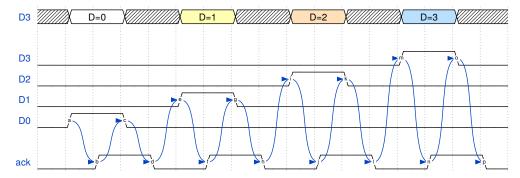

| 2.14.QDI timing                                                     | 34 |

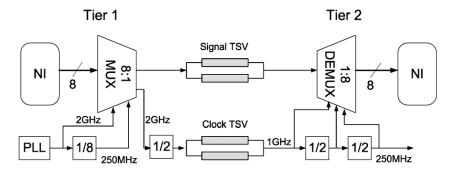

| 2.15. Synchronous serialization methodology of Sun et al            | 34 |

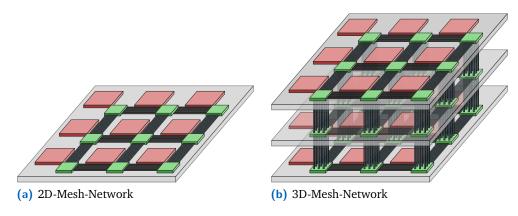

| 2.16.2D- and 3D-Mesh NoC topology                                   | 38 |

| 2.17. Routing schemes in a 2D-mesh Network-on-Chip (NoC)            | 40 |

| 2.18. NoC Router                                                    | 41 |

| 2.19. Scale preserving outline of a 3x3 3D mesh NoC                 | 43 |

| 2.20. Communication Graphs                                          | 44 |

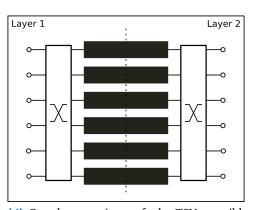

| 3.1. TSV-Hub (Schematic Illustration)                               | 49 |

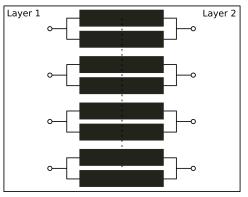

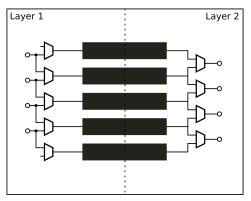

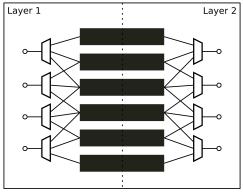

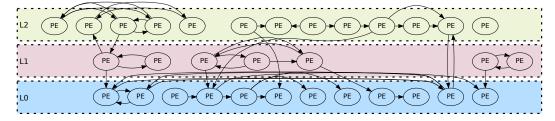

| 3.2. Inter-layer continuation of a 3D-mesh NoC                      | 52 |

| 3.3. Pass-through continuation                                      | 53 |

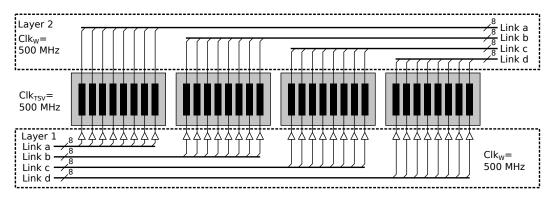

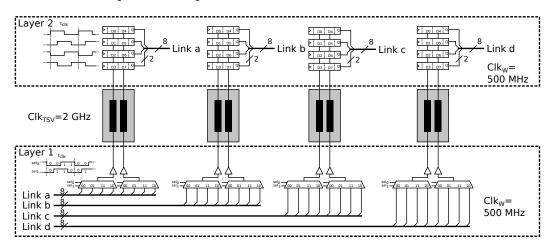

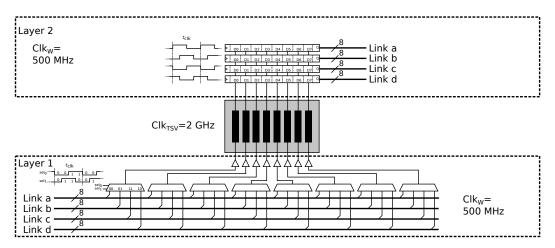

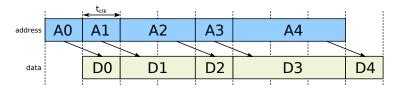

| 3.4. Serialization with increased TSV clock rate                    | 53 |

| 3.5. Multiplexing with increased TSV clock rate                     | 54 |

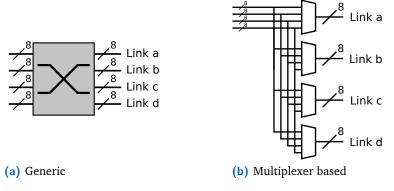

| 3.6. 4-port 8-bit crossbar                                          | 55 |

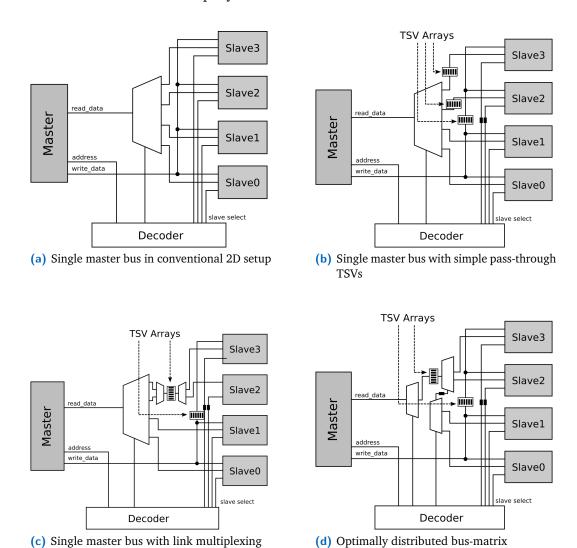

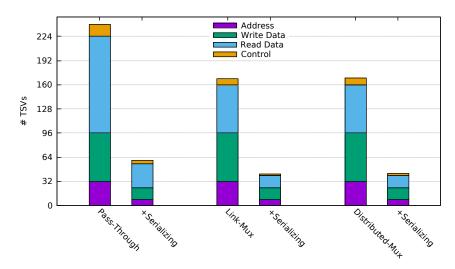

| 3.7. 3D Single Master Bus                                           | 57 |

| 3.8 TSV count for a generic single master bus and four slaves       | 58 |

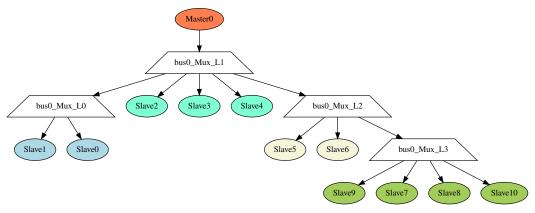

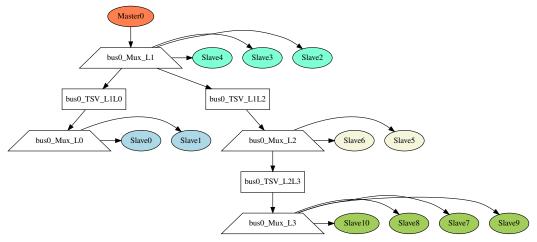

| 3.9. Different stages of bus multiplexer tree generation for 3D-ICs               | 60  |

|-----------------------------------------------------------------------------------|-----|

| 3.10. Address and data bus dependencies                                           | 62  |

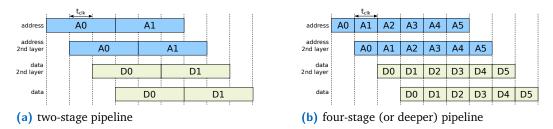

| 3.11. Bus transaction duration with different pipeline depths                     | 64  |

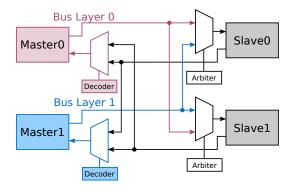

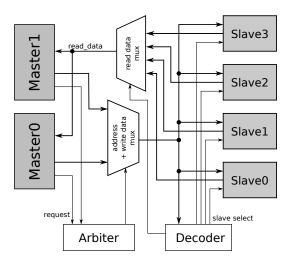

| 3.12. Multi-layer bus with two masters and two slaves (fully connected)           | 65  |

| 3.13. Multi-master bus with two masters and 3 slaves                              | 66  |

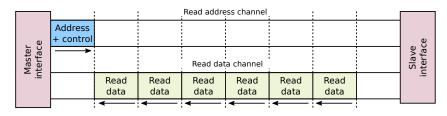

| 3.14. Axi protocol read channels                                                  | 67  |

| 3.15. Axi protocol write channels                                                 | 67  |

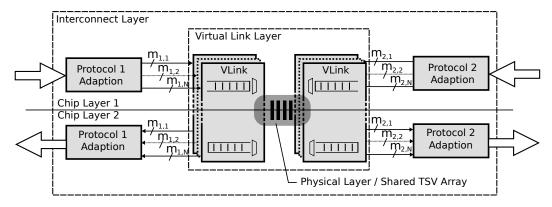

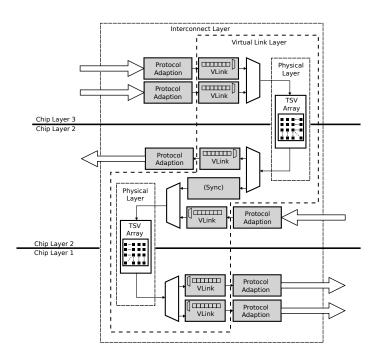

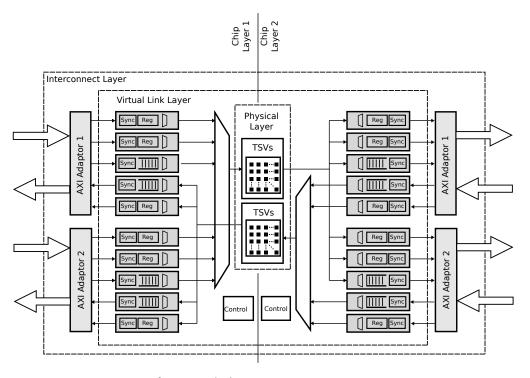

| 3.16. Vertical continuation of interconnects with a TSV-Hub                       | 70  |

| 3.17. Multiple TSV-Hubs in a GALS-Architecture                                    | 71  |

| 3.18. Abstraction layers in 3D on-chip-interconnect                               | 73  |

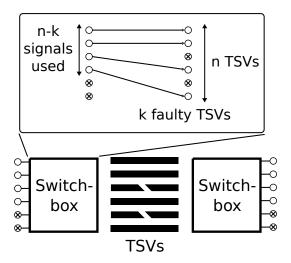

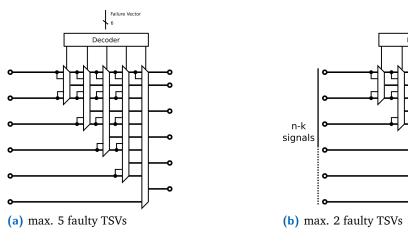

| 3.19. Principle of switch boxes (sparing defective TSVs)                          | 74  |

| 3.20. Switchbox architecture                                                      | 75  |

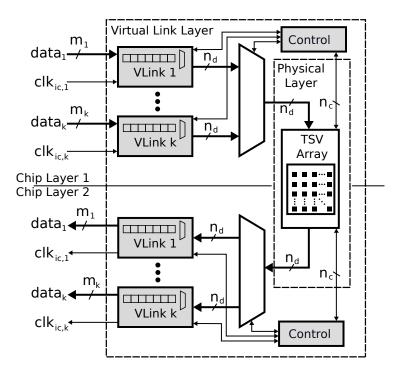

| 3.21. Multiple virtual links transported with the TSV-Hub                         | 76  |

| 3.22.TSV-hubs in series                                                           | 77  |

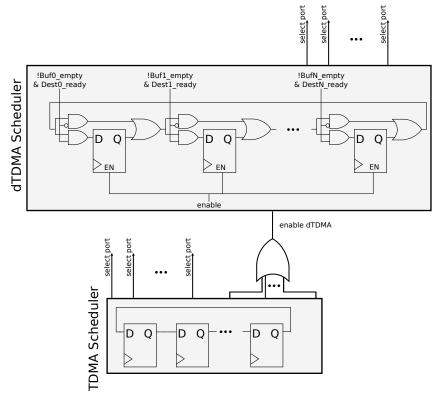

| 3.23. Hybrid TDMA and dTDMA Scheduler                                             | 79  |

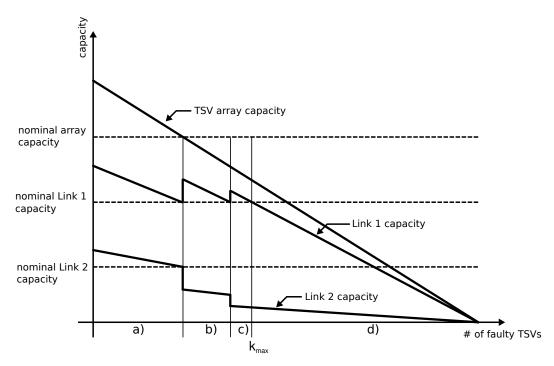

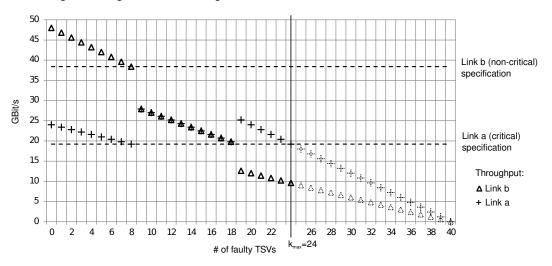

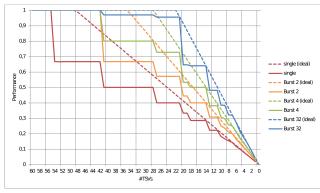

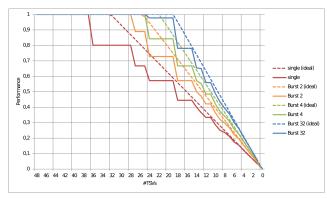

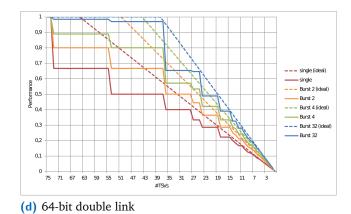

| 3.24.Link performance as a function of the number of faulty TSVs                  | 80  |

| 3.25.Link performance as a function of the number of faulty TSVs                  | 81  |

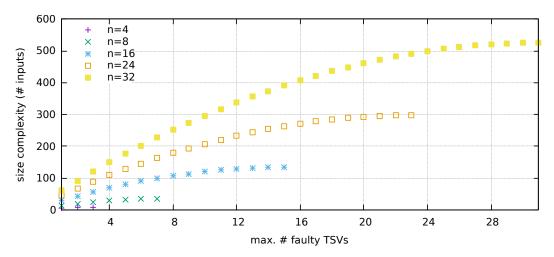

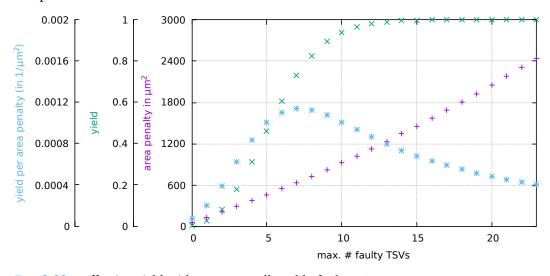

| 3.26. Switch box size complexity w.r.t. maximum number of faulty TSVs .           | 84  |

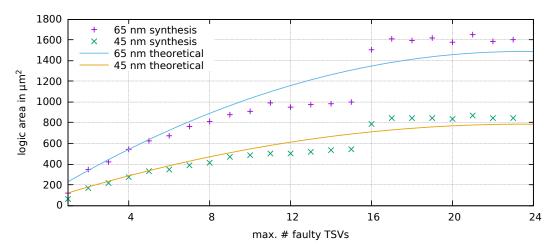

| 3.27. Switch box area as a function of $k_{max}$ for an array with 24 TSVs        | 84  |

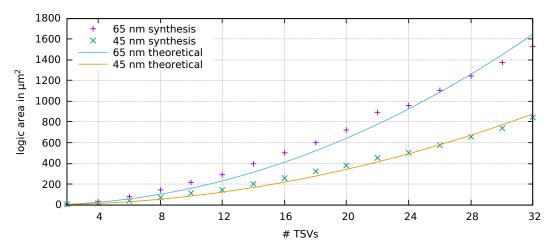

| 3.28. Switch box area with $k_{max}=0.5n$                                         | 85  |

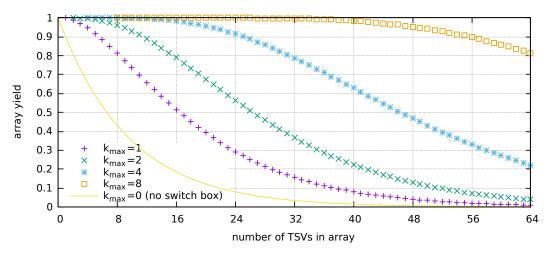

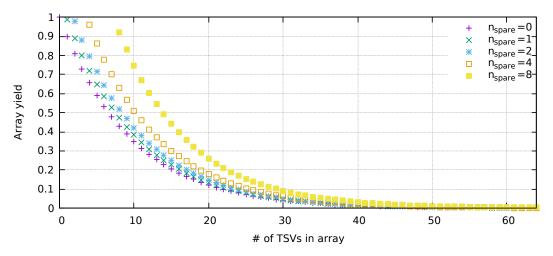

| 3.29.<br>Yield for switch box TSVs with respect to TSV count ( $p_{tsv}=0.9$ )    | 86  |

| 3.30. Effective yield with respect to allowable faulty TSVs                       | 87  |

| 3.31.TSV array with 4 <i>reinforced TSVs</i> among eight total vertical signals . | 88  |

| 3.32. Yield for TSV arrays with reinforced TSVs ( $p_{tsv}=0.9$ )                 | 88  |

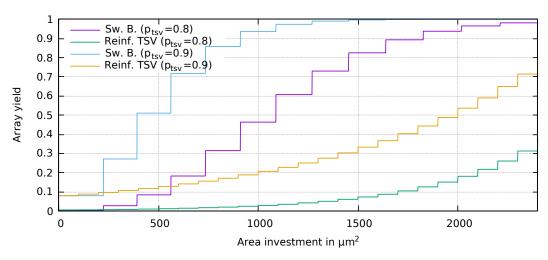

| 3.33. Yield per area investment                                                   | 89  |

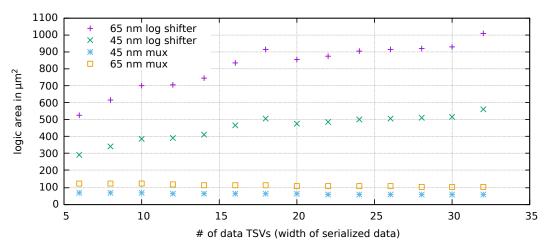

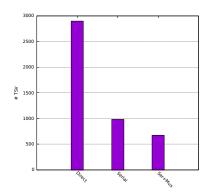

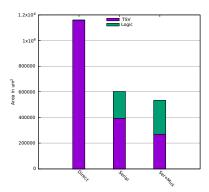

| 3.34. Area consumption of serializer implementations (64-bit link)                | 90  |

| 3.35. Continuation of two AXI links                                               | 91  |

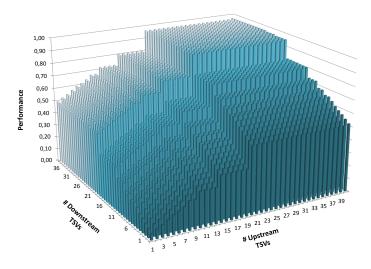

| 3.36.Performance with respect to TSV count for upstream and downstream            | 93  |

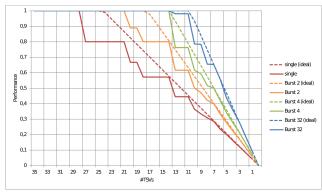

| 3.37.Performance degradation of TSV continued AXI links w.r.t. burst size         | 95  |

| 4.1. Communication graph example                                                  | 97  |

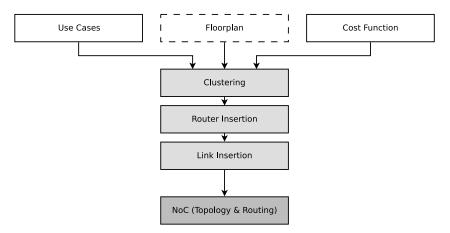

| 4.2. Synthesis Flow of Todorov et al                                              | 98  |

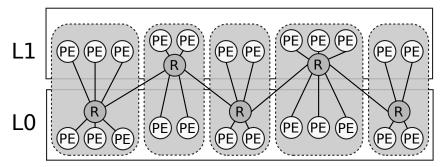

| 4.3. Outcome of using 2D-Synthesis flow for 3D-Design                             | 99  |

| 4.5. Intermediate stages of the 3D-NoC synthesis flow                             | 102 |

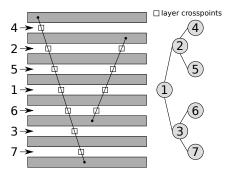

| 4.6. TSV bundling order and layer cross points                                    | 105 |

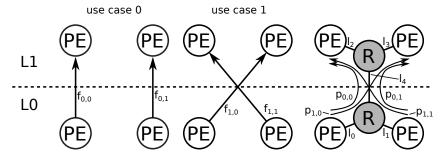

| 4.7. Simple flow mapping example                                                  | 105 |

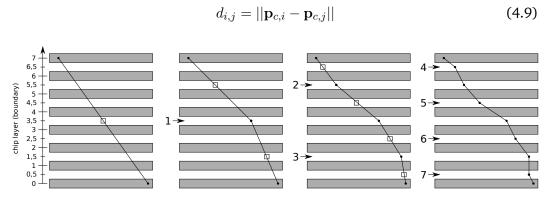

| 4.8. Successive preliminary TSV-Hub placement                                     | 108 |

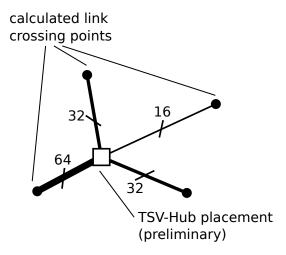

| 4.9. Preliminary TSV-Hub placement                                                |     |

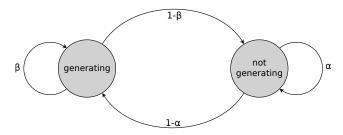

| 4.10. Markov modeled IPP                                                          | 114 |

| 4.11. Basic system with 32 PEs forming 16 independent pairs                       | 116 |

| 4.12. Synthesis output for different cluster counts                               | 117 |

| 4.13. Weighted costs with respect to cluster count                                | 118 |

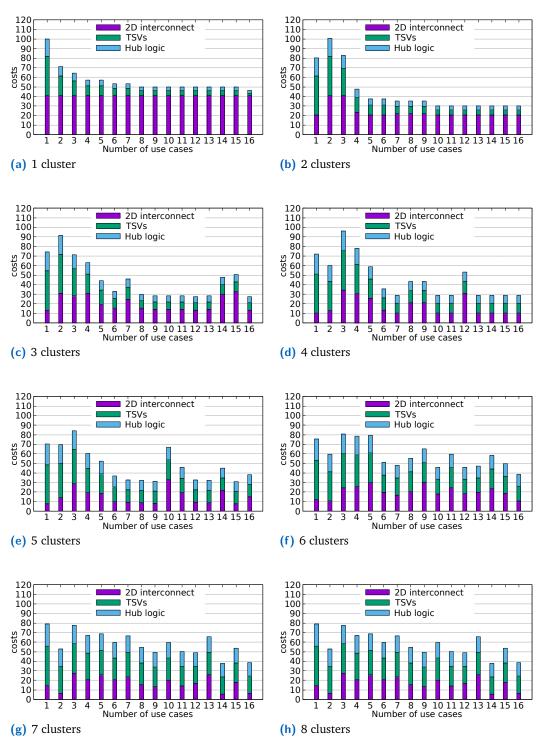

| 4.14. Weighted costs w.r.t number of use cases (1 to 8 clusters) 120   |

|------------------------------------------------------------------------|

| 4.15. Weighted costs w.r.t. number of use cases (9 to 16 clusters) 121 |

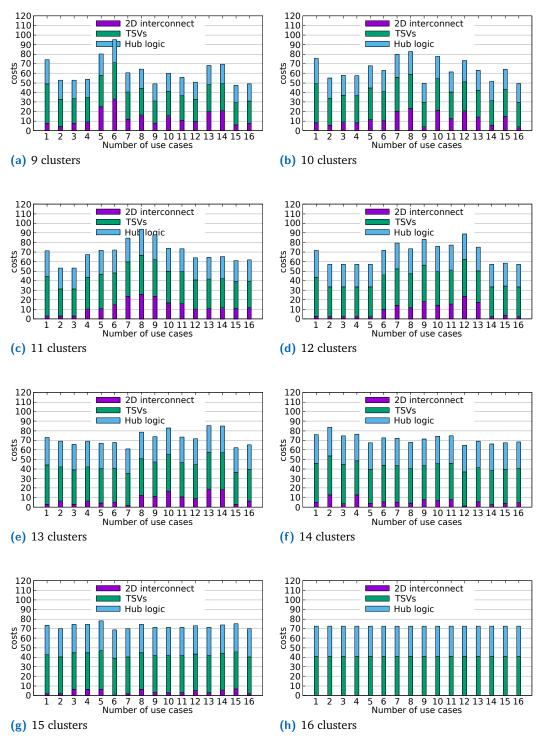

| 4.16.Example of auto-generated CCG an 3D network graph 124             |

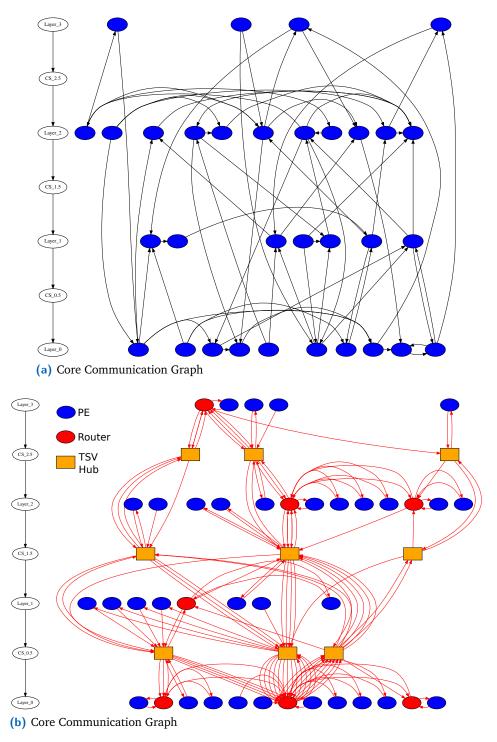

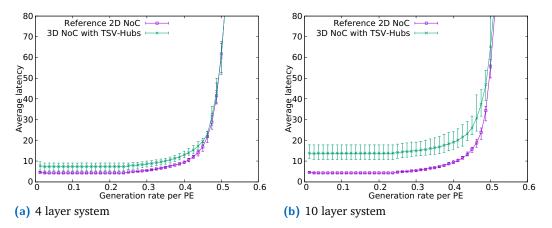

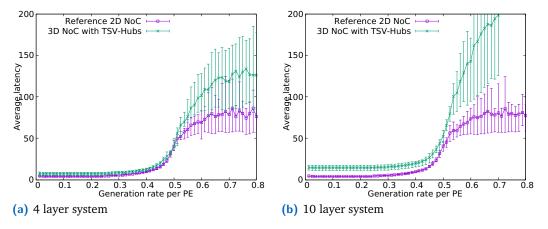

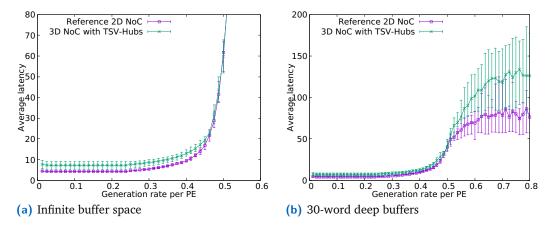

| 4.17. Average delay 4 layer system with infinite buffer space 125      |

| 4.18. Average delay in 4 layer system with 30 words deep queues 125    |

| 4.19. Average delay in 4 layer system with 64 cores                    |

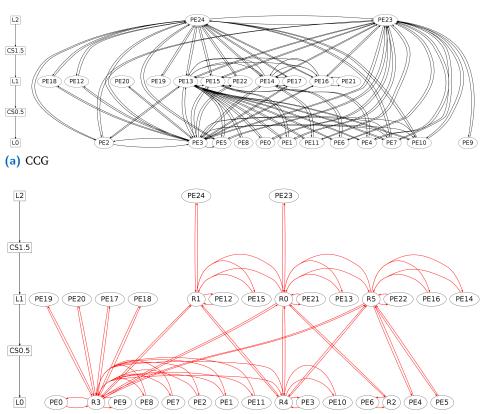

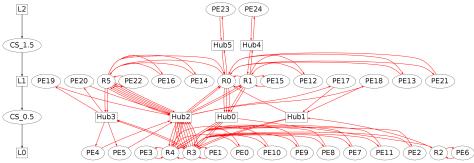

| 4.20.CCG, synthesized on-chip network and 3D-continued network 128     |

| 4.21.TSV count and area comparison                                     |

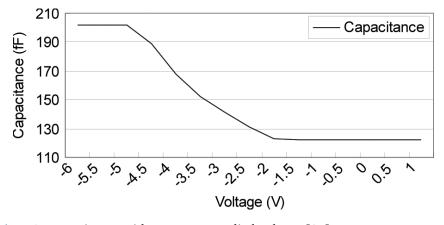

| A.1. TSV capacitance with respect to applied voltage [85] 139          |

| A.2. Markov modeled IPP                                                |

# List of Tables

| 2.1. | Comparison of stacking methods                               | 17  |

|------|--------------------------------------------------------------|-----|

| 2.2. | TSV Models in literature                                     | 24  |

| 2.3. | Input parameters for basic TSV model                         | 26  |

| 2.4. | Comparison of conventional wires and TSVs                    | 31  |

| 2.5. | Comparison synthesis solutions for Application Specific NoCs | 48  |

| 3.1. | Required AXI channel wires for different bus sizes           | 67  |

| 3.2. | VLink Termination Methods                                    | 77  |

| 3.3. | Area consumption of the mesochronous FIFOs                   | 92  |

| 3.4. | Area consumption of the mesochronous synchronizers           | 93  |

| 3.5. | Area consumption of full TSV-Hub                             | 94  |

| 3.6. | Percentage of original TSV induced area                      | 94  |

| 4.1. | Case study key parameters                                    | 127 |

| 4.2. | Case study results                                           | 127 |

# Acronyms

**3D-IC** Three dimensional integrated circuit

**AC** Alternating Current

AMBA Advanced Microcontroller Bus Architecture

APCG Application Characterization Graph

**AXI** Advanced eXtensible Interface

**BEOL** Back End of Line

**BIST** Built In Self Test

**CCG** Core Communication Graph

CG Core Graph

**CMOS** Complementary Metal–Oxide–Semiconductor

**CMP** Chip-Multi-Processor

CoWoS Chip-on-Wafer-on-Substrate

**CPU** Central Processing Unit

CTE Coefficient of thermal expansion

CTG Communication Task Graph

**D2D** Die-to-Die

**D2W** Die-to-Wafer

**DAP** Duplicate Add Parity

**DC** Direct Current

**DDR** Double Data Rate

**DMA** Direct Memory Access

**DOR** Dimension Ordered Routing

**DP** Dynamic Programming

**DRAM** Dynamic Random Access Memory

dTDMA dynamic Time Division Multiple Access

**ECC** Error Correcting Code

**EDA** Electronic Design Automation

**EMC** Electromagnetic Compatibility

**F2B** Face-to-Back

F2F Face-to-Face

**FEM** Finite Element Method

FEOL Front End of Line

**FIFO** First-In-First-Out

**FPGA** Field Programmable Gate Array

**GALS** Globally Asynchronous Locally Synchronous

**GMLS** Globally Mesochronous Locally Synchronous

**GPS** Global Positioning System

**GPU** Graphics Processing Unit

**HBM** High Bandwidth Memory

**HDL** Hardware Description Language

**HF** High Frequency

**HMC** Hybrid Memory Cube

**HoL** Head of Line

IC Integrated Circuit

**ILL** Inter Layer Link

**ILP** Integer Linear Programming

**IPP** Interrupted Poisson Process

ITRS International Technology Roadmap for Semiconductors

**JEDEC** JEDEC Solid State Technology Association (formerly: Joint Electron Device Engineering Council)

KGD Known Good Die

KGD Known Good Die

KoZ Keep-out-Zone

**LPDDR** Low Power Double Data Rate (a low power double data rate synchronous DRAM standard)

**LP** Linear Programming

**MEMS** Microelectromechanical System

MOS Metal-Oxide-Semiconductor

MPSoC Multi-Processor System-on-Chip

MTTF Mean Time To Failure

NEEDS German: Nanoelektronik-Entwurf fuer 3D-Systeme

**NI** Network Interface

NoC Network-on-Chip

NP nondeterministic polynomial time (a complexity class)

**OCP** Open Core Protocol

**OO** Out-of-Order

PCB Printed Circuit Board

**PE** Processing Element

PoP Package-on-Package

**PSO** Particle Swarm Optimization

**QDI** Quasi Delay Insensitive

QDI Quasi-Delay-Insensitive

**QoS** Quality of Service

**RDL** Redistribution Layer

**RF** Radio Frequency

**RPA** Routing Path Allocation

**RTL** Register Transfer Level

**RTL** Register Transfer Level

**SCG** Switch Communication Graph

**SEE** Single Event Effect

SiO<sub>2</sub> Silicon dioxide

**SiP** System in Package

**SoC** System-on-Chip

**TDMA** Time Division Multiple Access

**TSV** Through Silicon Via

**UART** Universal Asynchronous Receiver Transmitter

**UHD** Ultra High Definition

**VC** Virtual Channel

VHDL Very High Speed Integrated Circuit Hardware Description Language

vILL virtual Inter Layer Link

**W2W** Wafer-to-Wafer

Introduction

Integrated Circuits (ICs) have seen an incredible evolution over the past 50 years. This development has revolutionized our everyday life, it has affected how we consume, exchange and store information, how we control machines, how we travel and many other things. Across all domains of science and technology new applications were created, which again were enhanced, and as people adapted to new technologies a continuous demand for new and even more powerful devices was triggered.

The key enabler for this process is the still ongoing down scaling of the minimal feature size in semiconductor devices. This has allowed to integrate more and more transistors into the same area on a single die. The results are more computation resources, higher speed (clock frequencies) and lower power consumption (per transistor). Today, the highest transistor counts are found in the domain of massively parallel computing applications dominated by Graphics Processing Unit (GPU) and Field Programmable Gate Array (FPGA) devices. At the time of writing of this thesis, chips integrating more than 20 billion transistors are available on the market [8]. Besides, also heterogeneous platforms are highly profiting from the shrinking process. Today's high integration density allows to build systems integrating many different and specialized modules on a single chip instead of connecting individual ICs. This is what we call a System-on-Chip (SoC). SoCs power smartphones, smart TVs, navigation systems, Internet routers and many other devices.

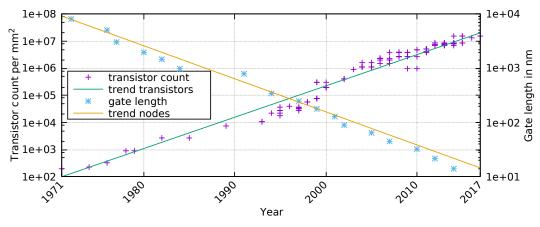

Fig. 1.1.: Evolution of transistor count per area and gate length (process nodes). The data points for the transistor count show the number of high end Intel server and desktop processors (data source [9]). The process node data points show the minimal gate length at the time of their introduction (data source [10]).

The shrinking process was first quantified by Gordon Moore in 1965 [11] as an increase of transistor count per area by a factor of two every year. He later corrected this to a factor of two every two years [12], and shortly later the term *Moore's Law* was born as a name for the process [13]. Looking back from today, we have to correct the number for the doubling to about 20 months, but it still follows very closely an exponential curve.

Fig. 1.1 visualizes the shrinking process and shows the evolution of both transistor count per  $\mathrm{mm}^2$  and the process nodes (represented by the gate length) for a time frame from 1971 to 2017. It shows that the process is still ongoing, although its end has often been predicted. However, it will eventually come to its natural end once the scaling reaches the atomic level of silicon [14].

Moore's Law is often illustrated as a continuous line in diagrams or is even characterized by the formula for exponential growth as a continuous process. However, we should be aware that it is in fact a sequence of discrete points of *Process Nodes*, and that a story lies behind each individual point in the graph. Researchers and engineers in the semiconductor industry have worked hard to achieve the individual technological leaps to reach the next node. Process technology has been continuously improved and new processing steps were researched, implemented and improved. In recent years, the shrinking could only be achieved through hard efforts and very sophisticated manufacturing processes, like double patterning lithography [15] or the introduction of FinFet transistors to mass production [16]. As a consequence, to this day, only a few companies have been able to keep pace with this development, and worldwide only a few semiconductor fabrication plants (Fabs) have the financial resources, the necessary equipment, the required know-how and accordingly well calibrated processes to produce the latest technology. It is clear that this process cannot continue forever, at least regarding mass production, since this would make modern chips too expensive for the normal consumer. However, the demand for more advanced SoCs with even more computational power and more building blocks is still unbroken. Lately, researchers and semiconductor manufacturers have therefore been looking in other directions and evaluating improved integration techniques that not solely relying on downsizing. The term More than Moore was coined [17] and can be understood as a process orthogonal to further scaling which is now labeled as More Moore.

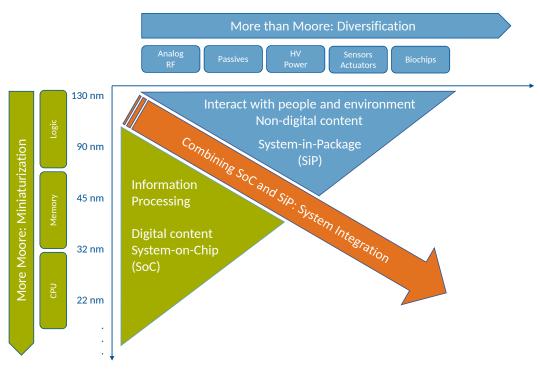

While transistor scaling is ideal for further improving computation power, More than Moore provides diversification beyond the digital level. It enables the chip to incorperate modules for interacting with the environment like sensors, power electronics, RF components, etc. Fig. 1.2 shows the two dimensions as illustrated in an International Technology Roadmap for Semiconductors (ITRS) White Paper from 2010 [17].

Fig. 1.2.: More Moore and More than Moore (adapted from [17])

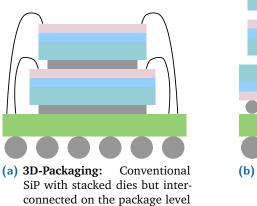

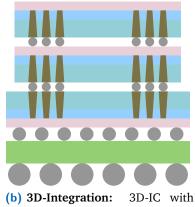

A prominent approach of the *Moore than Moore* category is the System in Package (SiP) technology which has been around for many years now and labels the integration of multiple dies in a single package. Such dies can be aligned next to each other (horizontally) or stacked on top of each other (vertically, Fig. 1.3a) or both. The reasoning for building a SiP is generally due to *Heterogeneous Integration* demands i. e. to combine dies that are manufactured with different integration technologies in order to use the individually best suited process for each one. A famous example is the combination of sensoring or Microelectromechanical System (MEMS) modules with a digital processing platform.

Combining both of the orthogonal evolutions shown in Fig. 1.2 results in a new category of systems that is both SoC and SiP and referred to as *System Integration* [6]. In other words, such are systems designed for the latest integration processes to create highly integrated SoC designs with a high module and transistor count but also to distribute those modules on several dies, possibly created with different integration processes. So-called *3D-ICs* generally fall into this category. Another important differentiator between conventional SiPs and 3D-ICs is the internal interconnection technology. In conventional SiPs wirebonding is the standard, and the individual dies are interconnected on package level. In contrast, in 3D-ICs, high performance direct interconnects are required (Fig. 1.3b) to fully exploit the performance offered by the submodules and to supply sufficient communication bandwidth. While different solutions for realizing such interconnects are investigated, the most promising by far is the so-called TSV technology.

Fig. 1.3.: 3D-Packaging vs. 3D-Integration

via wire bonding.

(b) 3D-Integration: 3D-IC with direct interconnection through TSVs.

At the level of the on-chip communication subsystem a higher SoC complexity poses problems for conventional interconnection designs. Schemes like buses, rings and crossbars do not scale properly for a larger number of nodes. Therefore, the concept and paradigm of NoC was introduced [18], [19], researched and integrated into first consumer products [20], [21]. It is clear that in complex 3D-IC designs, which are generally also complex SoCs, this issue is even more evident, and NoCs will clearly be required in most 3D-ICs and will be the communication subsystem of choice in such designs [22].

It can be concluded that TSV technology will play an important role in physically realizing NoC links in future 3D-SoCs. This work focuses on such 3D-ICs and in particular on the optimization of the communication subsystems for the use of TSV-based interconnects.

### 1.1 Problem Statement

With TSV-based 3D-ICs, the design of the on-chip interconnect backbone gets more challenging since TSVs differ from conventional wires of planar systems with respect to physical parameters, cost and reliability. Therefore, vertical connections between the individual active layers in 3D-ICs have to be treated differently compared to conventional wires, and conventional design tools as well as IP-Cores for interfacing cannot be directly used without modification and adaption.

Most existing research in the domain of 3D-NoCs considers TSVs in the scope of network topology and routing implications. This approach has clearly its justification, since, as a result of the added degree of freedom, novel topology layouts are possible and new challenges arise with this. However, the physical implications that TSVs impose even on higher levels of abstractions have to be considered as well.

SoCs are usually composed of a multitude of functional building blocks (*IP-Cores*). Such IP-Cores are equipped with standardized interfaces that can connect to onchip communication subsystems like buses or on-chip networks. Design re-use is crucial in the field of SoC design in order to reduce costs and meet time-to-market requirements. For future 3D-ICs this principle will not change, and designers will still have to rely on existing libraries of building blocks. One challenge is therefore to stretch conventional and popular on-chip interconnection protocols over multiple layers in 3D-ICs. Hence, it is important for the industry to know beforehand which conventional protocols are well suited to be used in a 3D environment and which are not.

The number of available metal layers in ICs has been constantly increased over the past years. This is reflected in modern interconnect protocols which are using many wires per link. Systems like AMBA AXI [23] require hundreds of wires for a single connection. Since wiring resources are plenty in conventional ICs, this is not critical here [24]. Also for 3D-ICs, highly parallel connections have been standardized (e. g. Wide I/O [25]), however those standards are intended for stacked DRAM designs, hence there is usually only a single link present in the system connecting a DRAM die to a CPU die. In a 3D-SoC, however, multiple links can be expected to traverse layer boundaries. If these links exhibit a high wire count, this will result in a total of thousands of TSVs when no countermeasures are taken. This is problematic due to large TSV footprint and reliability concerns. A one to one mapping of such wide connections is next to impossible because it would make the chip both very costly and very likely to fail [26]. Therefore, novel smart mapping mechanisms have to be found that efficiently use TSVs and exploit their physical properties by maintaining the interface compatibility and timing requirements.

NoCs usually use a rather wide interface, and due to their distributed layout they are constructed of many point-to-point connections between the individual routers. For 3D-ICs, this presents the designers with the same challenges as with bus-based systems: a very high expected TSV count.

On top of this, designing an application specific network on chip for a SoC is, due to the large search space and many degrees of freedom, a complex task. Generating such NoCs has to be done in automated fashion and is a research topic on its own. However, for 3D-ICs the step of mapping the on-chip connections on the TSV arrays has to be included in the NoC generation flow in order to enable an efficient and economic use of TSV resources.

Another problem with TSVs is the to this day still rather low reliability. TSVs can turn faulty due to mechanical stress already in the manufacturing process, and there is a significant probability for them to turn defective when the chip is operational. Thus, mechanisms have to be found to cope with such TSV faults.

### 1.2 Thesis Contributions

The solutions proposed in this thesis aim to leverage the physical properties of TSVs and operate the TSVs on the edge of their physical possibilities as well as aim at making TSV-based connections more resilient.

The three contributions of this work can be summarized as follows:

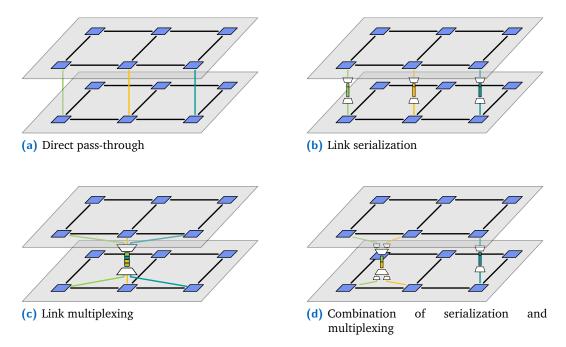

- The first contribution addresses the vertical continuation of conventional onchip interconnect protocols in 3D-ICs. The main objective is to reduce the total number of TSVs in order to save costs, reduce footprint and improve yield. This is achieved with multiplexing and serialization techniques in combination with operating TSVs at an increased clock speed. Pure serialization for a single inter-layer link has been proposed before [27], [28]. Link multiplexing and an evaluation when it is advantageous compared to pure serialization has been, to the best of our knowledge, first published by us in [1]. Distributing an on-chip bus structure to several chip-layers solutions has implications for the bus architecture and its timing. These implications are studied and solutions are presented how a bus-matrix can be optimally split on to multiple layers.

- The second contribution is presented in form of an IP-Core design, the so-called TSV-Hub. It is a configurable module that wraps a TSV array which is virtualized by implementing the principles of serialization and multiplexing. Thereby it provides generic virtual links. These links are used by protocol adapters which implement the interfaces of established on-chip communication protocols and thereby allow to transparently continue such links to other chip layers.

The TSV-Hub also provides means to cope with defective TSVs. Existing TSV redundancy techniques [29]–[32] make use of spare TSVs which are initially unused. In contrast, the proposed solution always uses the complete set of TSVs but spares defective ones and adjusts the link bandwidth dynamically. To the best of our knowledge, this approach was first published by us in [2].

• The third contribution is a synthesis flow for 3D application specific NoCs. It extends an existing 2D synthesis algorithm [33]–[35] for the 3D-scenario. The algorithm considers formally defined communication requirements and the spatial distances of IP-Cores in a 3D floorplan. NoC-links traversing layer-boundaries are analyzed and potentially continued over a shared TSV array depending on their timing relations and spatial distances. Compared to other 3D-NoC synthesis algorithms, this is, to the best of our knowledge, the first one that includes multiplexing and serialization techniques and a clock speed-up at TSV level. The new synthesis flow has been developed in collaboration with TUM colleagues from the Chair of Electronic Design Automation (EDA) and was published in [4].

Improvements on the physical level of TSV technology are not within the scope of this thesis. TSVs are, in this work, abstracted on the level of geometry, reliability and basic electrical properties such as capacitance and resistance. The proposed solutions are given as examples on Register Transfer Level (RTL), such that, together with the physical parameters of TSVs and those of targeted standard cell libraries, timing and power simulations can be carried out that show the achieved improvements and underpin presented evaluations.

The physical TSV properties are gathered from scientific publications based on actual measurements or simulations or by means of published calculations models and are referenced accordingly.

Next to the TSV-Hub other NoC building blocks are re-used which are based on state of the art NoC designs, mainly on the LISNOC [36] design.

The work presented in this dissertation is based on the research carried out as part of the NEEDS project, which was funded by the German Federal Ministry of Education and Research, funding label 01M3090.

The ideas presented in this dissertation have been published in the following works: [1],[2],[4],[6],[5].

### 1.3 Thesis Structure

This thesis is structured as follows:

Chapter 2 gives an overview of the state of the art for the relevant topics and discusses related work to the different subjects discussed in this thesis. This covers 3D integrated circuits in general but with a special focus on Through Silicon Vias (TSV), including surveys on TSV modeling and resilience. Another large part of this chapter concerns the topic of Network-on-Chip (NoC). NoC basics are introduced, and challenges that arise with integrating NoC-based communication structures into 3D-ICs are discussed. The chapter concludes with covering synthesis flows for application specific NoCs and also taking into consideration the impact of a stacked design.

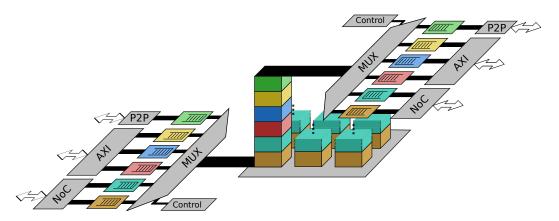

Chapter 3 presents the main contribution of this thesis, i. e.is the TSV-Hub, an IP-Core for efficiently using TSV-based vertical interconnects in 3D-ICs. It starts off with a study on the continuation of conventional interconnect protocols over TSV-based inter-layer connections. Then, the design of the TSV-Hub is introduced and its architecture is described in detail. Finally, experimental results are given in the form of synthesis results, simulations and a case study.

Chapter 4 outlines a TSV property aware 3D-Network-on-Chip synthesis flow for application specific NoCs. The given flow is based on an existing 2D synthesis flow, developed by TUM colleagues from the Chair of Electronic Design Automation (EDA). In collaboration with the authors of this flow, it has been extended to cover the requirements of stacked designs. First, the provision for the impact of TSV-based intra-layer links at an early stage in the flow is described. Later, a novel mapping technique for NoC links onto instantiated TSV arrays is given. The chapter concludes with experimental results for a real-world mobile SoC example.

Chapter 5 concludes this thesis and presents an outlook.

State of the Art

This work covers the optimization of TSV based vertical interconnects in 3D-ICs and presents an approach to include the optimizations in an automated NoC synthesis process. Therefore, research related to this work can be found in both, the domain of 3D-ICs and Network-on-Chip

The chapter starts off by an overview of 3D-IC related research and the driving forces behind it and outlines manufacturing methods and challenges. Next, the main aspects of TSVs are covered. This includes the electrical modeling, TSV reliability and throughput optimizations. Finally, on-chip networks and methods for the automatic generation of application specific NoCs are covered. This includes both general and 3D specific aspects.

### 2.1 3D-Integrated Circuits

The idea of building integrated circuits that extend into the third spatial dimension is nothing particularly new and has been around for many years. Looking at other fields of engineering we see that stacking is an obvious consequence if for instance ground space is limited, distances have to be kept short or just a denser package in general is desired. We stack stories in buildings, containers on ships, build bilevel rail cars and double decker buses. Therefore, also for integrated circuits the idea suggests itself. And in fact it is rather old. The history of silicon through-connections, so-called *TSVs*, dates back to the 1960ies. A patent [37] by IBM from 1967 is usually considered as the invention of TSV technology. However, transistor inventor William Shockley also mentioned TSV-like structures in one of his patents [38] as early as in 1962. Therefore, the question arises as to why 3D-ICs suddenly are becoming relevant more than 50 years after the idea was first described. Again, looking in other domains, there is one factor that often keeps engineers from performing stacking: cost. If there is enough ground available in and around a city, there is no reason to build higher, since this would drive up the costs.

For integrated circuits, reducing the costs per unit is one of the most important design goals, at least for mass production. Apart from a few exceptions (e. g. chips produced in very small volumes for space applications), it is very important to keep the costs as low as possible for a given performance and power requirement. And as long as manufacturers can fulfill these requirements, they will always opt for the technology with the lowest costs. When it comes to 3D Integration, the situation is similar. Until the recently the ongoing downscaling of feature sizes was fast

enough to satisfy the demand for increasing transistor count. Technologies like *System in Package (SiP)* and *Package-on-Package (PoP)* already provided options for heterogeneous integration, and actual die footprint was barely an issue. Looking at the history of integrated circuits, we observe that individual single technological upgrades (e. g. FinFETs) often enabled a new production process with a smaller feature size. These *upgrades*, however, were often not deployed right after their invention but have been kept in the drawer by the semiconductor companies until the time was right, meaning in the most cases, the increased cost for introducing the upgrade was now justifiable because further shrinking could not be achieved by other means. Although 3D-Integration technically does not contribute to die shrinking, it still allows moving forward to house more and diverse components, which are efficiently interconnected in a single package. Current demand for such applications has lead to the first commercially available 3D ICs in recent years.

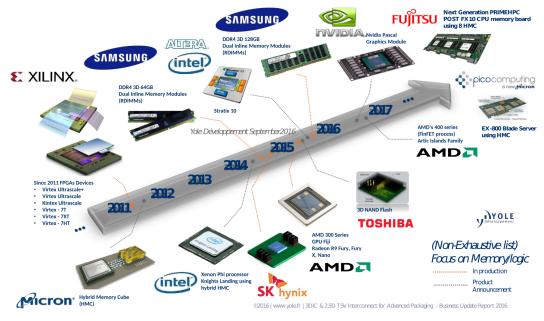

Fig. 2.1.: Timeline for TSVs based commercial 3D-ICs by Yole Développement [39]. Grey lines: announced products. Orange lines: commercially available products.

At the time of writing this thesis the first 3D-ICs (with a considerable amount of TSVs) are commercially available [14] in the form of highest-end FPGAs and memory products. Fig. 2.1 shows a time line of the past few years. Note that most listed products are announcements only (grey lines). The only commercial products that are somehow heterogeneous are the Xilinx FPGAs since they incorporate some transceiver chips next to the FPGA fabric [40]. However, chips are manufactured in very low volumes, and the price of a single chip is exorbitantly high (up to multiple tens of thousands of dollars). Nevertheless, they use TSVs in a significant quantity, which means that the first TSV-based applications have broken the cost barrier.

We see that 3D-IC have not yet hit the market in high volumes. The breakthrough is expected in the coming years when costs for the manufacturing process will be

lowered and performance demand will have increased. Nevertheless, there are many Chip prototypes, and the research community is highly active in both industry and academia.

At this point it is worth to discuss what a 3D-IC actually is and what it is not and why the above mentioned chips qualify as 3D-IC and others do not. In fact, it is not absolutely clear and some experts would disagree and not consider most of the currently commercially available 3D-ICs as *real* 3D-ICs since they are built with interposer technology (see Chapter 2.1.4) and do not stack active dies. Also the nomenclature is occasionally confusing, and many different terms have been coined.

Conventional integrated circuits (in the context of 3D-IC often referred to as 2D-circuits or planar circuits) are in fact (as every physical structure) already three dimensional objects. However, their vertical extent is small (several tens of  $\mu$ m) compared to their lateral one (in the range of some mm). Also, they represent already a layered structure. While there is only one layer of active silicon, there are many wiring layers (e. g. up to 13 in Intel's  $14 \,\mathrm{nm}$  process [41]).

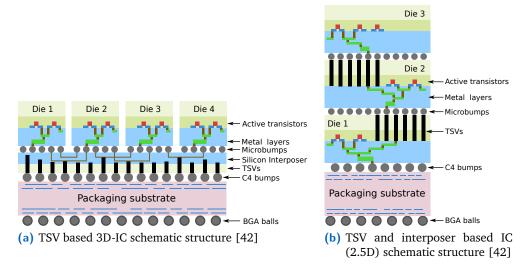

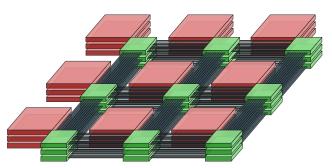

**Fig. 2.2.:** Different types of 3D-ICs. With the interposer technology (also *2.5D-Integration*) the dies are arranged horizontally and placed on a silicon interposer. *Real* 3D-ICs form an actual stack of active dies.

A 3D-IC is formed when several of such conventional ICs are stacked on top of each other, forming a layered structure of layered structures. This is why some researchers avoid the term *layer* for the individual levels of a 3D-IC but call them *tier* or *strata* instead. Throughout this work the term *layer* is used to denote an active layer of a 3D-IC. If a metal layer is meant, the term *metal layer* is used.

Still this is nothing new, using a single package for enclosing multiple dies is known for many years as *System in Package (SiP)*, where dies are either stacked on top of each other or arranged next to each other or a combination of both.

However, there is one important difference that qualifies a package to be labeled as *3D-IC*: The chip can communicate internally, meaning there are direct die-to-die connections. The most prominent technique to realize such connections is the TSV technology. Next to TSVs there are also other concepts which rely on inductive or capacitive coupling [43] or even make use of optical connections [44]. Compared to TSV technology, however, such solutions are more exotic and have not been commercialized yet. They face their own challenges like Electromagnetic Compatibility (EMC) issues and also space consuming and complex transceiver circuitry. In general, TSV technology offers the highest integration density of all direct die-to-die communication solutions [42].

This work is focused on TSV-based die-to-die connections. Therefore, a 3D-IC in the context of this work fulfills the following requirements:

- The chip is built by stacking multiple dies

- · TSVs are used for vertical interconnections

- There is a significant quantity of TSVs

However, there are other definitions, therefore it is worth to look at the 3D-IC terminology in general, which is done in the next section.

### 2.1.1 Terminology

As mentioned above, the terminology regarding 3D-ICs can be confusing, and different terms are used in both research and business. For example it is comprehensible that a chip manufacturing company advertises its interposer based product as a 3D-IC for marketing reasons whereas a researcher would refer to the technology as 2.5D-Integration to distinguish it from the *real* 3D-Integration with multiple active layers.

The following list shows some terms that have become popular in recent years:

**3D-IC** Usually refers to an IC built of multiple stacked dies that communicate internally (e.g. by using TSVs or wireless interconnects).

Stacked IC The same as above but some researchers dislike the term *3D-IC* since the third dimension is not a full degree of freedom (transistors can be placed on one of the available layers but not at any arbitrary z-position) and currently only small integer numbers of active layers (Tiers) are realistic (due to manufacturing challenges and heat dissipation issues).

Monolithic This term refers to a technology that does not rely on stacking dies

3D-IC or wafers to create a chip with a vertical extent of its active area,

but integrates all active components on a single wafer.

**2.5D-IC** This is a term often used in research for setups which are TSV

based but consist only of two layers: a signal redistribution layer and one active layer. The active layer, however, can comprise

multiple dies which are arranged horizontally.

**2.75D-IC** This is a term coined by Reisinger [45] used in the same way as

Stacked IC to avoid the term 3D-IC and emphasize the fact that

the third dimension is not a full degree of freedom [45].

Another possibility of confusion was added since FinFet technology has been rolledout in commercial products. The technology is sometimes marketed as *3D-Transistor technology* [46]. However, this is not related to chip stacking at all.

### 2.1.2 Driving forces behind 3D-ICs

There is not a single motivator behind 3D-ICs but multiple ones. The following list gives the main driving forces:

- Footprint

- Heterogeneous Integration

- Performance and Power

- · Yield and Cost

The most obvious of these drivers, but clearly not the dominant one, is reducing footprint. Naturally the 2D ground area is reduced if the same active silicon area is split into several vertically stacked layers. However, even for conventional planar ICs the actual area used by the die in the package is usually small compared to the full area consumed by the package. Even for applications where PCB space is limited (e. g. mobile phones) this is not critical, and for applications where chips with large sized dies are used, the consumed overall area of the package is mostly uncritical (e. g. high-end FPGAs or high-end graphic chips in work stations).

Heterogeneous integration to a certain extent overlaps with the footprint motivator since with heterogeneous integration it is possible to provide a single package containing multiple different dies manufactured with different processes. However, this is also possible with a SiP. The differentiator here is that a 3D-IC provides, on top of the reduced footprint, also a high direct interconnect throughput compared to the situation where the two dies are interconnected on package level via wire bonding or are even placed in different packages on the PCB.

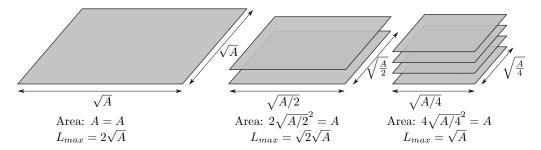

Interconnect length has a significant impact on both power and performance. Shorter wires lead to less resistance and lower capacitive load, hence smaller delays. The maximum wire length of global wires can be drastically reduced with 3D-Integration. Fig. 2.3 shows an example which has been adapted from [47]. The maximum (meaningful) global wire length in a die is the distance from one corner to the one

diagonally opposed. For a planar chip with a silicon area of A this gives a maximum global wire length of  $L_{max}=2\sqrt{A}$ . Note that the wire itself cannot be diagonally oriented for most standard cell processes, and its path is always aligned parallel to the X or Y direction, hence the total length of two times the side length. When the silicon area A is distributed onto n layers by using 3D-Integration, the per layer area is reduced to  $A_l=A/n$  and thus the side length is reduced to  $l=\sqrt{A/n}$ . Therefore, it can be concluded that the maximum length of global interconnects roughly scales with a factor of  $\sqrt(n)$  when silicon area is distributed to multiple layers [47] and overall silicon area is kept constant.

Fig. 2.3.: Scaling of the maximum interconnect length in a 3D-IC with the number of layers while keeping overall silicon area constant (adapted from [47]).

Another strong force demanding vertical integration are the cost and yield factors, which have to be seen intertwined. At first, it seems counterintuitive that with 3D-Integration yield can be increased since TSVs themselves have a rather low yield and in principal reduce the overall system yield. However, with 3D-Integration it is possible to split a large die into smaller portions. The probability that a defect is found on a die depends on its size. When splitting a chip into n dies the probability that a defect is found on any of the n smaller dies is still the same. However, each die can be tested separately, and it can be ensured that only functional dies are interconnected by a Known Good Die (KGD) approach. To this end, the dies do not necessarily have to be vertically stacked. They could also be arranged next to each other horizontally. Therefore, the same yield improvement can also be achieved by building a SiP. However, the requirements on interconnect performance might be too high for wire bonded connections on the package level but not that high that TSV-based connections are needed. For such systems an interposer based integration technology (2.5D-Integration) is the method of choice.

## 2.1.3 Manufacturing

The manufacturing process of 3D-ICs requires additional steps compared to the one for classical planar ICs. For TSV-based 3D-ICs at least the following three major steps have to be added to the process:

- TSV manufacturing (etching and filling)

- Wafer thinning

- · Die Stacking and bonding

#### 2.1.3.1 TSV Manufacturing

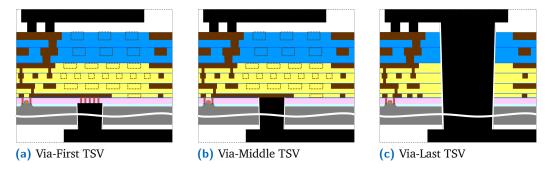

TSVs are vias that punch through the bulk silicon. To create such vias, holes have to be etched and then these holes have to be filled with conducting material (usually copper or tungsten). Different etching processes are available [48].

A major impact on TSV geometry and interconnection is governed by the point in time, relative to the other (2D) process steps, when TSV manufacturing is done. The three prominent approaches for manufacturing TSV based 3D-ICs are the following [49]:

- **Via First TSVs** are manufactured before Front End of Line (FEOL) processing (Fig. 2.4a), i. e. TSVs are fabricated even before transistors are patterned.

- **Via Middle TSVs** are manufactured in between FEOL processing and Back End of Line (BEOL) processing (Fig. 2.4b), i. e. TSVs are fabricated after transistors but before metalization.

- Via Last TSVs are manufactured after BEOL processing (Fig. 2.4c), i. e. TSVs are fabricated after metalization and therefore have to punch through all the metal layers additionally.

Fig. 2.4.: Different approaches for TSV insertion in the fabrication flow [50]

In general, short TSVs are desirable since, due to a limited geometric aspect ratio, short TSVs also achieve small diameters. The shortest TSVs can be created with the Via-First approach. However, in this flow, the TSVs have to withstand the high temperatures of up to  $1000 \,^{\circ}$ C during transistor formation of the FEOL process [42].

For this reason, copper or tungsten cannot be used as filling material due to their high Coefficients of thermal expansion (CTEs). The only choice remaining, is polysilicon which in turn has a much higher resistance and limits the TSV performance. Therefore, the Via-First approach is not widely used [42]. With the Via-Middle approach the TSVs only have to withstand a temperature of roughly  $400\,^{\circ}\mathrm{C}$  encountered during the metalization process. This is feasible with the CTE of tungsten but still problematic with the one of copper [42]. With the Via-Last approach no high temperatures are encountered anymore after TSV fabrication. Therefore, this process is ideal for materials with high CTEs like copper. However, here the TSVs are longer since they also traverse the metalization stack.

#### 2.1.3.2 Wafer thinning and Chip Stacking

When excluding the monolithic approach, the process to manufacture 3D-ICs always involves some sort of stacking. However, there are different possible points in time during the manufacturing process when the stacking can be performed. The main difference is wether stacking is performed before or after wafer dicing.

The available methods are [49]:

- Die-to-Die (D2D) Stacking: single dies are stacked on single dies

- Die-to-Wafer (D2W) Stacking: single dies are stacked on undiced wafers

- Wafer-to-Wafer (W2W) Stacking: undiced wafers are stacked on undiced wafers

The stacking method has implications for several aspects like testing, wafer handling, alignment and production throughput. Tab. 2.1 shows a comparison. A KGD approach is only possible with D2D and D2W flows. With D2D only functional dies are stacked, and with D2W the defective chips in the waver can be spared if wafer level testing is available. When stacking undiced wafers in a W2W flow, defective chips might be stacked on functional ones or vice versa, leading to a reduced yield. Also for the W2W flow, the handling of thinned wafers (with a height of only a few tens of  $\mu$ m) is needed, which is delicate due to possible warpage [51]. However, W2W stacking offers the highest production throughput.

## 2.1.4 Interposer based 3D-ICs (2.5D-Integration)

Two of the four drivers listed in Chapter 2.1.2 can be addressed without actually performing stacking of active layers, namely heterogeneous integration and yield and cost improvement. To this end, so-called *interposer based* systems (also 2.5D-Integration) can be used. Here, multiple active dies are arranged next to each other (horizontally) and are vertically stacked on a larger interposer die using a Face-to-Face (F2F) approach (see Fig. 2.2a). With such a F2F orientation no TSVs have to be placed in the active dies but only in the interposer. This removes all impact of TSV

Tab. 2.1.: Comparison of stacking methods

|                       | D2D                            | D2W                                       | W2W                                  |

|-----------------------|--------------------------------|-------------------------------------------|--------------------------------------|

| Production throughput | low                            | medium                                    | high                                 |

| Test<br>approach      | KGD possible die level testing | KGD possible<br>die + wafer level testing | KGD not possible wafer level testing |

| Alignment results     | critical                       | critical                                  | good                                 |

| Wafer<br>handling     | manageable                     | manageable                                | delicate                             |

manufacturing for active silicon and vice versa. Also, no silicon real estate is lost due to TSV footprint or Keep-out-Zones (KoZs). Looking at the list of drivers again, the issues not always addressed with 2.5D designs are footprint and performance. When splitting an otherwise large die into smaller pieces to create a 2.5D design, footprint cannot be reduced due to the horizontal arrangement. Performance is also not increased in this case, since wire length is not reduced. Every inter-die signal has to travel through the interposer and therefore, compared to a large planar chip, the average length of global wires is even increased. However, such a large planar chip might not be feasible due to low yield and resulting high costs. Therefore, the interposer design rather competes with the SiP approach or even a multi-package alternative interconnected on PCB level. Compared to such alternatives, a TSV-based interposer design clearly offers higher performance.

With heterogeneous 2.5D designs the remaining aspects (footprint and performance) are also addressed since here, the reference is a multi-package configuration on a PCB (or a SiP) and not a single larger die.

Currently silicon is used as bulk material for the interposer even though there are no active components realized on this layer. However, the process flow is well mastered and therefore the obvious choice for integrating a Redistribution Layer (RDL). In the future, glass might be used as an alternative to save costs [52].

## 2.1.5 Commercially available 3D-ICs

At the time of this writing only few commercial TSV-based products had reached the market. This is assumed to be due to the fact that TSV production costs are still high and yield is assumed to be low. However, the semiconductor foundries usually do not share much information on actual quantities regarding these figures.

In Fig. 2.1 a timeline of already available products is given. The list of available products is dominated by two applications:

- Interposer based high-end FPGAs

- · Stacked DRAM

The objective of the interposer based systems is (as already discussed in 2.1.4) mainly to improve the overall yield for chips with large silicon area. Therefore, it is no surprise that the only commercial representatives are high-end FPGAs with a very large die area, namely Xilinx' UltraScale FPGAs.

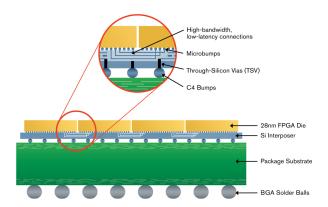

Xilinx 3D FPGAs are available since 2011 and use TSMC's Chip-on-Wafer-on-Substrate (CoWoS) platform [53], [54]. The first representative within this family was the Virtex-7 2000T FPGA made from four identical FPGA dies at the  $28\,\mathrm{nm}$  node and a silicon interposer at the  $68\,\mathrm{nm}$  node. Its structure is shown in Fig. 2.5. Roughly 10000 inter-die connections are used [55]. I/O connections are routed via TSVs to the package substrate. The TSVs are placed with a pitch of  $180\,\mu\mathrm{m}$  [56]. In 2012, Xilinx added the *Virtex-7 HT* family to their portfolio with some of its members including dedicated serial transceiver dies. This was advertised as the first *Heterogeneous 3D-IC* [57].

Fig. 2.5.: Interposer based FPGA design by Xilinx [55]

The remaining bulk of commercially available 3D-ICs is formed by stacked DRAM systems. In the realm of 3D DRAM different standards targeting three different application domains have been published: Mobile Memory, high-end server and datacenter memory and graphics memory. However, only for the latter two products can be purchased.

Currently products supporting the following memory standards are available:

**DDR4** is a conventional SDRAM standard, implemented also in a few 3D products. From an interface standpoint, such modules are not different compared to conventional DDR4 modules. The protocol as it is defined in the DDR4 standard

[58] is used for communication with the memory controller. The motivation behind such products is the denser package possible with stacking multiple DRAM dies. The technology was introduced by Samsung in 2014 with a 64 GB module. In 2014, a 128 GB module was announced by SK Hynix [59]. In 2015, Samsung also added a 128 GB module [60]. No information is publicly available regarding the underlying TSV technology like geometry, pitch and clocking.

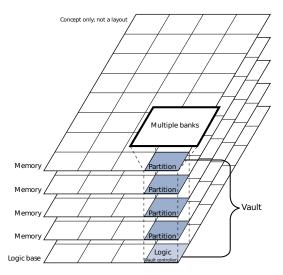

Hybrid Memory Cube (HMC) HMC is a high bandwidth memory standard for stacked DRAM. The first version (1.0) of the HMC standard was published in 2013 [61], later versions 2.0 (2014, [62]) and 2.1 (2015, [63]) were released. The standard is maintained by the HMC Consortium, which is backed by major semiconductor and memory vendors including Micron, ARM, Samsung, Altera, Xilinx. Fig. 2.6 shows the basic setup. An HMC chip stack consists of the controller logic, which always takes up the base layer. On top of the controller up to eight DRAM layers are stacked vertically and interconnected by TSVs. The individual DRAM layers are divided into 16 or 32 partitions (depending on the standard version). A so-called Vault is formed by interconnecting all partitions which are located at the same XY position but in different layers. Such a Vault is then controlled by the respective Vault Controller on the base layer. TSVs are fabricated with a pitch of 60 µm in the Micron module [64]. HMC is incompatible with existing DRAM memory standards like DDRx or LPDDR. A chip stack (also called *cube*) is interfaced with up to 4 links, each link comprising up to 16 differential serial lanes with a bandwidth of up to 30 Gbit/s per lane. Hence an aggregated (full-duplex) bandwidth of up to 480 GB/s is possible [63]. A packet based protocol is used on top of the serial links. With this protocol multiple cubes can be arranged in different topologies (described in the standard) and connected to one ore more processing cores. HMC is an off-chip memory system, and so far, the Micron cube is the only available memory module incorporating the standard on the memory side. However, multiple vendors have equipped their chips with the host interface in order to connect to an HMC.

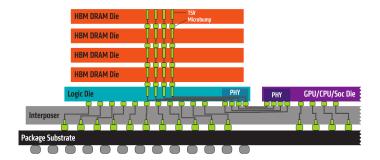

**High Bandwidth Memory (HBM)** is another standard for stacked DRAM, but which is targeting graphics applications. In contrast to HMC, it is not maintained by an industry consortium but by the independent JEDEC organization, which is also responsible for the conventional DDR1-5 standards. The standard was first published in 2013 and revised in 2015 [65]. The basic setup of an HBM system is shown in Fig. 2.7. In contrast to HMC the memory stack is included in a package together with the GPU. Both GPU and memory stacked are placed next to each other on a silicon interposer. On the host interface level, HBM implements a wide parallel interface consisting of 8 independent channels. An aggregated bandwidth (full-duplex) of 256 GB/s is provided [66]. HBM

is currently available in the AMD Fiji GPU [67] and the Nvidia Tesla P100 GPU [68].

The different stacked memory standards do not directly compete since they serve different target applications (server/supercomputer applications for HMC and GPU applications for HBM) [66]. Also a major difference between the two is that HMC uses a discrete package for the memory stack, whereas for HBM the memory is integrated in the SoC. With *Wide I/O* [69] another standard for stacked DRAM is available, which is, however, targeting mobile applications. No products have hit the market yet, though, since with advanced LPDDR standards the same bandwidth could be achieved at a much lower cost [14].

Note that also a multitude of non-TSV stacked memory solutions exist. Those are out of the scope of this work, however.

Fig. 2.6.: HMC die stack scheme from the HMC specification rev. 2.0 [62]. The base layer houses the control logic, and up to 8 DRAM layers are stacked on top of it.

**Fig. 2.7.:** HBM setup [67]. The DRAM stack is arranged next to a GPU on a silicon interposer. In the RAM stack the base layer houses the control logic. 4 or 8 DRAM layers are stacked on top of it (depending on the standard version).

# 2.2 TSV-based on-chip interconnect

The by far most promising interconnection technology for 3D-ICs is the TSV-based one. In both, the research community and industry, the vast majority of publications in the realm of 3D-ICs covers TSV-based systems.

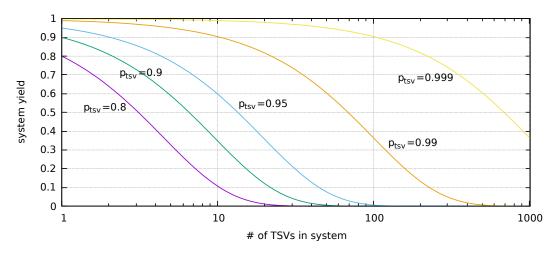

TSVs offer high throughput but are costly with regards to the following aspects:

- Area consumption: Despite being very short (compared to intra-layer interconnects) TSVs are wide (in the range of several (tens of  $\mu$ m) and thus consume a high amount of chip area. Additionally, most TSVs require surrounding Keep-out-Zones that further use up valuable silicon area.

- Yield drop: Even though the yield of a single TSV is high and close to 100%, when many TSVs are inserted in a system, the individual yield factors have to be multiplied, and the overall yield drops exponentially with the number of used TSVs.

- Manufacturing: Additional process steps have to be included when manufacturing TSVs (e.g. etching, filling and bonding).

The last one of the above points is mostly independent from the number of TSVs used in the system. The area consumption and yield drop, however, correlate with the number of used TSVs and are the reason why TSVs are a valuable resource that needs to be budgeted efficiently.

## 2.2.1 TSV Delay Model

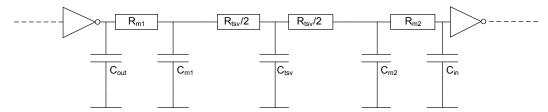

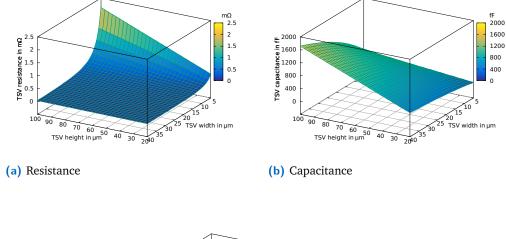

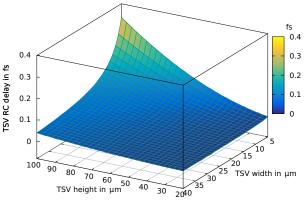

One objective of this work is to provide means to fully exploit TSV performance. To this end, relevant electrical parameters are studied in order to characterize TSVs from a more abstract viewpoint. Also, such models are needed to extract realistic parameter values which are then used in simulations and calculations on higher abstraction layers for calculating delay and power figures. To simulate the electric behavior with maximized accuracy so-called field solvers are required. Field solvers are software programs applying Finite Element Methods (FEMs) on user-entered geometric structures. However, entering the structure is a time-intensive task. This is why more compact models, so-called *lumped models*, are desired, which characterize TSV behavior by using an equivalent circuit network with a manageable number of electrical components like inductances, capacitances and resistances. The actual quantities for the model are then derived using closed-form expression based on geometrical and material parameters. Fig. 2.9 shows such a lumped model for characterizing a single TSV. Finally, a model can be verified for a set of input parameters by comparing the results to those of field solvers or measurement data with corresponding input data.

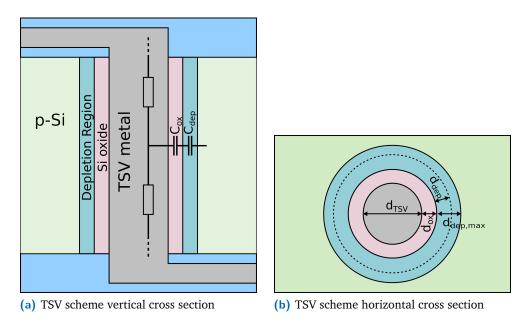

Several of such models and corresponding closed-form expressions have been published (see Tab. 2.2) in the recent years, with different levels of complexity, accuracy and set of input parameters and output values. Common to all of these models is that they consider at least in parts the geometric dimensions of a single TSV. Therefore, at first we have to understand that TSVs are in fact cylindrical structures, despite being often depicted with rectangle or cuboid like shapes in illustrations (Fig. 2.8 shows cross section views). Another property of TSV structures is that they form a Metal–Oxide–Semiconductor (MOS) setup with the surrounding bulk silicon and the Silicon dioxide (SiO<sub>2</sub>) as an insulator. Therefore, TSVs show behavior similar to MOS transistors.

**Fig. 2.8.:** TSV cross sections. The TSV forms a cylindrical MOS structure within the bulk silicon.

The first electrical model for TSV behavior was presented by Alam et al. in 2007 [70]. It does not yet use the term TSV but *Through-Si Via*. It is a very basic model relying solely on the standard formulas to calculate the resistance and capacitance of a cylindrical structure, also TSV inductance is neglected.

With respect to modeling the **resistance** we see two more steps of refinement. One is representing the geometric proportions more closely in the model. TSVs are strictly speaking not of pure cylindrical shape but resemble a tapered cylinder as a result of the etching process. This is accounted for in the model of [71] with an additional parameter for the *slope angle*. The other possible enhancement is considering the *Skin Effect*, which is obviously only relevant for higher frequencies. The impacts of the Skin Effect are included in [71], [72] and [73] by providing an additional formula for AC resistance.