#### Lehrstuhl für Realzeit-Computersysteme

# PC-basierte Systemarchitekturen für zeitkritische technische Prozesse

Gregor Burmberger

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. rer. nat. habil. Bernhard Wolf

Prüfer der Dissertation:

1. Univ.-Prof. Dr.-Ing. Georg Färber

2. Univ.-Prof. Dr.-Ing. Dr.-Ing. habil. Friedrich Schneider

Die Dissertation wurde am 17.01.2002 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 24.06.2002 angenommen.

Vorwort

#### Vorwort

Die vorliegende Dissertation entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl für Realzeit-Computersysteme der Technischen Universität München in den Teilprojekten Dreidimensionales Drucken von Bauteilen und Mikro-Stereolithografie des Forschungsverbundes Mikrosystemtechnik FORMIKROSYS II der Bayerischen Forschungsstiftung.

Herrn Prof. Dr.-Ing. Georg Färber gilt mein besonderer Dank für das in mich gesetzte Vertrauen. Die belebenden Diskussionen und seine wertvollen Ratschläge trugen wesentlich zum Gelingen dieser Arbeit bei. Herrn Prof. Dr.-Ing. Friedrich Schneider danke ich für sein Interesse an dieser Arbeit und die Übernahme des Zweitberichts.

Ganz herzlich bedanken möchte ich mich bei meinem Kollegen Robert Huber, der mir durch seine Fachkenntnisse ein geschätzter Diskussionspartner war. Die gemeinsame Zeit in unserem Büro werde ich vermissen. Für das kollegiale Arbeitsklima und zahlreiche interessante Gespräche danke ich den Mitarbeitern des Lehrstuhls. Besonders nennen möchte ich hier meine beiden Diplomanden Zoran Vujnovic und Raphael Neidinger, sowie Herrn Thomas Andreas, die wichtige Beiträge zur vorliegenden Arbeit geleistet haben.

Nicht zuletzt schulde ich großen Dank meiner Familie, im speziellen meiner Mutter, die mir das Studium ermöglicht hat, und meiner Lebensgefährtin Christina, die mir immer Beistand geleistet und mich in allen Phasen uneingeschränkt unterstützt hat.

München, im Januar 2002

## **Inhaltsverzeichnis**

| III |

|-----|

| V   |

| VII |

| IX  |

| XI  |

| 1   |

| 5   |

|     |

| 17  |

|     |

| 37  |

|     |

|     |

| 4.3 Verwendung von Realzeitbetriebssystemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 4.3.1 Realzeitbetriebssysteme für zeitkritische Prozesse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                        |

| 4.3.2 Grenzen der Realzeitbetriebssysteme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                        |

| 4.3.3 Kombination mit Ein-/Ausgabe-Komponente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                        |

| 4.4 Mehrprozessorsysteme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                        |

| 5 Hardwarebasierte Systemarchitekturen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                        |

| 5.1 Auslagerung zeitkritischer Prozesse auf zusätzliche Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                        |

| 5.1.1 Intelligente Controller-Komponente als eingebettetes System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                        |

| 5.1.2 Programmierbare Logik-Komponente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69                        |

| 5.1.3 Probleme bei der Nutzung von Zusatzhardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71                        |

| 5.2 Analyse der Grenzen der PC-Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                        |

| 5.2.1 Architekturbeschränkungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                        |

| 5.2.2 Grenzen des PCI-Busses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84                        |

| 5.3 Erweiterte Architekturkonzepte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |

| 5.3.1 Probleme und Verbesserungsansätze                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 88                        |

| 5.3.2 Neue Schnittstellen-Architekturen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94                        |

| 5.3.3 Verbesserte Software-Kommunikationsstrukturen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| 6 Anwendungsbeispiele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 99                        |

| <b>6 Anwendungsbeispiele</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99                        |

| 6.1 Druckkopfansteuerung eines 3D-Druckers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99<br>99                  |

| 6.1 Druckkopfansteuerung eines 3D-Druckers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99<br>99<br>102           |

| 6.1 Druckkopfansteuerung eines 3D-Druckers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99<br>99<br>102           |

| 6.1 Druckkopfansteuerung eines 3D-Druckers 6.1.1 Projektbeschreibung 6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen 6.1.3 Hardware- und Softwarekonzept                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99<br>102<br>105          |

| 6.1 Druckkopfansteuerung eines 3D-Druckers 6.1.1 Projektbeschreibung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99<br>102<br>105<br>109   |

| 6.1 Druckkopfansteuerung eines 3D-Druckers 6.1.1 Projektbeschreibung 6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen 6.1.3 Hardware- und Softwarekonzept 6.1.4 Realisierung 6.1.5 Verifikation und Ergebnisse 6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine 6.2.1 Projektbeschreibung                                                                                                                                                                                                                                                                                                     |                           |

| 6.1 Druckkopfansteuerung eines 3D-Druckers 6.1.1 Projektbeschreibung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

| 6.1 Druckkopfansteuerung eines 3D-Druckers 6.1.1 Projektbeschreibung 6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen 6.1.3 Hardware- und Softwarekonzept 6.1.4 Realisierung 6.1.5 Verifikation und Ergebnisse 6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine 6.2.1 Projektbeschreibung                                                                                                                                                                                                                                                                                                     | 99102105113116116         |

| <ul> <li>6.1 Druckkopfansteuerung eines 3D-Druckers</li> <li>6.1.1 Projektbeschreibung</li> <li>6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.1.3 Hardware- und Softwarekonzept</li> <li>6.1.4 Realisierung</li> <li>6.1.5 Verifikation und Ergebnisse</li> <li>6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine</li> <li>6.2.1 Projektbeschreibung</li> <li>6.2.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> </ul>                                                                                                                     | 99102105113116116         |

| <ul> <li>6.1 Druckkopfansteuerung eines 3D-Druckers</li> <li>6.1.1 Projektbeschreibung</li> <li>6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.1.3 Hardware- und Softwarekonzept</li> <li>6.1.4 Realisierung</li> <li>6.1.5 Verifikation und Ergebnisse</li> <li>6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine</li> <li>6.2.1 Projektbeschreibung</li> <li>6.2.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.2.3 Hardware- und Softwarekonzept</li> </ul>                                                                        | 99102105113116116120      |

| <ul> <li>6.1 Druckkopfansteuerung eines 3D-Druckers</li> <li>6.1.1 Projektbeschreibung</li> <li>6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.1.3 Hardware- und Softwarekonzept</li> <li>6.1.4 Realisierung</li> <li>6.1.5 Verifikation und Ergebnisse</li> <li>6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine</li> <li>6.2.1 Projektbeschreibung</li> <li>6.2.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.2.3 Hardware- und Softwarekonzept</li> <li>6.2.4 Realisierung</li> </ul>                                            | 9999102105113116120122125 |

| <ul> <li>6.1 Druckkopfansteuerung eines 3D-Druckers</li> <li>6.1.1 Projektbeschreibung</li> <li>6.1.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.1.3 Hardware- und Softwarekonzept</li> <li>6.1.4 Realisierung</li> <li>6.1.5 Verifikation und Ergebnisse</li> <li>6.2 Steuerung der X-Y-Scanner einer Mikro-Stereolithografiemaschine</li> <li>6.2.1 Projektbeschreibung</li> <li>6.2.2 Analyse der zeitkritischen Prozesse und Aufstellen der Realzeit-Anforderungen</li> <li>6.2.3 Hardware- und Softwarekonzept</li> <li>6.2.4 Realisierung</li> <li>6.2.5 Verifikation und Ergebnisse</li> </ul> | 9999102105113116120125127 |

## Abbildungsverzeichnis

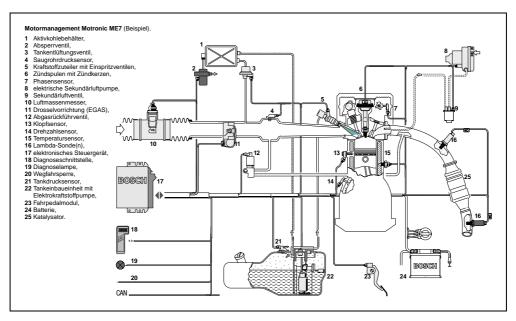

| Bild 2.1  | Elektronisches Motormanagement Motronic ME7 (Bosch)                                          | 7    |

|-----------|----------------------------------------------------------------------------------------------|------|

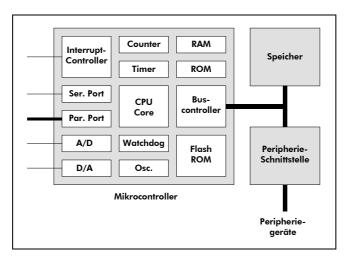

| Bild 2.2  | Struktur eines eingebetteten Realzeitsystems                                                 | 8    |

| Bild 2.3  | Schichtenmodell eines Realzeitbetriebssystems                                                | 9    |

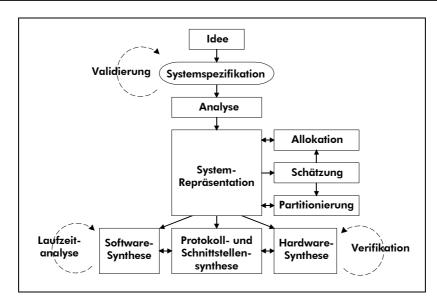

| Bild 2.4  | Entwurfsprozess für eingebettete Realzeitsysteme                                             | . 11 |

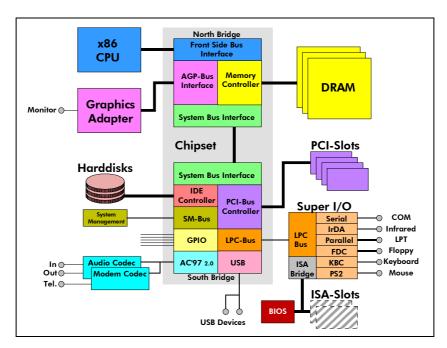

| Bild 2.5  | Hardwarekomponenten eines Standard-PCs                                                       | 12   |

| Bild 2.6  | Struktur des Dreams Subsystem                                                                | 14   |

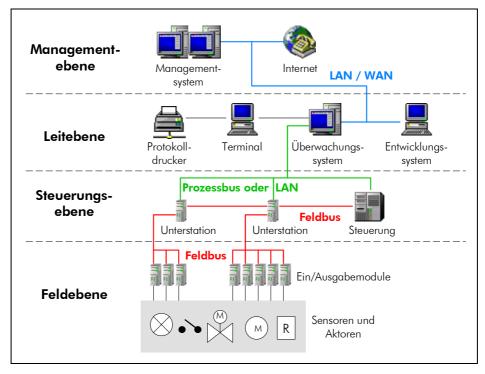

| Bild 3.1  | Ebenen der Prozessautomatisierung                                                            | 17   |

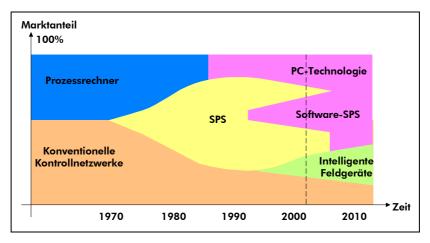

|           | Die Zukunft der SPS                                                                          |      |

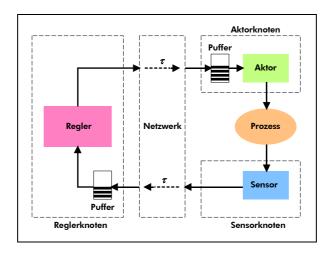

| Bild 3.3  | Digitaler Regelkreis mit verteilten Sensoren/Aktoren und Zwischenspeichern                   | 23   |

|           | Klassifizierung der Systemarchitekturen                                                      |      |

| Bild 3.5  | Zusammenhang von Reaktionszeit und Kosten der verschiedenen Systemarchitekturen .            | 36   |

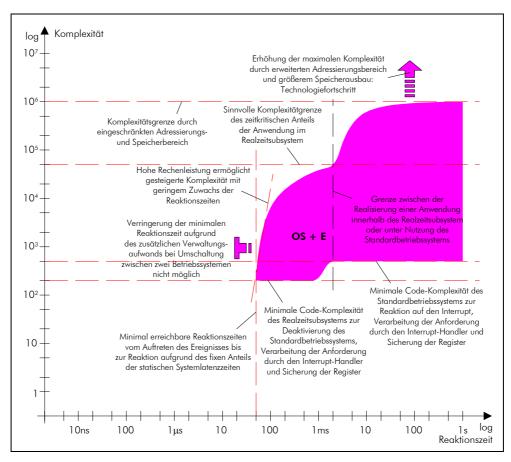

| Bild 4.1  | Parameterbereich der Standard-Softwareimplementierungen (OS)                                 | 38   |

|           | Regelung eines schwebenden Körpers                                                           |      |

|           | Parameterbereich der Realzeiterweiterungen (OS + E)                                          |      |

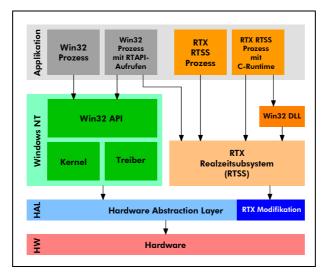

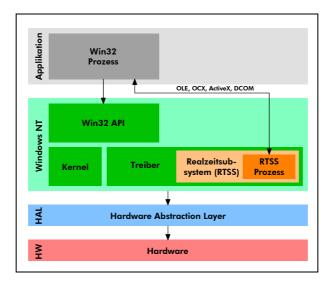

|           | Architektur von RTX                                                                          |      |

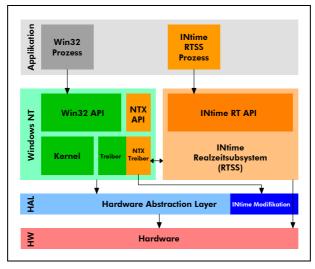

|           | Architektur von INtime                                                                       |      |

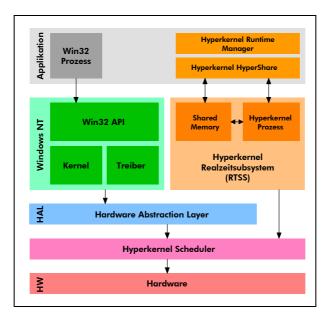

|           | Architektur von HyperKernel                                                                  |      |

|           | Realzeitsubsystem als Treiber im Kernelmode                                                  |      |

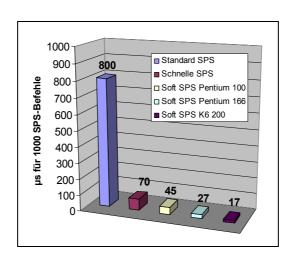

|           | Vergleich Hardware-SPS ⇔ Software-SPS mit Realzeiterweiterung                                |      |

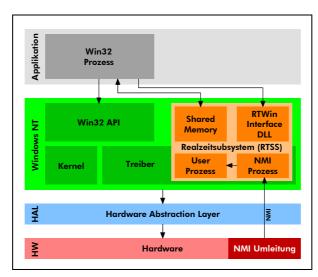

|           | Struktur des RTWin Toolkits                                                                  |      |

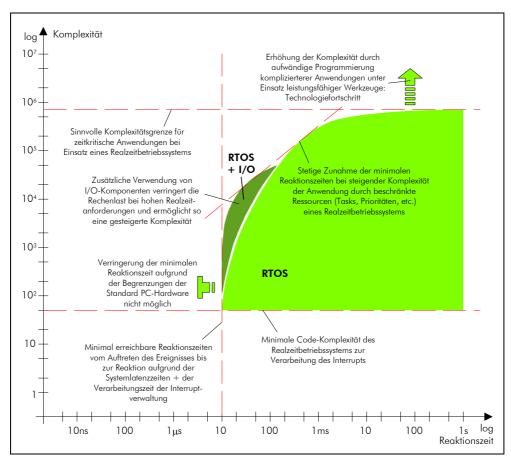

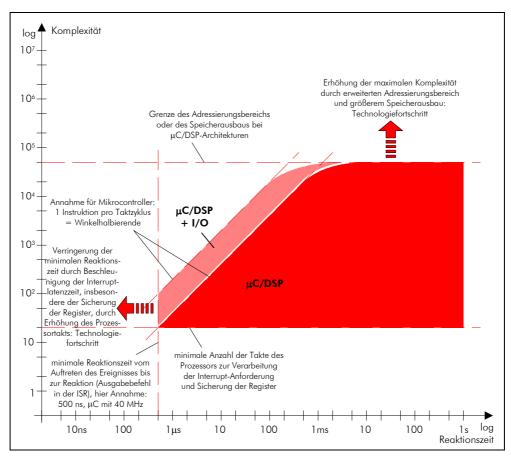

|           | Parameterbereich der Realzeitbetriebssysteme (RTOS, RTOS + I/O)                              |      |

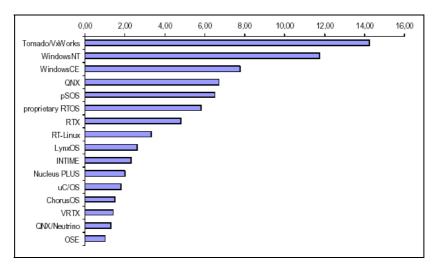

|           | l Prozentualer Anteil der Betriebssysteme und -Erweiterungen                                 |      |

|           | Parameterbereich der intelligenten Controller-Komponente ( $\mu$ C/DSP, $\mu$ C/DSP + I/O) . |      |

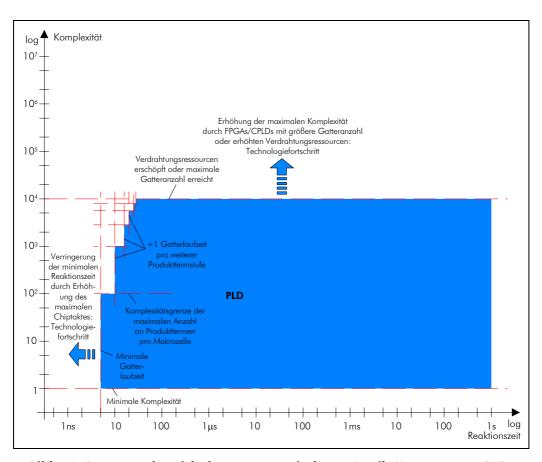

|           | Parameterbereich der programmierbaren Logik-Komponente (PLD)                                 |      |

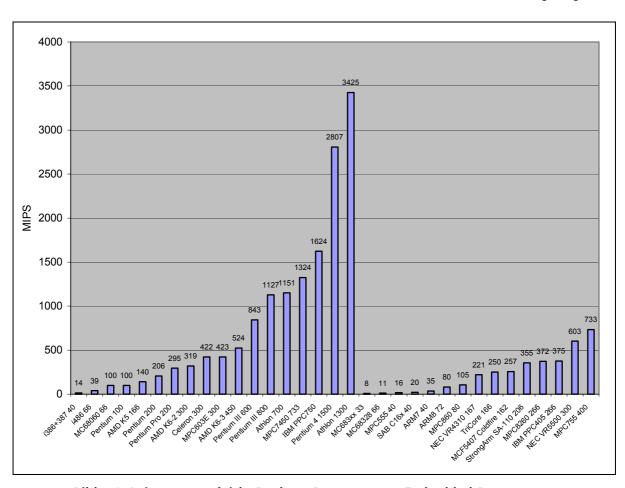

|           | Leistungsvergleich: Desktop-Prozessoren – Embedded-Prozessoren                               |      |

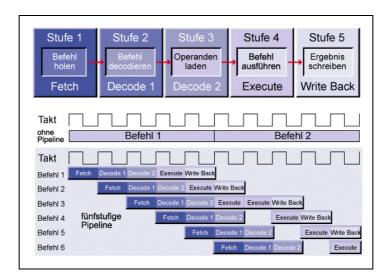

|           | Beispiel einer fünfstufigen Pipeline                                                         |      |

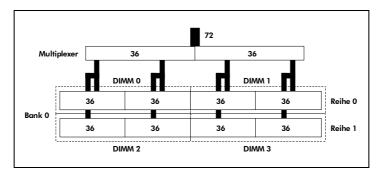

|           | 4-fach Interleaving mit 72-bit ECC-Speichermodulen                                           |      |

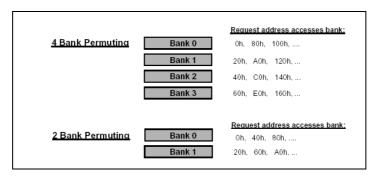

| Bild 5.6  | Adress-Bit Permutation.                                                                      | 81   |

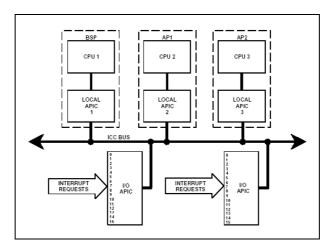

| Bild 5.7  | APIC – I/O-APIC Konfiguration                                                                | 82   |

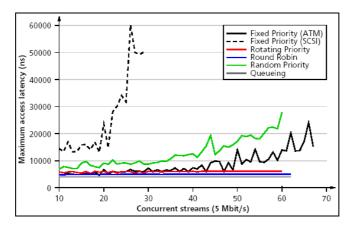

| Bild 5.8  | Latenzzeiten verschiedener PCI-Bus-Arbitrierungsalgorithmen                                  | 86   |

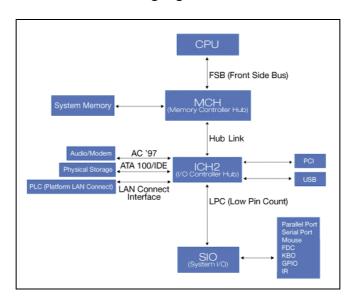

| Bild 5.9  | Moderne PC-Systemarchitektur mit Intel Hub-Link                                              | 89   |

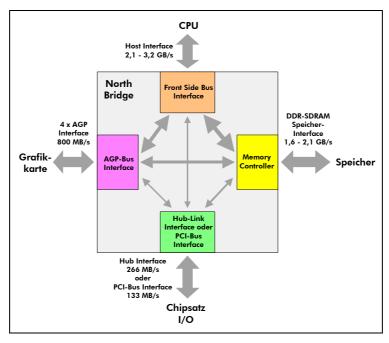

| Bild 5.10 | OInterne Busse und Datenpfade der North Bridge                                               | 91   |

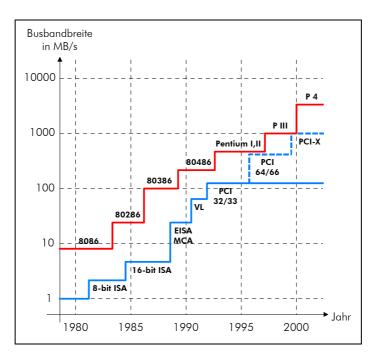

| Bild 5.11 | I Entwicklung der Busbandbreiten von Prozessoren und I/O-Schnittstellen                      | 93   |

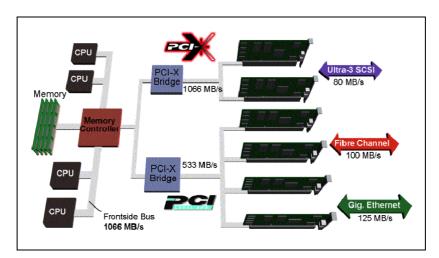

|           | 2 Erweiterung des PC-Systems mit PCI-X                                                       |      |

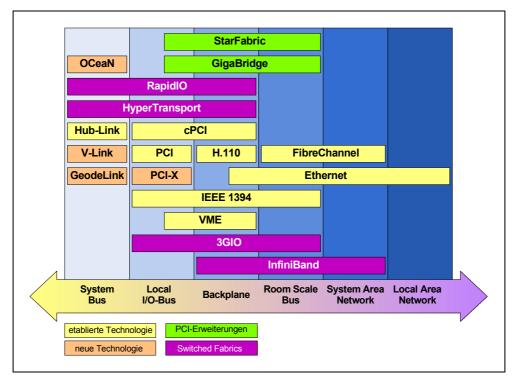

|           | B Einsatzgebiete der Schnittstellen-Architekturen                                            |      |

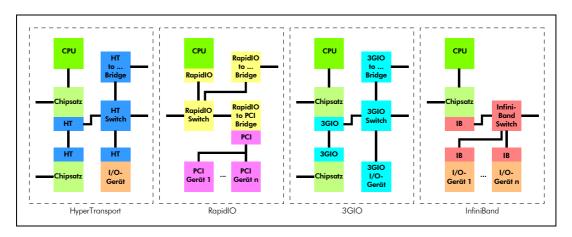

|           | 4 Beispiele zur Systemanordnung der Schnittstellen-Architekturen                             |      |

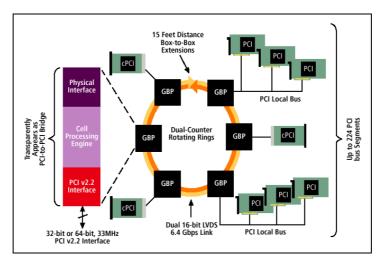

|           | 5 Systemstruktur der GigaBridge-Architektur                                                  |      |

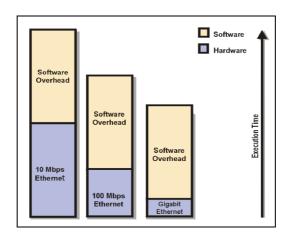

|           | 6 Software- und Hardware-Ausführungszeiten der Ethernet-Übertragung                          |      |

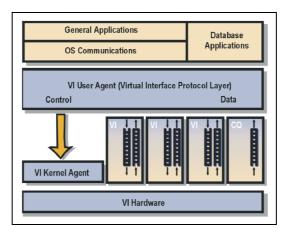

|           | 7 Kommunikationsstruktur der Virtual Interface Architecture                                  |      |

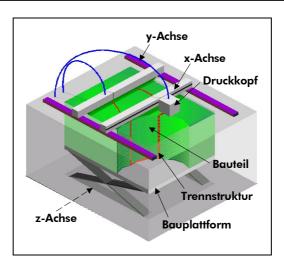

|           | Schematischer Aufbau eines 3D-Druckers                                                       |      |

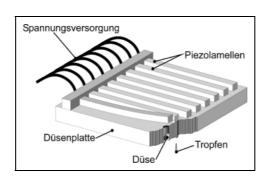

| Bild 6.2  | Konstruktion eines Mehrdüsen-Druckkopfs                                                      | 100  |

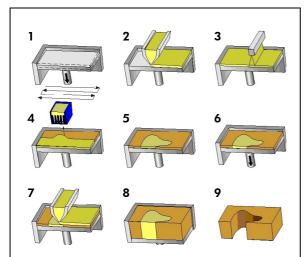

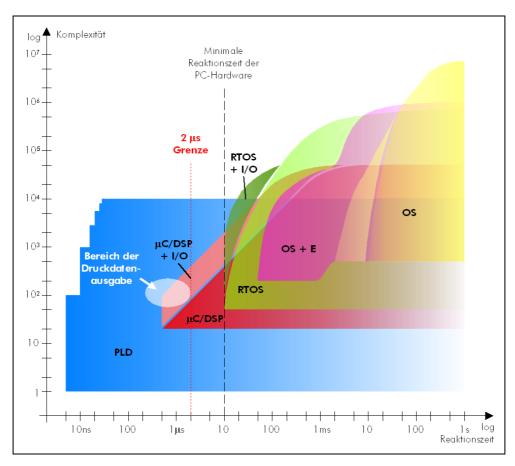

| Bild 6.3  | Sanddruck- und Wachsdruckprozess                                              | 101 |

|-----------|-------------------------------------------------------------------------------|-----|

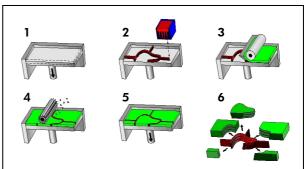

| Bild 6.4  | Zustandsdiagramm der Prozessphasen (3DD)                                      | 104 |

|           | Auswahl der passenden Systemarchitektur (3DD)                                 |     |

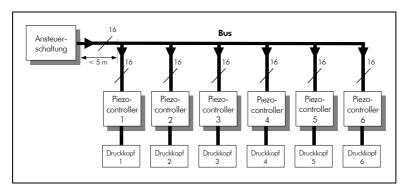

| Bild 6.6  | Aufteilung in Ansteuerschaltung und 6 Piezocontroller                         | 106 |

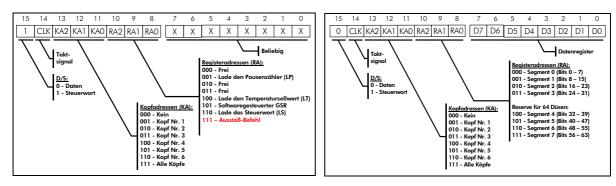

| Bild 6.7  | Busprotokoll bei Übertragung von Steuerdaten und Druckdaten                   | 106 |

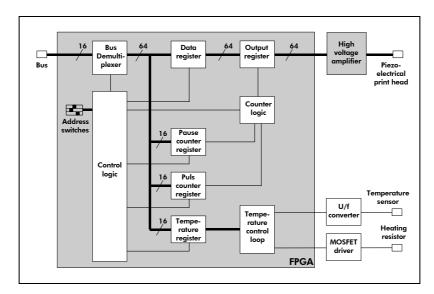

| Bild 6.8  | Blockschaltbild des Piezocontrollers                                          | 107 |

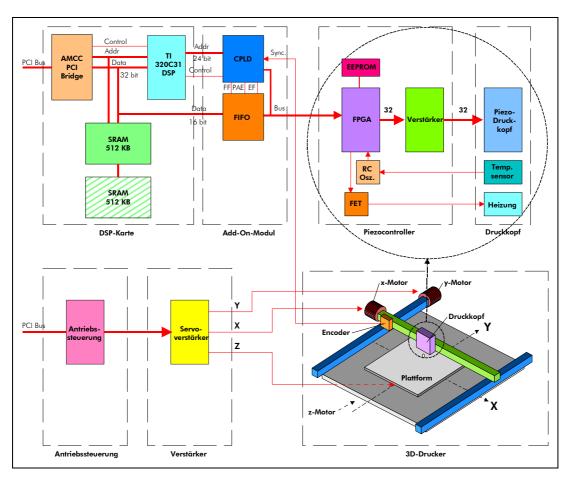

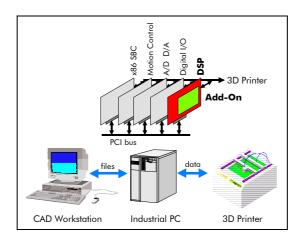

| Bild 6.9  | Systemdiagramm und Datenfluss des 3D-Druckers                                 | 107 |

| Bild 6.10 | Schematischer Aufbau der 3D-Drucker-Hardware                                  | 109 |

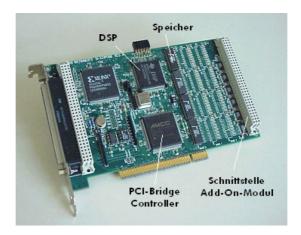

| Bild 6.11 | DSP-Karte                                                                     | 110 |

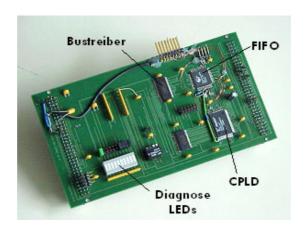

| Bild 6.12 | Add-On-Modul                                                                  | 110 |

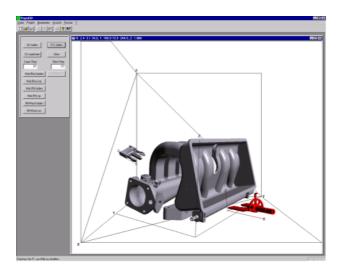

| Bild 6.13 | Screenshot der Steuerungsapplikation (3DD)                                    | 111 |

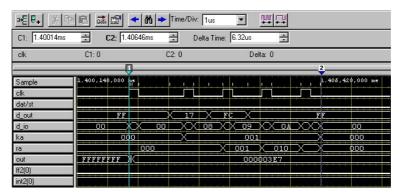

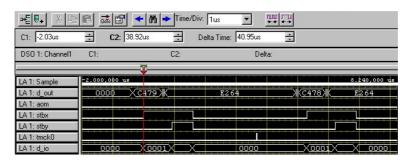

| Bild 6.14 | Übertragung einer Druckspalte (4 Bytes)                                       | 114 |

| Bild 6.15 | Datenübertragung für 5 kHz Ausstoß-Frequenz                                   | 114 |

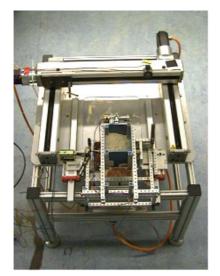

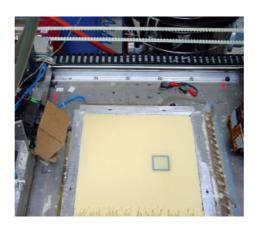

| Bild 6.16 | Prototypen des 3D-Druckers für den Sanddruckprozess                           | 115 |

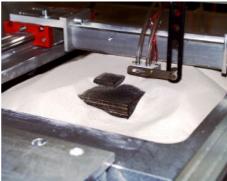

| Bild 6.17 | Musterstücke (Sanddruckprozess)                                               | 115 |

| Bild 6.18 | Prototyp des 3D-Druckers für den Wachsdruckprozess                            | 116 |

| Bild 6.19 | Testdruck und Musterstück für Separation (Wachsdruckprozess)                  | 116 |

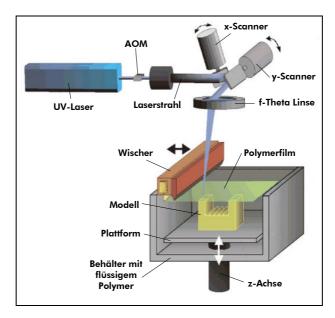

| Bild 6.20 | Stereolithografie-Prinzip                                                     | 117 |

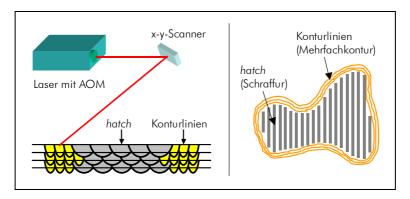

| Bild 6.21 | Belichtung von Konturlinien und Hatch                                         | 117 |

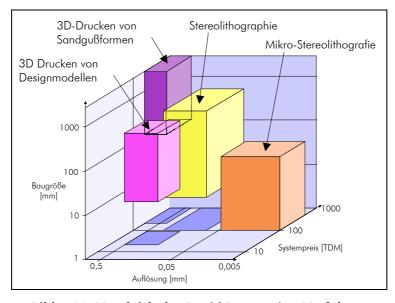

| Bild 6.22 | Vergleich der Rapid Prototyping-Verfahren                                     | 119 |

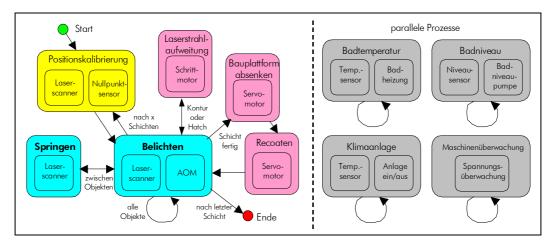

|           | Zustandsdiagramm der Prozessphasen (MSTL)                                     |     |

| Bild 6.24 | Auswahl der passenden Systemarchitektur (MSTL)                                | 123 |

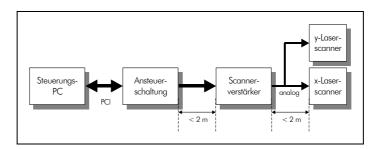

| Bild 6.25 | Datenübertragung der Belichtungssteuerung vom Steuerungs-PC zum Laserscanner. | 123 |

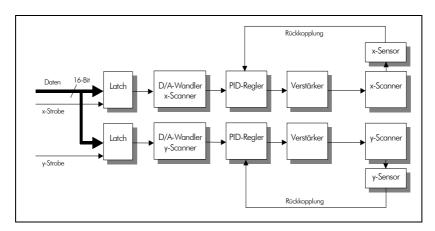

|           | Blockschaltbild des Scannerverstärkers                                        |     |

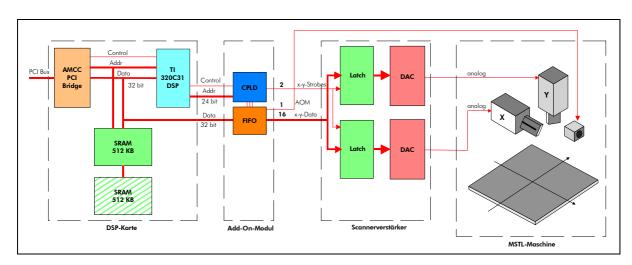

| Bild 6.27 | Systemdiagramm und Datenfluss der MSTL-Maschine                               | 124 |

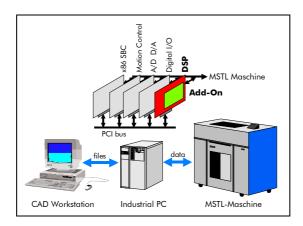

|           | Schematischer Aufbau der MSTL-Maschine                                        |     |

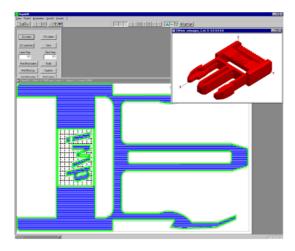

| Bild 6.29 | Screenshot der Steuerungsapplikation (MSTL)                                   | 126 |

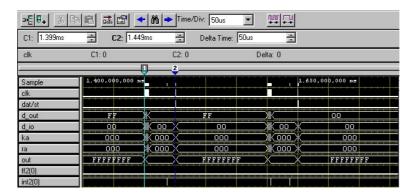

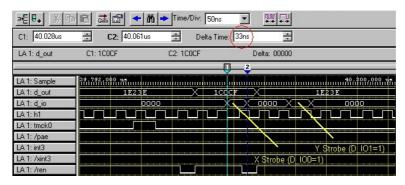

| Bild 6.30 | Timing des Datenbusses und der Strobe-Signale (ISR)                           |     |

| Bild 6.31 | Timing des Datenbusses und der Strobe-Signale (CPLD)                          | 128 |

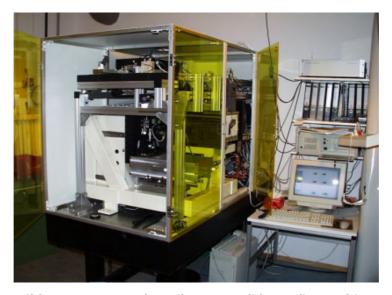

| Bild 6.32 | Prototyp der Mikro-Stereolithografiemaschine                                  | 129 |

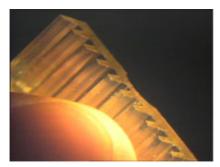

| Bild 6.33 | Ansaugkrümmer eines PKW-Motors und Struktur zum Einbetten kleiner Teile       | 130 |

| Rild 6 34 | Musterstücke: Faserkonnler, Turhine und Schachturm                            | 130 |

## **Tabellenverzeichnis**

| Tabelle 3.1 | Software-SPSen verschiedener Hersteller                                    | . 22 |

|-------------|----------------------------------------------------------------------------|------|

| Tabelle 3.2 | Ablauf bei Auftreten eines Interrupts                                      | . 30 |

| Tabelle 3.3 | Minimale Reaktionszeiten in Abhängigkeit von der Komplexität der Anwendung | . 35 |

| Tabelle 4.1 | Prioritätsspektrum von Windows NT                                          | . 40 |

| Tabelle 4.2 | Interrupt-Ebenen von Windows NT                                            | . 42 |

| Tabelle 4.3 | Optimierungsmethoden bei Festplattenzugriffen                              | . 43 |

| Tabelle 4.4 | Vergleich der verschiedenen Realzeiterweiterungen                          | . 55 |

| Tabelle 4.5 | Vergleich von Realzeitbetriebssystemen                                     | . 57 |

| Tabelle 4.6 | UART-Bausteine und -Implementierungen                                      | . 60 |

|             | Verhältnis der Ausführungszeiten für unterschiedliche Operationen          |      |

| Tabelle 5.2 | Datenübertragungsraten mit Write Combining und PCI Posting                 | . 75 |

|             | Fehlerquoten und Strafzeiten der Architekturmerkmale                       |      |

|             | Puffergrößen in Chipsätzen verschiedener Hersteller                        |      |

|             | Datenraten der Komponenten in der South Bridge                             |      |

|             | Auffrischungsintervalle gängiger Speichertechnologien                      |      |

|             | Interrupt-Sequenzen des APIC-Busses                                        |      |

|             | Einfluss des Latency Timers auf Bandbreite und Latenzzeit des PCI-Busses   |      |

| Tabelle 5.9 | Übertragungsraten verschiedener PCI-Hostcontroller (in [MB/s])             | . 87 |

|             | ) Übertragungsraten des Front Side Bus                                     |      |

|             | Bussysteme für Chipsatz-Kommunikation                                      |      |

|             | Paten- und Taktraten unterschiedlicher Speichertechnologien                |      |

|             | B Vergleich zwischen PCI und PCI-X                                         |      |

|             | Eigenschaften der neuen Schnittstellen-Architekturen                       |      |

|             | Ausführungszeiten wichtiger Funktionen                                     |      |

|             | Speicherbedarf von Kernel und Anwendung                                    |      |

| Tabelle 6.3 | Herausragende Eigenschaften der projektierten MSTL-Maschine                | 119  |

## Zusammenfassung

Seit einigen Jahren dringt der Personal Computer, ausgehend von seinem ursprünglichen Einsatzgebiet im Büro, verstärkt in den Bereich der Automatisierungstechnik vor. Steuerungssysteme für technische Prozesse sind nicht mehr ausschließlich die Domäne speicherprogrammierbarer Steuerungen und eingebetteter Systeme. Das PC-basierte System etabliert sich zunehmend in der Automatisierung der industriellen Produktion. Die Gründe hierfür liegen vor allem in der schnellen Entwicklung der Informationstechnologie. Die Vorteile für den Anwender sind hohe Verfügbarkeit, Wirtschaftlichkeit, Kommunikationsfähigkeit, Modularität, Systemoffenheit und Flexibilität, sowie hohe Leistungsfähigkeit zur Realisierung komplexer Steuerungsalgorithmen für anspruchsvolle Anwendungen. Durch die Verwendung der PC-Softwarearchitektur können Applikationen einfacher realisiert und neue Aufgaben schneller verwirklicht werden. Standardisierte Kommunikationsmethoden machen Produktionsdaten unternehmensweit verfügbar und schlagen so die Brücke zu integrierten Business-Plattformen wie z.B. SAP. Die Nutzung der modularen PC-Hardwarearchitektur mit bewährten Komponenten verschiedener Hersteller ermöglicht eine konsequente Verlagerung des Aufwands von der Systemauswahl hin zur Anwendungsentwicklung und erleichtert wesentlich die Integration in vorhandene Systeme. Der größte Nachteil der Systeme auf Basis von Standard-Soft- und Hardware, ist allerdings die ungenügende Realzeitfähigkeit. Firmen und Forschungsgruppen haben zwar eine Vielzahl von unterschiedlichsten Methoden und Lösungen entwickelt, die Qualität dieser Systeme ist aber sehr heterogen und ihre technologischen Grenzen und optimalen Anwendungsgebiete sind oft ungeklärt.

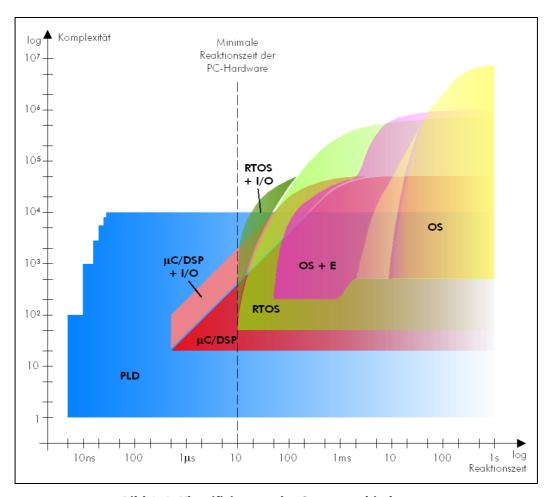

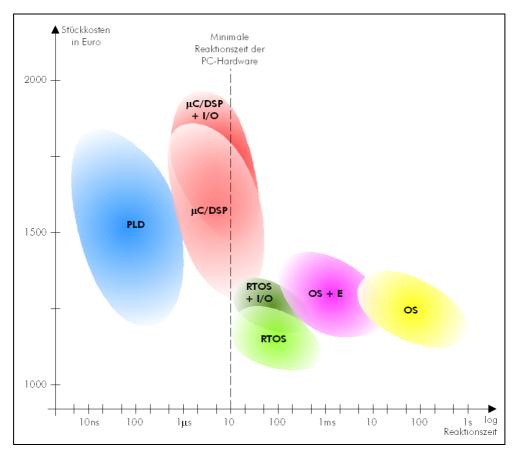

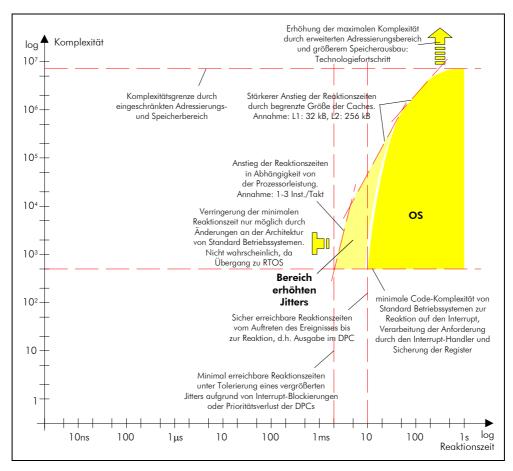

Die vorliegende Arbeit schließt diese Lücke durch die Schaffung einer Klassifizierung der Systemarchitekturen zur Realisierung von PC-basierten Steuerungssystemen für zeitkritische technische Prozesse. Mit dieser Klassifizierung ist man in der Lage, direkt nach dem Aufstellen der Realzeitbedingungen einer zu realisierenden Anwendung, schnell und unkompliziert einen passenden Lösungsansatz auszuwählen und sich auf die Implementierung zu konzentrieren. Die Unterteilung der Systemarchitekturen erfolgt in die zwei Hauptklassen Softwarebasierte Systemarchitekturen und Hardwarebasierte Systemarchitekturen mit insgesamt fünf Unterklassen. Zwei weitere nützliche Kombinationsmöglichkeiten entstehen durch Hinzufügen einer Ein/Ausgabe-Komponente ohne Eigenintelligenz. Auf der Basis von nur sieben Systemarchitekturen können, durch umsichtige Auswahl von Komponenten oder durch gezieltes Hinzufügen von Software- oder Hardwareerweiterungen, PCbasierte Steuerungssysteme für zeitliche Anforderungen vom Millisekunden- bis Sub-Mikrosekundenbereich konzipiert werden. Die weiteren Kapitel der Arbeit erläutern die spezifischen Eigenschaften der Systemarchitekturen. Grenzen, Probleme und geeignete Einsatzgebiete werden dabei einer gründlichen Analyse unterzogen. Erweiterte Architekturkonzepte mit Vorschlägen für Verbesserungen sowie neue Schnittstellenarchitekturen und Software-Kommunikationsstrukturen geben einen Ausblick auf die zukünftige Entwicklung. Zwei Anwendungsbeispiele aus der industriellen Praxis, die Entwicklung einer Druckkopfansteuerung eines 3D-Druckers und die Entwicklung einer Scannersteuerung einer Mikro-Stereolithografiemaschine, dienen zur Verifikation der erarbeiteten Klassifizierung. Die Ergebnisse dieser Arbeit können als Grundlage für den automatischen Systementwurf verwendet werden.

## 1 Einleitung

#### Der Siegeszug des Personal Computers

Im Privatbereich sowie in der Bürowelt ist der Siegeszug des *Personal Computers* ungebrochen. Auch aus der Management- und Leitebene in der Automatisierungstechnik ist der PC heute nicht mehr wegzudenken. Der PC hat sich auf breiter Basis etabliert. Nach dem Motto "schneller und billiger" werden Hard- und Softwarekomponenten immer leistungsfähiger und gleichzeitig kostengünstiger. Einleuchtend, dass von dieser Entwicklung auch die Industrie profitieren will, um Kosten zu reduzieren und die Produktivität zu steigern. Seit geraumer Zeit sind bestimmte Aufgaben fest in der Hand von PC-basierten Systemen. Mit Anwendungen auf Standardbetriebssystemen wie Windows oder Linux werden Datenbanken für Rezepturen und Maschineneinstelldaten verwaltet und Informationen aufbereitet und visualisiert.

Inzwischen machen sich Hersteller und Anwender Gedanken darüber, wie man weitere Aufgaben in den PC verlagern kann. In jüngster Zeit kommen mehr und mehr PC-basierte Systeme für unterschiedlichste Anwendungen auf den Markt, die kostengünstigere Steuerungssysteme auf nur einer Hardwarebasis versprechen. Tatsache ist, dass sich Aufgaben wie Steuern, Visualisieren, Datenverarbeitung und Kommunikation sowohl mit klassischen Systemen (SPS, eingebettete Systeme) als auch mit reinen PC-basierten Systemen lösen lassen. Was letztlich sinnvoll ist, hängt jedoch von vielen Faktoren ab und ist für jedes Projekt individuell zu betrachten. So können neben Rechenleistung auch die Vorkenntnisse und Vorlieben des Anwenders eine große Rolle spielen. Entscheidend ist insbesondere das Attribut Realzeitfähigkeit – eine Eigenschaft, die man bisher eher weniger mit einem PC in Verbindung gebracht hat.

#### Realzeitfähigkeit von Systemen

Unter Realzeitfähigkeit versteht man den Betrieb eines Rechnersystems in einer Weise, dass Programme zur Verarbeitung anfallender Daten ständig betriebsbereit und Ergebnisse innerhalb einer vorgegebenen Zeit verfügbar sind. "Harte" Realzeit bedeutet in diesem Sinn, dass ein System auf äußere Ereignisse in 100 % der Fälle im vorgegebenen Zeitfenster reagiert. Wenn dagegen die vorgegebenen Reaktionszeiten in Einzelfällen auch überschritten werden dürfen, spricht man von "weicher" Realzeit.

Klassische Steuerungssysteme mit ihren Realzeitbetriebssystemen sind für den rauen Industrieeinsatz konzipiert worden. Sie sind und bleiben daher erste Wahl bei allen zeitkritischen Steuerungsaufgaben in Verbindungen mit höchsten Sicherheitsansprüchen oder bei einfachen, kleinen Systemen, bei denen ein PC-basiertes System schlicht und einfach "eine Nummer zu groß" wäre. Sind neben dem eigentlichen Steuerungsprozess auch weitere Aufgaben, wie beispielsweise Datenverarbeitung, Vernetzung oder Visualisierung gefordert, kommt ein PC-basiertes System in Frage. Das gilt in besonderem Maße, wenn bereits ein (industrietauglicher) PC vorhanden ist und existierende Software weiter genutzt werden soll und kann. Die Standardbetriebssysteme Windows und Linux sind zwar für

sich genommen keine (harten) Realzeitbetriebssysteme, trotzdem erreicht man mit ihnen ausreichend schnelle Reaktionszeiten für den "weichen" Realzeitbetrieb. In Verbindung mit geeigneten Software- und Hardwareerweiterungen können sie sogar zur Realisierung von zeitkritischen "harten" Steuerungssystemen eingesetzt werden. Je nach Aufwand lassen sich so unterschiedliche Zeitanforderungen einhalten. Durch die weitgehende Beibehaltung von Standard-Soft- und -hardware und die damit einhergehende Kompatibilität kann sich das *PC-basierte Realzeitsystem* eventuell als zukünftiger Standard für die Steuerung von zeitkritischen technischen Prozessen durchsetzen.

#### Gestiegene Ansprüche

Die Ansprüche an Soft- und Hardware zur Steuerung von technischen Prozessen steigen ständig. Kunden fordern Systeme, die folgende Eigenschaften erfüllen:

- **Höhere Rechenleistung**, z.B. zur Realisierung von komplexen Steuerungsaufgaben und Berechnungsalgorithmen.

- **Mehr Speicherkapazität**, z.B. zur Datenerfassung von Signalen für die spätere Auswertung, oder bei Einsatz von ressourcenintensiven Programmiersprachen (Java).

- **Geringere Kosten**, z.B. für den ökonomischen Einsatz von vielen Systemen bei großen Industrieanlagen.

- Kleinere Ausmaße, z.B. für den Einsatz in mobilen Systemen im Kfz-Bereich.

- Vernetzbarkeit, z.B. für Ferndiagnose und Fernwartung, sowie zur Weiterleitung von Produktionsdaten (Intra-/Internet).

- Modularisierbarkeit, z.B. zur vereinfachten Rekonfiguration bei wechselnden Einsatzarten

- **Verwendung von (Quasi-)Standards**, z.B. aus Kompatibilitätsgründen und wegen der möglichen (Wieder-)Verwendung von bereits vorhandenen Softwaremodulen.

- **Einfache Wartbarkeit**, z.B. für den Ersatz von teuren Technikern "vor Ort" durch Fernwartung.

- **Verringerte Entwicklungskosten**, z.B. für den Einsatz in neuen kostensensitiven Anwendungsgebieten.

- Grafische Visualisierung, z.B. für eine anwenderfreundliche Mensch-Maschine-Schnittstelle.

Diese Eigenschaften erfüllen klassische Realzeitsysteme nur teilweise. Gerade die stetig steigende Leistungsfähigkeit der PC-basierten Systeme lässt klassische Systeme weiter ins Hintertreffen geraten. Die Vernetzung ist durch die zunehmende Verbreitung des Internets zu einer unentbehrlichen Eigenschaft von Steuerungssystemen geworden. Aktuelle Daten aus der Produktion werden in Business-Plattform-Systeme, z.B. SAP, eingespeist und sind unternehmensweit abrufbar. Die Controllingabteilungen haben somit eine aktuelle Datenbasis als Grundlage für ihre Analysen. Die Vernetzung ermöglicht auch die Ferndiagnose und Fernwartung von Steuerungssystemen, die bei entfernten Kunden installiert wurden. Kostenintensive Reisen von Technikern können verkürzt oder ganz eingespart werden. Auch die grafische Visualisierung der gesteuerten technischen Prozesse wird immer wichtiger oder ist gänzlich unverzichtbar. So ist z.B. der Teach-In-Prozess¹ bei Industrie-Robotern ohne grafische Benutzerführung schwerlich vorstellbar. Hier wurden bisher komplexe klassische Systeme mit proprietärer Visualisierung eingesetzt. Die Entwicklungskosten, speziell für die aufwändige Programmierung der grafischen Oberfläche waren entsprechend hoch. Die Ver-

\_

$<sup>^{1}</sup>$  Zum Beispiel Führung des Roboterarms zu Schweißpunkt-Koordinaten durch einen Produktionstechniker.

wendung eingeführter grafischer Benutzerschnittstellen, wie sie in Standardbetriebssystemen integriert sind, verringert die Entwicklungskosten und erhöht die Akzeptanz des Anwenders. Zu lösen ist jetzt noch das Problem der Realzeitfähigkeit.

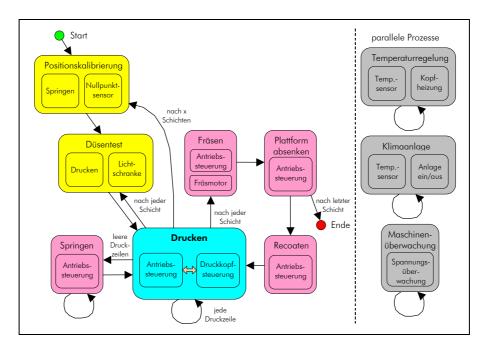

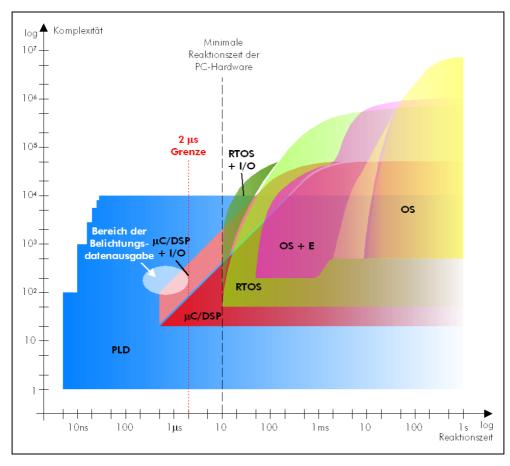

Für Steuerungssysteme mit weichen Realzeitanforderungen ist dies einfach zu realisieren. Bei Reaktionszeiten im zehn bis hundert Millisekunden-Bereich kann ohne weiteres ein Standard-PC mit einem beliebigen Standardbetriebssystem verwendet werden. Für erhöhte Anforderungen stehen Software-Erweiterungen oder Realzeitbetriebssysteme zur Verfügung. Die untere Grenze der Reaktionszeit der PC-Hardware ist bei ca. 2  $\mu$ s erreicht. Eine Unterschreitung dieser Zeit ist aufwändig aber dennoch durch Hardware-Erweiterungen möglich. Hierbei ist jedoch anzumerken, dass die überwiegende Zahl von technischen Prozessen keine solchen extremen Realzeitanforderungen stellt

#### Ziele dieser Arbeit

Die unüberschaubare Vielfalt und Menge der verschiedenen Lösungen und Erweiterungen macht die Auswahl einer geeigneten Methode zur Lösung einer gestellten Steuerungsaufgabe sehr schwierig und zeitaufwändig. Ein Ziel dieser Arbeit war es, die verschiedenen PC-basierten Lösungsmöglichkeiten aufzuzeigen, in wenige Klassen von Systemarchitekturen zu gruppieren und diese hinsichtlich der Einhaltung von Realzeitkriterien zu analysieren. Weiterhin waren die spezifischen Grenzen der software- und hardwarebasierten Architekturen zu ermitteln. Unter Einbeziehung der gestiegenen Ansprüche an Steuerungssysteme für zeitkritische technische Prozesse und des Fortschritts der PC-Technologie, wurde mit der vorliegenden Arbeit eine Entscheidungsgrundlage in Form einer Klassifizierung der Lösungsmethoden in nur fünf grundlegende Systemarchitekturen geschaffen. Zwei weitere Kombinationen vervollständigen die Gruppierung. Jede erhältliche PC-basierte Systemarchitektur lässt sich so in eine der 5 + 2 Klassen einteilen. Die Realzeitfähigkeiten der Klassen wurden verifiziert, die praktische Relevanz zeigen zwei Anwendungsbeispiele. Erweiterte Architekturkonzepte zeigen neue Lösungsansätze auf. In dem geschaffenen Klassifizierungs-Diagramm kann nun, nach Analyse der Realzeitanforderungen einer vorgegebenen Steuerungsaufgabe, d.h. nach Ermittlung der minimalen Reaktionszeit und maximalen Komplexität, sehr schnell eine geeignete Systemarchitektur gefunden werden. Alle Methoden, deren minimale Reaktionszeiten über den ermittelten Reaktionszeiten liegen, scheiden von vorneherein aus. Eine zeit- und kostenaufwändige Try-and-Error-Phase wird vermieden. Die Klassifizierungsergebnisse bilden somit eine wichtige Grundlage für den automatisierten Systementwurf.

## 2 Grundlagen

#### 2.1 Zeitkritische technische Prozesse

In vielen Anlagen und Maschinen treten Prozesse auf. Ein Prozess besteht aus technischen, physikalischen oder chemischen Abläufen, die festgelegten Gesetzen folgen oder nach solchen gesteuert werden müssen [Fär94]. Kontinuierliche Umwandlungsprozesse der Verfahrenstechnik und die Verteilung von Energie in elektrischen Netzen gehören genauso dazu, wie der Fertigungsprozess in einer Motorenfabrik, der Straßenverkehr oder die Materialbewegung in einem Lagerhaus. Im erweiterten Sinne kann auch die Sammlung, Umformung und Verteilung von Informationen als Prozesse gesehen werden. Im Hinblick auf die Struktur der Steuerungssysteme ist eine Einteilung aller Prozesse in vier Klassen nützlich [Heu84]:

- **Kontinuierliche Prozesse**, z.B. Chemische und verfahrenstechnische Prozesse, bei denen eine kontinuierliche Umwandlung von Materie stattfindet (Verbrennung in einer Wärmekraftmaschine).

- **Stückprozesse**, z.B. die Bewegung oder Bearbeitung diskreter, einzeln identifizierbarer Objekte (Materialfluss in einem Walzwerk).

- Befehlsprozesse, z.B. Anfahr- und Schaltprozesse, die durch eine festgelegte Folge von Steueranweisungen von einem Zustand in den anderen gebracht werden können (numerische Steuerung einer Werkzeugmaschine).

- Informationsprozesse, z.B. der Austausch von Nachrichten unterschiedlicher Länge und Dringlichkeit zwischen einer Vielzahl von Teilnehmern mit Hilfe eines Vermittlungssystems (Telefonanlage).

Technische Prozesse können aus sehr vielen Untersystemen mit unterschiedlich engen technischen und logischen Kopplungen zusammengesetzt sein. Jedes Untersystem wird durch Vorgabe von Sollwerten gesteuert und enthält Mechanismen, um automatisch oder manuell die vorgegebenen Arbeitpunkte einzustellen. Steuerungssysteme können technischer oder organisatorischer Natur sein; für eine Prozesssteuerung sind beide von gleichem Interesse. Aufgabe jeder Prozesssteuerung ist es, mit dem gesteuerten System bestimmte, meist wirtschaftlich optimale Ergebnisse zu erzielen. Diese Zielsetzung gilt auch für das Untersystem und damit auch für die gesamte Steuerungshierarchie. Üblicherweise sind auf bestimmten Ebenen eines Prozesses Menschen als Steuernde oder zu Steuernde vorhanden. In Einschränkung sprechen wir oft nur bei automatischen Systemen von Prozesssteuerungen.

Die technischen Prozesse sind von den zugehörigen Anwendungsprozessen (Tasks) einer Prozesssteuerung zu unterscheiden. Sind die Bearbeitungsprozesse aufgrund der physikalischen Randbedingungen des technischen Prozesses an zeitliche Einschränkungen gebunden, spricht man von Realzeitprozessen. Realzeitprozesse lassen sich nach ihren charakteristischen Eigenschaften in verschiedene Gruppen unterteilen. Wird z.B. die Art ihres Auftretens gewählt, kann man periodische und aperiodische Prozesse unterscheiden. Eine andere Aufteilung ergibt sich aufgrund der Lebens-

dauer der Realzeitprozesse. Einige sind statisch, d.h. ein permanenter Teil des Realzeitsystems, während andere dynamisch zur Laufzeit erzeugt werden und nur während der Bearbeitung vorhanden sind. In [RSZ89] wird eine Unterteilung der Bearbeitungsprozesse in (zeit)kritische (critical), notwendige (essential) und unwesentliche (nonessential) Prozesse vorgeschlagen. Zeitkritische Prozesse müssen ihre Zeitschranke (deadline) einhalten, sonst wären die Folgen "katastrophal". Deadlines von notwendige Prozesse sollten eingehalten werden, da sie für die Funktion des Realzeitsystems wichtig sind. Sporadische Überschreitungen der Zeitbedingungen können jedoch meistens toleriert werden, ohne fatale Auswirkungen nach sich zu ziehen. Die unwesentlichen Prozesse, z.B. Systemverwaltungsaufgaben, haben niedrigste Priorität und werden nur abgearbeitet, wenn keine kritischen oder notwendigen Prozesse anstehen. Hier ergeben sich unerwünschte Folgen nur bei sehr großen Verzögerungen.

Eine restriktive Sichtweise ergibt sich durch ausschließliche Einteilung der Prozesse nach den Kosten, welche bei einer angenommenen Überschreitung der Zeitbedingung entstehen würden. Bedeutet die Nichteinhaltung der Zeitbedingung eine Verfehlung der Funktion, so spricht man von harter Realzeit [Süs98]. Beispiele hierfür sind die Ampelschaltung oder die Regelung eines Flugzeugs. Bei der kleinsten Überschreitung der Zeitgrenze muss mit sehr hohen Kosten gerechnet werden. Führt die Nichteinhaltung der Zeitbedingung hingegen "nur" zu einer Verschlechterung der Funktion, so nennt man dies weiche Realzeit. Sporadische Überschreitungen führen zu erhöhten, aber nicht außerordentlichen Kosten. Beispiele hierfür sind die Telefonvermittlung oder die Übertragung von Bildmaterial.

#### 2.2 Klassische Realzeitsysteme

#### 2.2.1 Eigenschaften und Beispiele

Systeme zur Bearbeitung von Realzeitaufgaben gibt es schon seit mehreren Jahrzehnten. Zur Prozessrechner eingesetzt. Die Weiterentwicklung elektronischer Bauelemente und die Möglichkeit, mehrere Rechensysteme über standardisierte Übertragungseinrichtungen miteinander zu verbinden, ermöglichte in den 80er Jahren den Entwurf integrierter Steuerungssysteme, den speicherprogrammierbaren Steuerungen. In einer Vielzahl von Produkten der Automobilindustrie, der Verkehrstechnik, der Produktions- und Fertigungstechnik, sowie der Telekommunikationsindustrie findet man heute integrierte mikroelektronische Steuerungen, sogenannte eingebettete Systeme. Sie bestehen in der Regel aus für die jeweilige Aufgabe optimierter Hardware (Mikrochips) und darauf lauffähiger Software.

Alle Realzeitsysteme müssen charakteristische Anforderungen erfüllen, um Realzeitprozesse verarbeiten zu können [Law92][Fär94]:

- **Rechtzeitigkeit**: Implizit im Namen Realzeitsysteme ist die Forderung nach einer rechtzeitigen Verarbeitung von Daten gegeben. Unter allen Umständen muss die deadline eingehalten werden. Ansonsten wird das Ergebnis nutzlos: "Late data is bad data".

- Gleichzeitigkeit: Mehrere technische Prozesse erfordern eine quasi-parallele Bedienung durch die Bearbeitungsprozesse. Vorgänge müssen oftmals synchronisiert werden.

- **Vorhersagbarkeit**: Die Verarbeitungszeit im ungünstigsten Fall (worst case) als Reaktion auf ein Ereignis muss vorhersagbar sein. Für viele Prozesse gilt die Forderung nach einem deterministischen<sup>2</sup> System.

- **Korrektheit**: Die Erfüllung der Aufgabe gemäß der Spezifikation, die Einhaltung aller Zeitbedingungen und die Vermeidung von Verklemmungen (deadlocks) ist zu gewährleisten.

- **Robustheit**: Im Fehlerfall muss, sofern vorhanden, in einen fail-safe-Zustand übergegangen werden.

- **Kommunikation**: Schnittstellen und Busse ermöglichen den Datenaustausch mit anderen Systemen, Sensoren und Aktoren.

Typische Beispiele für Realzeitsysteme sind:

Einspritz- und Zündungssteuerung eines Verbrennungsmotors: Zahlreiche Signale, wie Kurbelwellenwinkel, Benzindruck, Lufttemperatur, Luftmenge, Drosselklappenwinkel,  $\lambda$ -Wert usw. dienen als Eingangsgrößen des Steuerungssystems. Ein elektronisches Steuergerät, bestehend aus einem leistungsstarken Mikrocontroller und Signalkonditionierungsschaltungen, berechnet optimale Werte für Einspritzzeitpunkt und –menge sowie Zündzeitpunkt aus den Sensorsignalen und gespeicherten Kennfeldern des Motors. Die Ausgangssignale werden an die Aktoren wie Einspritzdüsen, Zündspule, Magnetventile usw. weitergeleitet. Aufgrund der schnellen Kolbenbewegung müssen alle Berechnungen ihre Zeitbedingungen genau eingehalten werden, um einen emissionsarmen und treibstoffsparenden Betrieb zu gewährleisten. Bild 2.1 zeigt schematisch die hochintegrierte Motorsteuerung Motronic ME7 der Firma Bosch.

Bild 2.1 Elektronisches Motormanagement Motronic ME7 (Bosch)

Regelung eines Kernkraftwerks: Die physikalischen Eigenschaften der Kernspaltung erfordern eine exakte Regelung der Betriebsparameter. Die während der Kernspaltung von Uran 235 entstehenden schnellen Neutronen werden durch einen Moderator (z.B. Wasser) auf Spaltgeschwindigkeit abgebremst und treffen als langsame Neutronen auf weitere Uran-Kerne. Die Regelung der Aktivi-

<sup>&</sup>lt;sup>2</sup> Deterministisch heißt ein System, wenn seine Reaktion auf eine bestimmte Eingabe, ausgehend von einem bestimmten Zustand, eindeutig festgelegt ist. Wenn dies nicht der Fall ist, d.h. wenn sich Reaktionen des Modells nur durch Wahrscheinlichkeitsverteilungen beschreiben lassen, nennt man es stochastisch (oder probabilistisch).

tät der Kettenreaktion (Wachstumsfaktor) erfolgt durch Steuerstäbe aus B₄C oder Cadmium. Die Steuerstäbe haben die Aufgabe, die eventuell für weitere Spaltungen zur Verfügung stehenden Neutronen zu neutralisieren. Der Wachstumsfaktor in Kernkraftwerken beträgt maximal 1,0075 (0,75 % Zuwachs), um genügend Zeit zur Einregelung zu haben, zumal die bei der Kernspaltung frei werdenden Neutronen mit bis zu 20 Sekunden Verzögerung auftreten und eine Kernspaltung selbst nur ca. zehn Nanosekunden dauert.

<u>Mikroperforation von Spiralblockseiten</u>: Bei der Produktion von Schreibblöcken werden die einzelnen Seiten mit einer Perforation versehen, um sie einzeln heraustrennen zu können. Normalerweise wird eine Messerwalze verwendet, die mit dem Antrieb der Papierbahn fest verbunden ist. Zur Realisierung einer feineren Mikroperforation werden winzige Löcher mit kurzen Laserpulsen in das Papier gebrannt. Die Führung des Laserstrahls und die Energie der Laserpulse müssen absolut synchron zur Geschwindigkeit der Papierbahn geregelt werden, damit lineare Perforationsverläufe entstehen.

Ein Realzeitsystem in der Form eines eingebetteten Systems besteht aus verschiedenen Komponenten. Viele davon, wie z.B. Interrupt-Controller, Zähler, Zeitgeber, Watchdog, Takterzeugung, A/D-und D/A-Wandler, parallele und serielle Schnittstellen, internes Flash-ROM, ROM und RAM, sind im Mikrocontroller integriert. Zusätzlicher Speicher und Peripheriebausteine können über eine externen Busschnittstelle angebunden werden. Die Struktur zeigt Bild 2.2.

Bild 2.2 Struktur eines eingebetteten Realzeitsystems

#### 2.2.2 Realzeitbetriebssysteme und Anwendungen

Die auf einem Realzeitsystem zu implementierende Steuerungsanwendung wird überwiegend in Assembler oder in einer ressourcensparenden Programmiersprache wie z.B. "C" realisiert. Im Gegensatz zu einfachen sequentiellen Programmen können mit Realzeit-Kerneln oder Realzeitbetriebssystemen (RTOS) komplexe Prozesse gesteuert werden. Die Erstellung von Realzeit-Multitasking-Software erfordert eine andere Denkweise, spart aber bei der Entwicklung unnötige Programmierarbeit. Um die knappen Ressourcen zu schonen, sind moderne RTOS modular skalierbar gehalten, d.h. nur die zur Funktion des Systems benötigten Module werden zur Anwendung hinzugebunden (gelinkt). Außerdem bieten Realzeitbetriebssysteme die notwendigen Protokolle für die immer häufiger gewünschte Vernetzung mehrerer Systeme. Gerade für eine wirtschaftliche Administration der immer aufwändigeren Funktionen bietet die Vernetzung neue Möglichkeiten zur Fernadministration,

-wartung und -überwachung bei gleichzeitiger Kostenreduktion. In aller Munde ist das "Web-basierte Remote-Management" über einen integrierten HTTP-Server. Hierfür sind leistungsfähige Mikrocontroller mit ausreichendem Speicher vorzusehen.

Moderne Realzeitbetriebssysteme sind hierarchisch strukturiert, modular aufgebaut und taskorientiert implementiert. Hierarchie und Modularität reduzieren die Komplexität des Prüf- bzw. Verifikationsaufwands auf einen linearen Umfang. Das Betriebssystem wird heute aus Bausteinen nach den spezifizierten Anforderungen konfiguriert. Man kann die Struktur als Schichtenmodell beschreiben (Bild 2.3). Jede Schicht repräsentiert hierbei eine abstrakte (virtuelle) Maschine, die spezifische Funktionen bereitstellt. Die Betriebssystemkern-Schicht stellt z.B. sämtliche Funktionen der Taskverwaltung, wie Unterbrechungsverarbeitung, Taskdefinition, -scheduling und -synchronisation zur Verfügung. Ihre zweite Hauptaufgabe ist üblicherweise die Realisierung von Gerätetreibern. Die restlichen Schichten bauen auf der Betriebssystemkern-Schicht auf. Gegenwärtig versucht man, möglichst viele Funktionen in die oberen Schichten zu verlagern um die Abhängigkeiten von der Zielhardware zu minimieren. Damit erhöht sich die Portabilität und die Zuverlässigkeit des Realzeitbetriebssystems.

Bild 2.3 Schichtenmodell eines Realzeitbetriebssystems

Wichtige Funktionen eines Realzeitbetriebssystems sind die Betriebsmittelverwaltung und die Taskverwaltung. Bei der Erstellung der Realzeit-Anwendung teilt man zeitintensive Aufgaben in elementare Teilaufgaben (Tasks) auf. Dadurch können sie weitgehend unabhängig voneinander parallel ausgeführt werden. Voraussetzung hierfür ist das Multitasking, die Fähigkeit eines Systems, mehrere Aufgaben (Tasks) gleichzeitig (parallel) zu bearbeiten. Ein Realzeitsystem mit einem Prozessor oder Mikrocontroller kann immer nur eine Task pro Zeiteinheit bearbeiten. Durch schnelles Hin- und Herschalten zwischen den Tasks entsteht der Eindruck einer scheinbar parallelen Verarbeitung; man spricht in diesem Fall von quasiparalleler Verarbeitung. Echte Parallelverarbeitung ist nur auf einem Multiprozessorsystem möglich. Das Hin- und Herschalten zwischen den Tasks übernimmt der sogenannte Dispatcher, die Entscheidung welche Task als Nächste rechnen darf, der Scheduler. Dispatcher und Scheduler sind Bestandteile jedes Realzeitbetriebssystems. Die Schedulingalgorithmen lassen sich in statische und dynamische Verfahren unterteilen. Zu den in Realzeitsystemen überwiegend eingesetzten dynamischen Verfahren zählen das prioritätsbasierte Rate monotonic-Scheduling und das leistungsfähige Earliest-deadline-first-Scheduling. Im Gegensatz zu den statischen Verfahren wird hier erst zur Laufzeit entschieden, welche Task als Nächste vom Prozessor zu bearbeiten ist.

Betriebsmittel sind alle Mittel (Hardware und Software), die eine Task braucht, um durchgeführt werden zu können. Die Betriebsmittelverwaltung stellt somit die Teilfunktionen zum konfliktfreien Belegen, Betreiben und Freigeben von Betriebsmitteln für die einzelnen Tasks zur Verfügung. Neben der Task- und Betriebsmittelverwaltung gehören zwei weitere Maßnahmen zu den wichtigen Bestandteilen:

- Zuverlässigkeitsmaßnahmen: Beheben von Speicher- und Übertragungsfehlern, Unempfindlichkeit gegen fehlerhafte Benutzung, Rekonfiguration fehlertoleranter Systeme

- Schutzmaßnahmen: Speicherschutzregister, Speicherschutzschlüssel, Schutzbereiche, Zugriffskontrolle, Passwörter

Die Basis aller Zuverlässigkeitsmaßnahmen ist die Redundanz oder Robustheit (Unempfindlichkeit, z.B. exception handling und graceful degradation). Zu den Schutzmaßnahmen zählen alle Strategien zum Schutz der Betriebsmittel vor unberechtigten Zugriffen der Tasks. Bei vernetzten Systemen zählt aber auch der Schutz vor ungewollten Eindringlingen und Viren dazu. Die Basis der Schutzmaßnahmen sind das Berechtigungskonzept und die Schutzbereiche. So kann man sich das Betriebssystem aus verschiedenen Hierarchieebenen vorstellen, bei denen die Rechte zu den äußeren (bzw. oberen) Schichten hin immer mehr abnehmen.

Eine wesentliche strukturelle Schutzmaßnahme ist die Verhinderung von Verklemmungen von Prozessen. Die folgenden vier Bedingungen sind notwendig und hinreichend für das Auftreten von Verklemmungen. Indem man sicherstellt, dass mindestens eine der folgenden Bedingungen <u>nicht</u> erfüllt ist, lassen sich Verklemmungen erfolgreich verhindern:

- Betriebsmittel sind nur exklusiv nutzbar.

- Betriebsmittel können nicht entzogen werden.

- Prozesse belegen zugewiesene Betriebsmittel auch dann, wenn sie auf Zuweisung weiterer Betriebsmittel warten.

- Es gibt eine zyklische Kette von Prozessen, von denen jeder ein Betriebsmittel besitzt, das der nächste Prozess in der Kette benötigt.

#### Entwurfsprozess

Der Entwurfsprozess für eingebettete Realzeitsysteme (Bild 2.4) wird in zahlreichen Forschungsprojekten untersucht. Ziel ist meist die Entwicklung einer Methodik zum durchgängigen Entwurf von eingebetteten Systemen, speziell die automatische Generierung von Software aus der Systemspezifikation und die Synthese einer Schnittstellen- und Hardwarebeschreibung (Hardware/Software Co-Design). Für eine schnelle und kostengünstige Entwicklung komplexer Systeme ist die effiziente Wiederverwendung von Schaltungsbeschreibungen eine wichtige Grundlage. Durch die Verwendung von abstrakten Beschreibungssprachen, beispielsweise VHDL³, wird eine modulare Systemspezifikation ermöglicht. Jedes Modul dieser Spezifikation besteht aus einer Menge von Elementen, die durch Komponenten, Funktionen und Prozeduren gebildet werden. Das bietet die Möglichkeit, Module separat zu beschreiben und damit anderen Entwürfen wieder zur Verfügung zu stellen (reuse).

-

<sup>&</sup>lt;sup>3</sup> VHDL: **V**hsic **H**ardware **D**escription **L**anguage, vhsic = very high speed integrated circuit.

Bild 2.4 Entwurfsprozess für eingebettete Realzeitsysteme

#### 2.3 PC-basierte Realzeitsysteme

PC-basierte Systeme verwenden, im Unterschied zu den proprietären klassischen Realzeitsystemen, die Standard-PC-Hardware als Rechnerplattform. Der Prozessor (x86-CPU) fungiert hierbei als zentrale Recheneinheit. Prozesssignale können entweder über die vorhandenen Schnittstellen oder über separate Module in Form von Steckkarten eingelesen oder ausgegeben werden. Für die Bussysteme des PCs ist eine Vielzahl von Peripheriemodulen erhältlich. Eingangsmodule erfassen physikalische Eingangsgrößen und wandeln sie in digitale Signale um. Ausgangsmodule generieren analoge und digitale Signale zur Ansteuerung von Aktoren. Über Feldbusmodule können intelligente Sensoren und Aktoren oder andere Realzeitsysteme eingebunden werden.

Als Vorteile der PC-basierten Steuerungssysteme gegenüber klassischen Systemen gelten:

- Prozess-Informationen sind inhärent verfügbar und erleichtern die Einbindung der Prozesssteuerung in ERP-Systeme<sup>4</sup> bzw. die Integration von Büro und Produktion.

- Die grafische Visualisierung von Prozesssignalen und –abläufen schafft eine anwenderfreundliche Mensch-Maschine-Schnittstelle und erleichtert so die Bedienung.

- Die Verwendung von standardisierter Hard- und Software ermöglicht eine schnellere Projektierung.

- Der technologische Vorsprung der PC-Technik und die rasante Weiterentwicklung schafft eine leistungsfähige Plattform für die Prozesssteuerung, gerade für komplexe Steuerungsaufgaben.

- Offene Standards machen unabhängig von Herstellern und führen zu modularen Systemen.

- Vielfältige Kommunikationsmethoden ermöglichen dezentrale Lösungen. Besonders nützlich sind die bereits vorhandenen Schnittstellen für Intranet/Internet-Anschluss.

- Zur Programmierung werden meist Ablaufdiagramme eingesetzt, die sich mit geringem Aufwand aus der Spezifikation generieren lassen.

\_

<sup>&</sup>lt;sup>4</sup> ERP: **E**nterprise **R**esource **P**lanning

#### 2.3.1 Struktur

Die Systemstruktur des PCs sowie Aufbau und Funktion der eingesetzten Hardwarekomponenten werden durch eine Vielzahl von Industriestandards bestimmt. Wichtigste Grundlage bildet der von den Firmen Intel und Microsoft herausgegebene PC Design Guide. Die aktuelle Ausgabe (PC2001, Version 1.0, [IM00]) gibt der Hard- und Softwareindustrie Richtlinien und Vorschläge zur Gestaltung eines PC-Systems, speziell für den Einsatz mit Windows-Betriebssystemen. Innerhalb des Design Guides wird auf die entsprechenden Standards und Industrienormen verwiesen. Die Hardwarekomponenten und -struktur eines PC2001-Systems zeigt Bild 2.5.

Bild 2.5 Hardwarekomponenten eines Standard-PCs

Der Chipsatz ist das Bindeglied zwischen den einzelnen Komponenten eines Computersystems. Er steuert das Zusammenspiel und den Datenfluss zwischen Prozessor, Arbeitsspeicher, Bussystemen sowie den Schnittstellen und hat großen Einfluss auf die Leistung des Gesamtsystems. Die Chipsätze der verschiedenen Hersteller haben, bei ansonsten identischen Hardwarekomponenten, Leistungsunterschiede von bis zu 15 %. Mit der Auswahl des Chipsatzes werden Typ des Systembusses, des Speichers, der Schnittstellen und des Prozessors festgelegt. Fehlende Komponenten und Schnittstellen werden über Zusatzbausteine, wie z.B. einen Super-I/O-Chip, hinzugefügt.

Der Chipsatz ist meist in zwei separate Bausteine unterteilt, die über einen schnellen Systembus verbunden sind. Aus der Historie spricht man hier von North und South Bridge. Die North Bridge enthält Schnittstellen zur Anbindung des Prozessors (Front Side Bus), der Grafikkarte (Advanced Graphics Port, AGP) und des Systembusses (System Bus Interface), sowie eine Steuereinheit für den Arbeitsspeicher (memory controller). Die South Bridge beinhaltet Controller für die Festplatten (IDE), den PCI-Bus und den USB-Bus. Weiterhin befinden sich dort die Schnittstellen für das Systemmanagement (SM-Bus: Lüfter, Temperatursensoren usw.), Audio- und Modem<sup>5</sup>-Wandlerbausteine (AC97 Codec<sup>6</sup>), einige frei verwendbare Anschlusspins (General Purpose I/O, GPIO) und ein universeller

<sup>&</sup>lt;sup>5</sup> Modem: **Mo**dulator und **Dem**odulator.

<sup>&</sup>lt;sup>6</sup> Codec: **Co**ding and **Dec**oding.

Low-Pin-Count-Bus zum Anschluss von hochintegrierten Schnittstellenbausteinen. Über diesen können klassische Peripheriegeräte, wie Maus, Tastatur, Floppy, serielle und parallele Schnittstellen usw. an das PC-System angeschlossen werden. In neuen Systemen versucht man auf die Vielfalt dieser nicht immer unproblematischen Schnittstellen zu verzichten. So untersagt z.B. der PC2001-Vorschlag ausdrücklich die Verwendung von ISA-Bus, Floppycontroller, serieller oder paralleler Ports, sowie der PS2-Schnittstelle<sup>7</sup>. Unverzichtbare Geräte, wie Maus oder Tastatur, sind über den USB-Bus anzuschließen.

Für den Einsatz der Standard-PC-Hardware als Realzeitsystem zur Steuerung von technischen Prozessen werden Ein- und Ausgänge für analoge und digitale Signale benötigt. Vorrangig bieten sich die integrierten Schnittstellen an. Acht digitale TTL-Signale können ohne großen Aufwand über die parallele Schnittstelle eingelesen oder ausgegeben werden. Im industriellen Umfeld sind jedoch diese empfindlichen Schnittstellen aufgrund der fehlenden Schutzeinrichtungen nur begrenzt einsetzbar. Störspannungen und –impulse lassen die PC-Hardware einen "schnellen und leisen Tod sterben". Die hohe Integrationsdichte auf dem *Motherboard* verhindert eine kostengünstige Reparatur. Für einen zuverlässigen Betrieb sind also unbedingt Peripheriegeräte und Steckkarten mit galvanischer Trennung und ausreichenden Isolationsabständen einzusetzen; vorzugsweise als externe Komponenten mit eigener Stromversorgung.

#### 2.3.2 Realzeitfähigkeit

In vielen Forschungsprojekten wird die Realzeitfähigkeit von PC-Systemen und der darauf ablaufenden Standardbetriebssysteme für die Realisierung von Steuerungen für zeitkritische technische Prozesse untersucht. Die zeitlichen Anforderungen ergeben sich hierbei aus den charakteristischen Eigenschaften, der in einem technischen Prozess auftretenden Ereignisse. Wichtig sind Auftrittsverteilung, d.h. wann und in welchen Abständen treten die Ereignisse auf, sowie die maximal zulässigen Reaktionszeiten, d.h. wie lange darf es maximal dauern bis eine Antwort auf ein bestimmtes Ereignis generiert wird. Die Auftrittswahrscheinlichkeit reicht von einfachen konstanten und zyklischen Ereignissen bis hin zu komplexen, rein zufällig auftretenden Ereignissen ohne bekannte Statistik. In einigen Fällen ist das Auftreten mehrerer unterschiedlicher Ereignisse voneinander abhängig.

In der Literatur werden PC-basierte Systeme oft den weichen Realzeitsystemen zugeordnet. Diese Aussage gilt jedoch nicht pauschal, denn die Einhaltung von Realzeit-Bedingungen hängt stark von der eingesetzten Soft- und Hardware sowie den absoluten Zeitgrößen ab. "Realzeit" bzw. "zeitkritisch" ist relativ. So bedeutet zeitkritisch bei der Messwerterfassung von Atomzusammenstößen in Beschleunigeranlagen einige Nanosekunden. Bei der Steuerung von Antrieben, Robotern oder in Feldbussystemen wird Realzeit oft in Mikrosekunden gemessen, bei verteilten Prozesssteuerungen reichen Millisekunden. Sind hingegen thermische Prozesse zu steuern genügen oft Sekunden für die Einhaltung der zeitlichen Anforderungen.

#### Geringe zeitliche Anforderungen

Man ist bestrebt, den Aufwand minimal zu halten, d.h. bei den hier eingesetzten PC-basierten Systemen weitestgehend Standardkomponenten einzusetzen. Aus Kostengründen ist es außerdem sinn-

<sup>&</sup>lt;sup>7</sup> Hingegen gilt die Bereitstellung dieser Schnittstellen über eine PCI-Steckkarte als PC2001-konform.

voll, zuerst alle Möglichkeiten der Software auszuschöpfen. Man versucht hier, die Standardbetriebssysteme Linux und Windows NT zu verwenden. Wie im Kapitel 4 ausführlich beschrieben wird, erreicht man mit diesen Betriebssystemen (ohne Veränderungen) nur Reaktionszeiten im Bereich von einigen zehn Millisekunden. So untersuchte [WGT97] mit Hilfe des Hartstone Benchmark [DSW92] das Realzeitverhalten von Windows NT. Es ließ sich feststellen, dass Windows NT nur bedingt für die Erfüllung von Realzeitaufgaben geeignet ist. Lediglich für den Prozess mit der höchsten Priorität kann die Einhaltung von Realzeitbedingungen garantiert werden. Eine Alternative stellt die Überdimensionierung des PC-Systems in Bezug auf die Rechenleistung für Anwendungen mit Zeitschranken von über 50 ms dar. Bei einer Systemlast von unter 20 % werden Zeitbedingungen auch unter Windows NT relativ genau eingehalten.

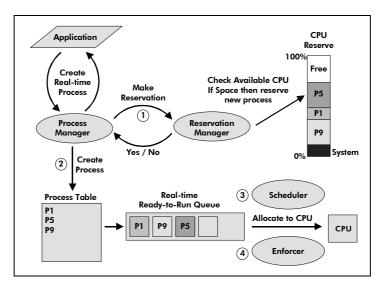

Die Reduzierung der großen Variabilität (Jitter) von bis zu mehreren hundert Millisekunden ist Gegenstand zahlreicher Forschungstätigkeiten. So implementiert [LCN98] einen Soft Real-time Scheduling Server für Windows NT, mit dessen Hilfe der Jitter beim Abspielen von Multimediadaten von 300 ms auf unter 100 ms reduziert wird. Hierzu wird zusätzlich zum Scheduler des NT-Kernels ein weiterer User level-Scheduler mit höchster Priorität ausgeführt. Dieser sorgt für eine faire Rechenzeitzuteilung zwischen zeitkritischen und normalen Prozessen. Zur effizienteren Programmierung von parallelen Anwendungen auf Multiprozessorsystemen entwickelt [HBP+00] einen Kernel-mode Resource Manager für das Betriebssystem Windows 2000 auf Grundlage des Nanothreads Programming Model. Die Aufgabe des Resource Managers ist, alle laufenden Anwenderprozesse zu überwachen und sie anhand einer optimalen Schedulingstrategie auf verschiedene Prozessoren aufzuteilen. Damit lassen sich die Ausführungszeiten gegenüber dem Windows-eigenen Schedulingmechanismus um den Faktor 2 verringern. Die von [SP95][SP96] vorgeschlagene Erweiterung Dreams Subsystem<sup>8</sup> (Bild 2.6) benützt mehrere Managementeinheiten zur Reservierung von Rechenzeit und ihrer Kontrolle.

Bild 2.6 Struktur des Dreams Subsystem

Die Methode der Rechenzeitbeschränkung und der Prozessor-Reservierung wird auch von anderen Forschungsteams untersucht. Eine Entwicklergruppe der Firma Microsoft [JBF<sup>+</sup>96] hat mit der Rialto Real-time Architecture ein entsprechendes System entwickelt. Mit der Hilfe von time constraints kann ein Prozess seine Zeitbedingungen spezifizieren, die er zur korrekten Ausführung benötigt. Hierzu

<sup>&</sup>lt;sup>8</sup> Ein Subsystem ist die Windows-Version eines Unix User Mode Servers.

stehen die Aufrufe BeginConstraint () und EndConstraint () zur Verfügung. Der Realzeit-Scheduler versucht diese Zeitbedingungen durch eine zweckmäßige Ablaufreihenfolge einzuhalten. Auch hier steht ein Resource Manager zur Verwaltung und Überprüfung der Anforderungen bereit. Die Rialto-Architektur greift sehr tief in das Windows-Betriebssystem ein und ersetzt Teile von diesem, sodass bestehende Anwendungen umgeschrieben werden müssen. Weitere Informationen finden sich in [JRR97] und [JR99].

Will man Windows NT für weiche Realzeitaufgaben verwenden, ohne Erweiterungen einzusetzen, so sollten die Ausführungszeiten der Prozesse vermessen werden. Hier bietet sich das von [GN99] entwickelte *Performance Monitoring Tool JewelNT* an, welches eine detaillierte grafische Anzeige und Analyse der Taskausführungszeiten, Task-Umschaltungen und Unterbrechungen erlaubt. In Entwicklungssystemen von Realzeitbetriebssystemen sind ähnliche Monitoring-Werkzeuge enthalten, wie z.B. das in die *Tornado-*Entwicklungsumgebung der Firma Wind River Systems integrierte *Wind-View* für das Realzeitbetriebssystem *VxWorks*.

Auch das Standardbetriebssystem Linux ist Gegenstand der Forschung. In [HR01] wird Rapid Reaction Linux beschrieben, das aus der Vereinigung zweier Linux-Realzeit-Patches entstanden ist. Die Basis bilden der Low-Latency-Patch von Molnar, der lange Latenzzeiten im Kernel verringert, und der UTIME-Patch der Universität von Kansas, der den PC-Timerchip auf die jeweilige Zeitspanne bis zum nächsten Ereignis umprogrammiert. Auf diese Weise können die Latenzzeiten des Linux-Kernels um den Faktor 10 auf ca. 5 – 10 ms reduziert werden.

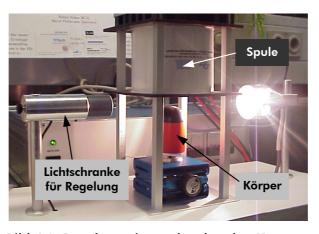

Zur Anwendung kommen diese nicht oder nur leicht veränderten Standardbetriebssysteme bei weichen Realzeitanforderungen, wie sie z.B. bei "gutmütigen" technischen Prozessen auftreten. In [HB00] wird die Regelung eines schwebenden Körpers nur mit einem Standard-PC, einer A/D-D/A-Steckkarte, Windows NT und der Multimedia-Bibliothek WinMM.lib realisiert. Sporadische Ausreißer der Abtastrate haben aufgrund der Trägheit der Masse und der Induktivität keine gravierenden Auswirkungen auf die Stabilität.

#### Anforderungen im Sub-Millisekundenbereich

Ergeben sich bei der Analyse eines technischen Prozesses harte Realzeitanforderungen im Sub-Millisekundenbereich, und will man weiterhin Standardbetriebssysteme verwenden, muss man größere Veränderungen vornehmen. Aufgrund des großen Interesses der Industrie für PC-basierte Prozesssteuerungen mit Reaktionszeiten im Bereich von 50 – 500 Mikrosekunden entwickelten verschiedene Firmen Lösungen. Gerade das angestammte Gebiet der klassischen SPS-Systeme bietet einen großen Markt mit hohen Ertragschancen.