Lehrstuhl für Realzeit-Computersysteme

# Worst Case Execution Time Estimation for Advanced Processor Architectures

Dipl.-Ing. univ. Stefan M. Petters

#### Lehrstuhl für Realzeit-Computersysteme

# **Worst Case Execution Time Estimation for Advanced Processor Architectures**

Dipl.–Ing. univ. Stefan M. E. Petters

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktor-Ingenieurs (Dr.-Ing.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. K. Antreich

Prüfer der Dissertation:

1. Univ.-Prof. Dr.-Ing. G. Färber

2. Univ.-Prof. Dr. techn. J. Swoboda

Die Dissertation wurde am 14.03.2002 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 22.08.2002 angenommen.

### **Preface**

Holzkirchen, 13th March 2002

As it is always with such a work, it needs the support of many people to be accomplished. First to be named is my supervisor Prof. Georg Färber. He took me under his wings even before I had finished my diploma thesis. His considerable and never slacking interest in the subject of this thesis has bourne me over a time, where the work seemed to become a never ending story. In a similar early stage I got support of Prof. Joachim Swoboda, who has taken upon him the task of doing the second review of my thesis. My collegues at the institute deserve many thanks for proof reading my publications, asking questions regarding my work, which sometimes got me flat footed, sustaining a good working climate and occasionally providing interesting tasks to avoid working on this dissertation. I want to mention explicitly Alexander v. Bülow, who gave me a good deal of thrust in motivation during his diploma thesis.

Muireann Bennis helped to fill in a lot of commas which I only use sparingly, pointed out many Germish errors, and sentences stretching over half a page. Last but definitely not least my wife Amine deserves many a thanks for her continuous support and trust in my work. Besides thanks I have to apologise to my wife and especially my children, Shahin and Anian who had to do more or less without husband and father for quite some time now. I hope I can make up for this time.

Stefan M. Petters.

Often you must turn your stylus to erase, if you hope to write anything worth a second reading.

-Horace, poet and satirist (65-8 BCE)

# **Abstract**

Advanced acceleration features, as they are used in todays mass market, high performance processors, have only been considered in isolation in previous worst case execution time estimation approaches. This thesis presents a measurement based approach to estimate the worst case execution time on a fully featured processor. To produce reliable results several aspects have to be considered. Prior to the start of a measurement, the acceleration techniques are preset, as far as possible, into their worst case state. The features, which cannot be controlled to produce the worst case state are either randomised or covered by penalties added to the measured results. All possible path combinations are enforced using additional instrumentation code. By partitioning the measurement problem into several measurement blocks, the coverage of all path combinations is ensured. To cover final uncertainty, an existing extreme value statistic approach is extended, to handle combinations of measurements. Additionally a scheduling analysis method, suitable for processors equipped with such acceleration techniques, is presented. A number of test cases, show the applicability and the limitations of the approach.

# **Contents**

|   | Glos  | ssary                            | V  |

|---|-------|----------------------------------|----|

| 1 | Intro | oduction                         | 1  |

|   | 1.1   | Motivation                       | 1  |

|   | 1.2   | Contribution and Limitations     | 1  |

|   | 1.3   | Organisation of the Dissertation | 2  |

| 2 | Rela  | ated Work                        | 4  |

|   | 2.1   | Control Flow Analysis            | 4  |

|   |       | 2.1.1 Annotations                | 4  |

|   |       | 2.1.2 Symbolic execution         | 5  |

|   | 2.2   | Execution Time Estimation        | 7  |

|   |       | 2.2.1 Hardware Modelling         | 7  |

|   |       | 2.2.2 Measurement Approach       | 10 |

|   |       | 2.2.3 Calculation Methods        | 12 |

|   | 2.3   | Operating System Analysis        | 13 |

|   | 2.4   | Scheduling Analysis              | 14 |

| 3 | Rea   | I-time and Monitoring            | 16 |

|   | 3.1   | Real-time                        | 16 |

|   | 3.2   | Monitoring                       | 17 |

|   |     | 3.2.1   | Event Detection                         | 18 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 3.2.2   | Statistical Sampling                    | 19 |

|   |     | 3.2.3   | Hardware Monitoring                     | 20 |

|   |     | 3.2.4   | Software Monitoring                     | 22 |

|   |     | 3.2.5   | Hybrid Monitoring                       | 23 |

| 4 | Mod | els     |                                         | 26 |

|   | 4.1 | Model   | of Embedding Process                    | 26 |

|   | 4.2 | Basic l | Hardware Model                          | 28 |

|   |     | 4.2.1   | Model of Processor                      | 29 |

|   |     | 4.2.2   | Peripheral Hardware                     | 31 |

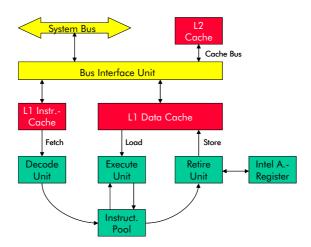

|   | 4.3 | Intel P | entium III                              | 33 |

|   |     | 4.3.1   | General Architecture                    | 33 |

|   |     | 4.3.2   | Memory Organisation                     | 35 |

|   |     | 4.3.3   | Caches                                  | 35 |

|   |     | 4.3.4   | Branch Prediction                       | 36 |

|   |     | 4.3.5   | Monitoring Support                      | 37 |

|   |     | 4.3.6   | Relevant Facts for the WCET Measurement | 37 |

|   |     | 4.3.7   | Preemption Handling                     | 42 |

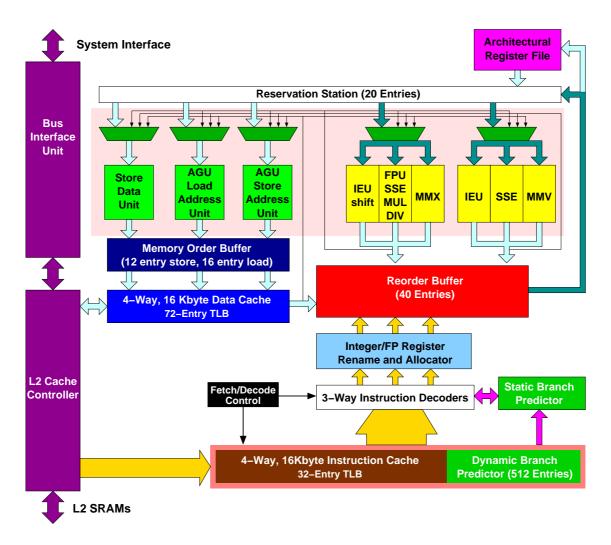

|   | 4.4 | AMD .   | Athlon Family                           | 46 |

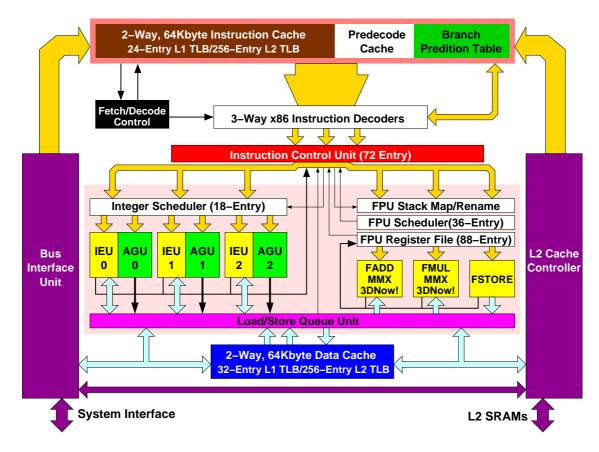

|   |     | 4.4.1   | General Architecture                    | 46 |

|   |     | 4.4.2   | Memory Organisation                     | 47 |

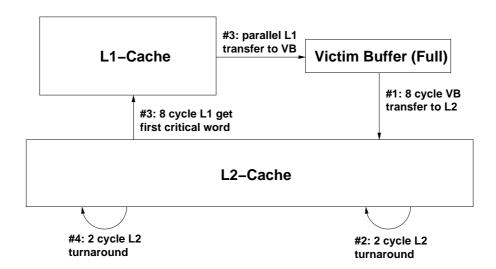

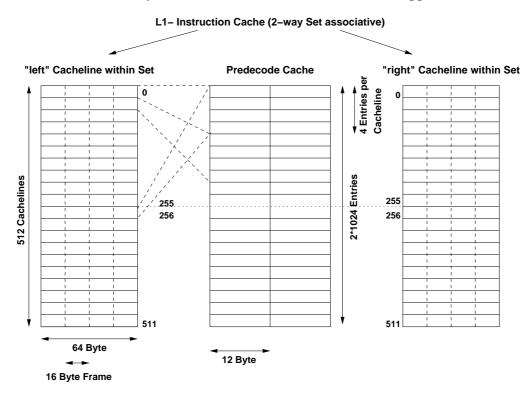

|   |     | 4.4.3   | Caches                                  | 48 |

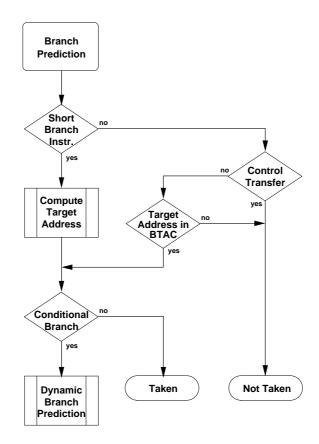

|   |     | 4.4.4   | Branch Prediction                       | 48 |

|   |     | 4.4.5   | Monitoring Support                      | 49 |

|   |     | 4.4.6   | Relevant Facts for the WCET Measurement | 49 |

|   |     | 117     | Preemption Handling                     | 51 |

|   | 4.5 | Interac | ction with a Real-Time Operating System                     | 52 |

|---|-----|---------|-------------------------------------------------------------|----|

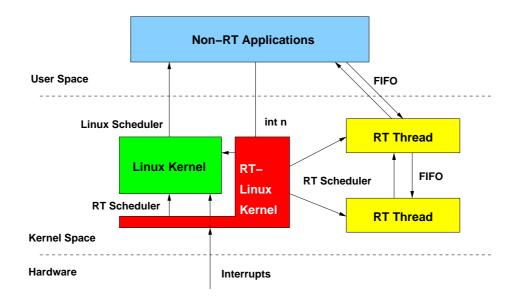

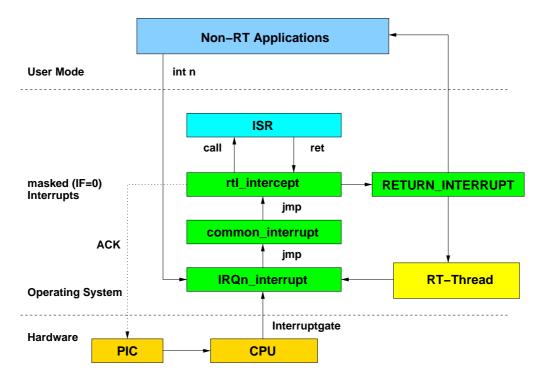

|   |     | 4.5.1   | Extensions to a General Purpose Operating System            | 53 |

|   |     | 4.5.2   | System Calls                                                | 60 |

|   |     | 4.5.3   | Preemption                                                  | 61 |

|   |     | 4.5.4   | Thread Model                                                | 63 |

|   | 4.6 | Confid  | lence in Measured Values                                    | 64 |

|   |     | 4.6.1   | Statistical Processes                                       | 64 |

|   |     | 4.6.2   | Probability Distribution of Measurement Blocks              | 66 |

|   |     | 4.6.3   | Joining of Measurement Blocks                               | 68 |

|   | 4.7 | Real-ti | ime Analysis                                                | 74 |

|   |     | 4.7.1   | Response Time Analysis of a Simple System                   | 74 |

|   |     | 4.7.2   | Extending the Simple Real-Time Analysis for Complex Systems | 75 |

| _ | _   | . ,     |                                                             | •  |

| 5 | _   |         | al Validation                                               | 82 |

|   | 5.1 | Metho   | dology Overview                                             | 82 |

|   | 5.2 | Tool D  | Description                                                 | 83 |

|   |     | 5.2.1   | Assumptions                                                 | 83 |

|   |     | 5.2.2   | Development Tool chain                                      | 85 |

|   |     | 5.2.3   | PAN as Controlling Unit                                     | 86 |

|   |     | 5.2.4   | РЯN Analysis Part                                           | 87 |

|   | 5.3 | Test So | etup                                                        | 91 |

|   |     | 5.3.1   | Athlon Hardware                                             | 92 |

|   |     | 5.3.2   | Pentium III Hardware                                        | 92 |

|   |     | 5.3.3   | Operating System                                            | 93 |

|   | 5.4 | Examp   | ole Applications and Evaluation                             | 96 |

|   | 5.5 | Limita  | ations to the Instrumentation                               | 99 |

|   | 5.6 | Codin   | g Guidelines                                                | 99 |

#### Contents

|   | 5.7   | Real-T  | ime Analysis                | 102 |

|---|-------|---------|-----------------------------|-----|

| 6 | Con   | clusion |                             | 105 |

|   | Bibli | iograph | у                           | 107 |

|   | Inde  | ×       |                             | 117 |

| Α | Prod  | essor [ | Description                 | 121 |

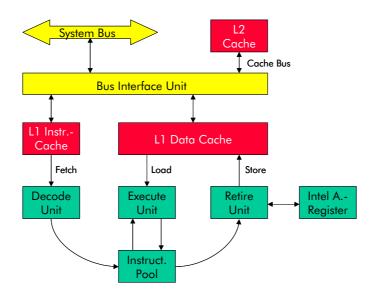

|   | A.1   | Intel P | 6 Family                    | 121 |

|   |       | A.1.1   | General Structure           | 121 |

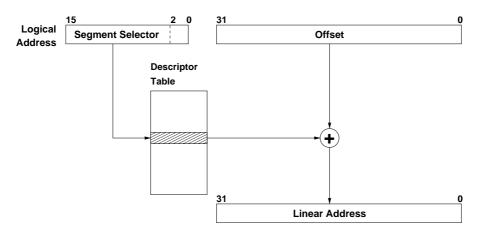

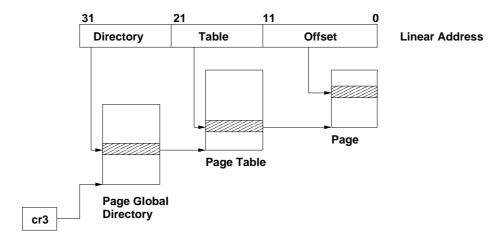

|   |       | A.1.2   | Memory Management           | 124 |

|   |       | A.1.3   | Caches                      | 127 |

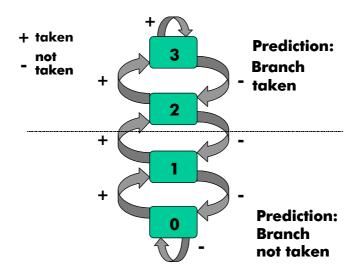

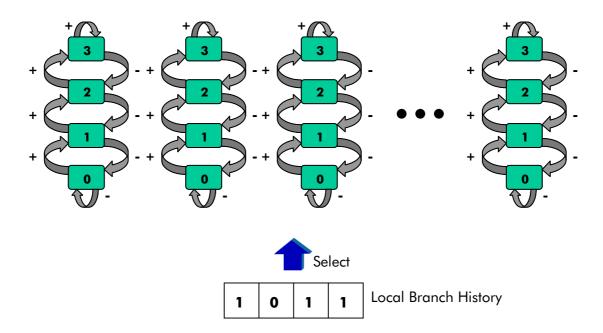

|   |       | A.1.4   | Branch Prediction           | 129 |

|   |       | A.1.5   | Builtin Monitoring Support  | 132 |

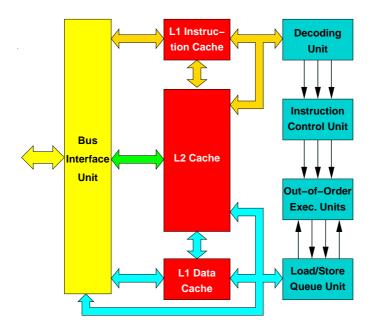

|   | A.2   | AMD .   | Athlon                      | 133 |

|   |       | A.2.1   | General Structure           | 134 |

|   |       | A.2.2   | Memory Management           | 136 |

|   |       | A.2.3   | Caches                      | 136 |

|   |       | A.2.4   | Branch Prediction           | 138 |

|   |       | A.2.5   | Built in Monitoring Support | 142 |

# **Glossary**

| factual dead code | code which may never be reached, regardless of the input parameters, but cannot be identified as such by a compiler.     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| $B_i$             | Blocking time suffered by thread $\tau_i$ induced by resource contention.                                                |

| $C_i$             | Uninterrupted WCET of thread $\tau_i$ .                                                                                  |

| $E_j(R_i)$        | Worst case number of releases of thread $\tau_j$ during time $R_i$ .                                                     |

| PAWCET            | Confidence level of an Assumed WCET value $t_{AWCET}$ for a specific piece of code.                                      |

| $P_{i,j}^n$       | Worst Case number of preemptions of thread $\tau_i$ by thread $\tau_j$ which are not covered at start of iteration $n$ . |

| $R_i$             | Worst case response time of thread $\tau_i$ .                                                                            |

| $T_{j}$           | Minimum interval between two releases of thread $\tau_j$ .                                                               |

| $t_{AWCET}$       | Assumed WCET value for a specific piece of code.                                                                         |

| $t_{MWCET}$       | Measured WCET value for a specific piece of code including all additional penalties.                                     |

| $t_{WCET}$        | Physical WCET value for a specific piece of code, which is usually unknown.                                              |

| $w_i^n$           | Execution window of thread $\tau_i$ in the <i>n</i> th iteration.                                                        |

| $\delta_i$        | Worst case individual preemption delay suffered by thread $\tau_i$ each time it is preempted.                            |

$\Theta_{i,i}^n$

$\mathbf{H}_{i}$ Set of threads with higher priority than thread  $\tau_i$ .  $\mathbf{L}_k$ Set of threads with lower priority than thread  $\tau_k$ .  $\mathbf{P}_{S_m}$ Set of threads which potentially may obtain the semaphore  $S_m$  during their execution.  $\mathbf{S}_{i,j}^n$ Set of threads which potentially suffer preemption by  $\tau_k$ , instead of  $\tau_i$ , and have not been covered at start of iteration n. max(...)The maximum value of the arguments. min(...)The minimum value of the arguments. Mean value of a random variable. μ Deviation of a random variable. σ

thread  $\tau_i$ , after n-1 iterations.

The cumulative additional preemption delay caused by thread  $\tau_i$ , on

# 1 Introduction

#### 1.1 Motivation

Modern general purpose processors are subject to various optimisation techniques aimed at improving average performance, and resulting in nondeterministic and/or, in poor worst case performance. Despite this tradeoff more and more of these processors are deployed in real-time systems. One reason for this trend is that the domain of real-time systems has grown considerably in the last few years, due to the increasing penetration of computer systems in every day life. Typical examples are cash dispensers, the microwave oven, or the up to 50 processors integrated in modern cars. Not all of these applications have real-time properties, and even less are life threatening, but if you take the example of a customer with his brand new car it would be completely unacceptable if his newly bought product ceases to work on the motorway, due to a deadline violation in the engine control unit. Due to this broadening application area the factors development, cost and time-to-market have gained considerably in importance. To use general purpose processors would be one way to achieve this.

Using measurements to estimate the worst case execution time is common practice in industry. However, up until now the common aproach for addressing this were ad-hoc and rule of thump methods. In most cases neither the test coverage, nor the real-time analysis are investigated. One of the main reasons for this is the tradeoff between the estimated probability of a failure on one hand and the cost and time consumed for testing and analysis on the other.

#### 1.2 Contribution and Limitations

This dissertation contributes to research in this topic in several aspects. It shows how to provide reliable bounds on state of the art processors, not only on the WCET, but also on the delay induced by the preemption of task, utilising measurements. Path enforcement is deployed as a means to ensure that all path combinations possible in the later application

of the software are surely covered in the testing phase. The complexity of this brute force method is reduced enourmously, by partitioning the program into several measurement blocks. The measurements are conducted utilising built in performance monitoring hardware of the processors. Such hardware is available on many high performance processors and is intended for performance optimisation.

To decouple consecutive measurements, and produce reliable results, the accceleration techniques of the processor are manipulated in such a way that either a worst case state, or a randomised state is provided at the start of each measurement block. In cases where neither is possible an analysis of the processor features delivers penalties to be considered to cover the potential negative effects. As with all real-time system, the programmer of real-time software is required to follow coding restrictions and guidelines. The restrictions imposed are necessary to avoid underestimation of the WCET. A typical example of such a restriction is the proscription of random access to memory through pointers, since the approach is not able to guarantee the WCET for such cases. The coding guidelines provide the programmer with hints to reduce overhead on the WCET. In some cases the gain in accuracy has to be bought with actual performance in some cases the coding guidelines even accelerate the code.

The approach relies in the current form on user annotations to provide information on the paths to be executed. However, techniques to automatically rule out infeasible paths and bound loop iteration can be easily integrated.

In order to avoid excessive overestimation of the worst case execution time, extreme value statistics are deployed. The previous work in this area, regards only the execution time of a monolithic program i.e.; one extreme value distribution describes the execution time of the program. Due to the partitioning of the measurement problem, the calculation of the overall WCET for a program is investigated. Since there is no analytical solution known to this problem, a empirical study is presented in this dissertation. A real-time analysis has been developed, that considers the complexity of state of the art processors. Over previous work this has the advantage of considering the acceleration techniques of the processor in the preemption of a task.

#### 1.3 Organisation of the Dissertation

The following Chapter will provide an overview on related work in the area of real-time systems while Chapter 3 comprises an introduction to real-time systems and possible monitoring techniques. The models of the embedding system, processor and software is the main theme in Chapter 4. Due to its high importance factor, the operating system software is more closely inspected. Furthermore, a statistical analysis of the worst case execution time, utilising extreme value statistics, is provided. Chapter 4 concludes with

the scheduling proof for systems using state of the art processors. Finally, Chapter 5 is dedicated to the experimental validation of the previously described methods and also concludes this work.

# 2 Related Work

The task of estimating the worst case execution time of a piece of software can be divided into analysing the control flow of the software, estimating the execution time of a given sequence of instructions, and calculating the WCET based on the results of the two previous steps. Additionally, the analysis of the operating system itself, and the effects on the execution of the application software has to be investigated in context of a real-time operating system.

#### 2.1 Control Flow Analysis

The potential control flow of a piece of software can be described using a *control flow graph (CFG)*. The CFG is usually extracted directly from the source, assembly or object code. The missing information in this control flow graph is the specification of feasible paths. A basic necessity is the bound on loop iterations. Additionally, infeasible paths may be excluded from the later search of the worst case execution time. Two basic principles are used in providing this information. Either the user is needed to specify the necessary information or symbolic execution of the code is deployed.

#### 2.1.1 Annotations

Various papers have been published concerning the user supplied information on loop bounds and infeasible paths. One fundamental work referred to by many later publications is [71] by Puschner and Koza. In this work no actual annotations are used, instead the syntax of C has been extended to provide the information. A modified for statement is introduced which accepts the usual arguments of a for statement, plus additional information regarding maximum number of loop iterations or maximum amount of time for the loop, plus additional exception code to be executed when the given bound on time or iterations has been exceeded. Furthermore, *marker* and *scopes* are defined. A scope specifies a range of instructions in the code while a marker, within a scope, denotes how often this particular path may be executed through the marker within one execution of the

associated scope. Markers are not allowed within nested loops. Using this system, the number of paths to be investigated are reduced considerably. A major drawback of the system is the necessity for many coding restrictions, and a simple underlying hardware i. e.; the processor utilises no caches and pipelines. The tool of Park and Shaw presented in [69] prompts the user for information on loop bounds, wherever needed.

Stappert, Ermedahl and Engblohm describe in [77] a more elaborate system where scopes and flow facts are used. The scopes provide a hierarchic description form of the program. The flow facts create restrictions to the possible path combinations like, for example, the number of times a given path may be executed within a loop, or the infeasibility of particular path combinations.

A symbolic expression of the number of loop iterations is used by Colin and Puaut in [20]. This allows the programmer to provide a closer bound on the number of loop iterations, for example, with non rectangular nested loops. In non rectangular nested loops the inner loops are not iterated to their maximum all the time. A classical algorithm providing this property is the bubble sort algorithm, where the number of inner loop iterations decreases with the number of outer loop iterations. The gain can be considerable depending on the nature of the program, but the additional complexity leads to an error prone process of annotating the program which is not easily verified since no functional property of the program is affected. Only a tedious manual check of the provided annotations, or a measured sample execution which exceeds the provided WCET, may reveal errors.

#### 2.1.2 Symbolic execution

The deployment of symbolic execution as compared to manual annotations has the major advantage of avoiding the error prone annotation process, while the largest obstacle is the complexity of the problem itself. Gustafsson and Ermedahl describe in [22] a symbolic execution approach for a subset of C. In order to cope with the complexity, while at the same time avoiding serious overestimations, a mixture of value ranges and value sets are used. Whenever a value cannot be determined to a single value during data flow analysis ranges, or set of values is used as appropriate. A variable may also have both a set of values and a range of possible values.

In [58] and [59] by Lundqvist and Stenstroem the paths are simulated, but the values are either defined exactly or are marked *unknown*. No sets of values or ranges are used, thus the complexity is reduced considerably, even though this reduction is known to be of lesser accuracy. Whenever an if statement is encountered with an *unknown* in the decision statement, both paths have to be analysed. When two branches are joined, a conservative merge of the variable values is done. The memory and register state are joined, but only identical variables render a specific value for future reference of this

variable, all others being assumed as *unknown*. Pipeline effects are considered at these joining points, by adding machine state information. As regards the caches at a join operation, the penalty potentially incurred by the cache state of the path with the shorter WCET is estimated. When this penalty, plus the WCET of the shorter path, is smaller than the WCET of the longer previous path the cache state is taken from the longer path. Otherwise only memory references contained in both joining cache states are considered. This results in many *unknown* references in the caches. At each branch instruction the path with the least progress is chosen for further analysis, thus ensuring that loop bodies are completed before iterating. The extensions to ranges or sets of valuables is relatively easy to implement.

Liu and Gomez use a similar approach in [57]. Here, as well, the value *unknown* is introduced to handle complexity and undetermined path execution. In the first instance, the program is transformed to carry additional parameters which describe the execution properties. These properties provide the number of primitives used by the program. The execution time of these primitives is measured once and this information is used, together with the symbolic evaluation, to provide the WCET. This approach is, however, unsuitable for processors with acceleration techniques.

A slightly different method is presented by Ernst et al. in [88], [87] and [91]. Symbolic execution is used in these papers to detect input dependent, and input independent parts of the program. These properties are used later on in hardware modelling, where input independent parts can be bound much closer to the real WCET than parts which lack this property. The parts are separately analysed by a cycle true processor simulator, when available, or with instruction timing addition for a simple processor architecture.

Healy et al. in [34] focused in bounding the number of loop iterations. First of all, those branch instructions that can affect the number of loop iterations are identified by utilising compiler techniques like computing the dominator tree. Then the conditions under which these branch instructions change direction are computed by utilising compiler optimization techniques like loop unrolling. Next follows a reachability analysis to determine in which iteration a certain branch instruction is actually met. For loop exit conditions, dependent on input variables and loop invariant, the user is prompted to provide bounds on the values of these input variables and the number of iterations is computed. Finally, nested loops, where the number of inner loop iterations directly depends on the outer loop iteration, are considered. The loop bound is provided using a symbolic summation expression.

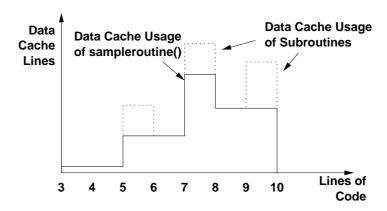

Blieberger, Fahringer and Scholz in [11] use symbolic evaluation to determine the cache usage of an application. To demonstrate this, instrumented C code is evaluated symbolically, yielding a symbolic tracefile which indicates the memory references accessed. By symbolic evaluation a cache hit function, dependent on the input data, is computed.

#### 2.2 Execution Time Estimation

In order to estimate the best and worst case execution time, we can utilize modelling and measurement based approaches. Since these approaches often focus on small portions of code, a third major thrust in research dealing with the computation of the execution time bounds of the whole program out of the execution time bounds of the parts.

#### 2.2.1 Hardware Modelling

The work in this field can be divided into two approaches, that of modelling either simple processors or partial features of more advanced processor.

An analytical model exclusively for caches is the sole focus of Harper, Kerbyson and Nudd in [33]. This approach is limited to rectangular nested loops. In the first step, the cache footprint i. e.; the used cachelines of each memory reference, is computed. The memory references with identical access patterns are grouped into translation groups. Secondly, the cache footprint of the translation groups are computed. Finally, the interference is computed. The authors distinguish between spatial self interference, spatial cross interference and external interference. Self interference is caused when the members of a single array within one loop iteration are referenced in such a way that they preempt each other. The act of members of a single translation group preempting each other is called cross interference. External interference, on the other hand, is present when members of different translation groups force each other out of the cache. The restriction to rectangular loops considerably narrows the application field of this approach.

Narasimhan and Nilsen analyse a pipelined RISC processor in [67]. The presented pipeline simulator is fairly straightforward. The main focus of this paper is the aspect of portability with regard to which data must be provided in order to configure the presented analyser for a given processor.

The branch prediction unit of the Intel Pentium processor was investigated by Colin and Puaut in [20]. The caches provided by the processor are switched off. A classification of the control transfer instructions is introduced and fed into a branch predictor model. No actual modelling of the pipelines, or the execution time, was conducted.

Stappert and Altenbernd model a processor including caches and pipeline, but simplified the analysis by assuming straight-line code in [75] and [76]. According to the authors straight-line code i. e.; code without loops or recursions, is found quite frequently in code produced by automatic code generators. The analysis begins on basic block level and is then extended to handle inter basic block interferences. Part of this work is used as *local low level analysis* in [77] by Stappert, Ermedahl and Engblohm. Here, a 32 bit RISC micro–controller with pipeline, but without caches, is investigated. Loops are broken up

and the basic block responsible for iteration or continuous operation is duplicated. Thus the pipeline analysis of the loop iteration is decoupled from the analysis of the loop exit.

Li, Malik and Wolfe in [54] model a processor with direct mapped instruction cache. The analysis begins at basic block level. Nevertheless, the execution time of a sequence of instructions is assumed to be time invariant, and subroutines are handled as if inlined for multiple calls to this routine. Thus the gain of the instruction cache by multiple calls of a subroutine is voided. A cache conflict graph is used to determine the number of cache hits and misses.

Coloured petri nets are used by Burns Koelmans and Yakolev in [29] to model a super-scalar processor. The instructions are modelled as tokens passing through the petri net. These tokens have source and target dependencies to model the register and memory reference usage. A small non-determinism example extends the model into 4 different execution states which shows the major weakness of the approach due to the fact that the state space explodes with only a small number of indeterminisms.

A case study for WCET analysis for a MIPS R3000/3010 is presented by Hur et al. in [36]. The processor has a pipeline and direct mapped data and instruction caches. Start of the analysis is done on basic block level. With each basic block the pipeline state at the beginning and end of the basic block, and the cache usage, is computed. The cache usage is provided as <code>first\_reference</code> and <code>last\_reference</code>. The term <code>first\_reference</code> indicates the memory references that lead to a cache hit, if already in the cache, while <code>last\_reference</code> provides the cache state after the execution of the basic block. When the paths are resolved the <code>last\_reference</code> of all "executed" basic blocks are merged and used as input for the <code>first\_reference</code> of the succeeding block. A very similar approach to these reference sets of basic blocks is used by Wolf and Ernst in [86]. The memory address of a data access is of the form baseregister plus displacement. The authors classify the data references into three types:

- 1. Global data which is accessed through the global base register i.e.; the memory location is known and fixed.

- 2. Local data referenced through the stack pointer where the actual memory reference is dependent on the calling structure.

- 3. Finally, all other accesses which are assumed to induce two cache misses. One cache miss due to the potential necessary load of the referenced data, and another for a useful cacheline preempted by this reference.

This has been extended in [50] and [52] to determine the intertask preemption delay in multitasking systems (cf. Section 2.4).

In [46] and [45] Kim, Ha and Min try to determine the overestimation sources of WCET

analysis. They consider data caching, instruction caching, pipelining, effects across basic blocks (combines virtually the first three) and the effects of infeasible paths. To analyse the amount of overestimation introduced, by not considering the effects described above, they introduced some switches into the previously described MIPS R3000 simulator in order to be able to switch the consideration of these effects off and on. The impact of the infeasible path analysis is orthogonal to the rest and is therefore handled separately.

In [60] Lundqvist and Stenstroem address timing anomalies in modern processors. They show how a cache miss can speed up execution on processors equipped with out-of-order execution units. In their investigation, they used a reduced PowerPC Simulator derived from *psim* from Cygnus.

The work of Müller et al. starting with the dissertation of Müller [64] over [7] up to the recent publication [65] focusses on the simulation of caches with special regard on instruction caches. All cache accesses are classified into:

**Always Miss**: this memory access will never hit the cache.

**Always Hit**: this memory access will always hit the cache.

**First Miss**: within execution of this program/loop, the first access will miss and all subsequent accesses will hit the cache.

**First Hit**: within execution of this program/loop only the first access will hit and all other accesses will miss the cache.

For this classification *abstract cache states (ACS)* are introduced. These ACS describe all the memory references that might be in the cache at a given point of the program. It contains the addresses of the memory references and the corresponding age. The age is necessary for the least recently used preemption computation for the cachelines. Each basic block takes an ACS as an input and transforms it in accordance with the memory references inside the basic block. At a junction point, where two or more paths are joined, the ACS of all paths are combined in such a way that all memory references that are potentially held in a cacheline at this point are included into the the joint ACS. The modelled cache has only a size of 256 bytes.

The fundamental theory of the work above has been used by Theiling, Ferdinand and Wilhelm as a basis in [79]. They have developed three analysis steps to determine the type of memory reference with regards to the classification of memory references above. The *must analysis* abstracts the age of a memory reference i.e. the minimum lifetime of this reference. The join operation after alternative paths takes only those memory references into account, which are contained in the abstract cache states of all paths joined at this point. The age of these references is assigned from the age of the oldest i.e.; most likely to be replaced reference in the joint ACS. This allows the detection of always

hits. The *may analysis* focus on identifying always misses. The join operator takes all memory references potentially held in the cache. If the memory references of two paths to be joint have a different age, the minimum age is taken. The *persitance analysis* is utilised to detect first misses. The persitance analysis is a blend between must and may analysis. The join operation takes all memory references as in the may analysis, but picks the oldest age of duplicate entries as with the the must analysis. Additionally, the persistance analysis tags memory references which have been removed from the cache. If a memory reference is not an *always hit*, but has not been removed out of the cache then it has to be a *first miss access*.

A Motorola PowerPC with pipelines and caches but without caches is the target platform for Hergenhan and Rosenstiel in [35]. Their analysing tool GROMIT takes assembler text, a simplified processor description and a path relation file as input. The latter provides essentially all necessary control flow information. A cache conflict graph and cache state transition graph are deployed for analysis of the cache behaviour. The authors provide a method to make a tradeoff between accuracy and simulation time. The output is an integer linear programming problem description (cf. Section 2.2.3).

The problem of insufficient and flawed processor documentation is tackled by Atanassov, Kirner and Puschner in [8]. To provide a reliable hardware model they utilise measurements to complete and either correct, or proof the information regarding the execution time of instructions as gathered out of the processor manual. The Infineon C167 used processor is relatively simple since it has no caches or pipelines. After building a model of the execution times of instructions this model is again validated against real hardware by executing programs and comparing the results with that of the theoretical work.

#### 2.2.2 Measurement Approach

Measurement based approaches have experienced a revival within the last couple of years. Years ago the research focused on getting reliable information about worst case execution time by means of measurements. As processors tended to be more complex, using pipelines and having data dependent execution times for instructions, this was no longer regarded feasible, with the result that the theoretic models were developed. Now again complexity issues make those exact models almost infeasible for state of the art processors. Additionally, it has been perceived that the documentation of the processors is often inaccurate or incomplete.

A very simplistic processor without pipeline and caches is the target platform of Lindgren in [56]. The paths of the program are instrumented by ADD opcodes to specific variables identified with a path. Only a number of measurements with random input data are taken and, together with the path counter, provide an linear equations system which is then solved. By intelligent placement of these instrumentations the amount of variables can

be reduced drastically. For example, a piece of linear code succeeded by an alternative needs only one counter for the linear code, and another within one of the two alternative paths. More elaborate variants are possible. The gcov utility of the GNU gcc compiler uses a similar technique.

The performance monitoring hardware provided by the Motorola PowerPC 604e processor is utilised to estimate the execution time in [61] by Corti, Brega, and Gross. The ultimate target of this approach is not to put an upper bound on the WCET but to approximate the execution time for a given percentage of executions of the program i.e.; a quality of service. The scheduler of their system will take care that a task using more than it's alloted time will be prematurely terminated. All instructions are measured under best case conditions. The results are used to provide a cycle per instruction metric. A given program is then run and the performance monitoring hardware counts the number of issued instructions, cache misses and mispredicted branches. This data is used to compute an estimate on the worst case execution time.

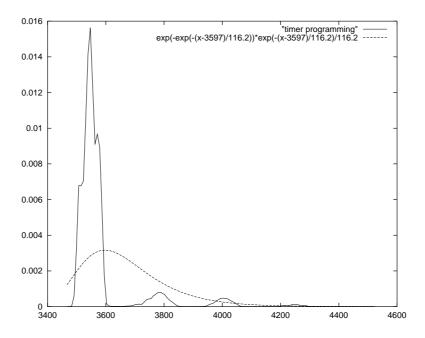

An extreme value statistics approach is described by Burns and Edgar in [13], [14] and [15]. Extreme value statistics are used in civil engineering in predecting worst case weather or flood scenarios. This approach takes no information about the nature of the executed program. A large number of measurements are taken and then an extreme value statistics probability density function is matched to the measured execution time. With this probability density function it is possible to provide an bound on the WCET according to a required confidence in this value. This approach relies solely on the statistical properties of the program since no worst case state and no worst case input data is used. Additionally, code and data is preloaded into the caches of the processor. The concept of extreme value statistics is explained in greater detail in Section 4.6.

Müller and Wegener compare an accurate timing model, as presented in the previous section, with a genetic algorithm testing approach in [66]. The underlying idea of the approach is to produce an estimate on the worst case execution time by trying to find the input producing the WCET. One necessity for a useful deployment of genetic algorithms on a particular problem, is the tuning of a large number of parameters. Here it is the number of input parameters to the program. A SPARC IPX architecture has been used for the experiments. The caches have been switched off, due to the fact that Rational Quantify, the tool used for the measurements, does not take the effect of caches into account. Quantify performs cycle-level timing through object code instrumentation. Thus overhead by the operating system was ruled out and repeated runs, with the same parameter set, resulted in identical execution time measured. The results showed that evolutional testings are unsuitable for providing secure bounds on the execution time of a program. This is due to the fact that the parameter/fitness space in the case of a program is a set of plains which may have no direct connection to each other, for example a given if condition, where an input parameter is compared against a fixed value, and is evaluated as either true or false. On the contrary, genetic algorithms work best with a contignous fitness/paramter space which may have a limited number of salti.

Writes to an address monitored by a logic analyser are used by Wolf, Kruse, and Ernst in [89] to determine the execution time. The write addresses named trigger points inserted in the source code have two functions. On one hand the trigger points allow for extraction of the path which has been taken by the program, on the other hand the logic analyser is capable of providing cycle true values for the execution time between two consecutive measurement points. Thus a segment wise measurement with exact control of the taken paths is possible.

#### 2.2.3 Calculation Methods

Most of the approaches for WCET estimation are based on providing meta results as regards the WCET estimation of partial constructs of the program. These constructs may be individual opcodes, basic blocks or a group of basic blocks. The WCET of the program is computed using either tree based, path based or implicit path enumeration based approaches. Syntactical parse trees, as used by compilers, are usually used for the tree based approaches. Using a bottom up method each edge in the tree is assigned a execution time, and the overall worst case execution time is computed by summing up the edges according to the rules given by the control flow analysis. The work of Puschner and Koza in [71] resorts to this comparably simple method.

The path based approaches search all potential execution paths explicitely given for the one with the longest WCET. This method works well for flow restrictions within one nesting level, but gets rather complicated when the restrictions stretch across different nesting levels. Stappert and Altenbernd use this path based approach in [76]. As described in the previous section, the approach computes the individual WCET of all paths in non-looping software. After this, k paths which have the greatest WCET are checked for feasibility. If one or more feasible paths are found, the largest WCET is provided as WCET of the programm. Otherwise the shortest WCET of the k paths is taken as an upper bound on the WCET. This has been extended by Stappert et al. in [77] to handle each nesting level of a loop in itself. The flow information is used to limit the number of paths to be analysed. The Dijkstra algorithm is deployed to search for the longest path in the program.

Lundqvist and Stenstroem use a comparably simple technique for their machine modelling approach in [58] and [59]. To bound the number of paths to be investigated the largest WCET of all the paths joining in one point inside the program is taken. The handling of caches has been explained previously in the hardware modelling section.

As regards the IPET approaches, each unit, usually a basic block, is provided with a time variable  $WCET_i$  and a counter  $x_i$ . With respect to the constraints reflecting the results of

potential control flow, the following equation is maximized:

$$WCET_{sum} = \sum WCET_i * x_i$$

(2.1)

Li, Malik and Wolfe [54] were the first to name this technique. An example of the estimation of execution counts is that, the execution count of two sequential basic blocks are identical. Given an alternative, the sum of the execution counts of the alternatives equals the execution count of the preceding block. Further restrictions are loop bounds, or mutual exclusive parts. The result of this description is a large number of linear equations and linear inequalities. These can be reduced to an *integer linear programming (ILP)* problem, which may be solved using existing ILP solvers. Another example of an IPET based approach is the graph theoretical method of Puschner and v. Schedl in [72]. The authors assume the execution time of basic blocks to be known and constant. This excludes all processors with pipelines and caches. The graph is used for loop detection and finally mapped to an ILP problem.

Theiling et al. [79] use a virtual loop unrolling and virtual functions inlining method to enhance the accuracy of their execution time estimate in the presence of caches and pipelines. The result is still an ILP as in [54]. The approach of Hergenhan and Rosenstiel in [35] is similar.

The basic idea of the approach presented by Wall et al. in [82] is to assign each Ada-Source construct a worst and best case execution time, and to compute the WCET and BCET of the whole program by linear superposition of the WCET and BCET of the constructs. To identify the WCET and BCET measurements of reference programs with a consecutive regression analysis is used. As processor, an Motorola 68030 derivate was used which has not the problem of caches and complex pipeline structures.

## 2.3 Operating System Analysis

A general purpose operating system is the target of the profiling tool Kitrace presented Kuenning in [49]. By insertion of TRAP instructions in the kernel code, a provided routine is called whenever one of the instrumented pieces of code is reached. In the provided interrupt service routine, hardware counter are utilised to measure the time. In contrast to the approach presented in this work no steps are taken to produce the worst case situation instead the measurement objective is to produce average performance measures for operating system services. This approach utilised Motorola, Intel i386 and 68000 on Sun OS 4.1.1 as target processors.

The focus of Colin and Puaut in [21] lies on the applicability analysis of their WCET analysis tool on the operating system kernel. The main problems the authors encountered are the dynamic features in general, and of these especially the memory management.

The memory management allows dynamic memory allocation and deallocation. As regards the allocation of heap memory, the search tries to provide a continuous piece of free memory which suits the allocation request. This results in very pessimistic assumptions for memory allocation requests. A good part of RTEMS could not be automatically analysed by their tool, and had to be thoroughly manually analysed and then modified to be suitable for the tool. The overall result of the work is that automatic analysis methods can also be applied to operating system code, but that usually a lot of manual work is still necessary, since the constructs of the operating system supporting the dynamic features of the operating system are not easily accessible to automatic analysis.

#### 2.4 Scheduling Analysis

In the literature a huge amount of scheduling schemes and corresponding proof methods are proposed. Most of these suffer from lack of support for non zero task switching times. These non zero task switching times have two origins. One is the time needed for the scheduling analysis itself, the other stems from the disruption of the working set within the caches and the stalls in the pipeline (for further examples refer Section 4.2.1) on modern processors. The consideration of schedulability analysis methods will be limited to those approaches supporting these effects.

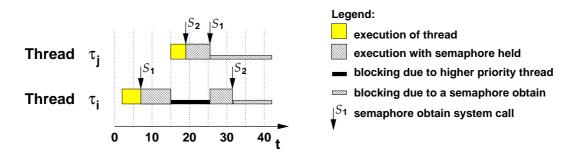

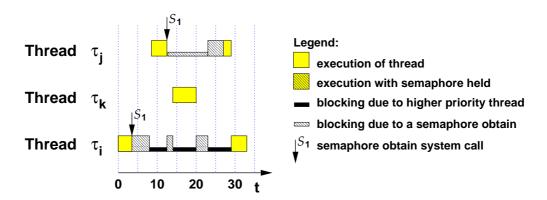

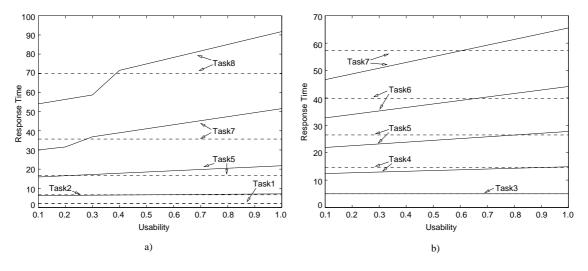

Busquets et al. provide a simple formula, and the corresponding proof, for a simple fixed priority scheduling scheme in [16], [17], and [18]. A basic requirement for the applicability of this approach is that the deadline of a task  $\tau_j$  is shorter than the interarrival time of the task  $T_j$ . The approach tries to allocate a time window  $w_i$  for the execution of the whole task  $\tau_i$ , including the WCET of the isolated task  $C_i$ , all blocking times  $B_i$ , preemptions by tasks of higher priorities  $\mathbf{H}_i$  and the corresponding penalty for the scheduling algorithm and disruption of the cache  $\gamma_j$  for each preemption. The cache preemption in this  $\gamma_j$  is computed solely by the cache usage of the preempting task. The preempted task is not considered for this computation. The resulting equation for the schedulability analysis is provided as follows:

$$w_i^{n+1} = C_i + B_i + \sum_{\tau_j \in \mathbf{H}_i} \left\lceil \frac{w_i^n}{T_j} \right\rceil * \left( C_j + \gamma_j \right)$$

(2.2)

An initial  $w_i^0$  can be arbitrarily chosen. The formula computes a new execution window  $w_i^1$  by considering all effects that may arise during the initial set time window. This process is iteratively repeated, until either the resulting window  $w_i^{n+1}$  exceeds the deadline  $D_i$  of the task  $\tau_i$  i.e.; completion of task  $\tau_i$  cannot be guaranteed before its deadline, or the window stops to increase i.e.  $w_i^{n+1} = w_i^n$ . In the latter case the execution window corresponds to the response time of the task i.e.  $R_i = w_i^n$ .

Lee et al. present in [50] and [52] an integral approach for modelling the processor with caches and the schedulability analysis. The cache related preemption delay is bound by inspecting exactly the cache behaviour of the different tasks, and compute the amount of cachelines of task  $\tau_i$  which might actually be dislocated from the cache due to the preemption of task  $\tau_i$  by  $\tau_j$ . The interactions are presented as an equation system which are solved by employing an ILP approach.

# 3 Real-time and Monitoring

#### 3.1 Real-time

The term *real-time system* is often confused with *extremely fast system*, but a real-time system is actually defined by time constraints which can be in any given order of magnitude. Most technical systems, have such time constraints which usually take the following form:

*The result has to be delivered within x seconds after the triggering event!*

Such time constraints are called *relative deadlines* or simply deadlines. Examples of such deadlines can be as short as some tens of nano seconds for the inter bit timing of a 1 MBit/s CAN controller (Controller Area Network) or as large as several hours for a weather forecast system.

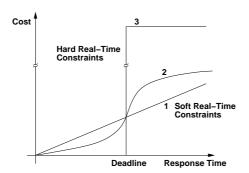

Because of the central role of time constraints in real-time systems, these systems are classified according to the type of time constraints. The first class of real-time systems are the *soft real-time* systems. This class covers those systems where a miss of a deadline results in degraded performance, and/or the increasing of costs. Examples of this kind of deadline would be, for example, the response time of an entertainment system (e. g. car radio) after pushing a button, or a stall in a production line due to a communication timeout and retransmission. While the first leads to reduced customer satisfaction and a possible loss in market share, the second leads to direct loss of production output (return of interest). Most systems belong to the soft real-time systems. Figure 3.1 shows the development of costs versus time in real-time systems. With soft real-time systems (line 1 and 2), the miss of a deadline simply leads to an increase in cost. In the case of most of those systems, a deadline miss can be tolerated, as long as the probability of such a miss is less than a given value.

The second class are the *firm real-time* systems. In these systems, the miss of a deadline leads to the result becoming worthless. An example of such a system is a weather forecast system, where the result becomes void no later than when the forecasting horizon has passed.

Figure 3.1: Cost Function of real-time-Tasks [30]

The *hard real-time* systems build the third and last category. A miss of a deadline here is followed by more or less catastrophic consequences. The consequence is usually loss of life or, at the very least a serious amount of money. We think here of an X-by-wire system in vehicles and planes, or of simple things like the destruction of a machine and the following halt of a complete production line. Line 3 in Figure 3.1 shows the enormous jump in costs. A deadline violation is considered fatal and cannot be tolerated.

#### 3.2 Monitoring

A monitor is a tool, or a set of tools, that facilitate analytic measurements in observing a given system. The goal of these observations is usually the performance analysis and optimisation, or the surveillance of the system. The reason for the latter may be a measure of safety to avoid critical system states or unauthorised access. In the following the focus will be set on performance monitoring as part of the development process.

There are a number of major questions which have to be answered in order to to decide which monitoring scheme should be used.

- 1. What information is pertinent to the measurement objective?

- 2. When or under what condition should the information be gathered?

- 3. How to obtain the desired data and what is the impact of the method?

Identifying the measurement objective, and the relevant data needed to reach this objective is the first step to building a monitor. In the literature the focus is often set on measuring and optimising the performance of multiuser computer systems (e. g. [24], [78], and [25]). The relevant data in this case is the number of user processes running

concurrently, the amount of computation time consumed by the operating system, and the amount of time spent waiting for external hardware (communication and IO).

Generally, the objective is to gather information about either system states or events. In the case of events, this may be the number of events in a given interval or the inter arrival time between events. Examples of such monitor events are the occurrence of an interrupt, or access to a particular piece of hardware. In the case of system states, the basic factors are the probability or the duration of a specific state. Typical examples of relevant system states may be the number of users in a multiuser system, or the execution of the idle task in a simple multitasking system. The work of Ferrari et al. in [25] focuses on state observation for tuning and optimisation purposes. Systems with a state based monitoring objective can be treated as an system with event objective, whereas a change in the system state is defined as an event.

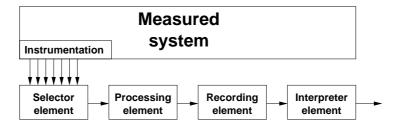

Figure 3.2: Structural Elements of a Monitor [78]

Figure 3.2 shows the typical structure of a monitoring system. The system under investigation is instrumented in a way, to produce the data needed. That may be for example some additional code in the software, or the connector to the system bus. The selector element serves as a filter, focussing the measurements towards specific relevant data. In the case of the bus-monitor, this may be the detection of access to a particular memory address. The processing element brings all the relevant data together and in some cases performs data preprocessing, while the recording element is used to store the data to a suitable device. This may be, for example, a memory portion or a hard disc drive. The data stored consists usually of the event or system state type and possibly a times tamp and/or additional values of variables, or registers of interest. The interpretation and visualisation of the accumulated measurement data is usually done off line. In cases where this is done online, it is often executed on an additional computer, to avoid the commonly large impact this part of the operation would have on the measured system.

#### 3.2.1 Event Detection

The question "when to sample" is closely related to the potential data to be gained from monitoring. Detecting an event to sample the relevant data is one possibility to achieve

this. Such a monitor is said to be *event-driven* and the data produced by this mechanism is called an *event trace*. Events can be classified into software and related events called *software events* and *hardware events*. A software event occurs when one of a set of certain points in code is executed, e.g. the start of an I/O-routine, or the value of a variable being within a given range. A hardware event may, or may not be, directly dependent on the logical content of a piece of software executed but consists of the appearance of a signal constellation in the circuitry of a system component. Typical examples for hardware events are a cycle stealing DMA request or the change of state of a photo sensor. Many hardware events generate a corresponding software event like an interrupt request and vice versa a specific piece of code which is recognisable as an opcode fetch of a specific address.

It is usually easier not to build an event detector for every single event type but to trigger instead on event groups. This may be the occurrence of, for example, any interrupt instead of two or more specific ones or simply avoiding to trigger on a complex signal pattern and using a less complex pattern while taking into account that there will be an additional registration of events which are of no interest regarding the measurement objective. This corresponds to a strongly reduced functionality of the selector unit in Figure 3.2 and is called *full trace monitoring*. The concept of full trace monitoring has several drawbacks. First of all the impact on the system under test has to be considered. In addition to this, the amount of data to be processed increases very quickly thus producing problems (e. g. the rapid filling of available buffer space and the problem of pushing the data to a mass storage system). In order to avoid these problems, it is usually reasonable to make the event trace selective. But even without full trace monitoring the amount of data accumulated is often considerable.

There are two basic fields of application for event driven monitors. The *count mode* and the *interval mode*. In the count mode the number of events of a given kind, which occurred in a given interval, are of basic interest. An example of such measurement objectives would be to get a statistical grip of interrupt activity. In the interval mode for each event the type of the event and the time, this particular event occurred, is stored. The time is usually relative to the first event or system start. A sample application field is used to extract the amount of time a system is persistent in a given state.

#### 3.2.2 Statistical Sampling

The design of an event detection mechanism, as described in the previous section, is usually very time consuming. As an alternative method statistic sampling can be utilised. Unfortunately as the name implies only statistical statements can be derived from these, i. e.; it is only applicable when the exact sequence and number of occurrences of a given state is not needed. In contrast to the event monitoring, which provides all the relevant

data for the monitoring objective, only a subset of the system is taken into account. This subset is defined by the points in time the samples are drawn.

The state of the system may be sampled either in periodic, or in statistic intervals, or in periodic intervals with a statistic deviation. While the periodic intervals have the problem of potential aliasing effects in the observation, the mere statistical approach suffers from the fact, that a local burst of samples may produce a completely wrong view of the systems properties. To avoid both problems the two methods are often combined using periodic intervals with statistic variation. Thus the aliasing effect is avoided while observing the system. The major advantages of this method is the usually simple implementation of such a monitor, and the comparably small impact on the system. On the other hand, the method degrades considerably in the face of system states, which are seldom reached or which are only observable for a very short time. In the presence of such states only two ways remain to observe and gain statistical relevance for these states. Either the sampling rate or the test interval have to be increased. While in the first case the impact on the measurement object will usually rise, the necessary extension of the test interval is often very painful and not feasible. In both cases the data volume that needs to be handled increases considerably.

Since statistical sampling can be done using an event driven monitor in combination with an induced event load, the main focus in the further discussion will be laid on event driven monitors.

#### 3.2.3 Hardware Monitoring

The main characteristics of a hardware monitor is that they are external to the system under test. The connection of hardware monitors to the system is realised by high impedance *probes* (see also figure 3.3). Thus hardware monitors for digital systems do not need any of the resources of the system under test and usually imply virtually no influence to the measured system at all. However even the high impedance probes of the monitor add to the electrical load to the signal and, therefore alter the timely behaviour of the signals slightly. In modern, fast computer systems, this minimum change at critical points of observation can lead to random errors or completely inhibit the system's operation. These critical points obviously need to be eliminated from the list of observable signals. Thus, generally, it can be assumed that hardware monitors are systematically induced and more accurate than software or hybrid monitors.

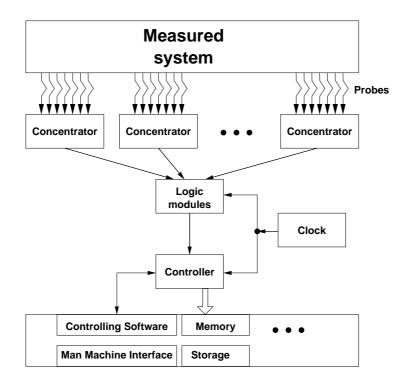

The probes may be connected to *concentrators*, or in simpler monitors fed directly to the *logic modules*. The concentrators collect the various signals from the probes and transform these to signals compatible with the tools internal structure. It is often possible to switch the impedance of the probes as deemed necessary, by sending control commands to the concentrators. The logic modules implement the event filters by logically

Figure 3.3: Elements of a Hardware Monitor [25]

combining the signals from the probes as specified by the user. The complexity of the capabilities of the logic modules varies vastly from detection of a simple combination of a number of input signals, the combination of input signals to numerical values and tracking of the, for example, *less*, *greater*, *between limits* type, to the congregation of rather complex signal patterns over time. In older systems the logic elements were basically plug boards, while in modern systems programmable logic devices like FPGAs programmed at reset by static RAM are used. The clock in Figure 3.3 is necessary for synchronising the incoming data. The task of the *controller* is to transfer the relevant data to the main memory.

Hardware monitors are often built on the basis of personal computers. This has several advantages. First of all, this frees the developer of a hardware monitor from having to design of the basic system which usually consists, besides other less important things, of a user interface, storage facilities and considerable memory space. The storage facilities are usually needed to file away the enormous amount of data for later processing which often exceeds an economical legitimate amount of RAM. To fill the gap between the main memory and the controller, the controller often implements a small buffer and transfers its contents via direct memory access (DMA) to the main memory.

Logic analysers are often used as implementations of hardware monitors, since they are

equipped with all necessary elements i.e. the probes, triggering logic, memory and the user interface, but a given logic analyser is only suitable as a hardware monitor if it provides the essential elements of counters or interval measurement.

An example of a hardware monitor is described in [47]. Klar et al. focus on monitoring of distributed systems by utilising the self built, event driven hardware monitor *ZM4*. For evaluation and correlation of the measured data the tool *Simple* is deployed.

# 3.2.4 Software Monitoring

As the term software monitors implies these tools are based on software technology as opposed to hardware monitors. To make a software monitor work, extra code has to be inserted into the system under test. There are three possible ways to do this:

- 1. Modification of the software under test.

- 2. Modification of the operating system or system task.

- 3. Addition of a task.

The method chosen depends on the measurement objective. In the following an exclusion is assumed, whenever the method is not suitable for measurement. The third method which simply involves adding a task or program is usually preferred, since it is easy to add if required and easy to remove if not. In this way, the integrity of the application software and the operating system is maintained. This kind of tool requires appropriate interfaces to application software and operating system to gather the needed data. An unfortunate limitation of this method is that it will almost always be restricted to the class of monitoring objectives that allow sampling techniques.

The second method is used whenever the required data is not accessible to user tasks. Advantages of the extension portion in the operating system are the accessibility of the memory of all tasks and the easy transition from measurement to production code for the application software. A major reason for non-applicability of this method is that commercial real-time operating systems are usually delivered without source code and thus a developer has no means to implement the necessary extensions.

The last possibility, or first method, can also be seen as the use of *software probes*. Similar to the hardware monitors, the probes are placed at critical points in the software to be measured. The freedom of this process puts forth an enormous application area, however, the placement of these probes is critical, time consuming and must be redone with every new application under test. Another problem is that of accessibility of the necessary hardware. Modern processors often supply clock cycle counters, which are very

useful in getting an exact time for software monitoring. However, these cycle counters are, in many cases, only accessible in the supervisor mode of the CPU. This mode is often reserved for the operating system. In the case of real-time systems the application software is often organised in threads rather than in tasks. The basic difference between a thread and a task is that each fully fledged task has its own separate and protected memory area whereas threads share their memory. The threads of a real-time systems usually run without memory protection, in the supervisor mode, to avoid the considerable task switching times implied with the memory protection and the change of the priority level while evoking system calls.

Commercial operating systems, even without working with the thread mechanism, allow the implementation of *interrupt service routines*. Thus the necessary access can be implemented via a trap mechanism i. e. a software generated interrupt. The use of a function call instead of a trap within a thread based operating system allows greater accuracy since the switching time from user to kernel mode is afflicted with indeterminism.

The ease of obtaining descriptive data is an outstanding advantage of software monitors. Because of this, much cryptic post processing needed to reconstruct the data can be avoided. Since the software tool can access the main memory, usually all relevant data can be gathered. As opposed to this hardware monitors depend on the information that passes on system buses.

Software monitors have, in contrast to hardware monitors, the undesirable effect of altering the system under test in a non-obvious way. This change in the system is called *monitoring artifact*. In general, the changes introduced by the monitor to the system require memory, possibly I/O resources, CPU time and alter the state of the acceleration techniques of the CPU (cf. Section 4.2.1).

Further information to software monitors can be found in Section 5.2. of [25].

# 3.2.5 Hybrid Monitoring

Hybrid monitors combine the advantages of both software and hardware monitors. Event detection is implemented using software probes. Thus, the great flexibility of software monitors is maintained. The preprocessing of relevant data is implemented in the hardware part of the monitor, and therefore reduces the impact of the monitor on the system under test.

The event detection is realised in two parts. One is by the insertion of additional code like in the software monitors described before. These probes trigger the hardware part either by a set of general purpose I/O pins of the processor, or by a memory access to a specific memory. The latter can be used to provide additional information to the hardware monitor, where a write access is usually used for that purpose. The hardware

part combines this information with the data gathered in parallel by hardware probes, and is also responsible for the recording of the gathered data.

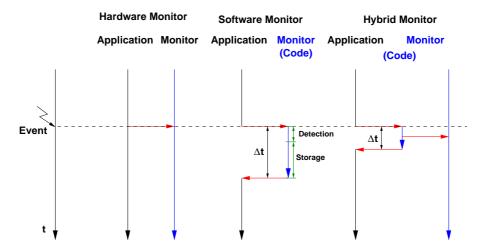

Figure 3.4: Temporal Impact of Monitor Types [63]

Figure 3.4 depicts the impact of the different monitoring schemes during the time the execution of the application is suspended. The hardware monitor induces no such impact, whereas hybrid monitors generate a rather small suspension time on the application software and software monitors suffer considerably from this effect. It should be noted that the actual suspension time is strongly correlated to the amount of data gathered in the software part of the monitor.

Liba Svobodova covers hybrid monitors in greater detail in Section 6.7. in [78].

Despite the greater accuracy of hardware monitors, the simpler application of software monitors and the blend of interests in the intermediate hybrid monitors a comparison can not be made assuming they had equivalent fields of application. Some monitor tasks can only be performed by using software and some only by utilising hardware monitors. Even if all monitor types were possible, one monitor type would usually be superior to the other from either a technical, or economical point of view. This is induced by the different types of events, which must be detected, and the varying depth of information needed.

The measurement objective is to retrieve the worst case time of a given piece of code. This excludes the sampling monitor from the list, since it is only suitable for retrieving statistical information on the run-time of code. Event driven monitoring on the other hand is able to provide the necessary information i. e.; the interval time between two measurement points within a program.

A basic desired functionality of the measurement is to provide the given piece of code

with a worst case scenario of processor state. Taking this into consideration, one can distinguish between two kind of processors:

- Processors with caches and other acceleration techniques. In general, processors

with acceleration techniques like branch prediction and speculative execution use

these techniques only in addition to caches. These kind of processors are used

whenever a serious amount of computational work needs to be done. This might

be a driving assistance system or a telecommunication calling centre.

- Processors providing only simple pipelining, or no acceleration techniques at all. These are used often in mass market products with low computational demands like mobile phones (excluding the digital signal processing part) or the engine control for a car.

The final decision as to which kind of monitor to choose, strongly depends on which of the classes described above the processor belongs to. In the case of a simple pipelining processor like the Motorola MC68332, there is usually no need for complex actions to provide the worst case state of the processor. On the other hand, the execution of a instruction at a specific address in memory can be easily tracked by utilising a hardware monitor. To minimise the impact of measurement for this kind of processor hardware monitoring will usually be chosen. Logic analysers are utilised in most cases like this, in order to avoid having to develope a specific monitor.

To provide the worst case state for one of the more complex processors, it is usually necessary to insert additional code into the software under test. A hardware monitor might be able to detect the start and end of a piece of code on some processors, but the additional inserted code necessary negates the advantage of not having to instrument the software. The major advantage of a hybrid monitor is in reducing the impact of the software instrumentation. The advantage of this monitor for software detection and hardware sampling is again made void by the additional instrumentation used to provide the worst case state of the processor.

A sepcial feature available with many modern processors makes a different hybrid monitor possible: hardware detection and software sampling can be implemented by utilising debug registers, which generate an interrupt whenever an opcode at a specific address is executed. The following processor descriptions will therefore focus on relevant facts for event driven software and hybrid monitors.

# 4 Models

For an embedded system, there are three basic parts, which need to be modelled. One is the software which has to cover everything from application software to run-time system. Another is the hardware the software is running on i.e.; the controlling computer with processor busses and peripheral units. The last is the environment the system is embedded in. While the former mentioned models are essential for the measurement method itself, the last is only of marginal relevance.

# 4.1 Model of Embedding Process

Real-time computing systems are usually deployed as the controlling instance of parts of their environment. One can think of examples like a drive by wire unit in a car, a quality control in an assembly line, or a video based obstacle avoidance system on a mobile robot. The connections to the environment consist of a number of sensors and actors.

In general, the deadlines are specified as the interval from detection on a set of inputs, to the reaction on a set of outputs. The processor is involved only from the time an input is registered, which is usually an interrupt, to the point where the write command to external hardware is issued. To perform a real-time analysis, shortened deadlines have to be used which only cover the time between the assertion on an interrupt and the write command. To determine the extreme response times computed by the real-time analysis (see Section 4.7), the maximum number of interrupts within a given interval is needed. This is not only limited to interrupts issued from external sensors, it must also be applied to interrupts of components of the computer system itself like, for example, timers, the hard disc controller or the keyboard.

One method of providing these values is by specifying the minimum *inter arrival time* between two interrupts of the same type. For the real-time analysis which is exemplified in Section 4.7 it is assumed that these interrupts appear at the rate specified by this minimum inter arrival time. Situations where interrupt bursts have long intervals between each burst lead to severe over-estimation of the induced load on the machine.

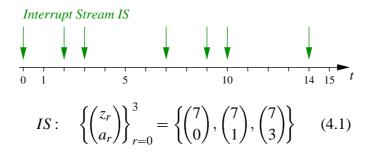

To circumvent this drawback the notion of event streams (ES) was introduced by Gresser [31] and [32] and further utilised in [70]. In order to avoid confusion with the term event of the monitor nomenclature and due to the fact that these kind of events usually generate interrupt requests, this descriptions will further on be referred as interrupt streams or IS. Interrupt streams are a formal means to express the maximum possible number i of interrupts of a certain type within an interval  $a_r$ , with the cycle time  $z_r$ .

Figure 4.1: Interrupt Stream Example[70]

An example of a possible interrupt stream and its notation is given in Figure 4.1. This corresponds to the following statements:

- 1. At most 1 interrupt within interval 0 i.e.; no simultaneous interrupts, as there is only one tuple given with  $a_r = 0$ .

- 2. Within any interval of 1 time unit chosen of the stream there will be at most 2 interrupts. This is denoted by the number of tuples with  $a_r \le 1$ .

- 3. At most 3 interrupts within any interval of 3 time units.

- 4. The pattern is repeated no sooner then every 7 time units.

The simple case of an interrupt with only a minimal distance can be expressed by a single tuple specifying the period and an interval of 0. A tuple with a period  $z_r = \infty$  can used to model unique interrupts after power on or during a long period of inactivity. In [31] to take an example, an elevator is chosen where initially the request buttons at all levels may be pressed simultaneously. Afterwards the request buttons lead to no more interrupts until the previous request has been served.

In order to provide the maximum possible number of interrupts of type i within a given interval T the following equation is used:

$$E_i(T) = \sum_{r=1}^{s} \begin{cases} 0 : T < a_r \\ \left\lfloor \frac{T - a_r}{z_r} + 1 \right\rfloor : T \ge a_r \land z_r < \infty \\ 1 : T \ge a_r \land z_r = \infty \end{cases}$$

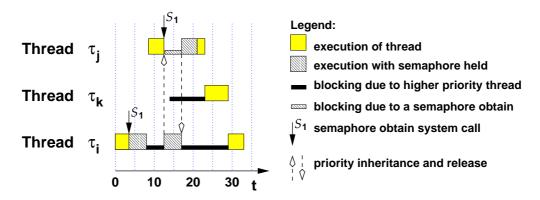

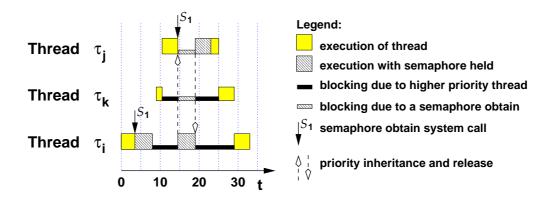

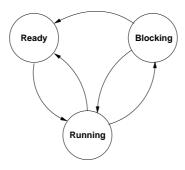

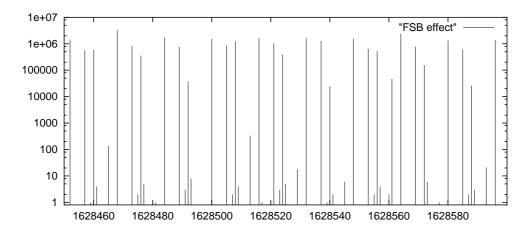

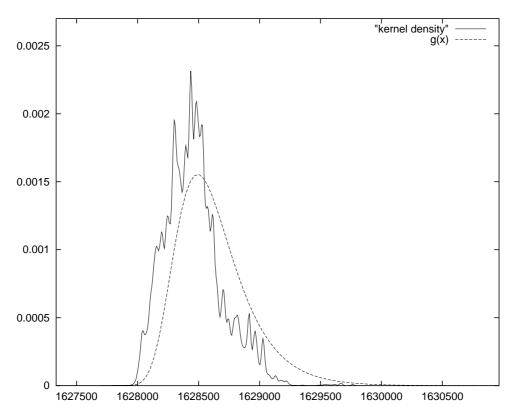

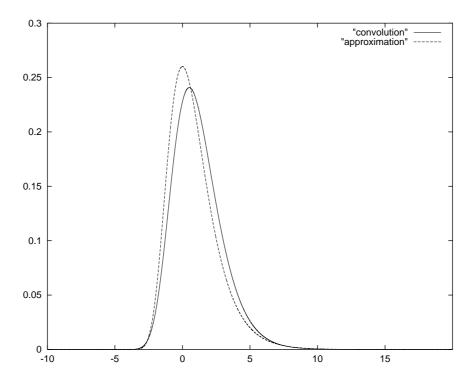

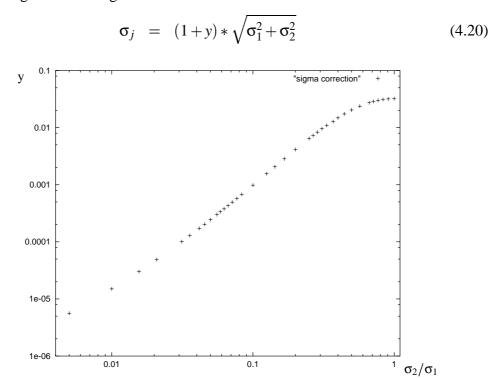

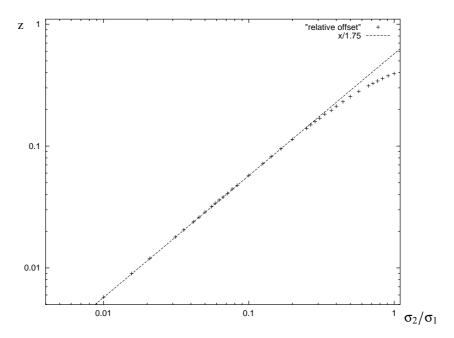

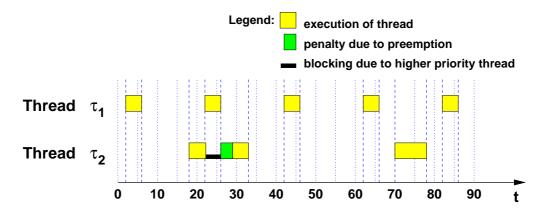

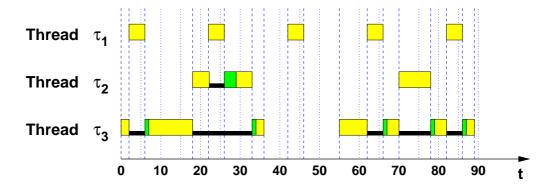

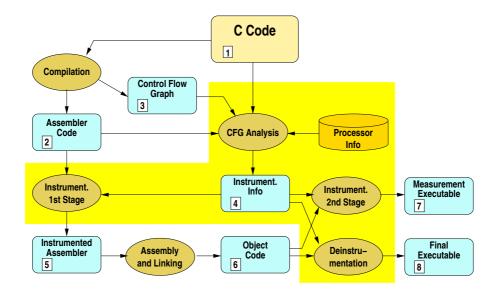

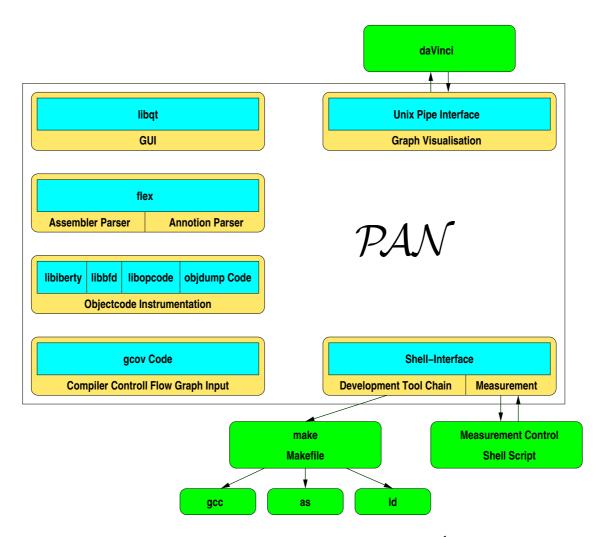

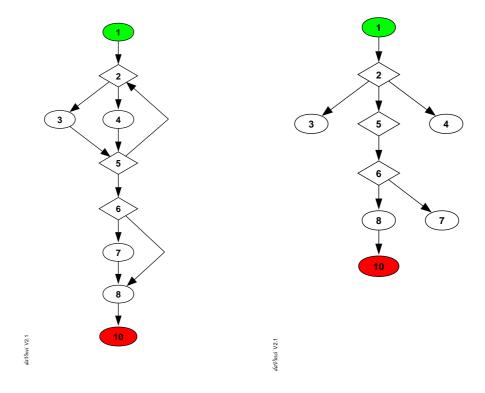

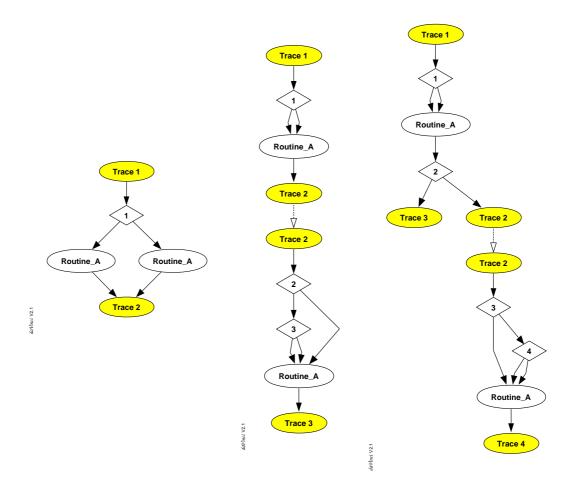

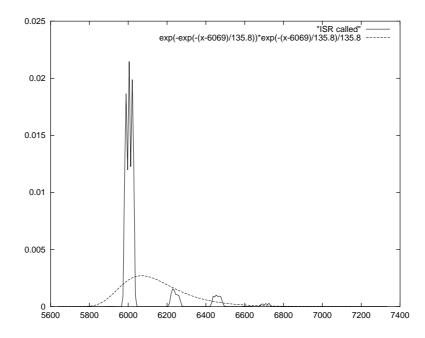

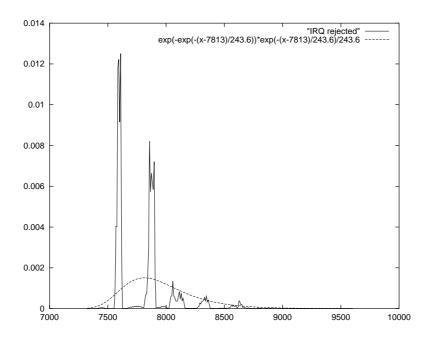

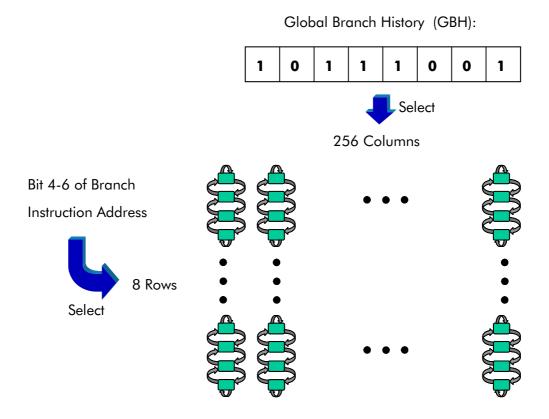

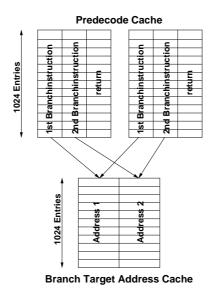

(4.2)