Technische Universität München Lehrstuhl für Technische Elektronik Fachgebiet Halbleiterproduktionstechnik

## Complementary Tunneling-FETs (CTFET) in CMOS Technology

### Peng-Fei Wang

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

| Vorsitzender:            | UnivProf. P. Lugli, Ph. D.            |

|--------------------------|---------------------------------------|

| Prüfer der Dissertation: | 1. UnivProf. Dr. Ing. W. Hansch       |

|                          | 2. UnivProf. Dr. rer. nat. I. Eisele, |

|                          | Universität der Bundeswehr München    |

Die Dissertation wurde am 10.11.2003 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 10.12.2003 angenommen.

to my wife Jing Zhao

## Abstract

The short channel effects (SCE) are becoming serious problems as the metal oxide semiconductor field effect transistor (MOSFET) scales down to the deep sub-micron dimension. Recently, a silicon tunneling transistor called TFET was proposed as the candidate of MOSFET. This transistor realizes the gate-controlled tunneling at room temperature. As a novel device, there are still many unknowns and challenges in the physics, fabrication, and application of TFETs. In this work, the device and process simulations are carried out to investigate physical principle, optimized fabrication conditions, and future structure of TFETs. Starting from the simulation results, the necessary technologies are improved for the fabrication of high performance TFET.

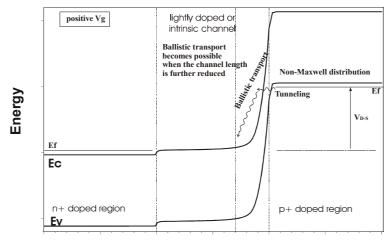

Proved by both simulation and experimental measurement, the working principle of TFET is the gate-controlled band-to-band tunneling. Compared to MOSFET, TFET has several advantages: 1) Suitable for low power application because of the lower leakage current (due to the higher barrier of the reversed p-i-n junction in TFET). 2) The active region (band-toband tunneling region) is about 10nm in TFET. Simulation shows that this transistor can be shrunk down to at least 20nm gate length. 3) The subthreshold swing of TFET is not limited by 60mV/dec because of its distinct working principle. 4) The tunneling effect and the ballistic electron transport in TFET can enhance the operating speed of TFET. 5) Since the threshold voltage of TFET depends on the band bending in the small tunnel region, but not in the whole channel region, V<sub>t</sub> roll-off is much smaller than that of MOSFET while scaling. 6) The channel region can be intrinsic silicon which suppresses the V<sub>t</sub> fluctuation caused by dopant atoms random distribution. 7) Because of the reverse biased p-i-n structure, there is no punch-through effect in TFET.

It is summarized from the simulation results that high performance TFET needs thin gate oxide (but relaxed compared to MOSFET), abrupt doping profile, and heavy source doping concentration. If both source and drain are heavily doped, one TFET has both n-channel TFET (NTFET) and p-channel TFET (PTFET) characteristics. By enhancing or suppressing the NTFET and PTFET characteristics inside of one TFET, the complementary TFET can be realized. From our investigation, it is found that the  $p^+$  doping concentration of NTFET should be higher, but the  $n^+$  doping level should be relatively lower. In order to fabricate PTFET, the  $n^+$  doping concentration should be higher, but the  $p^+$  doping level should be relatively lower.

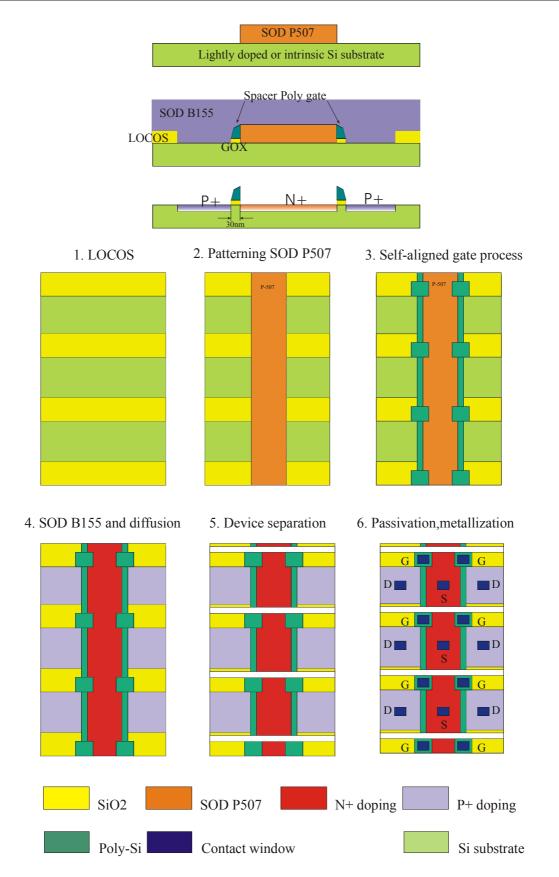

According to simulation results, the technologies are developed for TFET fabrication. The Reactive Ion Etching (RIE) technology, the heavy boron doping diffusion and the Rapid Thermal Diffusion (RTD) technology are developed in this work. The heavy n-type diffusion and the gate dry oxidation process are also calibrated. The RIE technology is applied in the fabrication of the vertical TFET, the vertical mesa diode, the self-aligned gate, and the shallow trench isolation (STI) for device separation. The n and p type diffusion of spin-ondopant (SOD) is also investigated. For the n<sup>+</sup> doping, the surface concentration of  $2 \times 10^{20}$  $cm^{-3}$  can be achieved. For the p<sup>+</sup> doping, the active surface concentration of boron is about 2.8  $\times 10^{20}$  cm<sup>-3</sup>. The patterning of SOD P507 is studied in order to form the distinctive doping profile. The patterning and thickness control of SOD P507 makes the self-aligned TFET fabrication process possible. In addition, SOD B150 is calibrated to form the p-well which enables the fabrication of the Complementary TFET (CTFET) on the single n<sup>-</sup> doped wafer. Thin gate oxide fabricated in the normal thermal oxidation oven is studied. Stable 5nm and 6 nm oxide is fabricated at 950°C and 900°C by dry oxidation. Finally, the Rapid Thermal Processing (RTP) technology is developed and calibrated in this work. The RT-Diffusion can form the ultra-shallow junction. In the planar TFET fabrication, the RTD is applied to form the  $n^+$  and the  $p^+$  regions by the diffusion of SOD.

With these improved technologies, two types of TFETs - PTFET and NTFET- are realized on the same silicon substrate. The room temperature gate-controlled tunneling is realized in the silicon device. Very low leakage current in both NTFET and PTFET is found. The realization of NTFET and PTFET also make it possible to fabricate the CTFET circuits. According to the measurement results of TFET, many physical characteristics, such as drain current saturation, the punch-through, impact ionization and avalanche, ballistic electron transport, and gate-controlled tunneling will be discussed.

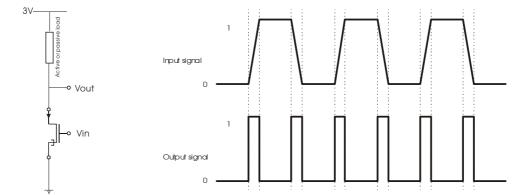

Finally, the applications of TFET are investigated. When the channel length is decreased below 20nm, TFET will be a hot electron device. That makes TFET suitable for microwave application because of the short electron transit time through the channel region. Due to the low leakage current, TFET can be used in the low power circuits. TFET can also configure the edge detector in the logic circuit using very simple TFET circuit, if the threshold voltage is well adjusted. Because of the similar characteristics to CMOS, CTFET is capable to configure many CMOS-like circuits. In this work, the CTFET inverter characteristics are derived from the CTFET characteristics. The switching of this CTFET inverter is faster and the noise margin is larger than the CMOS inverter. The reason is that TFET has a better saturation behaviour and also an earlier saturation than the conventional MOSFET. The CTFET inverter also has a smaller short circuit leakage current than the CMOS inverter. For this reason, the 6-transistor static RAM with the low stand-by power consumption can be configured using CTFET.

# Acknowledgement

Outmost, I would like to give my sincere gratitude to Prof. Dr. Ing. Walter Hansch for giving me this opportunity to do the research work in Germany. His strict manner in the scientific research and the erudite knowledge give me very deep impression. Without his encourages and numerous suggestions, this work could not have been finished.

I would like to give my sincere gratitude to Prof. Dr. rer. nat. Doris Schmitt-Landsiedel for the valuable discussions on the TFET improvements and applications. The investigation of subthreshold swing limit of TFET is one of her proposals.

I wish to express my sincere appreciation to Prof. Dr. rer. nat. Ignaz Eisele for the discussion on the TFET physics. He also allowed me to use the "Mentor Graphics" software in his laboratory for the planar TFET mask design.

Many people helped me during this project. I want to thank my former diplomands Christian Schorn and Marcus Weis for their contribution to this work. They helped me in the repairing and characterization of RIE and RTP, and also the TFET device fabrication.

Many thanks to my colleague Thomas Nirschl for many valuable ideas from the view of a circuit design expert. I also thank him for his help on the automatic electrical measurement instrument in the TFET measurement.

I want to thank Christoph Stepper, Michael Oswald, Kirsten Hilsenbeck, Liming Gao, Jürgen Gstöttner, and Peter Worm. It is a pleasure for me to work together with them in the semiconductor technology team of Lehrstuhl für Technische Elektronik. At the same time, I would like to thank all the colleagues in LTE for their support for my work. The good time in LTE will always stay in my memory.

In addition, I would like to give my appreciation to Stefan Sedlmaier, Carolin Tolksdorf, Krishna K Bhuwalka, Gunter Freitag, and Jörg Schulze for their helps and discussions, when I worked at the Institut für Physik, Universität der Bundeswehr München.

Finally, I want to thank my family for their infinite love to me.

# Contents

| Chapter 1 Introduction                                                   | 1  |

|--------------------------------------------------------------------------|----|

| 1.1 TFET working principle and definition                                | 2  |

| 1.2 Simulation tools for TFET investigation                              | 4  |

| 1.3 Process development and mask design                                  | 6  |

| 1.4 TFET fabrication                                                     | 7  |

| 1.5 Scope of this work                                                   | 8  |

| Chapter 2 Physical Theories                                              | 11 |

| 2.1 Fundamental semiconductor theories in TFET                           | 11 |

| 2.1.1 Energy band diagram in TFET                                        | 11 |

| 2.1.2 Carrier density in TFET                                            | 13 |

| 2.1.3 Carrier transport in TFET                                          | 14 |

| 2.2 p-n diode, p-i-n diode and Esaki tunnel diode                        | 16 |

| 2.2.1 p-n diode                                                          | 16 |

| 2.2.2 p-i-n diode                                                        | 17 |

| 2.2.3 Esaki Tunnel diode                                                 | 18 |

| 2.3 Summary                                                              | 22 |

| Chapter 3 Simulation of MOSFET and TFET                                  | 23 |

| 3.1 Simulation of the Esaki tunnel diode                                 | 23 |

| 3.2 Simulation of MOSFET                                                 | 25 |

| 3.2.1 Band-to-band tunneling in the 100nm vertical MOSFET                | 25 |

| 3.2.2 Double gate and fully depleted MOSFET                              | 27 |

| 3.3 Device simulation of TFET                                            | 30 |

| 3.3.1 Simulation of the basic TFET structure                             | 30 |

| 3.3.1.1 Definition of the simulated structure and electrodes             | 30 |

| 3.3.1.2 Transfer and output characteristics of the simulated NTFET       | 32 |

| 3.3.1.3 Relation of Band Diagrams, II.GENER, BB.GENER and Electric Field | 34 |

| 3.3.1.3.1 Energy band diagrams                                              | 34 |

|-----------------------------------------------------------------------------|----|

| 3.3.1.3.2 BB.GENER, II.GENER and Electric Field                             | 36 |

| 3.3.2 Impacts of the gate oxide thickness on NTFET                          | 38 |

| 3.3.3 Impacts of the doping profile on NTFET                                | 39 |

| 3.3.3.1 Characteristics of the NTFET with various source doping levels      | 39 |

| 3.3.3.2 Impacts of the channel doping level and the channel length on NTFET | 42 |

| 3.3.3.2.1 NTFET with various channel doping levels                          | 42 |

| 3.3.3.2.2 NTFET with various channel lengths                                | 43 |

| 3.3.4 Influence of the dopant smear-out on NTFET                            | 43 |

| 3.3.5 Double gate TFET simulation                                           | 45 |

| 3.3.5.1 <i>I-V</i> characteristics of the double gate NTFET                 | 45 |

| 3.3.5.2 Scaling prospect of the double gate NTFET                           | 46 |

| 3.4 TFET Process simulation                                                 | 47 |

| 3.4.1 Simulation of vertical MBE-TFET                                       | 48 |

| 3.4.2 Impacts of the oxidation process on the MBE-TFET                      | 50 |

| 3.4.3 Impacts of the delta doping layer on the MBE-TFET performance         | 52 |

| 3.4.4 Impacts of n <sup>+</sup> drain doping level on NTFET                 | 53 |

| 3.4.5 Impacts of the channel doping on the MBE-TFET                         | 54 |

| 3.5 Study of tunneling in the simulated MBE-TFET                            | 54 |

| 3.5.1 Two types of tunneling in the MBE-TFET                                | 54 |

| 3.5.2 Application of the "line tunneling" in the vertical NTFET             | 57 |

| 3.5.3 Impacts of G-S overlap on the performance of MBE-TFET                 | 58 |

| 3.6 Simulation of the planar TFET fabricated by diffusion doping            | 59 |

| 3.7 Subthreshold swing in TFET                                              | 60 |

| 3.8 NTFET vs. PTFET                                                         | 61 |

| 3.9 Summary                                                                 | 62 |

| Chapter 4 Process Development for the TFET Fabrication                      | 65 |

| 4.1 Silicon Etching Technology                                              | 65 |

| 4.1.1 Introduction to the etching technology                                | 65 |

| 4.1.2 Hard mask for the silicon etching in the TEPLA RIBE 160 system        | 68 |

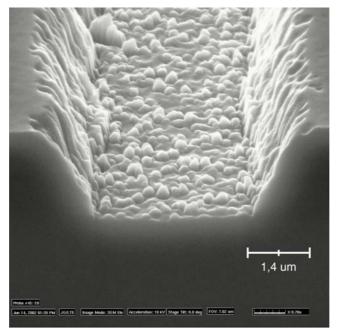

| 4.1.3 Silicon trench etching                                                | 71 |

| 4.2 Doping technology                                                       | 72 |

| 4.2.1 Mechanism of the spin on diffusion                                    | 72 |

| 4.2.2. Electrical results of SOD diffusion                                  | 74 |

| 4.2.2.1 N diffusion using SOD P507                                   | 74  |

|----------------------------------------------------------------------|-----|

| 4.2.2.2 P-type diffusion using SOD B150 and SOD B155                 | 75  |

| 4.2.2.2.1 Diffusion using SOD B150                                   | 75  |

| 4.2.2.2.2 Diffusion using SOD B155                                   | 77  |

| 4.2.3 SOD using the RTP chamber                                      |     |

| 4.2.4 Patterning of the SOD layer                                    |     |

| 4.2.5 Application of the SOD in self-aligned TFET fabrication        |     |

| 4.3 Gate oxide formation                                             |     |

| 4.4 Summary                                                          |     |

| Chapter 5 TFET Fabrication and Characterization                      | 91  |

| 5.1 Silicon tunnel diode fabrication                                 | 91  |

| 5.2 Vertical TFET fabrication                                        |     |

| 5.2.1 4-mask vertical TFET fabrication for process calibration       | 93  |

| 5.2.2 4-mak self-aligned gate vertical SOD-TFET                      | 96  |

| 5.2.2.1 Fabrication details                                          | 96  |

| 5.2.2.2 Electrical measurements                                      |     |

| 5.2.3 Discussion on the self-aligned vertical SOD-TFET               | 100 |

| 5.3 6-mask planar SOD-TFET fabrication                               | 100 |

| 5.3.1 Details of the device fabrication                              |     |

| 5.3.2 Device characterization and discussion                         | 102 |

| 5.4 8-mask planar SOD-TFET fabricated using RTP                      |     |

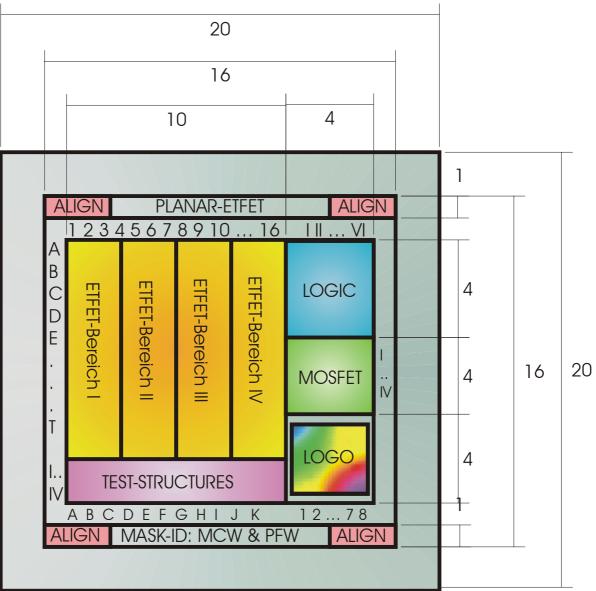

| 5.4.1 Mask design                                                    |     |

| 5.4.2 Process sequence design                                        |     |

| 5.4.3 Experimental details of fabrication                            |     |

| 5.4.4 Electrical characterization                                    | 109 |

| 5.4.4.1 NTFET characteristics                                        | 109 |

| 5.4.4.2 PTFET characteristics                                        | 111 |

| 5.4.4.3 Discussions on the planar SOD-TFET fabrication               | 112 |

| 5.4.4.3.1 Over-etching problem in the TFET fabrication               | 112 |

| 5.4.4.3.2 Influence of the structural design on the TFET performance | 113 |

| 5.4.4.3.3 Planar TFETs with various channel lengths                  | 113 |

| 5.4.4.3.4 Effects of $p^+$ diffusion time on TFET                    | 116 |

| 5.4.4.3.5 Effects of the sputtering processes on TFET                | 117 |

| 5.4.4.3.6 Problems caused by STI                                     | 118 |

| 5.4.4.4 Yield of TFET on one wafer                                                                                                                                                                                                                                                                                                                                 | 118        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.5 Discussion on the TFET properties                                                                                                                                                                                                                                                                                                                              | 120        |

| 5.5.1 Moving tunneling junction in TFET                                                                                                                                                                                                                                                                                                                            | 120        |

| 5.5.2 Current saturation in TFET                                                                                                                                                                                                                                                                                                                                   | 121        |

| 5.5.3 Punch-through and avalanche in TFET                                                                                                                                                                                                                                                                                                                          | 125        |

| 5.5.4 Ballistic electron transport in TFET                                                                                                                                                                                                                                                                                                                         | 126        |

| 5.5.5 Gate-controlled Esaki-Tunneling current in TFET                                                                                                                                                                                                                                                                                                              | 127        |

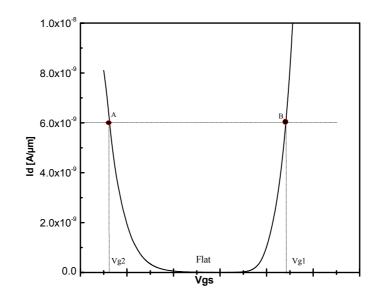

| 5.5.6 Flat region in the TFET transfer characteristics                                                                                                                                                                                                                                                                                                             |            |

| 5.5.7 Integrated complementary TFET (CTFET) inverters                                                                                                                                                                                                                                                                                                              | 129        |

| 5.6 Conclusion and proposal                                                                                                                                                                                                                                                                                                                                        |            |

| 5.6.1 Comparison of vertical and planar TFET                                                                                                                                                                                                                                                                                                                       |            |

| 5.6.2 TFET properties and applications                                                                                                                                                                                                                                                                                                                             |            |

| 5.6.3 Proposed self-aligned process for the planar TFET fabrication                                                                                                                                                                                                                                                                                                |            |

| Chapter 6 Summary                                                                                                                                                                                                                                                                                                                                                  | 135        |

| 6.1 Results obtained from the simulation                                                                                                                                                                                                                                                                                                                           |            |

| 6.2 Process development results                                                                                                                                                                                                                                                                                                                                    |            |

| 6.3 TFET fabrication results                                                                                                                                                                                                                                                                                                                                       | 137        |

|                                                                                                                                                                                                                                                                                                                                                                    |            |

| 6.4 Conclusions and outlook                                                                                                                                                                                                                                                                                                                                        |            |

| 6.4 Conclusions and outlook                                                                                                                                                                                                                                                                                                                                        | 139        |

|                                                                                                                                                                                                                                                                                                                                                                    |            |

| Appendix A Medici, Suprem and Taurus Simulation                                                                                                                                                                                                                                                                                                                    | 139        |

| Appendix A Medici, Suprem and Taurus Simulation<br>A.1 TFET device simulation using Medici                                                                                                                                                                                                                                                                         | 139<br>145 |

| Appendix A Medici, Suprem and Taurus Simulation<br>A.1 TFET device simulation using Medici<br>A.2 TFET process simulation using Suprem                                                                                                                                                                                                                             |            |

| Appendix A Medici, Suprem and Taurus Simulation<br>A.1 TFET device simulation using Medici<br>A.2 TFET process simulation using Suprem<br>A.3 TFET 3-dimensional process simulation                                                                                                                                                                                |            |

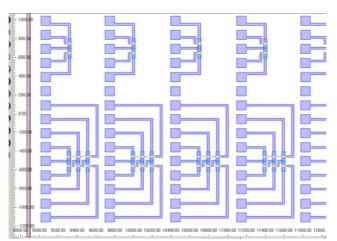

| <ul> <li>Appendix A Medici, Suprem and Taurus Simulation</li> <li>A.1 TFET device simulation using Medici</li> <li>A.2 TFET process simulation using Suprem</li> <li>A.3 TFET 3-dimensional process simulation</li> <li>Appendix B 2<sup>nd</sup> Version Planar TFET Mask</li> </ul>                                                                              |            |

| <ul> <li>Appendix A Medici, Suprem and Taurus Simulation</li> <li>A.1 TFET device simulation using Medici</li> <li>A.2 TFET process simulation using Suprem</li> <li>A.3 TFET 3-dimensional process simulation</li> <li>Appendix B 2<sup>nd</sup> Version Planar TFET Mask</li> <li>B.1 Overview of the mask for the 2<sup>nd</sup> version planar TFET</li> </ul> |            |

# **List of Figures**

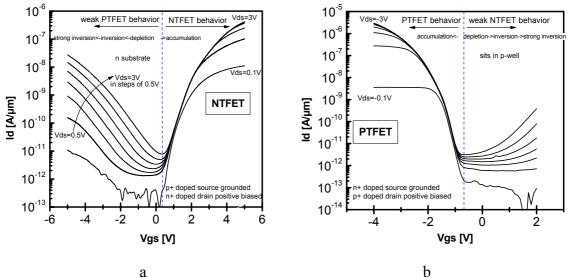

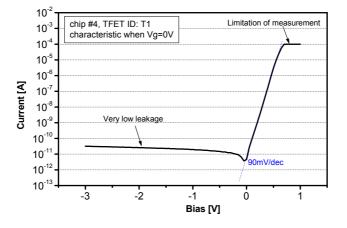

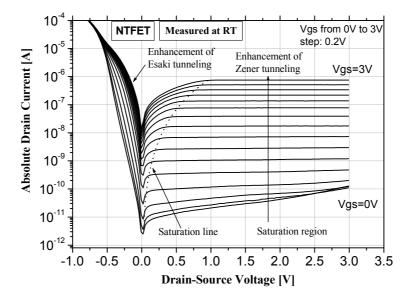

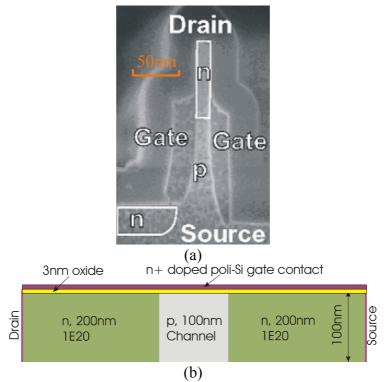

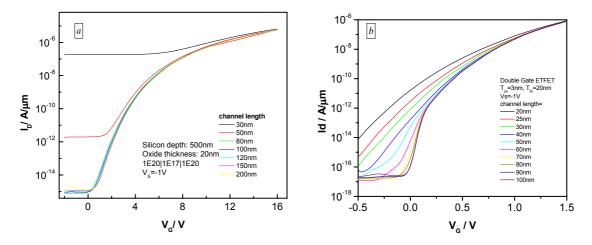

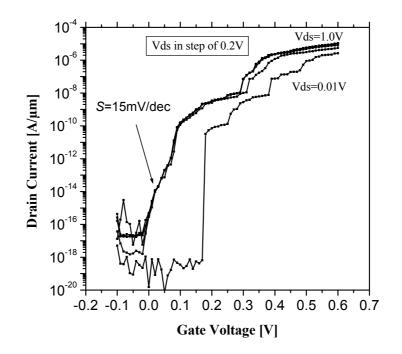

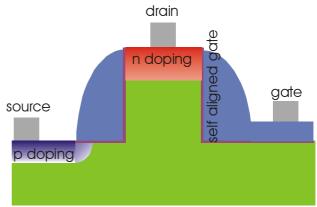

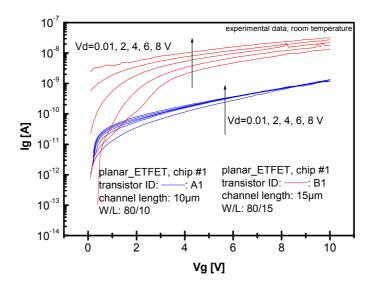

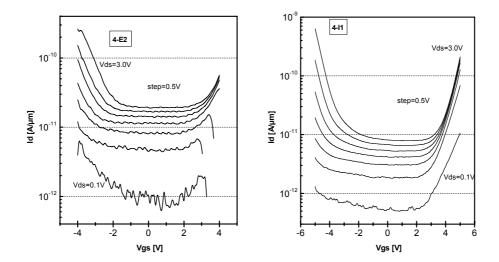

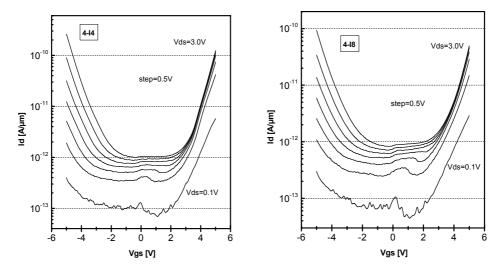

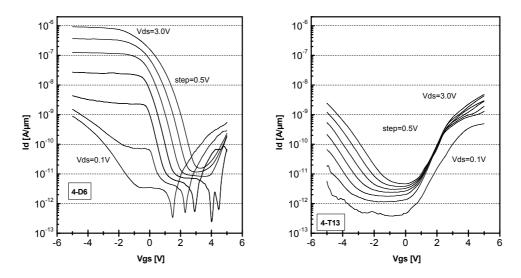

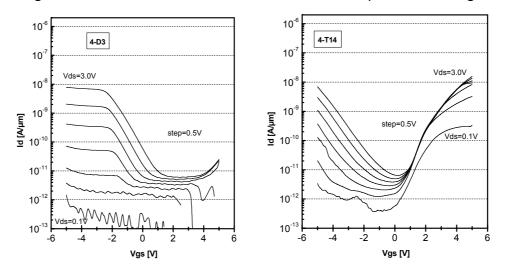

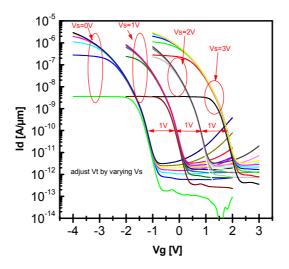

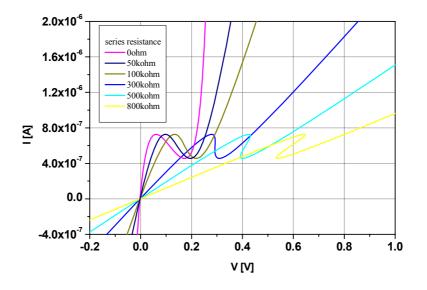

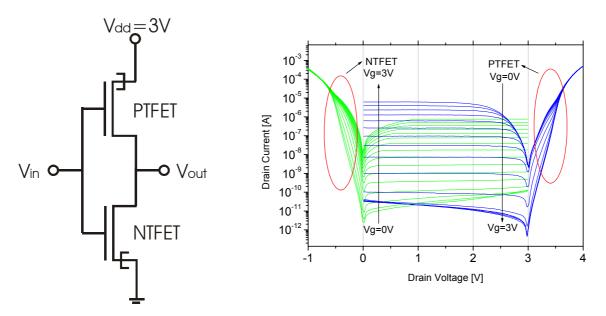

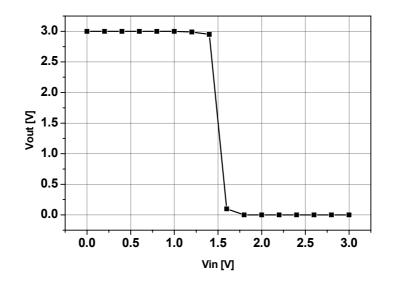

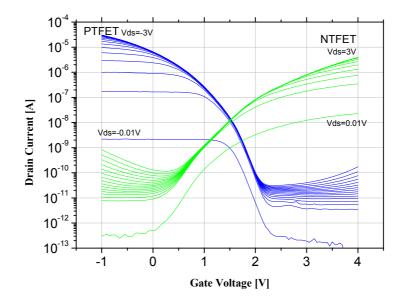

| Fig. | 1-1 Experimental transfer characteristics of NTFET (a) and PTFET (b)2                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------|

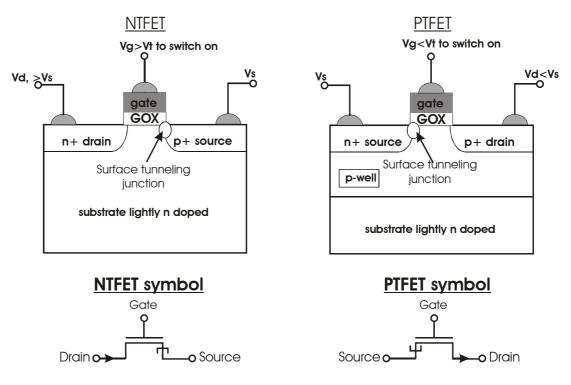

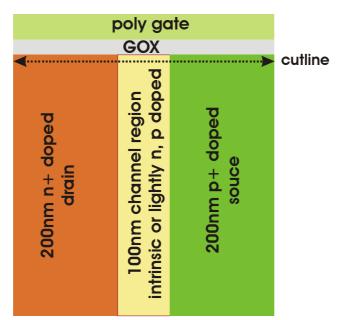

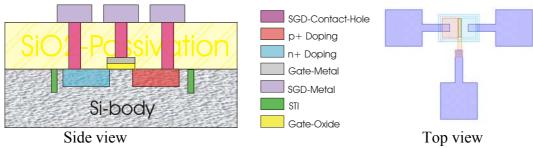

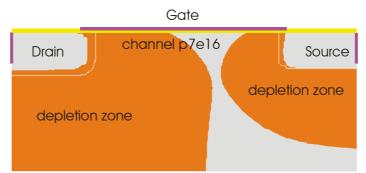

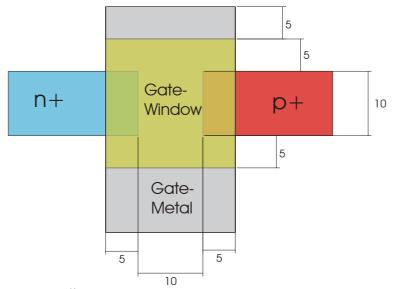

| Fig. | 1-2 Basic TFETs structural models and the electrodes definition of TFET                                                     |

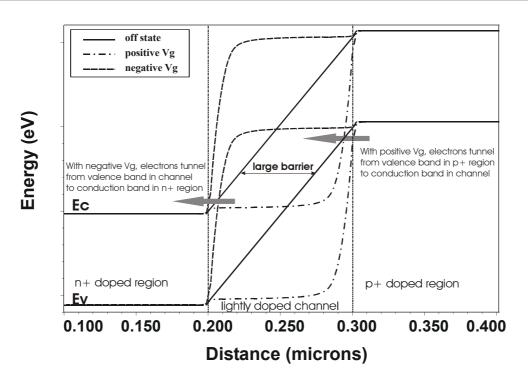

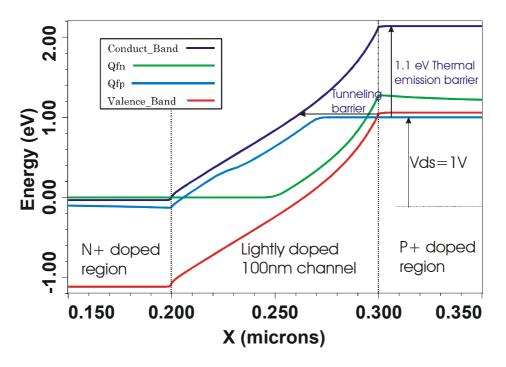

| Fig. | 1-3 MEDICI simulated band diagram of the on-state TFET ( $V_{ds}$ =1V, $V_{gs}$ > V <sub>t</sub> )4                         |

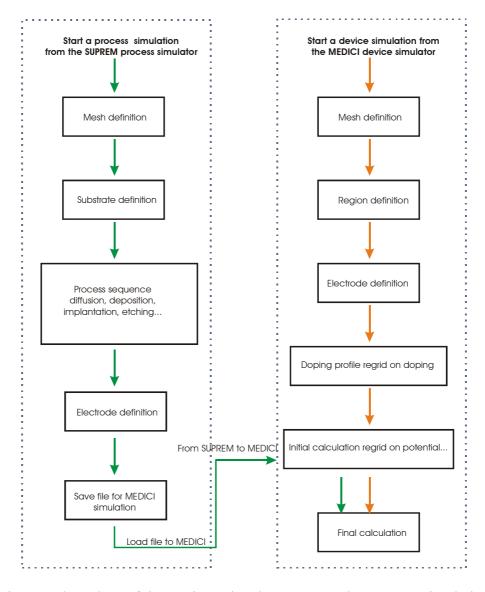

| Fig. | 1-4 Flow chart of the 2-Dimensional MEDICI and SUPREM simulation                                                            |

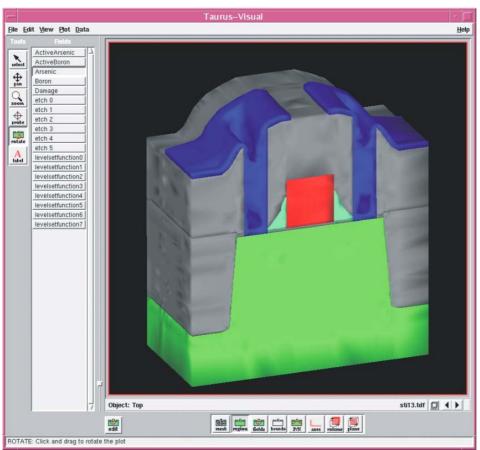

| Fig. | 1-5 A STI MOS obtained by 3-D simulation (displayed in the Taurus Visual window)6                                           |

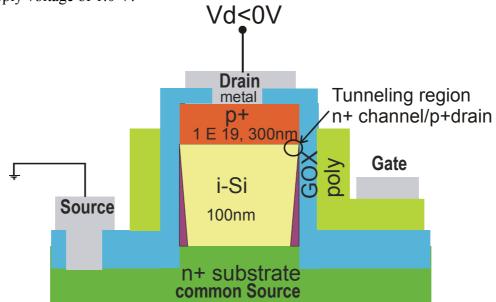

| Fig. | 1-6 Schematic structure of a vertical TFET fabricated using MBE7                                                            |

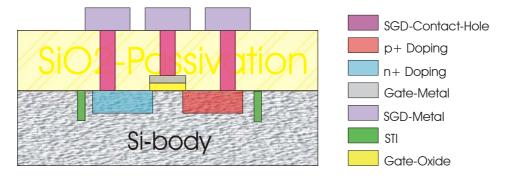

| Fig. | 1-7 Schematic structure of the planar TFET fabricated using the diffusion of SOD                                            |

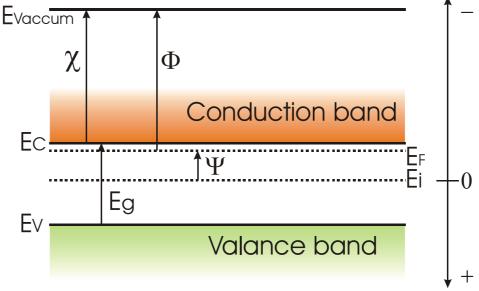

| Fig. | 2-1 Simplified energy band diagram of a n doped silicon                                                                     |

| Fig. | 2-2 Band diagram along the cutline beneath the gate oxide of the off-state TFET12                                           |

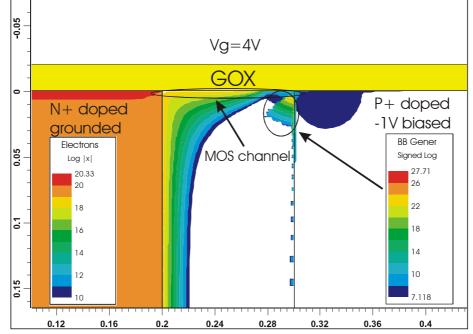

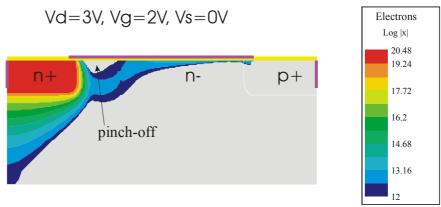

| Fig. | 2-3 Contour of electrons density and band-to-band generation rate in the on-state TFET14                                    |

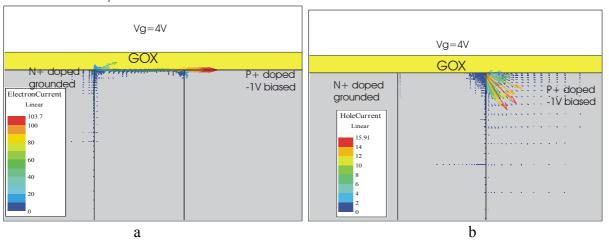

| Fig. | 2-4 Contour of the electron ( <i>a</i> ) and the hole current ( <i>b</i> ) in the on-state TFET15                           |

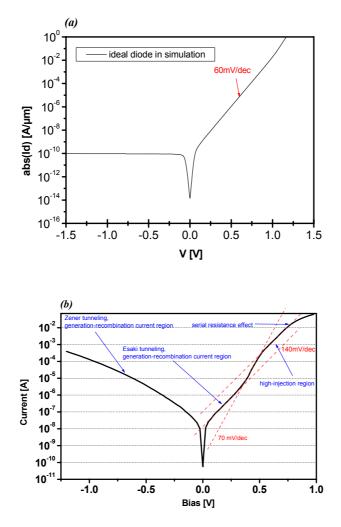

| Fig. | 2-5 Characteristics of a simulated ideal diode (a) and an experimental diode (b)16                                          |

| Fig. | 2-6 Measured pin diode characteristic in the off-state TFET                                                                 |

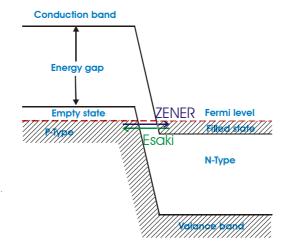

| Fig. | 2-7 Energy band diagram of the tunnel diode at the thermal equilibrium                                                      |

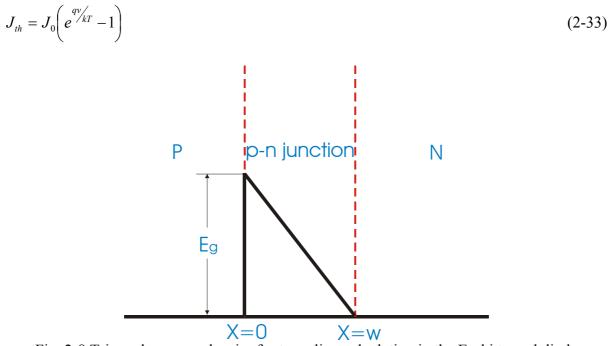

| Fig. | 2-8 Triangular energy barrier for tunneling calculation in the Esaki tunnel diode20                                         |

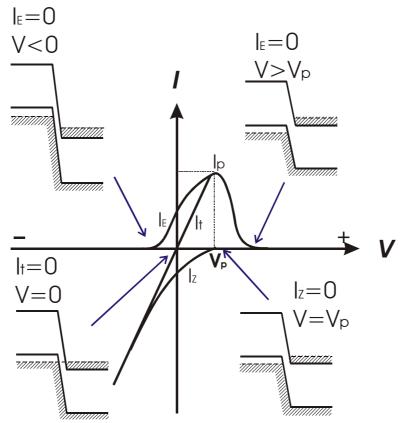

| Fig. | 2-9 Relation of Zener and Esaki tunneling current in the ideal Esaki tunnel diode ( $I_t=I_E-I_Z$ )                         |

|      |                                                                                                                             |

| Fig. | 2-10 Gate-controlled surface Esaki tunnel current and Zener tunnel current in the measured                                  |

|      | TFET output characteristics                                                                                                 |

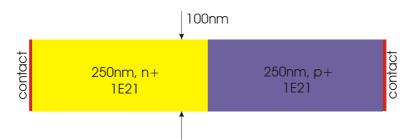

| Fig. | 3-1 Structure for the simulation of the Esaki tunnel diode                                                                  |

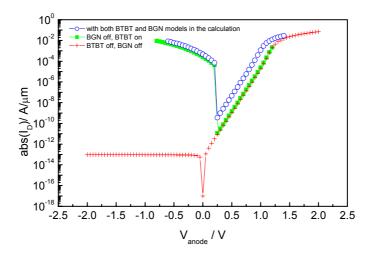

| Fig. | 3-2 Simulated <i>I-V</i> characteristics of the Esaki tunnel diode with the different physical                              |

|      | models                                                                                                                      |

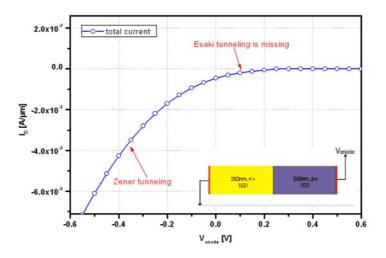

| Fig. | 3-3 <i>I-V</i> characteristics of the Medici simulated Esaki tunnel diode                                                   |

| Fig. | 3-4 Structure of the experimental in ref. [26] (a) and the simulated MOSFET structure (b)25                                 |

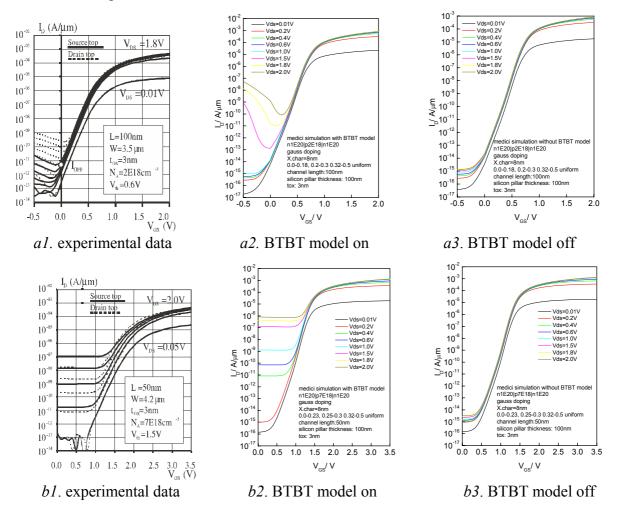

| Fig. | 3-5 Comparison of the experimental (a) and the simulated (b) transfer <i>I-V</i> characteristics .26                        |

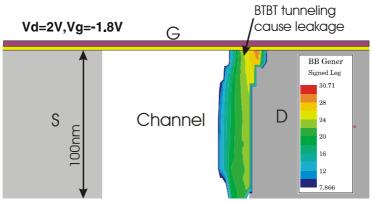

| Fig. | 3-6 Contour of the band-to-band tunneling generation rate of NMOS                                                           |

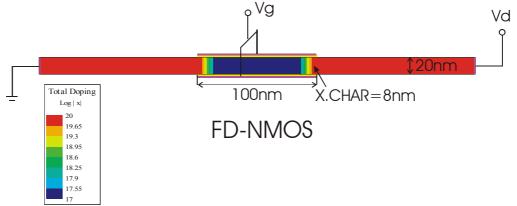

| Fig. | 3-7 FD-NMOS structure with silicon thickness of 20nm and channel length of 100nm27                                          |

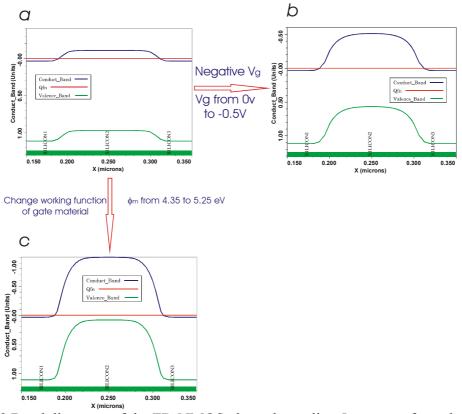

| Fig. | 3-8 Band diagrams of the FD-NMOS along the cutline 5nm away from the oxide interface.                                       |

|      | a). $V_{gs} = 0V$ , the gate is n <sup>+</sup> doped poly-Si ( $\phi_m = 4.35eV$ ). b). Decrease $V_{gs}$ from 0V to -0.5V, |

|      |                                                                                                                             |

| the electron barrier increases. c). Change the gate material to the $p^+$ doped poly-Si                                    |  |

|----------------------------------------------------------------------------------------------------------------------------|--|

| ( $\phi_m$ =5.25eV), the barrier also increases. The simulations are performed at V <sub>ds</sub> =0V and the              |  |

| channel doping is p $1 \times 10^{17} \text{ cm}^{-3}$                                                                     |  |

| Fig. 3-9 Transfer characteristics of FD-NMOS with different gate materials, $\phi_m$ =4, 5, 6 eV 28                        |  |

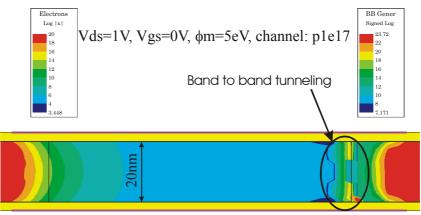

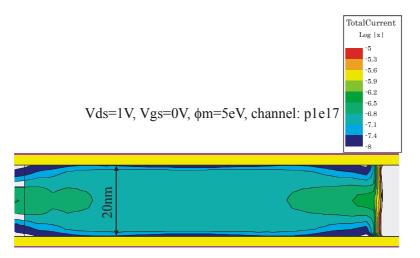

| Fig. 3-10 Contour of the band-to-band tunneling generation rate and the electron density in an                             |  |

| off-state FD-NMOS, $V_{ds}=1V$ , $V_{gs}=0V$                                                                               |  |

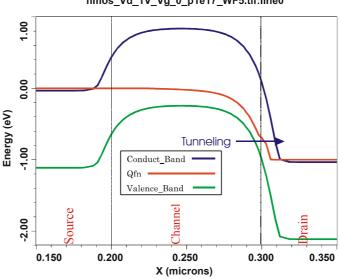

| Fig. 3-11 Band diagram of a FD-NMOS with $\phi_m$ =5eV. (V <sub>ds</sub> =1V and V <sub>gs</sub> =0V)                      |  |

| Fig. 3-12 Total current of FD-NMOS at $V_{ds}$ =1V and $V_{gs}$ =0V                                                        |  |

| Fig. 3-13 Structural model for the NTFET simulation                                                                        |  |

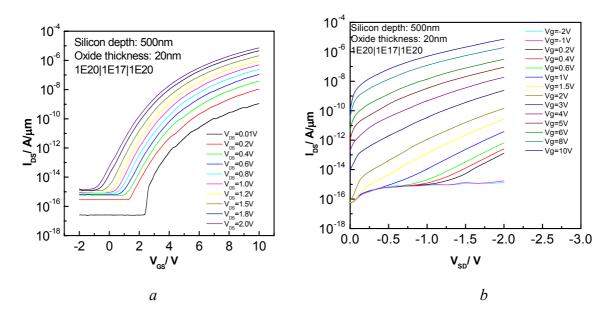

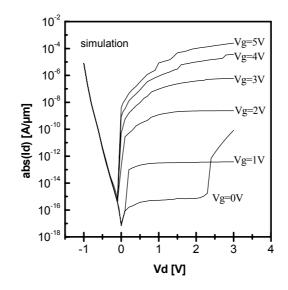

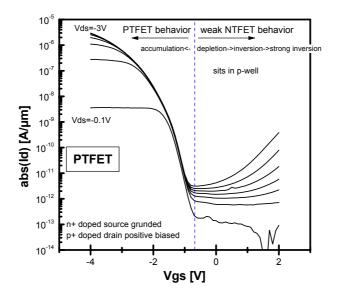

| Fig. 3-14 Transfer (a) and output <i>I-V</i> characteristics (b) of the basic NTFET simulation model 33                    |  |

| Fig. 3-15 Simulated transfer characteristics of the basic NTFET structure with the $p^+$ source                            |  |

| grounded and the $n^+$ drain positive biased. The V <sub>t</sub> shift is reduced                                          |  |

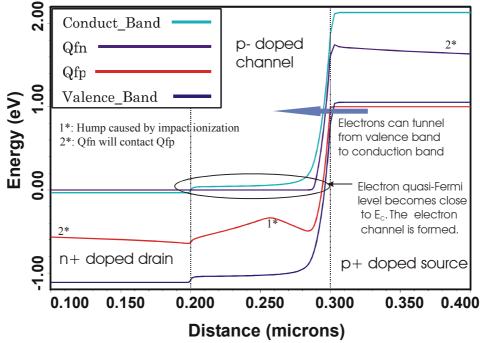

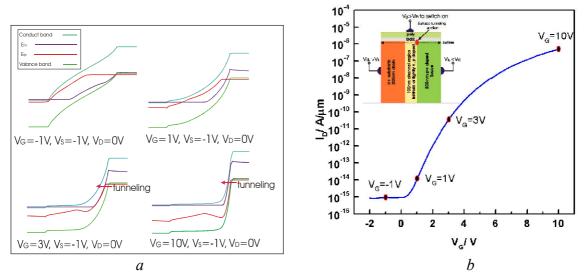

| Fig. 3-16 Band diagram in the basic NTFET model with $V_s = -1V$ , $V_g = 10V$ , $V_d = 0V$                                |  |

| Fig. 3-17 Band diagram along the cut line at the location of y=2nm (a), and the <i>I-V</i> characteristic                  |  |

| of the basic tunneling model (b). ( $V_d=0V$ , $V_s=-1V$ ). $t_{ox}=20$ nm                                                 |  |

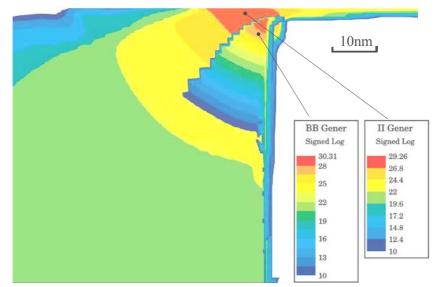

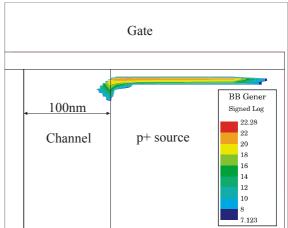

| Fig. 3-18 Contour of <i>BB.GENR</i> and <i>II.GENER</i> @ $V_g = 10V$ , $V_s = -1V$ , $V_d = 0V$ in NTFET 37               |  |

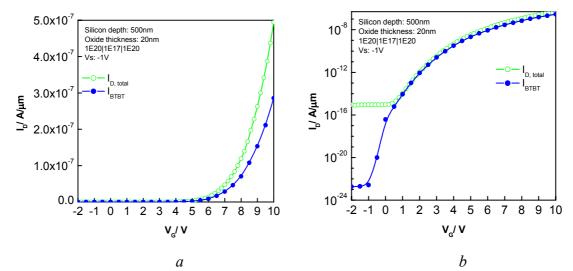

| Fig. 3-19 Relation of the total drain current and the band-to-band tunneling current with the                              |  |

| linear Y axis (a), and the log Y axis (b), $V_s = -1V$ , $V_d = 0V$ in NTFET                                               |  |

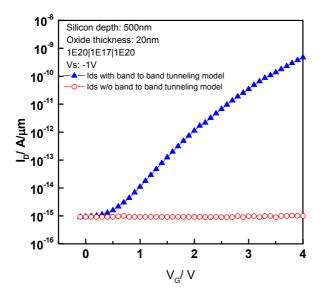

| Fig. 3-20 Transfer curves with the BTBT model on and off when $V_s = -1V$ , $V_d = 0V$                                     |  |

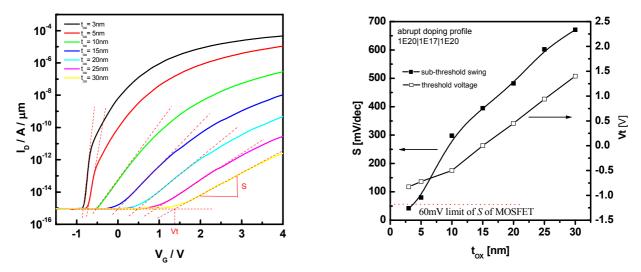

| Fig. 3-21 Transfer <i>I-V</i> characteristics with the supply voltage of $-1V$ (left); the dependence of                   |  |

| subthreshold swing and threshold voltage on tox (right)                                                                    |  |

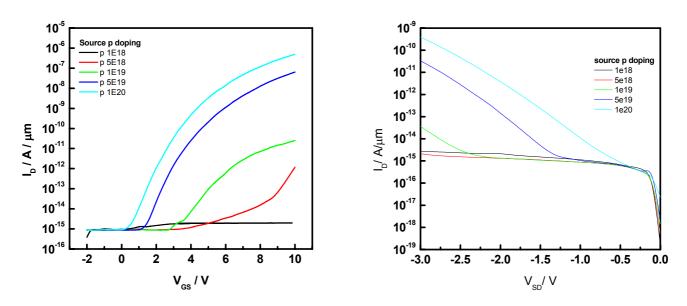

| Fig. 3-22 Dependence of the transfer (left) and the output <i>I-V</i> characteristics (right) on the                       |  |

| source doping of NTFET with $V_s = -1V$ , $V_d = 0V$                                                                       |  |

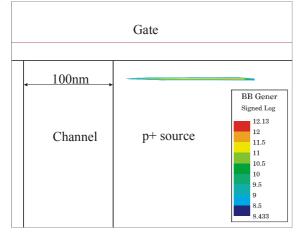

| Fig. 3-23 Contour of BB.Gener in the tunneling transistors with the different source doping                                |  |

| when $V_s = -1V$ , $V_d = 0V$ and $V_g = 4V$                                                                               |  |

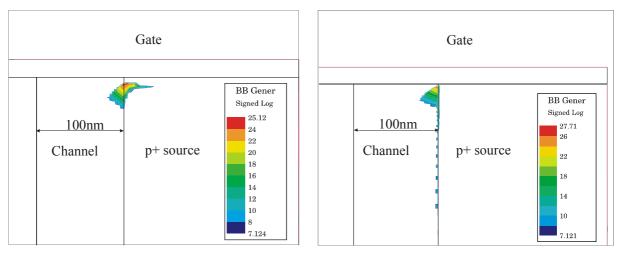

| Fig. 3-24 Contour of the electric field in the tunneling transistors with the different source                             |  |

| doping when $V_s = -1V$ , $V_d=0V$ and $V_g = 4V$                                                                          |  |

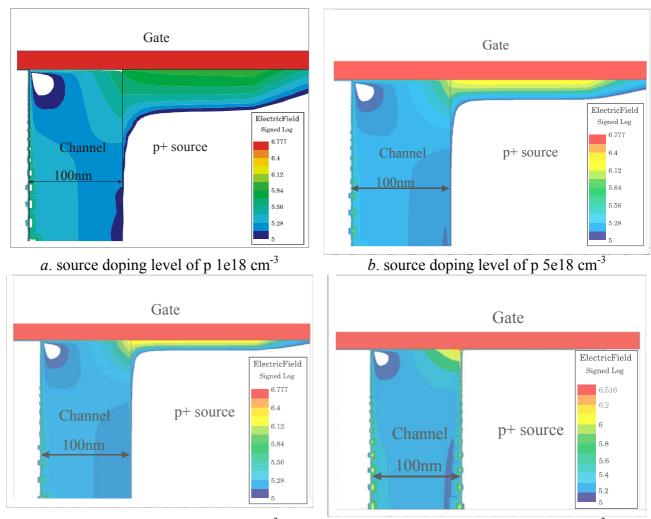

| Fig. 3-25 Transfer <i>I-V</i> characteristics of the NTFET with different channel doping levels (left),                    |  |

| and the contour of BB.Gener in the NTFET with the channel doping of $p1 \times 10^{18}$ cm <sup>-3</sup> at V <sub>s</sub> |  |

| =-1V, $V_d$ =0V, $V_g$ =0V (right)                                                                                         |  |

| Fig. 3-26 Transfer characteristics of the basic NTFET structure with various channel lengths.                              |  |

| (left), silicon body thickness is 500nm; and the transfer characteristics of the double gate                               |  |

| NTFET with various channel lengths (right), $t_{ox}$ =3nm and $t_{Si}$ =20nm                                               |  |

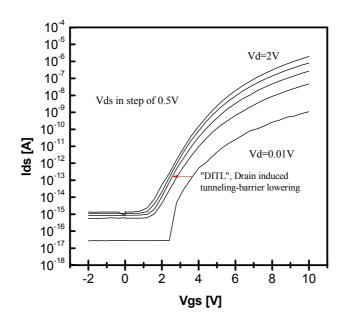

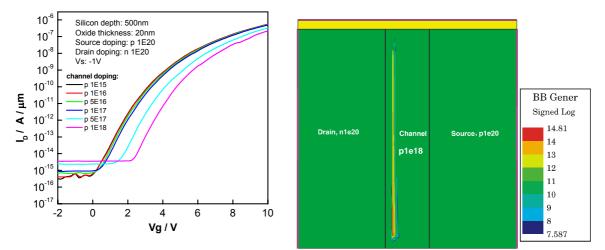

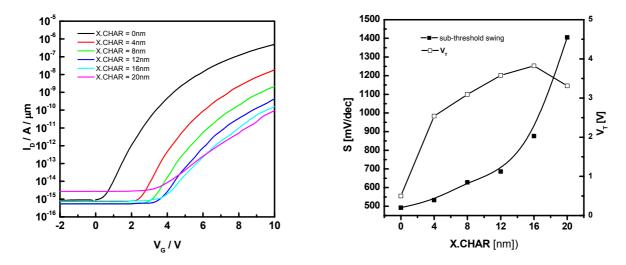

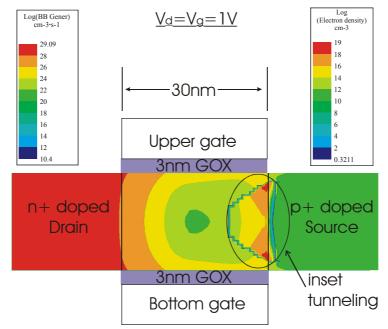

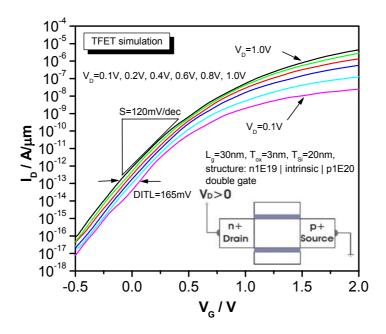

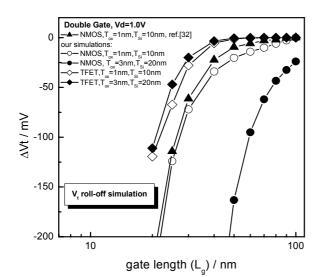

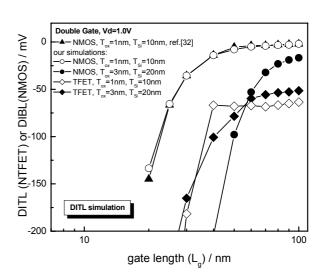

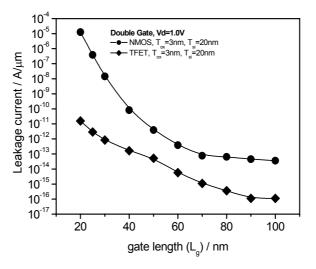

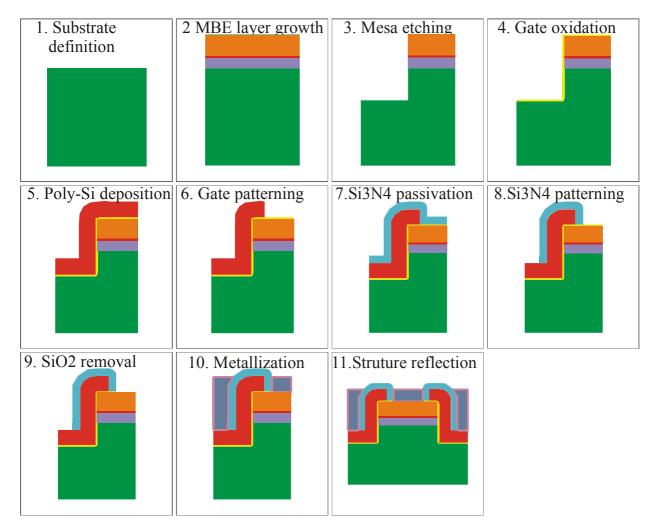

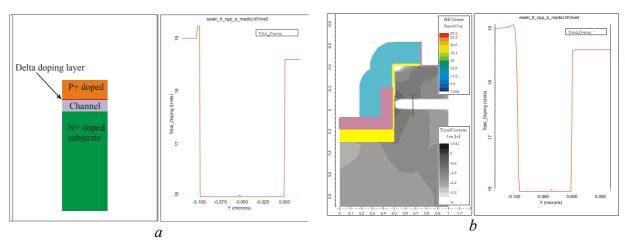

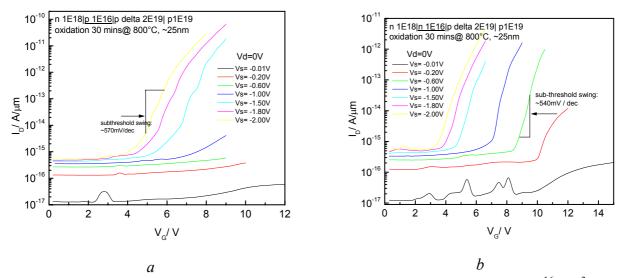

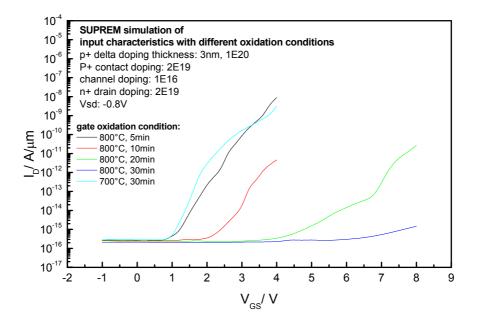

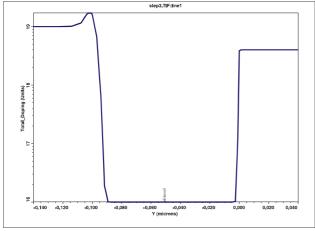

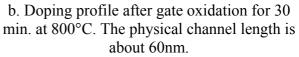

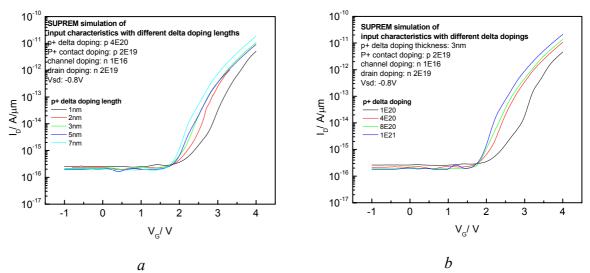

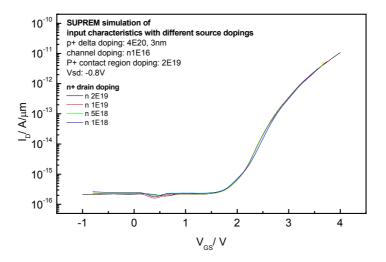

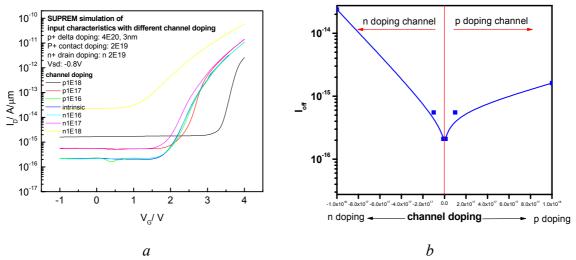

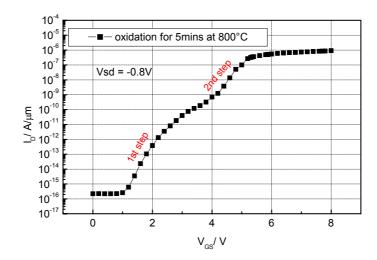

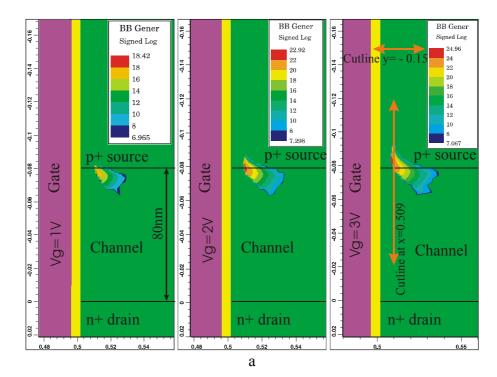

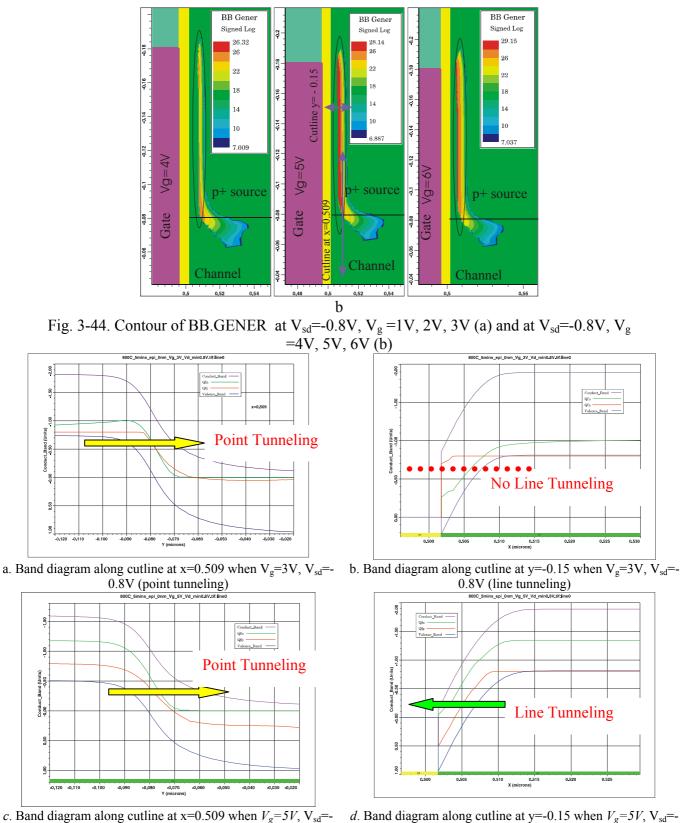

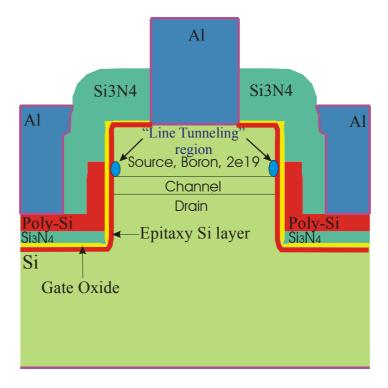

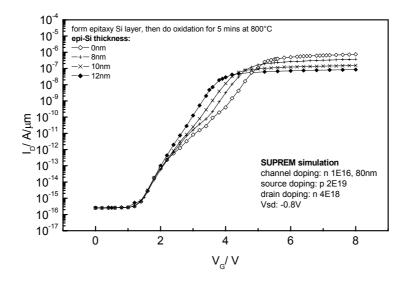

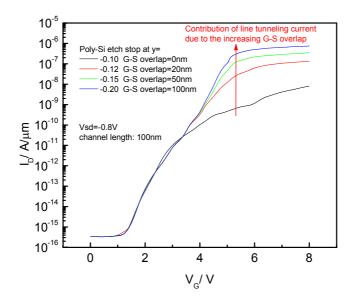

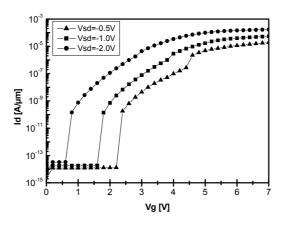

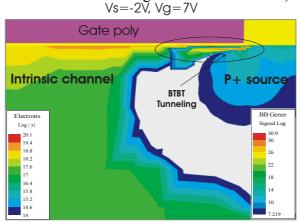

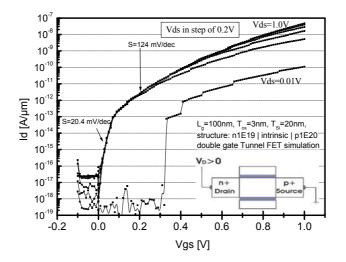

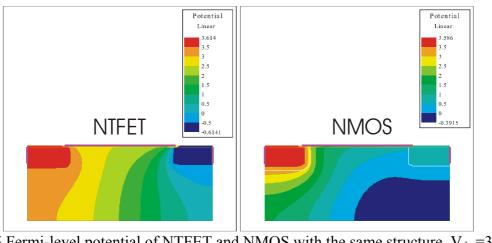

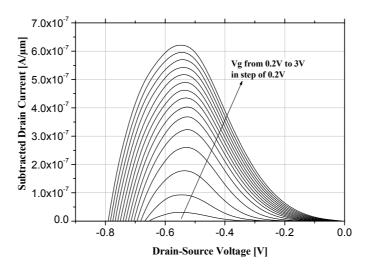

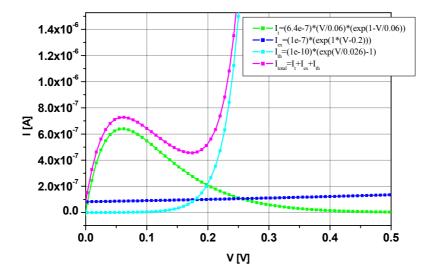

Fig. 3-27 Transfer I-V characteristics of the NTFET simulation model with different X.CHAR (left); the dependence of the subthreshold swing and threshold voltage on X.CHAR (right) Fig. 3-28 Simulated transistor structural parameter and the contours of band-to-band tunneling generation rate and electron density in the double gate NTFET......45 Fig. 3-29 Transfer characteristics of the proposed double gate NTFET with  $V_{ds}$  as differing Fig. 3-31 Comparison of DITL in the double gate TFET and the DIBL of double gate NMOS.47 Fig. 3-32 Comparison of the leakage current of the double gate TFET and the double gate Fig. 3-35 Doping profile after MBE layer growth(*a*) and the doping profile after the final Fig. 3-36 Simulated transfer characteristics of the MBE-TFET with the p type  $1 \times 10^{16}$  cm<sup>-3</sup> Fig. 3-37 Simulated performance of the MBE-TFET with the different oxidation conditions....51 Fig. 3-38 Comparison of the doping profile before and after oxidation for 30 min. at 800°C .... 52 Fig. 3-40 Performance of the MBE-TFETs with various delta doping layer thicknesses (a) and Fig. 3-42 Transfer characteristics of the MBE-TFET with various channel dopings (a); the Fig. 3-44. Contour of BB.GENER at  $V_{sd}$ =-0.8V,  $V_g$ =1V, 2V, 3V (a) and at  $V_{sd}$ =-0.8V,  $V_g$ =4V, Fig. 3-45 Band diagrams along the cutline at x=0.509 for the point tunneling and the band diagrams along the cutline at y=-0.15 for the line tunneling. The TFET structure can be Fig. 3-46 Proposed structure with an additional epitaxial intrinsic layer grown after the mesa

| Fig. 3-48 Performance of the MBE-TFET with various G-S overlap lengths                                                       | . 58 |

|------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 3-49 Simulated transfer characteristics of the planar TFET with the SOD process. (Using                                 |      |

| the connection configuration <i>c</i> in table 3-1)                                                                          | . 59 |

| Fig. 3-50 Contour of the BTBT generation rate and the electron density in the on-state planar                                |      |

| TFET with the SOD process. $t_{ox} = 4.2$ nm. (the channel length is 1µm)                                                    | . 59 |

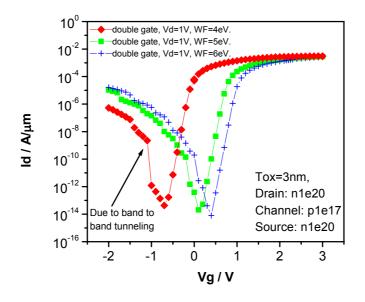

| Fig. 3-51 Transfer characteristics of the double gate TFET with 100nm channel length and 3n                                  | m    |

| gate oxide thickness                                                                                                         | . 60 |

| Fig. 3-52 Simulated transfer characteristics of the double gate NTFET with the $p^+$ doping level                            | el   |

| of 10 <sup>22</sup> cm <sup>-3</sup>                                                                                         | 61   |

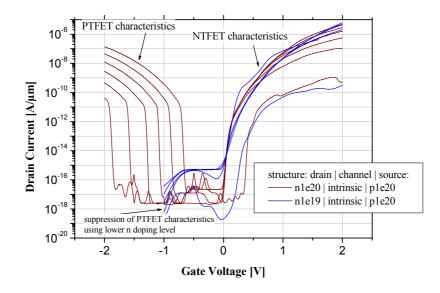

| Fig. 3-53 Suppression of the PTFET characteristics using the lower $n^+$ doping level                                        | . 62 |

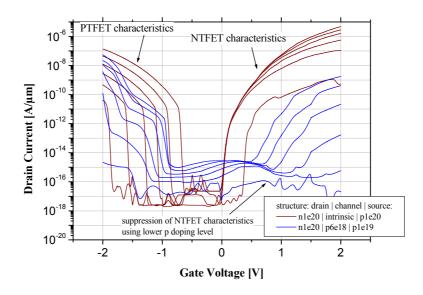

| Fig. 3-54 Suppression of the NTFET characteristics using the lower $p^+$ doping level                                        | . 62 |

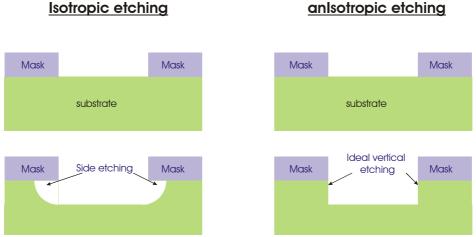

| Fig. 4-1 Comparison of isotropic etching and anisotropic etching                                                             | . 66 |

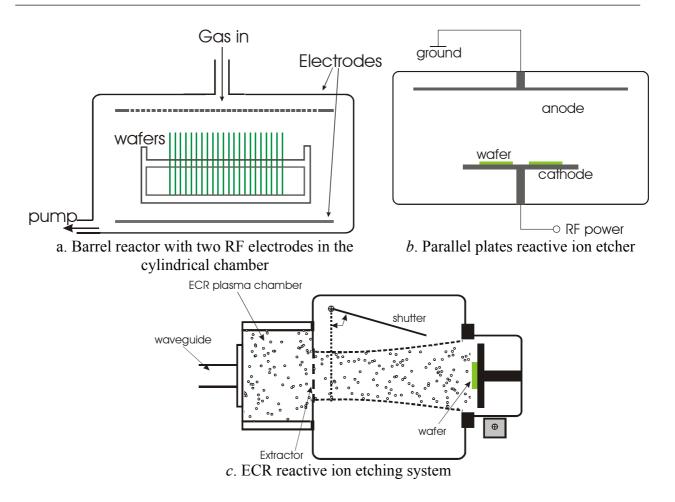

| Fig. 4-2 Different types of plasma etching systems                                                                           | . 67 |

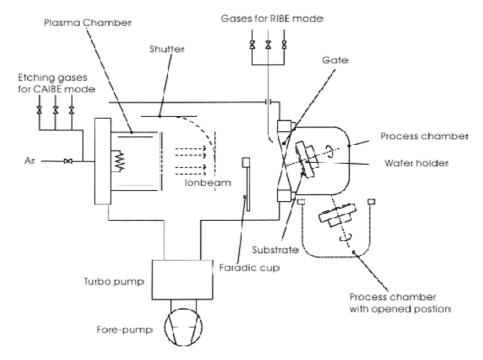

| Fig. 4-3 Schematic structure of the TEPLA ECR-RIBE 160 system                                                                | . 69 |

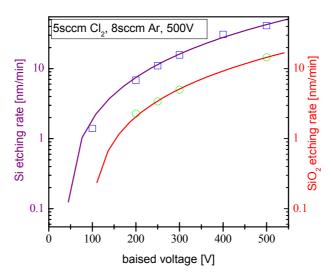

| Fig. 4-4 Etching rate of silicon and silicon oxide in the RIBE 160 system using the Cl <sub>2</sub> gas                      | . 70 |

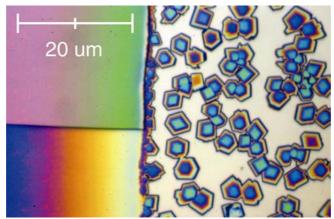

| Fig. 4-5 Pattern of Al <sub>2</sub> O <sub>3</sub> after the buffered HF etching, AlF <sub>3</sub> are created after etching | . 70 |

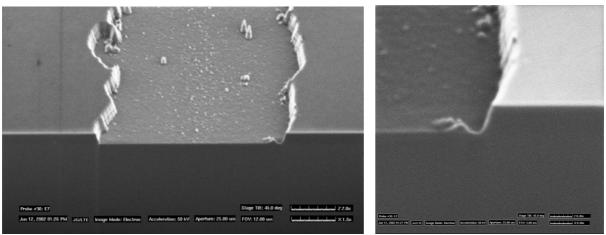

| Fig. 4-6 Silicon trench formed by the Cl <sub>2</sub> reactive ion etching                                                   | . 71 |

| Fig. 4-7 STI used to suppress the surface leakage and to separate the devices.                                               | . 71 |

| Fig. 4-8 Silicon trench etched using Al <sub>2</sub> O <sub>3</sub> as the hard mask.                                        | . 72 |

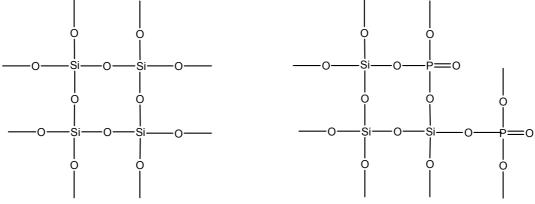

| Fig. 4-9 Chemical structures of the silicon dioxide (left) and the phosphorous-containing SOL                                | )    |

| (right)                                                                                                                      | . 73 |

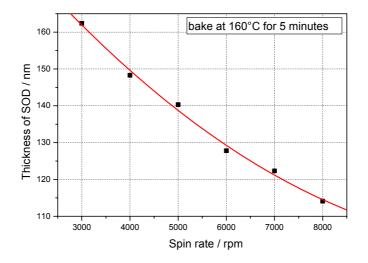

| Fig. 4-10 Thickness of the SOD P507 film vs. the spin rate, baking condition: 160°C 5min                                     | . 74 |

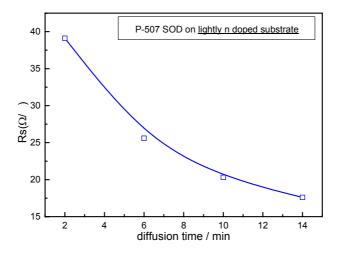

| Fig. 4-11 Sheet resistance of the wafer doped using SOD P507 diffusion at 1000°C                                             | . 75 |

| Fig. 4-12 Sheet measured resistance of the sample covered by SOD B150 film. Diffusion                                        |      |

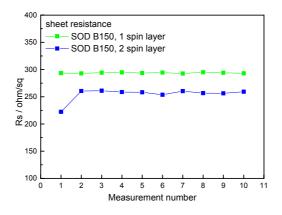

| parameter: 1100°C for 60 minutes                                                                                             | . 76 |

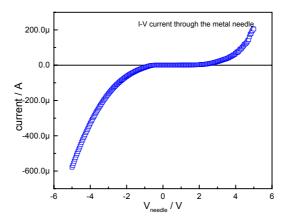

| Fig. 4-13 <i>I-V</i> curve of the metal-pSi diode shows the Schottky diode characteristic                                    | . 76 |

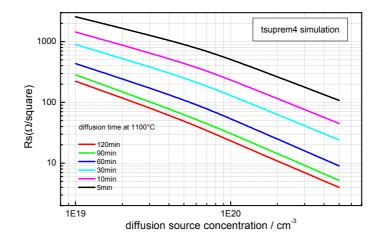

| Fig. 4-14 Simulation of the sheet resistance obtained by p-type diffusion doping                                             | . 77 |

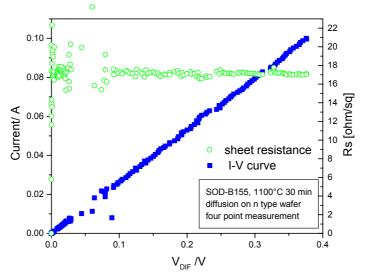

| Fig. 4-15 Four-point sheet resistance measurement result of wafer with SOD B155 diffusion a                                  | at   |

| 1100°C for 30 minutes                                                                                                        | . 77 |

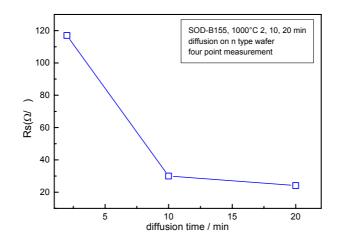

| Fig. 4-16 Sheet resistance of the boron doped layer measured by 4-point measurement, diffusion                               | ion  |

| source: SOD B155                                                                                                             | . 78 |

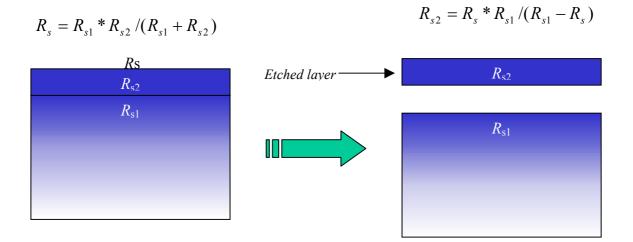

| Fig. 4-17 Calculation of the sheet resistance of the removed layer                                                           | . 78 |

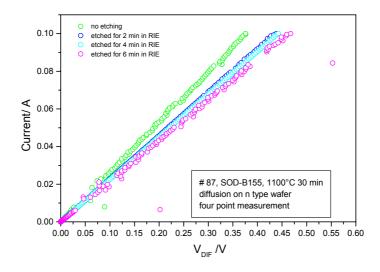

| Fig. 4-18 Sheet resistance measurement results of wafer #87 after RIE with an etching rate of                                |      |

| 20nm/min                                                                                                                     | . 79 |

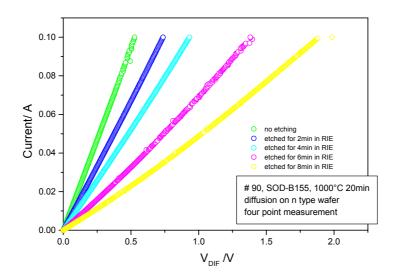

| Fig. | 4-19 Sheet resistance measurement results for wafer #90 after RIE with an etching rate of            | f    |

|------|------------------------------------------------------------------------------------------------------|------|

|      | 20nm/min                                                                                             | . 79 |

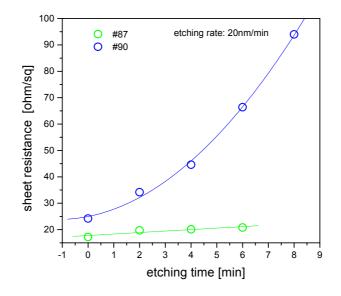

| Fig. | 4-20 Sheet resistance vs. etching time for wafers #87 and #90                                        | . 80 |

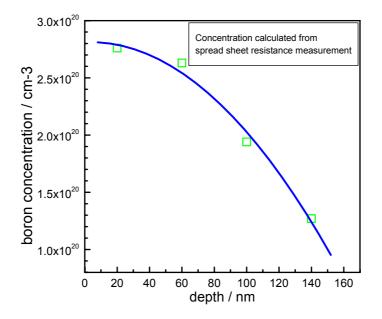

| Fig. | 4-21 Calculated doping profile of wafer #90 with the SOD B155.diffusion at 1000°C for                | 20   |

|      | minutes                                                                                              | . 81 |

| Fig. | 4-22 Picture of the RTCVD system (JETLIGHT 200)                                                      | . 82 |

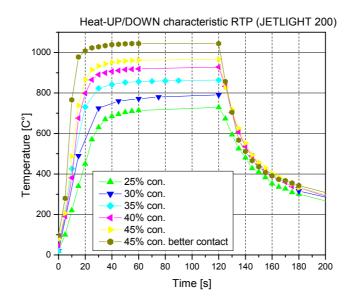

| Fig. | 4-23 Heat-up/ down characteristic of JETLIGHT 200                                                    | . 82 |

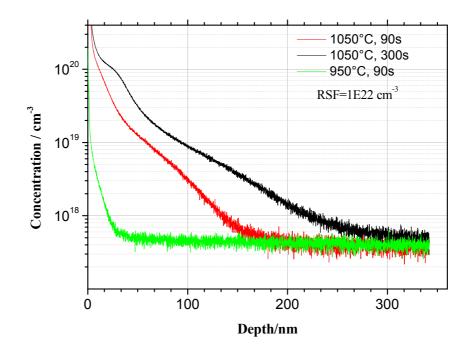

| Fig. | 4-24 SIMS measured phosphorous depth profile in Si after the RT-Diffusion                            | . 83 |

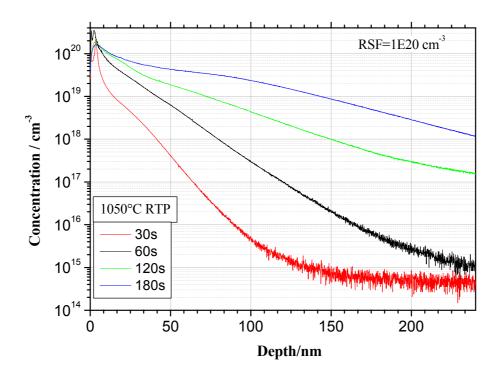

| Fig. | 4-25 SIMS measured boron depth profile in Si after the RT-Diffusion                                  | . 84 |

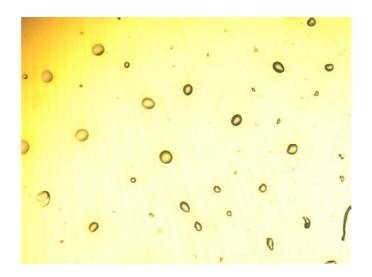

| Fig. | 4-26 Nodes on the SOD layer after absorbing water                                                    | .85  |

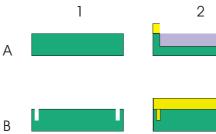

| Fig. | 4-27 Proposed TFET fabrication processes sequence using SOD diffusion                                | . 86 |

| Fig. | 4-28 Formation of self-aligned Poly-Si sidewall gate using SOD planarity flow                        | .86  |

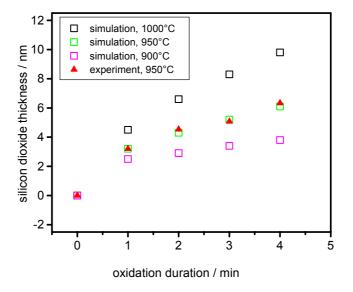

| Fig. | 4-29 Experimental and simulated oxidation rates in the normal thermal oxidation oven                 | .87  |

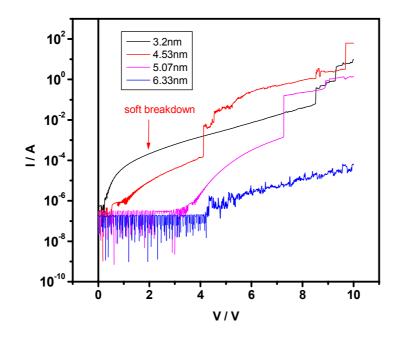

| Fig. | 4-30 <i>I-V</i> characteristics of the oxide with various thicknesses grown at 950°C                 | . 88 |

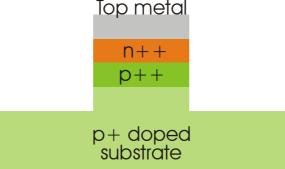

| Fig. | 5-1 Schematic structure of the vertical diode fabricated using the out-diffusion of SOD              | .92  |

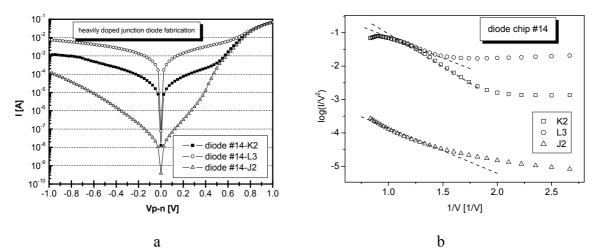

| Fig. | 5-2 Characteristic of several diodes fabricated in the RTP chamber using p and n type                |      |

|      | diffusion on $p^+$ substrate (left); Plot using $log(I/V^2)$ as the Y axis and $1/V$ as the X axis,  |      |

|      | data are derived from the reversed diode region (right). (from diode wafer #14)                      | .92  |

| Fig. | 5-3 Electrical characteristics and linear fitting using $\log(I/V^2)$ as the Y axis and $1/V$ as the | e    |

|      | X axis. (diode #7-C5)                                                                                | .93  |

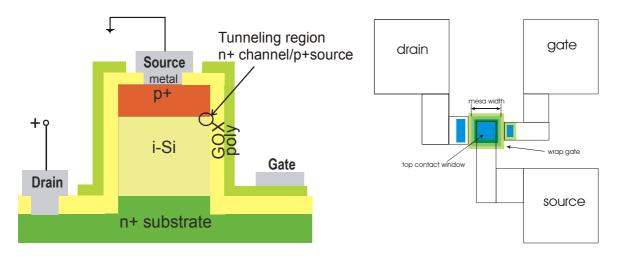

| Fig. | 5-4 Structural design of vertical MBE doping TFET                                                    | .94  |

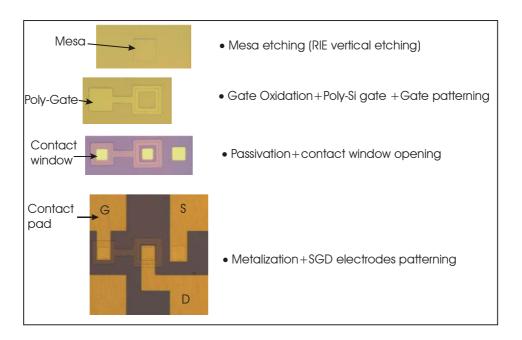

| Fig. | 5-5 Process sequence and corresponding patterns in the fabrication                                   | .94  |

| Fig. | 5-6 Structure of the vertical TFET mesa                                                              | .95  |

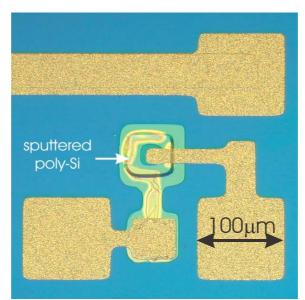

| Fig. | 5-7 Device with poor quality sputtered Si gate                                                       | .95  |

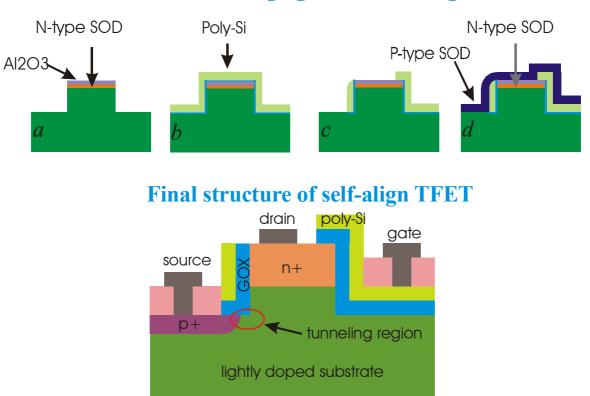

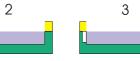

| Fig. | 5-8 4-mask process sequence of the vertical self-aligned SOD-TFET                                    | .96  |

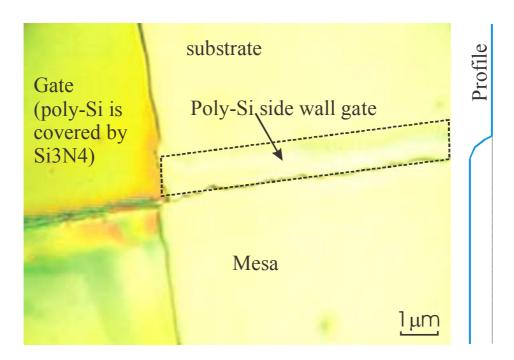

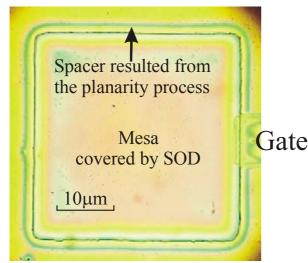

| Fig. | 5-9 Spacer surrounding the vertical mesa after the planarity process                                 | .97  |

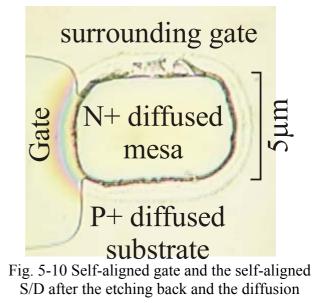

| Fig. | 5-10 Self-aligned gate and the self-aligned S/D after the etching back and the diffusion             |      |

|      | process                                                                                              | .97  |

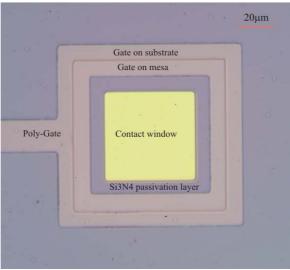

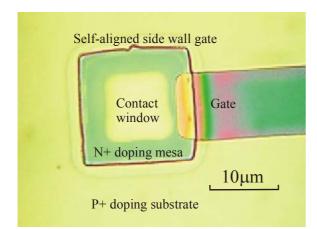

| Fig. | 5-11 Self-aligned device after passivation layer deposition and contact window lithograp             | hy   |

|      |                                                                                                      | .98  |

| Fig. | 5-12 Schematic final structure of the vertical transistor with the self-aligned spacer gate .        | .98  |

| Fig. | 5-13 Transfer characteristics of a vertical SOD-TFET                                                 | .98  |

| Fig. | 5-14 Output characteristics of a vertical SOD-TFET                                                   | .99  |

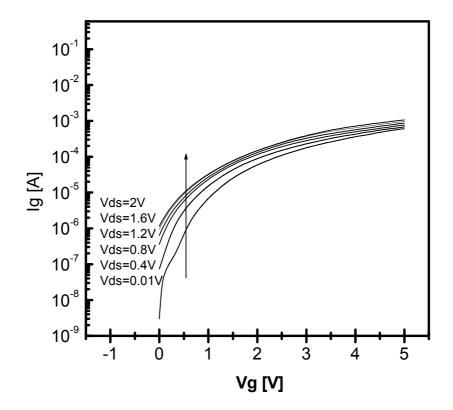

| Fig. 5-15 Dependence of the gate leakage current on $V_g$ . The gate oxide is formed at 950°C to | for 4 |

|--------------------------------------------------------------------------------------------------|-------|

| minutes                                                                                          | 99    |

| Fig. 5-16 6-mask fabrication process of the planar SOD-TFET                                      | 100   |

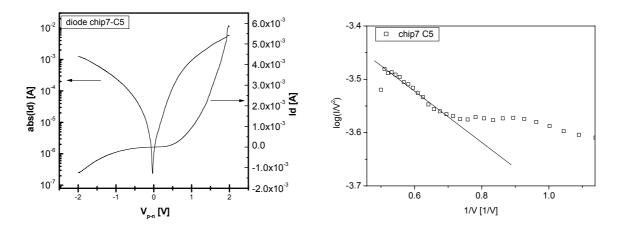

| Fig. 5-17 Mask set designed for the 6-mask planar SOD-TFET fabrication                           | 101   |

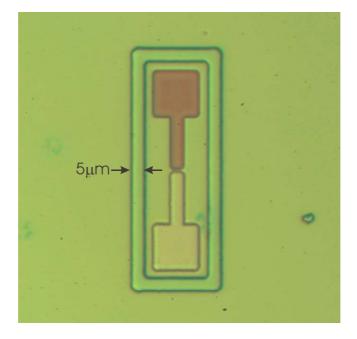

| Fig. 5-18 Plot of the planar TFET in the mask set                                                | 102   |

| Fig. 5-19 Transfer characteristics of the planar TFET fabricated using 6 masks                   | 102   |

| Fig. 5-20 Gate leakage current of the 6-mask planar TFET                                         | 103   |

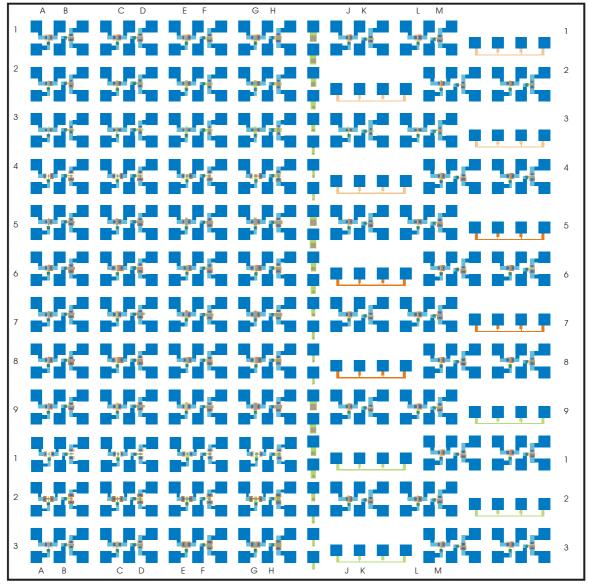

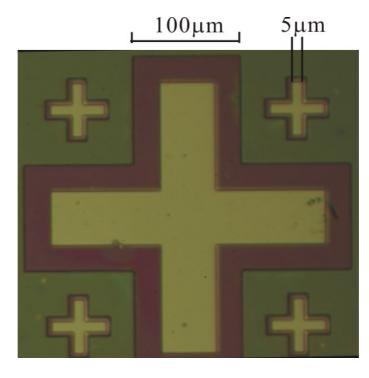

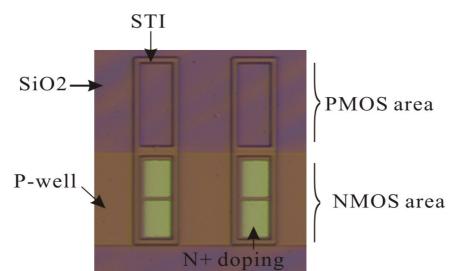

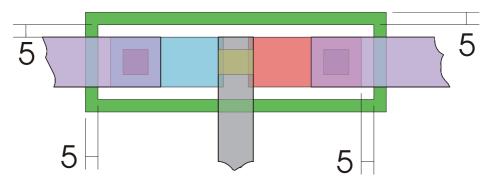

| Fig. 5-21 Mask set for the planar TFET with STI and TFET circuits                                | 104   |

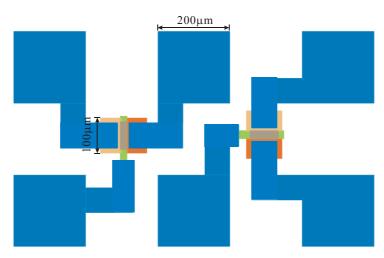

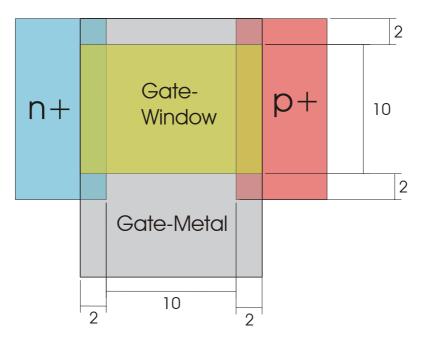

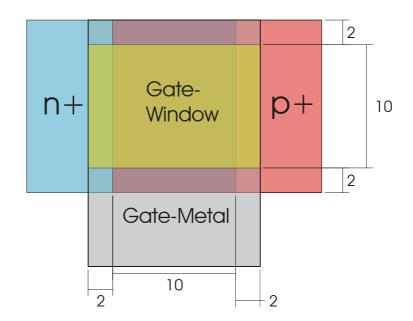

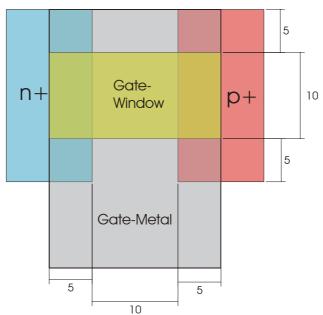

| Fig. 5-22 Single planar TFET with STI                                                            | 104   |

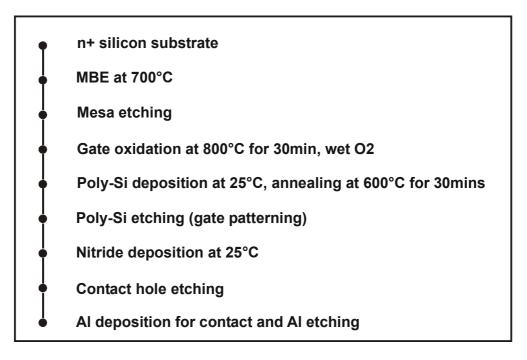

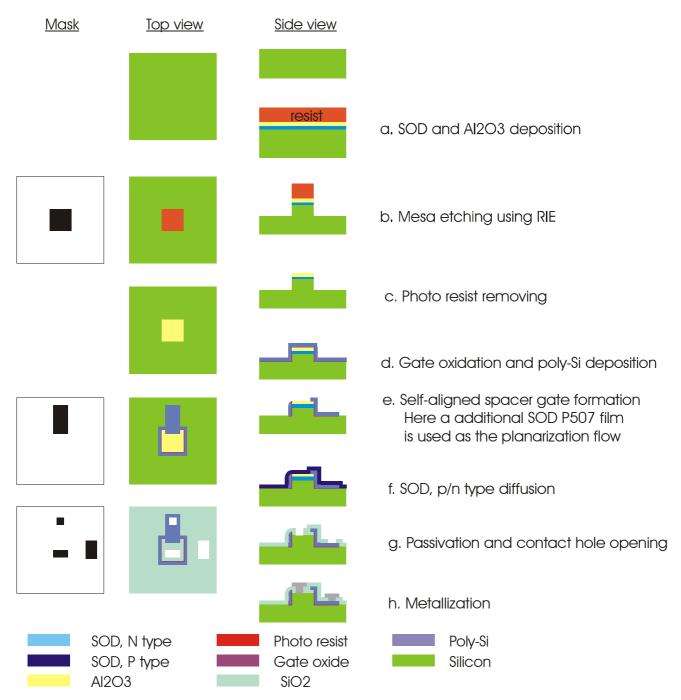

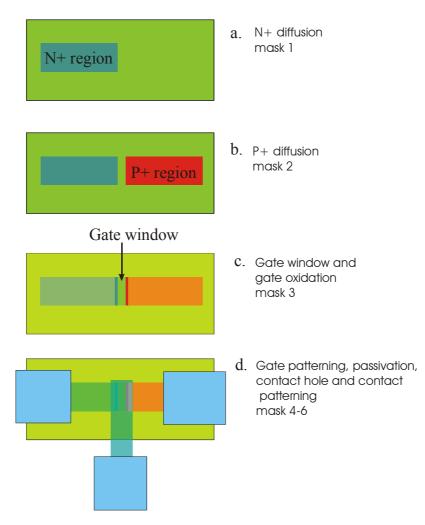

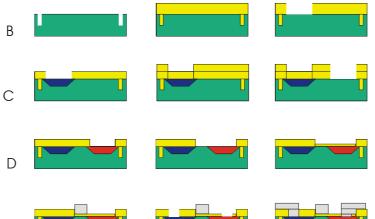

| Fig. 5-23 Process sequence for the second version TFET fabrication                               | 105   |

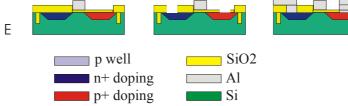

| Fig. 5-24 5-crosses alignment for Karl Süss MJB-55 alignment machine                             | 107   |

| Fig. 5-25 Structure of the inverters composed by NTFET and PMOS (not finished structure)         | 108   |

| Fig. 5-26 Final structure of a NTFET without STI                                                 | 108   |

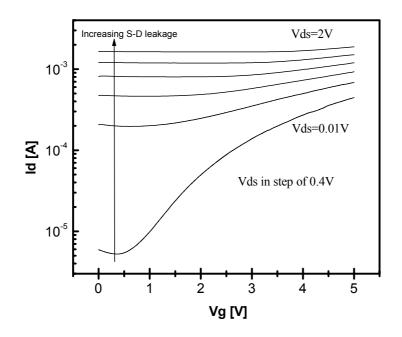

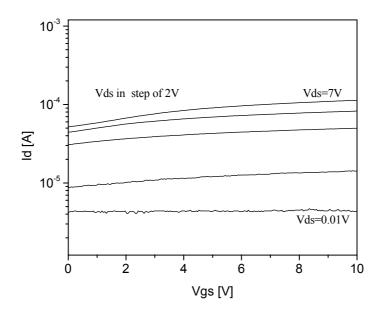

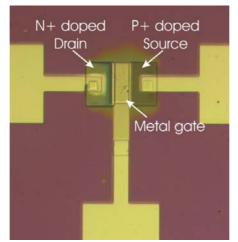

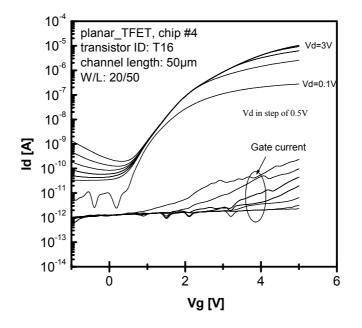

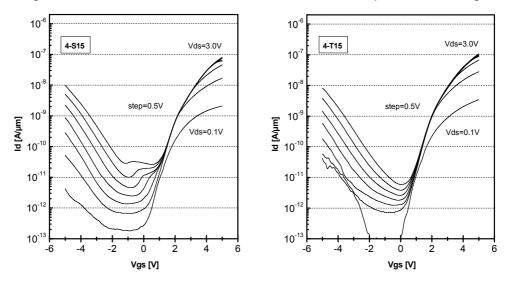

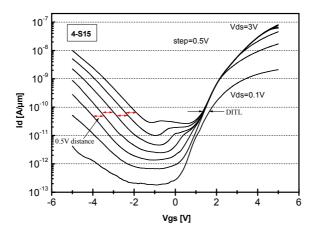

| Fig. 5-27 Measured transfer characteristics of the planar SOD-NTFET                              | 109   |

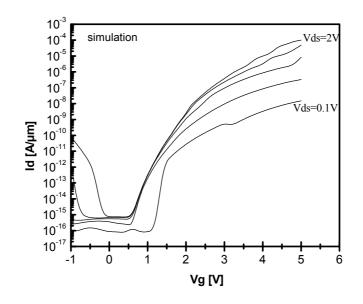

| Fig. 5-28 Simulated transfer characteristics of the planar NTFET with 5nm gate oxide             | 110   |

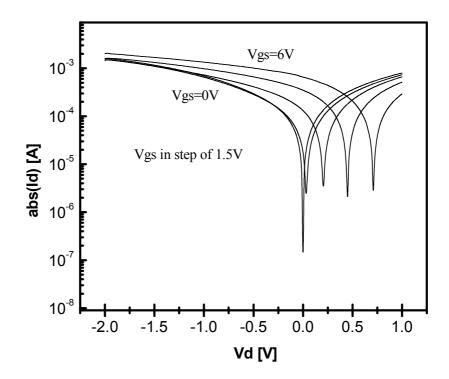

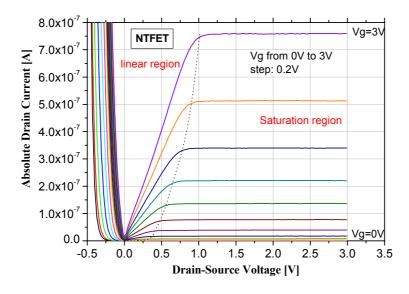

| Fig. 5-29 Measured output characteristics of the transistor T16                                  | 110   |

| Fig. 5-30 Simulated output characteristics of the planar NTFET with 5nm gate oxide               | 111   |

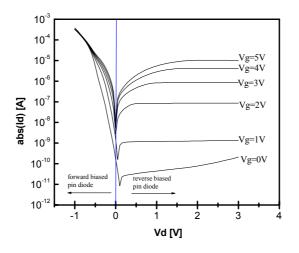

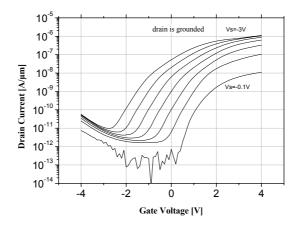

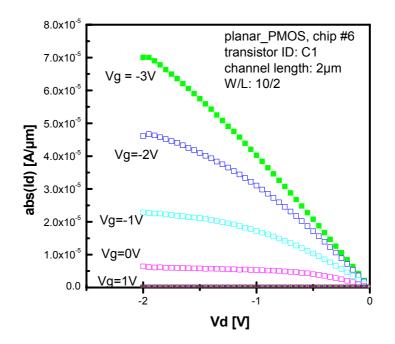

| Fig. 5-31. Transfer characteristics of the PTFET with fixed $V_s$ . ID: 4-N3                     | 111   |

| Fig. 5-32 Output characteristics of the PTFET, transistor ID: 4-N3                               | 112   |

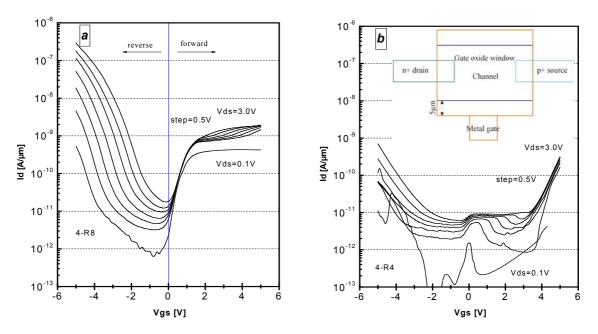

| Fig. 5-33 Transfer characteristics of 4-R8 and 4-R4 with the same structures                     | 113   |

| Fig. 5-34 Transfer characteristics of the TFETs with 1µm channel length                          | 114   |

| Fig. 5-35 Transfer characteristics of the TFETs with 2µm channel length                          | 114   |

| Fig. 5-36 Transfer characteristics of the TFETs with 4µm channel length                          | 114   |

| Fig. 5-37 Transfer characteristics of the TFETs with 6µm channel length                          | 115   |

| Fig. 5-38 Transfer characteristics of the TFETs with 10µm channel length                         | 115   |

| Fig. 5-39 Transfer characteristics of the TFETs with 20µm channel length                         | 115   |

| Fig. 5-40 Transfer characteristics of the TFETs with 50µm channel length                         | 116   |

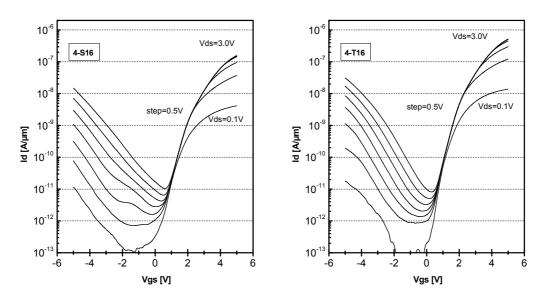

| Fig. 5-41 Gate breakdown is observed in the transfer characteristics of TFET 1-C1 (a); Trans     | sfer  |

| characteristics of TFET 1-B2 (b); Transfer characteristics of TFET 1-B3 (c)                      | 116   |

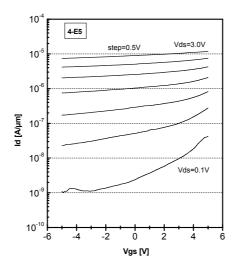

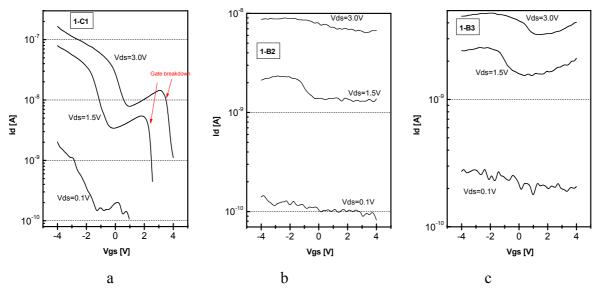

| Fig. 5-42 Transfer characteristics of several working TFETs in wafer #6                          | 117   |

| Fig. 5-43 Pt gate metal is lifted away during the process because of the poor adhesion on SiC    | )2    |

|                                                                                                  | 118   |

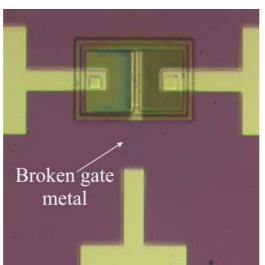

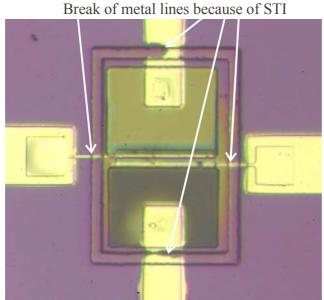

| Fig. 5-44 A defect TFET because STI causes break of metal lines                                  | 118   |

| Fig. 5-45 Transfer characteristics of TFET measured using the $n^{\scriptscriptstyle +}$ region as drain and the $p^{\scriptscriptstyle +}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| region as source. (source is grounded)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .120         |

| Fig. 5-46 Transfer characteristics of a NTFET measured with a grounded $n^+$ drain and different difference of the second secon                                                                                                                                     | ent          |

| source voltages. The shift of current curves with $V_s$ variation is observed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .121         |

| Fig. 5-47 Transfer characteristics of the PTFET with various $V_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .121         |

| Fig. 5-48 Linear plot of one measured NTFET output characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .122         |

| Fig. 5-49 Linear plot of the measured on-wafer PMOS output characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 122        |

| Fig. 5-50 Band diagrams of NTFET along the cutline 5nm beneath the gate oxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .123         |

| Fig. 5-51 Pinch-off of the channel in a TFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .123         |

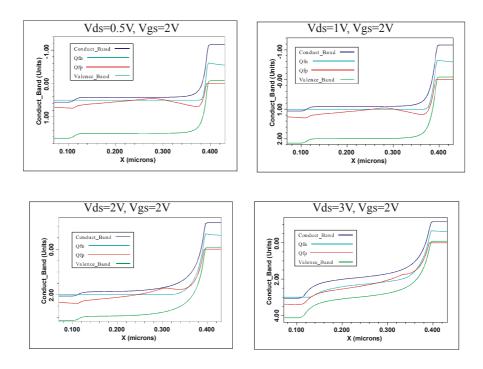

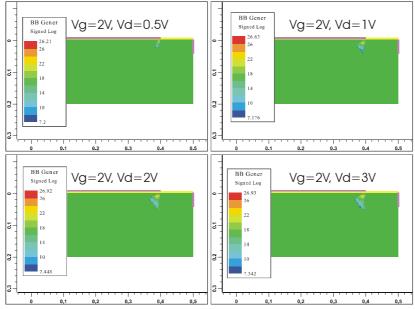

| Fig. 5-52 Band-to-band tunneling generation rates in TFET, when $V_{ds}$ is increased from 0.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | / to         |

| 3V (V <sub>gs</sub> remains 2V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .124         |

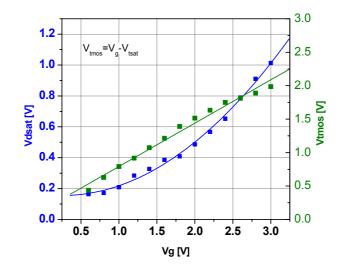

| Fig. 5-53 Dependence of $V_{dsat}$ and $V_{tmos}$ on $V_{gs}$ in NTFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .124         |