## Technische Universität München Lehrstuhl für Technische Elektronik Fachgebiet Halbleiterproduktionstechnik

# Development and Electrical Characterization of Air Gap Structures for Advanced Metallization Schemes

## **Andreas Stich**

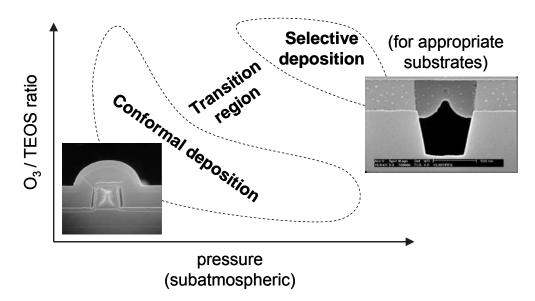

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

**Doktor-Ingenieurs (Dr.-Ing.)**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.rer.nat. Gerhard Wachutka

Prüfer der Dissertation: 1. Univ.-Prof. Dr. Ing. Walter Hansch

2. Univ.-Prof. Dr.rer.nat Ignaz Eisele, Universität der Bundeswehr München

Die Dissertation wurde am 12.10.2006 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 27.02.2007 angenommen.

Abstract

#### **Abstract**

The *RC*-delay and crosstalk noise of the interconnect system are major problems in modern and future high-performance semiconductor chips. For that reason, the coupling capacitance or the *k*-value of the insulator between the metal lines has to be reduced, which can be achieved by substituting SiO<sub>2</sub> by so-called low-*k* materials or by integration of cavities, called air gaps. In this work, air gaps fabricated by the selective O<sub>3</sub>/TEOS deposition are considered for reduction of the line-to-line capacitance. Different integration schemes with air gaps were fabricated; air gaps requiring an additional lithography in a single and double layer Cu damascene metallization, self-aligned air gaps in Cu and in tungsten metallization, utilizing RIE (reactive ion etch) processing and air gaps fabricated by use of non-conformal deposition processes for the insulator in a 90nm Al RIE metallization scheme. For comparison of the properties of air gaps, structures were fabricated with and without air gaps.

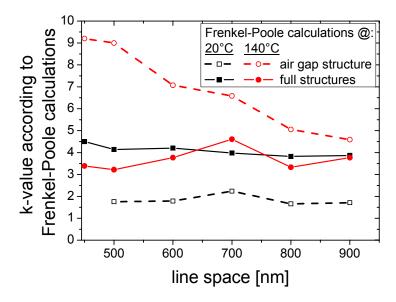

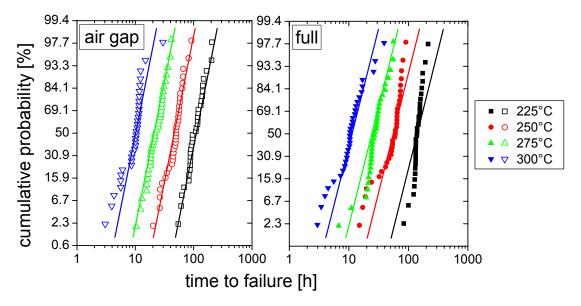

The investigation shows that air gaps offer a substantial reduction of the line-to-line capacitance up to 50%, corresponding to an effective k-value of  $k_{eff} = 2.3$  while using of standard SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> as materials of choice for the insulator. Measurements from the first to the second metal layer show, as expected, only a marginal reduction of the coupling capacitance of 10%. It could be shown that due to the hybrid structure of air gaps, the crosstalk can be reduced more efficiently than with a uniform low-k material. As a consequence of the high aspect ratio of the metal lines, the self-aligned air gaps in Al RIE metallization results in a very low effective k-value ( $k_{eff} = 1.8$ ). All  $k_{eff}$ -values obtained by simulations are in good agreement with the measured capacitance values. The  $k_{eff}$ -value strongly depends on the geometry variations, which have been evaluated by additional simulations and can be optimized by extending the air gaps above and below the metal lines and increasing the aspect ratio of the metal lines. Vertical and horizontal air gap displacements are not critical. A  $k_{eff} = 1.9$  was calculated for air gaps in SiO<sub>2</sub> material, a line aspect ratio of 2.0 and an air gap height of 1.4 times the line height. The breakdown field strength of air gap structures is lower (5-6MV/cm) than of full structures (8.4MV/cm). Compared to full structures, the leakage current of air gap structures is 30% higher at an electric field strength of 1MV/cm and 125°C. This can be explained by surface leakage currents and field enhancement inside the air gaps. The conduction mechanism between metal lines isolated by air gap structures can be described by the Frenkel-Poole mechanism at 20°C and Schottky emission at 140°C. A Frenkel-Poole behavior of full structures can be seen at all temperatures. Electromigration reliability tests showed an activation energy value of  $E_a = 0.79 \pm 0.05 \text{eV}$  and current density exponent of  $n = 1.1 \pm 0.2$  for air gaps and  $E_a = 0.83 \pm 0.07$  eV,  $n = 1.1 \pm 0.2$  for full structures. Despite totally different failure mechanisms observed by SEM, the structures show comparable extracted lifetimes of 10.6a for air gap and 9.6a for full structures at 105°C, 5mA/µm² use conditions. Finally, the impact of air gaps on self-heating of the metal lines was measured and simulated, showing a 75% higher temperature increase compared to structures in dense SiO<sub>2</sub>. In relation to the integration of porous low-k materials as intermetal and interlevel dielectric, the temperature increase of air gaps is only one quarter.

The results show that air gaps fabricated by the selective O<sub>3</sub>/TEOS deposition can be integrated in a damascene or RIE metallization scheme. They display very promising electrical properties and exhibit an attractive alternative to low-k or ultra-low-k materials.

Contents

## **Contents**

| A | bstrac      | Ct                                                                           | iii        |

|---|-------------|------------------------------------------------------------------------------|------------|

| 1 | Intro       | oduction                                                                     | 1          |

| 2 | Inter       | connect system in advanced semiconductor technology                          | 5          |

|   | 2.1         | Requirements for advanced interconnects according to the ITRS                | 6          |

|   | 2.2         | RC-delay in interconnects                                                    |            |

|   | 2.3         | Crosstalk in interconnects                                                   | 9          |

|   | 2.4         | Interconnect fabrication techniques                                          | 10         |

|   |             | 2.4.1 Interconnects by reactive ion etching (RIE)                            | 10         |

|   |             | 2.4.2 Interconnects by damascene technology                                  |            |

|   | 2.5         | Requirements for the intermetal dielectric (IMD)                             | 11         |

|   | 2.6         | Low-k materials as IMD materials                                             |            |

|   |             | 2.6.1 Dense low-k materials                                                  |            |

|   |             | 2.6.2 Porous low- <i>k</i> materials                                         |            |

|   | 2.7         | Air gaps as an alternative approach                                          |            |

|   |             | 2.7.1 Gas dome concept as ultimate low-k solution                            |            |

|   |             | 2.7.2 Air gap fabrication with the sacrificial layer approach                | 19         |

|   |             | 2.7.2.1 Carbon layer as sacrificial material.                                |            |

|   |             | 2.7.2.2 Low-k material as sacrificial layer and porous capping layer         | 21         |

|   |             | 2.7.2.3 Silicon oxide as sacrificial layer                                   | 22         |

|   |             | 2.7.3 Air gaps by non-conformal CVD deposition                               | 23         |

|   |             | 2.7.3.1 Air gaps in a RIE metallization scheme                               | 23         |

|   | 2.0         | 2.7.3.2 Air gaps in a damascene metallization scheme                         | 24         |

|   | 2.8         | Capacitance and $k_{eff}$ of interconnects                                   |            |

|   |             | 2.8.1 Plate capacitor and fringe fields                                      |            |

|   |             | 2.8.2 Capacitance simulations with Maxwell Spicelink                         |            |

|   |             | 2.8.3 Effective k-value of interconnects.                                    |            |

|   | 2.0         | 2.8.4 Measurement of the capacitance                                         |            |

|   | 2.9         | Reliability of the interconnect system 2.9.1 Electromigration of metal lines |            |

|   |             | 2.9.2 Leakage current and conduction mechanism through dielectrics           |            |

|   |             | 2.9.3 Dielectric breakdown of gases at micrometer spaces                     |            |

|   | 2.10        | Power dissipation and thermal crosstalk of interconnects                     |            |

| 3 | CVD         | O <sub>3</sub> /TEOS process                                                 | <i>1</i> 1 |

| J |             | Properties of the CVD O <sub>3</sub> /TEOS deposition                        |            |

|   | 3.1 3.2     | <u> </u>                                                                     |            |

|   | 3.2         | Selective O <sub>3</sub> /TEOS process                                       |            |

|   | 3.3         | 3.3.1 Selectivity caused by hydrophilicity                                   |            |

|   |             | 3.3.2 Selectivity caused by electronegativity                                |            |

|   |             | 3.3.3 Selectivity caused by hydrogen saturation on surface                   |            |

|   | 3.4         | Selectivity experiments on blanked wafers                                    |            |

|   | J. <b>⊤</b> | Scientify experiments on blanked waters                                      | 70         |

vi Contents

|   |      | 3.4.1    | Dense growth of selective O <sub>3</sub> /TEOS                        | 48   |

|---|------|----------|-----------------------------------------------------------------------|------|

|   |      | 3.4.2    | Swiss cheese effect of selective O <sub>3</sub> /TEOS growth          | 50   |

|   |      | 3.4.3    | Summary of selective O <sub>3</sub> /TEOS deposition                  | 52   |

| 4 | Fabi | ricated  | air gap structures                                                    | 55   |

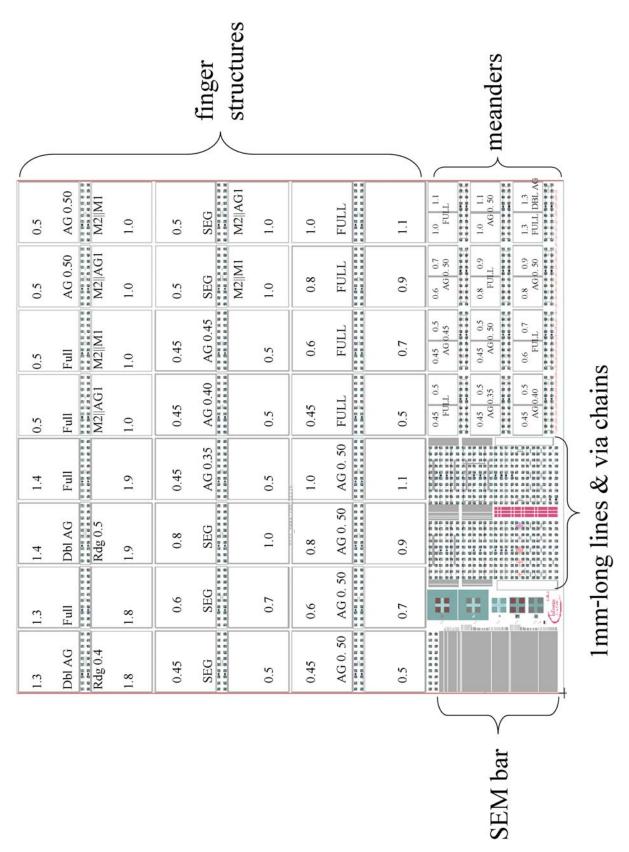

|   | 4.1  | Test c   | hip structures                                                        | 55   |

|   |      | 4.1.1    | Mask set of the test chip                                             | 55   |

|   |      | 4.1.2    | Comb structures                                                       | 56   |

|   |      | 4.1.3    | Structure for SEM analysis                                            | 57   |

|   |      | 4.1.4    | Reliability structures                                                | 57   |

|   |      |          | Crosstalk structures                                                  |      |

|   |      | 4.1.6    | Additional test structures                                            | 59   |

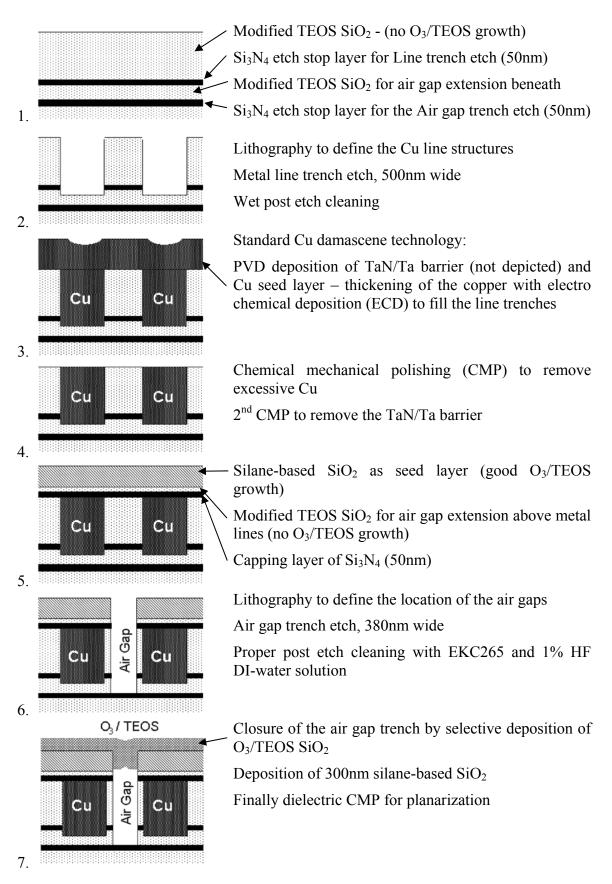

|   | 4.2  | Air ga   | nps by additional lithography                                         | 59   |

|   |      | 4.2.1    | Processing scheme of air gaps by lithography                          | 59   |

|   |      | 4.2.2    | Preparation and SEM inspection of air gaps by lithography             |      |

|   |      | 4.2.3    | Process challenges                                                    | 64   |

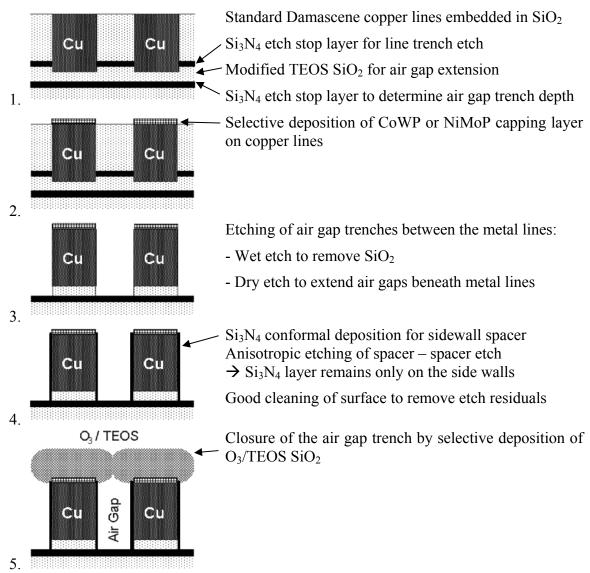

|   | 4.3  | Self-a   | ligned air gap approach in damascene metallization                    |      |

|   |      | 4.3.1    | Process steps for self-aligned air gap approach                       |      |

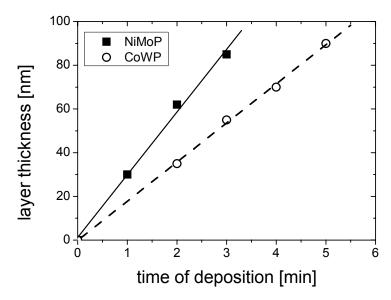

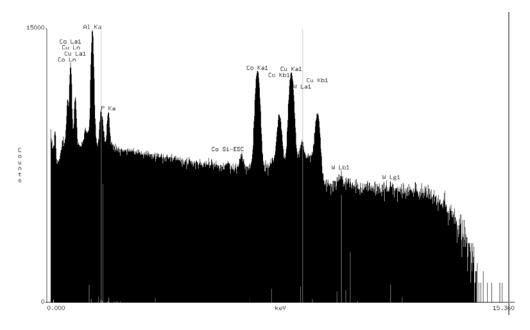

|   |      | 4.3.2    | Properties and deposition of selective metal barriers                 |      |

|   |      | 4.3.3    | Plasma cleaning and SEM analysis of self-aligned air gaps             |      |

|   | 4.4  | Self-a   | ligned air gap approach in RIE metallization                          |      |

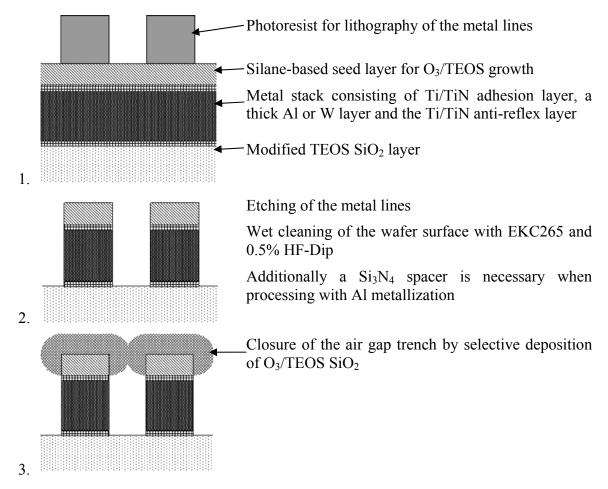

|   |      | 4.4.1    | Process steps                                                         |      |

|   |      | 4.4.2    | Air gaps in tungsten RIE metallization                                |      |

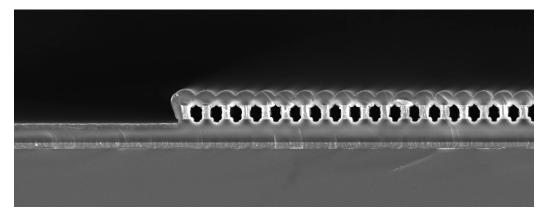

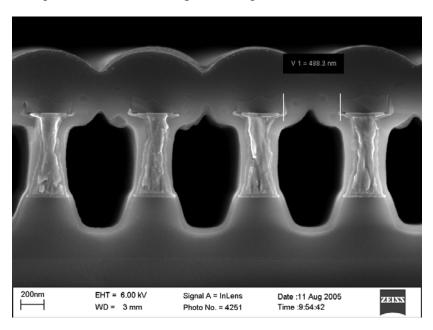

|   |      |          | Air gaps in 90nm aluminum RIE metallization                           |      |

| 5 | Elec | trical c | characterization                                                      | 81   |

|   | 5.1  | Capac    | eitance properties                                                    | 81   |

|   |      | 5.1.1    | Capacitance simulations setup of fabricated structures                | 81   |

|   |      | 5.1.2    |                                                                       |      |

|   |      |          | 5.1.2.1 Results of air gaps in a single metal layer scheme            | 82   |

|   |      |          | 5.1.2.2 Results of air gaps in a double metal layer scheme            |      |

|   |      | 5.1.3    | Capacitance measurements of self-aligned air gaps                     |      |

|   |      | 5.1.4    | Simulations to demonstrate potential of air gaps                      | 88   |

|   |      |          | Simulations and measurements of air gaps in 90nm Al RIE metallization |      |

|   | 5.2  |          | etric reliability performance                                         |      |

|   |      | 5.2.1    | Dielectric breakdown of air gap and full structures                   | 94   |

|   |      | 5.2.2    | Leakage current of air gap and full structures                        |      |

|   |      | 5.2.3    | Breakdown voltage of air gaps                                         |      |

|   |      | 5.2.4    | Temperature dependence of dielectric breakdown                        |      |

|   |      | 5.2.5    | Simulations of the dielectric field distribution inside air gaps      | 98   |

|   |      | 5.2.6    | Conduction mechanism                                                  | 99   |

|   | 5.3  | Resist   | ance and resistivity of interconnects with air gaps                   | .101 |

|   | 5.4  | Reliat   | pility against electromigration                                       | .102 |

|   |      |          | Electromigration results                                              |      |

|   |      |          | Post electromigration analysis                                        |      |

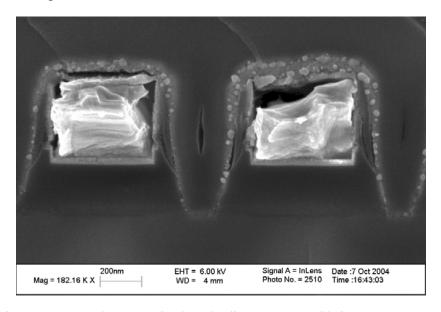

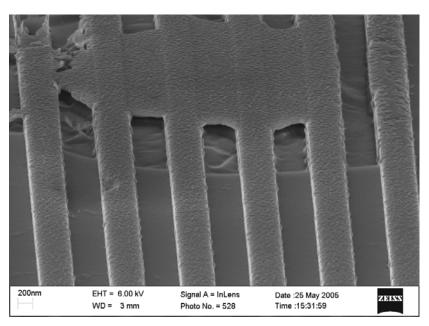

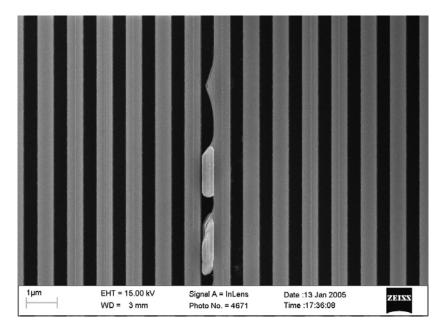

|   |      |          | 5.4.2.1 Void formation during electromigration stress test            | .104 |

|   |      |          | 5.4.2.2 Extrusion of copper during electromigration stress test       | .106 |

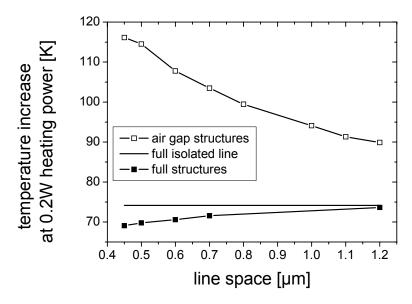

|   | 5.5  | Thern    | nal conductivity with air gaps                                        |      |

|   |      | 5.5.1    | Measurements of thermal properties                                    | .108 |

|   |      |          |                                                                       |      |

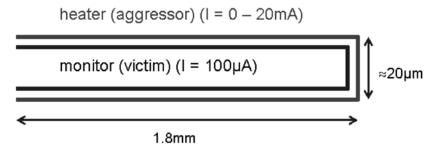

|              | 5.5.1.1 Self-heating measurements      | 108 |

|--------------|----------------------------------------|-----|

|              | 5.5.1.2 Thermal crosstalk measurements | 109 |

| 5.5.2        | Simulations of thermal crosstalk       | 110 |

| 6 Conclusion | 1                                      | 115 |

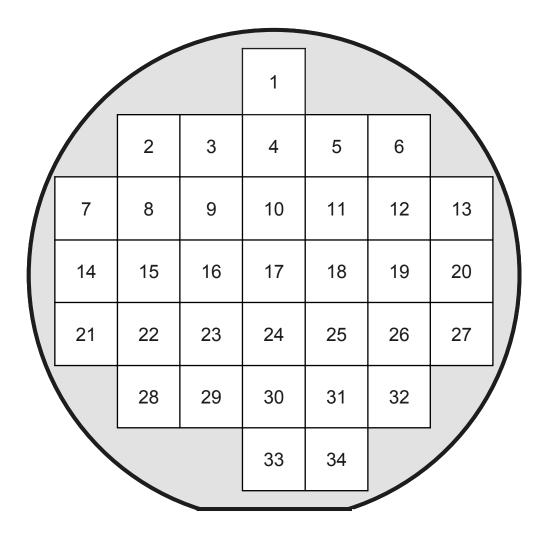

| Appendix A:  | Die layout on wafer and mask layout    | 119 |

| Appendix B:  | Structures on test chip                | 121 |

| Appendix C:  | Process recipes                        | 123 |

| Symbols and  | abbreviations                          | 125 |

| Figures      |                                        | 129 |

| Tables       |                                        | 133 |

| Publications |                                        | 135 |

| Acknowledgn  | nents                                  | 137 |

| Rihliography |                                        | 130 |

Introduction 1

#### 1 Introduction

The information technology revolution and enabling era of semiconductor integration have initiated an ever-increasing level of functional on-chip integration, driven by the need for higher circuit complexity, higher power density and higher operating frequencies. The larger number of transistors and bigger chip sizes lead to a more complex interconnect system. The number of wires increases with the square of the number of transistors and their average length increases linearly with the chip size. The functionality of an interconnect system is to distribute clock, data buses and other signals and to provide power/ground to and among the various circuits and systems on a chip. As gate lengths of the transistors approach 50nm and below, there is a demand for interconnect widths to decrease to similar dimensions. While traditional transistor scaling has thus far met this challenge, multilevel wiring is increasingly becoming a bottleneck in the fabrication of high-performance circuits. The growing influence of interconnect parasitics on crosstalk noise and RC-delay as well as electromigration and power dissipation concerns have stimulated the introduction of low-resistivity copper and low dielectric constant materials to provide performance and reliability enhancement [Hav01].

The industry is still in the process of a very difficult transition from silicon dioxide, silicon nitride and the dual damascene integration process to low-k and ultra-low-k materials. These dielectric materials exhibit some of the best combinations of mechanical, electrical, and chemical stability properties that integration engineers have had the luxury of working with. Although integrated circuits with copper-based metalization were introduced in 1998 with silicon dioxide as intermetal dielectric, the lowering of insulator dielectric constant predicted by the ITRS has been problematic. Instead of the revolutionary path contemplated in the ITRS 2001 document, the industry has chosen an overall evolutionary path. Fluorine doped silicon dioxide k = 3.7 was introduced at 180nm, however, insulating materials with k = 2.7 - 3.0 were not widely used until 90nm [ITR05]. Even at 60nm, the effective k-value will be still around 3.0 and only dense materials will be used. It is even believed that it will be very challenging to reduce the effective k-value far below 3.0 for future technology nodes.

The slower than projected pace of low-k dielectric introduction for microprocessors (MPUs) and application-specific ICs (ASICs) comes from the unexpected challenging reliability and yield issues associated with integration of these materials with dual damascene copper processing. The integration of porous low-k materials is expected to be even more challenging. Since the development and integration of these new low-k materials is rather time-invariant, the predicted acceleration of the MPU product cycle (two versus three years until 2009) will shift the achievable k to later technology generations. The introduction of these new low dielectric constant materials, along with the reduced thickness and higher conformity requirements for barriers and nucleation layers, pose a difficult integration challenge. Further challenges like resist poisoning, precise etching of porous materials, sidewall damage during etching, which increases the k-value, pore sealing to reduce diffusion, UV cure to repair the material, to name just some of them, have to be taken into consideration. Because of the foam-like structure of porous

2 Introduction

materials, the contact with wet cleaning, etch solutions, water rinse or other liquid agents is problematic since the liquid penetrates into the film and especially water increases the k-value dramatically since it has a k-value of k = 80. Moreover, these new materials suffer from mechanical and thermal stability issues, reliability degradation, high metal diffusion, higher leakage currents and low dielectric breakdown field strength.

As of 2012, according to the ITRS, ultra-low-k dielectrics with k < 2.0 (ULK) will be required. Novel integration schemes may be necessary, such as air gap architecture – a hybrid dielectric stack utilizing air [ITR05]. The term "air gaps" describes cavities between adjacent metal lines filled with air or gas, or being under vacuum with a dielectric constant close to k = 1.0. Of course, the overall effective k-value is in practice larger than 1.0 since the metal lines have to be supported by some solid material. To obtain air gaps, several integration schemes are being pursued. The most straightforward approach is to remove the dielectric between the metal lines and then deposit another dielectric layer with a very non-conformal process [Arn01]. This will leave the gaps between the lines mainly unfilled. The air gaps extend above the top surface of the Cu lines and form domeshaped voids. Despite its simplicity, this process has the drawback that for a wide spacing of the Cu lines the voids might become too high and be damaged by the subsequent metallization layer. The second approach uses a sacrificial material in which the Cu lines are embedded. The sacrificial material is capped by a porous dielectric. After the damascene process, the sacrificial material is then removed for example by a thermal process to vaporize the sacrificial material, leaving the air gaps [Daa05]. This way the air gaps fill only part of the space between the lines and moreover new porous materials need to be integrated.

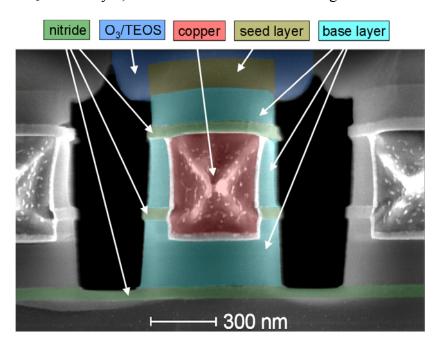

The motivation of this work was to integrate and characterize air gap structures fabricated by the selective O<sub>3</sub>/TEOS deposition as an alternative to porous ultra-low-*k* materials. The major advantage of the integration of such air gaps is that exclusively well-known conventional dielectric materials are used to achieve an effective *k*-value of as low as 2.4. The key process of our air gap fabrication is the selective O<sub>3</sub>/TEOS deposition, which is an ozone activated deposition of SiO<sub>2</sub> with TEOS as precursor. This process can be treated such that the deposition only takes place on a "seed" material and is suppressed on a "base" material. The selective O<sub>3</sub>/TEOS growth was performed on a variety of materials to investigate candidates as seed or base material. The basic principle of this selective process leads to a structure with base material on the sidewalls of the air gap trench and seed material at the top surface of the wafer. Since the selective O<sub>3</sub>/TEOS only grows on the seed material, the air gaps are closed. The advantage over the non-conformal approach is the isotropic growth of the selective SiO<sub>2</sub> layer, which results in less high air gaps. Thus, the risk of opening the air gaps during CMP processing is reduced.

Various integration schemes were evaluated like air gaps in a two metal layer copper metallization scheme with an additional lithography, self-aligned air gaps in copper and tungsten RIE metallization, air gaps beneath metal lines and air gaps by non-conformal deposition in RIE aluminum metallization.

Another scope of this work was the overall characterization, like capacitance, leakage current, resistance, resistivity, breakdown voltage, thermal crosstalk, self-heating, mechanical properties and electromigration resistance of structures with air gaps compared to structures without air gaps. Further on, simulations of the line-to-line capacitance were performed to evaluate the effective k-value and simulations of thermal properties. The intention of this work is to highlight the advantages and risks of integrating air gaps by the

Introduction 3

selective O<sub>3</sub>/TEOS deposition and to compare their properties and characteristics to those of ultra-low-k materials. Besides integration and design, issues or potentials of air gaps within a modern metallization scheme will be discussed and assessed in detail.

## 2 Interconnect system in advanced semiconductor technology

The task of the interconnect system is to connect the active devices with each other and through bond pads, bond wires and pins with the outside of the chip. In recent times, the relative importance of the interconnect system called "Back End Of Line" has greatly increased, and will be likely to continue as integrated circuit technology progresses [Hav01]. The interconnect system itself consists of metal lines and via plugs, see Fig. 1. The metal lines are arranged in different levels and embedded in the intermetal dielectric (IMD). The interlayer dielectric (ILD) separates the different metal levels and comprises the via plugs, which connect the different metal levels. The interconnect system is hierarchically organized, divided in either global or local interconnects.

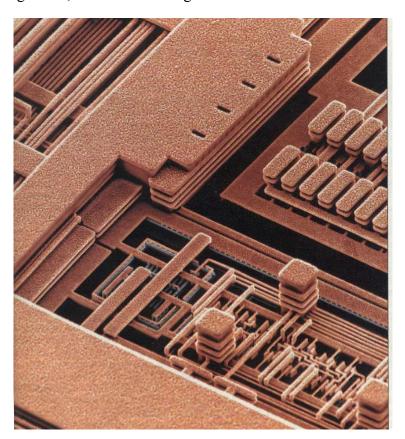

Fig. 1: Scanning electron microscope image of IBM's six-level copper interconnect technology [IBM98]

In general, local interconnects are the lowest level of interconnects, located just above the active devices. They usually directly connect the active semiconductor regions and gates in MOS technology or bases in bipolar technology. Therefore, local interconnects can afford to have higher resistivity than global interconnects since they are rather short

[The00]. The rest of the interconnect system above the local interconnects consists of global interconnects, mostly made of Al or Cu. They are much longer than local interconnects and connect different devices and even different blocks of the circuitry. For this purpose, metals with low resistivity are used.

## 2.1 Requirements for advanced interconnects according to the ITRS

The international technology roadmap for semiconductors (ITRS), the essence out of Moore's law, predicts the properties of future chips. In Table 1, an excerpt of the ITRS is depicted, showing the requirements for future interconnect systems [ITR05].

|                                                  | 2005    | 2006    | 2007    | 2008    | 2010    | 2013    | 2016    | 2020    |

|--------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| DRAM ½ pitch [nm]                                | 80      | 70      | 65      | 57      | 45      | 32      | 22      | 14      |

| Metal 1 A/R<br>(for Cu)                          | 1.7     | 1.7     | 1.7     | 1.8     | 1.8     | 1.9     | 2.0     | 2.0     |

| Conductor eff. resistivity [ $\mu\Omega$ ·cm]    | 3.15    | 3.29    | 3.47    | 3.67    | 4.08    | 4.83    | 6.01    | 8.19    |

| j <sub>max</sub> [A/cm <sup>2</sup> ] @<br>105°C | 8.9E+9  | 1.4E+6  | 2.1E+6  | 3.1E+6  | 5.1E+6  | 8.1E+6  | 1.5E+7  | 2.7E+7  |

| Intermetal insulator $k_{eff}$                   | 3.1-3.4 | 3.1-3.4 | 2.7-3.0 | 2.7-3.0 | 2.5-2.8 | 2.1-2.4 | 1.9-2.2 | 1.6-1.9 |

| Intermetal insulator $k_{bulk}$                  | ≤2.7    | ≤2.7    | ≤2.4    | ≤2.4    | ≤2.2    | ≤2.0    | ≤1.8    | ≤1.6    |

Table 1: ITRS predictions for the interconnect system [ITR05]

Manufacturable solutions exist and are being optimized

Manufacturable solutions are known

Manufacturable solutions are NOT known

According to the ITRS, the minimum metal line width for DRAMs will decrease from currently 70nm down to 22nm by 2016. In contrast, the aspect ratio of metal lines will further increase to lower the resistance increase with decreasing feature sizes. Unfortunately, this increase leads to a higher coupling capacitance of parallel lines [Hav01]. To reduce the coupling and RC-delays in interconnects, the k-value of the intermetal dielectric (IMD)  $k_{bulk}$  and the effective k-value  $k_{eff}$  between the metal lines is decreased. In former times,  $SiO_2$  with k = 3.9 - 4.2 was the standard dielectric material, whereas at the moment, materials with k-values of about 3 are in use. The conductor effective resistivity is increasing with smaller feature sizes. This effect is described by the size-effect which originates in a scattering of the electrons at the side walls and grain boundaries which becomes more prominent as the feature size approaches the mean free path of the electrons (~ 45nm for Cu at room temperature) [Ste05]. The current density  $J_{max}$  will increase from about  $1MA/cm^2$  in 2005 up to  $15MA/cm^2$  by 2016. Extreme high current densities lead to severe reliability problems of the interconnect system due to

electromigration of metal. All in all, these requirements initiate a lot of numerous challenges for the future.

## 2.2 RC-delay in interconnects

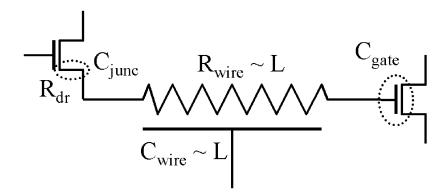

In integrated circuits, the RC-delay slows down the overall performance and raises the power consumption. In Fig. 2, a simple model of one metal line connected to two MOSFETs is depicted to show the different terms contributing to the overall signal delay  $\tau$ . The signal delay is the time a signal change at the input affects the output signal by 70.7% ( $1/\sqrt{2}$ ) of its total signal level. The resistive elements are the on-resistance of the driving transistor  $R_{dr}$  (which is between 10 - 12k $\Omega$  for all considered nodes), and the wire resistance  $R_{wire}$ . The capacitive elements are the junction and gate capacitance  $C_{junc}$ ,  $C_{gate}$  which originate from the active MOSFET device and the wire capacitance  $C_{wire}$  [Sch03]. These values are fixed because they are dependent of the dimensions of the MOSFET device.  $R_{dr}$  for example could only be reduced by a wider MOSFET, but increasing the width would be in total contrast to the feature size reduction.

Fig. 2: Sketch of simple circuit with the parasitic elements considered

Out of this simple interconnect model, the total RC-delay  $\tau$  of an interconnect wire can be derived, which conducts to the following formula:

$$\tau = \tau_{prop} + R_{dr}C_{junc} + \left(R_{wire} + R_{dr}\right)C_{gate} + R_{dr}C_{wire} + \frac{1}{2}R_{wire}C_{wire} \tag{1}$$

The resistance  $R_{wire}$  and the capacitance  $C_{wire}$  are dependent of the wire-length, whereas  $C_{junc}$ ,  $R_{dr}$ ,  $C_{gate}$  are dependent of the device design. This is particularly important for scaling, which is described by the scaling factor f(f < I). The scaling factor f describes the shrinking of every dimension on a chip from one technology generation to another. For example, the length of an intermediate wire is shortened by the scaling factor and at the same time the cross section of the wire shrinks with  $f^2$  because the height and the width of the wire are scaled by f, too. Consequently, the RC-delay of the short and intermediate interconnects remains more or less constant because the resistance  $R_{wire}$  is increased by the factor 1/f, but at the same time, the capacitance  $C_{wire}$  is decreased by the factor f.

In contrast to the feature scaling, the length of global wires will remain roughly constant because of the integration of increasing functionality, leading to a constant chip area [RHo01]. In this case, the capacitance remains constant, while the resistance increases

with the inverse square of the scaling factor f as described before. Therefore,  $R_{wire}C_{wire}$  will also increase with  $1/f^2$ , indicating that the global wires will suffer most from the feature size reduction. This effect can only be lowered by the introduction of repeater circuits. In Fig. 3, the terms contributing to the overall signal delays are individually depicted.

Fig. 3: Individual contributions to the delay time [Sch03]

As can be seen, the terms contribute very differently to the overall signal delay. For these calculations, minimum size transistors were assumed as driver and receiver. The propagation delay  $\tau_{prop}$ , which is linear to the wire length, is negligible because it only accounts for 0.25% at the maximum of the signal delay. The so-called "device delay"  $R_{dr}(C_{gate}+C_{junc})$  determines the delay for very short local connections and does not depend on the wire length. The dominant factor for short and intermediate wires is  $R_{dr}C_{wire}$ , which depends linearly on the wire length. The main contribution for long wires is  $R_{wire}C_{wire}$ , which depends only on wire parameters like cross section, length of wire and surrounding wires, dielectric. The contribution from  $(R_{dr}+R_{wire})C_{gate}$  for long interconnects is negligible [Sch03].

This leaves two main delay contributions to be examined:  $R_{dr}C_{wire}$  and  $R_{wire}C_{wire}$ . Assuming a minimum size transistor, the crossover between the two terms is usually in the range of hundreds of  $\mu$ m to a few mm, depending on the node size. However, for intermediate and long wires, usually larger transistors with smaller  $R_{dr}$  are used, therefore reducing the  $R_{dr}C_{wire}$  contribution and shifting the crossover to smaller wire lengths. Consequently, even for intermediate wires, the  $R_{wire}C_{wire}$  term cannot be neglected. The only way to improve the signal delay is to lower  $C_{wire}$  and  $R_{wire}$ . The resistivity term was already addressed by the introduction of copper replacing the higher resistivity aluminum. The capacitance can only be reduced by changing the dielectric material with a lower dielectric constant.

#### 2.3 Crosstalk in interconnects

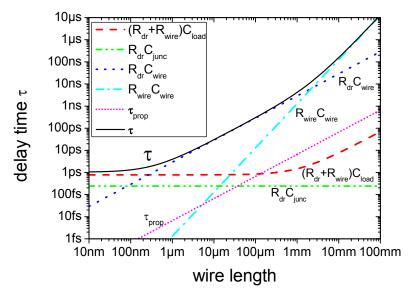

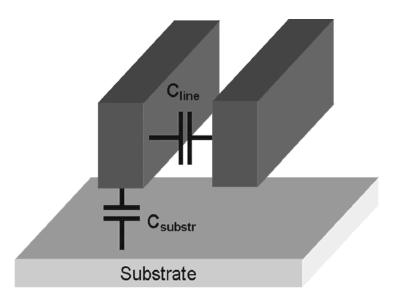

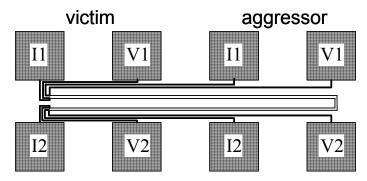

Crosstalk between two parallel RC lines is another important issue in the VLSI design. For instance, in combined circuits with bipolar and CMOS circuitry, the so-called BiCMOS, the CMOS large-swing logic signals and ECL small logic signals coexist on a chip. This combination may lead to malfunctions, if crosstalk induced by the high levels of the CMOS signal on the low level signals of ECL logic is so large that the noise on the ECL signal exceeds the logic threshold of ECL gates [Sak93]. As can be seen, these interactions may cause faulty functional and timing behaviors on the silicon chip [Sch03]. The timing behavior may vary extremely when two parallel lines are switched in push-pull mode. Push-pull mode means that the signal on the one metal line switches from high to low and vice versa on the other metal line. Especially bus systems can be affected dramatically, since there are long wires in parallel, and switching of the lines occurs with the system clock at the same time. In Fig. 4, a simple model of the parasitic capacitances of the interconnect system is shown.

Fig. 4: Capacitive model of two parallel interconnect lines

Generally, only two parasitic capacitances affect the crosstalk behavior of interconnects; on one hand, the coupling intermetal capacitance  $C_{line}$  from line to line and on the other hand, the interlayer capacitance  $C_{substr}$ . The interlayer capacitance does not only designate the capacitance to the substrate but also to other metal lines. Practically, this capacitance is maximized when accounting lines directly above the substrate because metal lines in different levels are usually perpendicular to each other and, therefore, the face-to-face area is rather small, respectively  $C_{substr}$ . These two capacitances affect the disturb voltage induced by crosstalk  $V_{x-talk}$ , see following equation [Sak93].

$$V_{X-talk} \approx \frac{1}{1 + \frac{C_{substr}}{C_{line}}} \tag{2}$$

The crosstalk signal  $V_{X-talk}$  does not depend on the dielectric constant of the surrounding material, but on the ratio of line-to-line capacitance  $C_{line}$  and line to substrate capacitance

$C_{substr}$ . As can be seen, it is appropriate to reduce only  $C_{line}$  to reduce crosstalk of adjacent lines. Especially in the future, crosstalk will become more important since the aspect ratio of the metal lines is increasing [ITR05], consequently  $C_{line}$  will increase.

## 2.4 Interconnect fabrication techniques

#### 2.4.1 Interconnects by reactive ion etching (RIE)

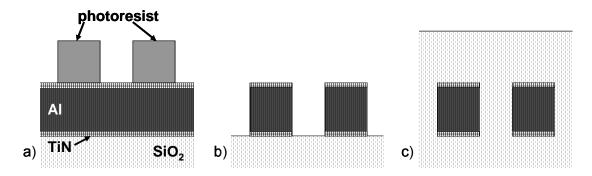

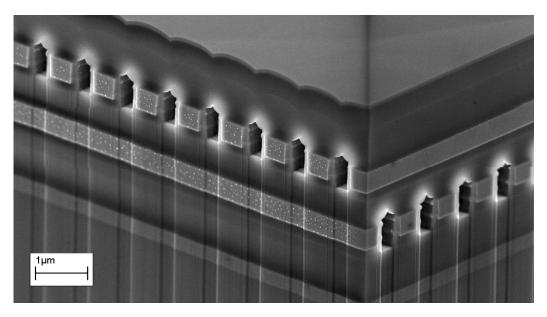

The reactive ion etching RIE technique is a subtractive technique and has been used for more than 20 years for aluminum patterning. First, a silicon oxide layer is deposited on the wafer as interlayer dielectric (ILD). Then, a sandwich of a thin TiN layer serving as a barrier and adhesion layer, a thick aluminum layer, and a thin TiN anti-reflection layer is deposited. On top, a resist or double layer of hardmask and resist is deposited and patterned by a subsequent lithography step. The anti-reflection layer is necessary to prevent the aluminum from reflecting the light during lithography exposure which would lead to overexposure of the resist. This lithography resist exhibits the positive image of the metal lines (Fig. 5a). After the lithography step, the metal sandwich is dry-etched with reactive ion plasma etch (RIE) (Fig. 5b). For passivation of the metal lines, SiO<sub>2</sub> is deposited to close the gaps between the metal lines and to cover the metal lines. Chemical mechanical polishing of SiO<sub>2</sub> (CMP) may be used to planarize the wafer surface (Fig. 5c). This technique is also used for some types of tungsten metallization processing.

Fig. 5: RIE metallization scheme

The major advantages of aluminum metallization are that it can be easily dry-etched, it has a low resistivity and it does not contaminate Si because no diffusion of Al occurs in  $SiO_2$  nor Si. Further on, it builds up ohmic contacts to Si and shows excellent adhesion to dielectrics [Sar03]. One severe disadvantage of aluminum is its low resistance against electromigration. For that reason, aluminum is doped with small incorporations of copper to strengthen the electromigration properties. Electromigration is the movement of atoms due to the impact of the electrons carrying the current through the wire. This effect can cause open circuits and is therefore a well-known reliability problem, see Chapter 2.9.1.

### 2.4.2 Interconnects by damascene technology

To reduce the line resistance and strengthen the electromigration resistance, copper was introduced as a new metallization material in 1997 [ITR05]. Unfortunately the subtractive

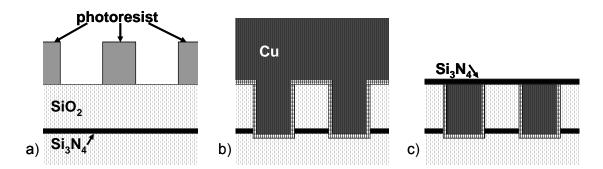

technique used in former aluminum technology is no more applicable due to difficult dryetching of copper. The standard technology for the processing of copper interconnects is the damascene (in-laid) technique (Fig. 6). In contrast to the direct patterning of the reactive ion etch processing, the basis of the damascene technique is the deposition of copper into trenches of a patterned silicon oxide layer. First, a silicon oxide layer is deposited on the wafer. Then, a photoresist is deposited over the silicon oxide layer and subsequently patterned by lithography. This lithography exhibits the negative image of the metal lines (Fig. 6a). The following etching process leaves a patterned silicon oxide layer with trenches for the metal lines. Subsequently, a thin barrier layer is deposited to prevent diffusion of copper into the surrounding dielectrics and into silicon. Due to the bad adhesion of copper to dielectrics, the barrier also serves as an adhesion layer. Materials used as copper diffusion barriers are tantalum, tantalum nitride or titanium nitride. Often, both tantalum nitride and tantalum are deposited successively to obtain the better conducting alpha phase of tantalum [Tra02] (Fig. 6b). Finally, copper is deposited by electroplating on the whole wafer and polished back to the top of the patterned oxide by chemical mechanical polishing (CMP). After this step, only the trenches are filled with copper. To passivate the copper upper surface, a capping layer of Si<sub>3</sub>N<sub>4</sub> or a-SiC is deposited (Fig. 6c). The damascene technique is also used for tungsten via processing. For the processing of tungsten wires both techniques - damascene or reactive ion etch - can be used.

Fig. 6: Damascene metallization scheme

The major advantages of copper metallization is the lower resistivity of copper compared to aluminum and the serious increase in electromigration strength. Copper lines can carry about 3 - 6 times higher current density than aluminum lines without failure under the same stress conditions and the same dimension.

## 2.5 Requirements for the intermetal dielectric (IMD)

Properties required for an acceptable intermetal dielectric material are a low dielectric constant (ideally k=1.0); mechanical, chemical and thermal stability; no moisture absorption or permeability to moisture; good thermal properties (high thermal conductivity and comparable coefficient of thermal expansion to the used metals and to silicon) and process compatibility. In Table 2, the requirements on the dielectric material are shown:

| Key Performance Areas | General Requirements      |  |  |  |

|-----------------------|---------------------------|--|--|--|

|                       | Low dielectric constant   |  |  |  |

|                       | High breakdown strength   |  |  |  |

| Electrical            | Low loss factor           |  |  |  |

|                       | High bulk resistance      |  |  |  |

|                       | Low DC leakage current    |  |  |  |

|                       | Good Adhesion             |  |  |  |

| Mechanical            | Low film stress           |  |  |  |

|                       | High hardness             |  |  |  |

| Chemical              | Good patternability       |  |  |  |

| Chemical              | Low moisture uptake       |  |  |  |

| Thermal               | Good thermal conductivity |  |  |  |

| rnermai               | High thermal stability    |  |  |  |

Table 2: Dielectric requirements [Vit04]

Besides the permittivity, further electric properties are of importance. The loss factor must be as low as  $10^{-3}$  or lower over a wide range of frequencies. The breakdown voltage is another issue together with low leakage currents. Values of 2 - 3 MV/cm are needed if the material is supposed to replace  $SiO_2$  or related compounds. Mechanical strength is important especially for bonding, packaging and for CMP. The thermal coefficient of expansion should not exceed  $10\text{ppm}/^{\circ}\text{C}$  otherwise cracks or delamination may occur. At last, environmental considerations must be taken into account. Generating large amounts of waste in processing must be avoided as well as use of poisonous precursors and byproducts. These requirements except the dielectric constant of 4.1 - 4.4 were achieved by CVD  $SiO_2$ , which was the material of choice up to now. The dielectric constant of  $CVD-SiO_2$  is about 10% higher than of thermally grown  $SiO_2$ , because of impurities and a less stoichiometric  $SiO_2$ . As mentioned in Chapter 2.1, the International Technology Roadmap for Semiconductors calls for dielectrics with  $k_{bulk} \le 2.4$  by 2008 and  $k_{bulk} \le 2.0$  by 2012. If a reliable ultra-low-k dielectric system could be realized using conventional technological processes, a quantum step towards these goals would be achieved.

#### 2.6 Low-k materials as IMD materials

The expression low-k dielectric in the semiconductor industry designates a material, which has a lower dielectric constant than  $SiO_2$ . These materials are meant as interlayer or intermetal dielectrics. They can be divided into two major groups, dense low-k materials and porous low-k materials. In general, there are three main physical ways to reduce the k-value of a material, first, reducing the polarity of the material, reducing the density or leaving out material. It has to be mentioned that the following k-values of the material are all bulk k-values which tend to be significantly lower than in an interconnect structure because etch stop layers, etch damage, moisture uptake or densification are neglected. Especially moisture uptake increases the k-value dramatically since water with its polar molecule has a k-value of 80. For example, for a typical comb structure, built in a

damascene scheme with a porous MSQ-based dielectric of relative permittivity  $k_{bulk} = 2.3$ ,  $k_{eff}$  is 3.1 ±0.1. This structure includes a CVD SiCN etch stop (100 nm), hard mask (20 nm after CMP) and capping layer (50 nm), all of which have k = 4.3 [Kas04].

#### 2.6.1 Dense low-k materials

Dense low-k dielectrics can roughly be divided in two groups: inorganic and organic materials. The purely inorganic materials are mostly successors of the incumbent silicon dioxide. This low-k materials are SiO<sub>2</sub> doped with fluorine (FSG) or with carbon (SiOC), the latter being an intermediate between organic and inorganic matter. The incorporation of such impurities leads to a less polar molecule and therefore reduces the k-value.

Silicon oxyfluoride (FSG) is a CVD-based deposited dielectric, which fulfills almost all of the requirements and is already used in production. But the problem is, that the dielectric constant can only be reduced to around 3.7. With higher fluorine content, the k-value could be further decreased, but the fluorine content must be limited to about 4% because otherwise fluorine evolution may cause degradation of the metal barrier or the metal lines. The stress and water absorption also increase with higher fluorine content.

Hydrogen silsesquisiloxane (HSQ) is another inorganic low-k material with a  $k \sim 3.0$ , which can be deposited by spin on [Dow05]. Furnace curing of the material at 400°C and higher results in an increase of the k-value accompanied by loss of hydrogen. The film stress is high and the resilience against  $O_2$ , which is usually used for resist strip is low [Cla01].

Amorphous fluorinated carbon (a-CF) films can be described as an inorganic material, because there is only carbon and fluorine present. The permittivity of 3.2 is rather high. Poor adhesion was observed on all substrates except for thermal oxide and silicon nitride and outgassing of fluorine occurs above 400°C with the *k*-value increasing.

Although organic dielectrics show an in situ low-k value, the thermal stability and sensivity towards oxygen at elevated temperatures or with plasma treatment are issues. Only some groups of polymers are candidates for integrated circuit processing: Fluorinated carbon (a-CF), polytetrafluorethylene (PTFE), fluorinated polyimide (FPI), polybenzoxazole (OxD), poly(arylene)-ether (PAE), parylenes, benzocyclobutene (BCB) and organo-silicon-based materials (alkyl-,aryl-siloxanes).

Si-based polymers (SiOC, MSQ) consist of a SiO<sub>2</sub>-typical network with methyl-groups (CH<sub>3</sub>-) attached to many of the silicon atoms. The SiOC can be deposited by spin on techniques or CVD [App05]. *K*-values reaching from 2.5 to 3.0 can be achieved. Because of the high content of organic material, SiOC-layers degrade very easily during resist stripping. Water uptake is also a problem, which degrades the *k*-value and leads to a high loss factor. Nevertheless, it was the first organo-spin-on-glass that reached integration at Sematech.

Fluorinated Polyimide (FPI) with (-CF<sub>3</sub>) groups show good electrical (k = 2.6 - 2.9) and mechanical properties. The materials are tough, have a lower moisture uptake than normal polyimide and show high glass transition temperatures. Planarization and the reaction of excess fluorine with barrier materials seem to be problematic. Water uptake can still reach about 1 wt%.

Poly(arylen)ether (PAE) is obtained by reaction of an bi-functional aromatic monomer with bisphenol giving a fully aromatic polyether chain. PAEs exhibit a  $k \sim 2.6$  - 2.8. They better withstand temperature cycling than polymers. Excellent adhesion was observed on SiO<sub>2</sub> or Al. PAE material can be polished without a capping layer. A two-level Cu damascene structure was demonstrated by Fujitsu [LaPO3].

Silicon containing benzocyclobutene (BCB) resins are spin on materials [Kaw03]. In contrast to the polymerization-reaction of polyimide, no water or other byproducts are formed and, hence, no corrosion or side reactions should occur. Because BCB contains silicon in the molecule plasma etching must be carried out with fluorine containing gas mixture. The fully cured BCB is a highly cross-linked material with excellent stability, resistant towards oxidation and very low water uptake. The loss factor over a wide range of frequency is low with a permittivity of 2.3 - 2.7 [Cla01]. The thermal stability of the BCB-film is limited to nearly 400°C. When the temperature reaches 375°C or higher, the adhesion on oxide or nitride layers deteriorates and blisters occur.

As can be seen, there is a wide spectra of dense low-k dielectric materials, every one with different integration issues or the necessity of additional process steps. With dense low-k dielectrics, the bulk k-value can be reduced down to 2.5. For further reduction, the density of the materials has to be decreased with the incorporation of pores filled with gas.

#### 2.6.2 Porous low-k materials

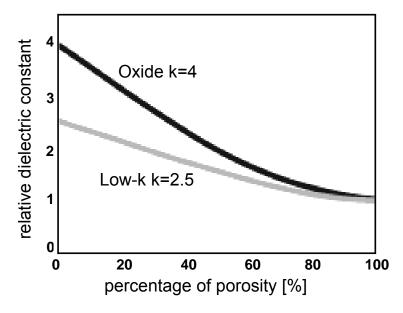

The most effective way of reducing permittivity is the conversion of low-k materials, inorganic or organic, into nano- or mesoporous films formed by the evaporation of solvent or other sacrificial material leaving a layer with a foam-like structure. These advanced, porous dielectrics are also called ultra-low-k (ULK) materials. Because most of space occupied by the film is empty, the k-value can be as low as 1.3. The pore size in those films should be smaller than the pattern formed on their surface with a narrow distribution of pore diameters. In Fig. 7, the correlation of the porosity for two different materials versus the overall k-value is shown [Gol01].

Fig. 7: Dielectric constant versus percentage of material porosity [Gol01]

As can be seen in the graph, the k-value can be reduced drastically by introducing pores into dielectrics. For example, when introducing 40% porosity in a material with a k-value of 4, the k-value would drop to as low as 2.3. When starting with a material with a k-value of 2.5, this value would drop to 1.8 with 40% porosity.

Nanoporous dielectrics are among the few materials options with ultra low-k < 2.0. Porous dielectrics called xerogels, nanogels, nanofoams or aerogels are commonly made by spin on deposition of dissolved organosilicates (e.g. TEOS) followed by partial hydrolysis (aging), a hydrophobic treatment and an outgassing and baking step leaving the silica species cross-linked with 30 - 80% porosity. Due to the low density of the material, the k-value can be as low as 1.3 - 2.5. The exact value is tunable by the process parameter changing the porosity of the product. This approach works for example with HSQ and two solvents with different boiling points [Iac02]. The pores are made by boiling out a solvent during a cure step, which lowers the dielectric constant of HSQ significantly to 2.0 - 2.5, depending on pore size. Afterwards, a hydrophobic treatment is necessary to prevent water absorption. Despite this treatment, i.e. conversion of hydrophilic surface silanole groups into hydrophobic trimethylsilyl groups (-Si(CH<sub>3</sub>)<sub>3</sub>), moisture uptake is still an issue.

Porous PAE materials have also been developed showing a k = 1.9 - 2.2 with good adhesion. A single layer Cu damascene integration was completed, but Young's modulus was reduced by 50% and there has been some decrease in thermal stability and plasma resistance due to the higher exposed surface area [Leu00].

Other nanoporous films can be formed via a two-phase controlled nanophase separation of a blend, hybrid or copolymer system. Porosity is controlled by selective removal of sacrificial components. IBM is characterizing porous organosilicates (nanofoams) with k-values of < 1.7 at < 40% porosity [Cla01]. These materials demonstrate high thermal stability and process simplicity. The nanoporous inorganic-organic hybrids are created through the vitrification of low molecular weight silsesquioxane (MSQ) in the presence of highly branched thermally labile aliphatic polyesters of controlled molecular weight and architecture. The thermally labile pore generator decomposes by heating to 350 - 400°C to leave behind pores in the inorganic oxide. The combined structure contains closed-cell pores in a hydrophobic matrix, minimizing moisture absorption.

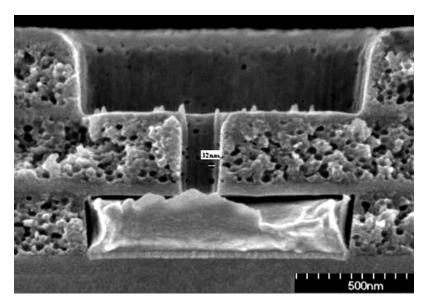

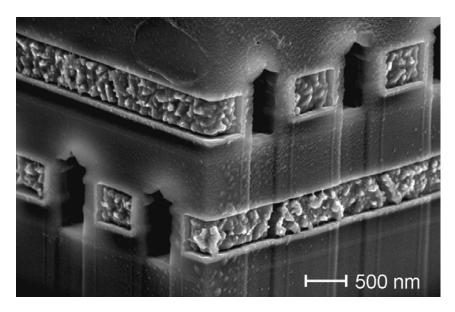

Process integration of porous materials is very challenging because these dielectrics are mechanically weak and have large internal surface areas which can absorb moisture. They are brittle, generate particles and are easily attacked by etching, ashing, cleaning and CMP processes. Etching holes is a problem and migration of metals into the pores may occur. In Fig. 8, a metal line, etched via and line trenches in a porous low-*k* dielectric are shown, elucidating some of the integration issues associated with porous low-*k* materials:

Fig. 8: SEM image of interconnects in a porous low-k dielectric [Pfe04]

A further issue associated with ULK materials is plasma damage, which leads to a less porous sidewall, see Fig. 8. The pore sealing itself is necessary because it prevents metal intrusions into the pores during metal deposition. Unfortunately, this effect leads directly to an increase of the material's k-value and therefore of  $k_{eff}$  of the insulation scheme. And even worse, the percentage of  $k_{eff}$  increase is higher with decreasing feature sizes as the thickness of the damaged surface layer does not decrease with scaling of the feature sizes. The pores also degrade dielectric breakdown voltage as well as increase the difficulty of depositing continuous films on these dielectric surfaces [Pfe04].

In the first integration experiments of low-k, films resist and via poisoning were a major problem. Via poisoning occurs when etched and stripped dielectric sidewalls absorb moisture prior to via filling, leading to metal corrosion respectively high via resistance. The moisture absorption takes place with the reaction of hydrogen bound to the low-k surface (during etching) and oxygen (during strip process). Resist poisoning can be avoided by plasma sources that convert nitrogen or ammonia gases to atomic nitrogen that quickly react with hydrogen and diffuse into the low-k films. Thereby, the hydrogen is bonded and cannot react with oxygen. Significant process work is required to eliminate such contamination [Cla01].

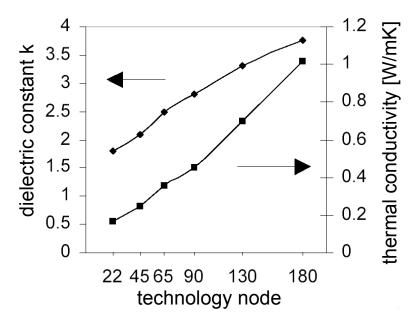

Further on, the Young's modulus due to the porous structure of these soft ULK materials is much lower than of dense materials. Thermal coefficient of expansion is very high and may cause cracks in the film. Thermal conductivity is very low and may cause power dissipation problems. Some of these problems can be solved by depositing an oxide or nitride cap layer over the porous material, but this of course increases the effective k-value. In Fig. 9, an estimation of the thermal conductivity and the dielectric constant versus the future technology nodes is depicted [Chi02]. As can be seen, the effective k-value is directly correlated to the thermal conductivity, thus leading to very low thermal conductivity values for future technologies.

Fig. 9: Dielectric constant versus thermal conductivity of dielectrics [Chi02]

Despite the introduction of copper-containing chips in 1998 with silicon dioxide insulators, problems arose when reducing the insulator dielectric constant predicted by the ITRS. Although fluorine-doped silicon dioxide ( $k_{bulk} = 3.7$ ) was introduced at 180nm, the use of insulating materials with  $k_{bulk} \le 2.7 - 3.0$  was not very common until 90nm. Contrary to the prediction, it soon was obvious that the reliability and yield issues associated with the integration of these materials with dual damascene copper processing would be a challenge, with the integration of porous low-k materials even being a higher challenge. The combination of introducing these new low dielectric constant materials and reducing the thickness and higher conformality requirements for barriers and nucleation layers turns out to be an integration difficulty [ITR05].

## 2.7 Air gaps as an alternative approach

Air gaps based on well-known conventional materials may be a viable alternative. The term air gap describes cavities between adjacent metal lines filled with air or gas. Since air/gas/vacuum has the lowest permittivity of  $k \sim 1$  among all materials it looks very beneficial for electrical insulation purposes in interconnect schemes. In addition, air gaps can offer a scalable solution for multiple technology nodes. Of course, the overall effective k-value is in practice larger than 1 since the metal lines have to be supported by some solid material. As mentioned before, similar restrictions also apply to more conventional low-k or ultra-low-k approaches. There are various ways of producing air gaps, each with different advantages and disadvantages as functions of process maturity and targeted dielectric constant.

## 2.7.1 Gas dome concept as ultimate low-k solution

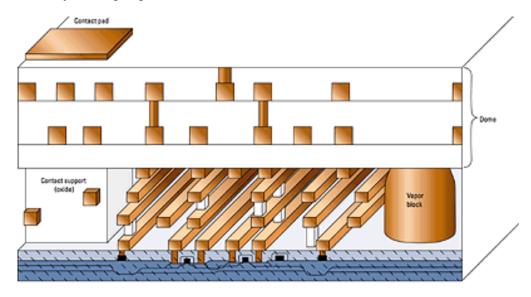

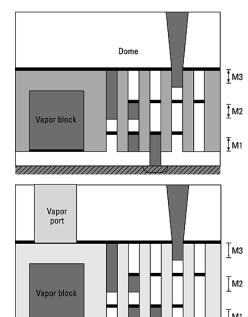

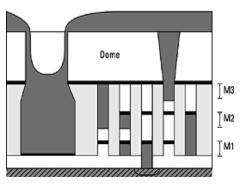

The gas dome concept is the most aggressive air gap approach. In the gas dome dielectric system (GDDS), SiO<sub>2</sub> forms a dome, in which a gas surrounds the metal conductors

underneath, see Fig. 10. The proposed concept can be summarized like this: Over dual damascene metal structures embedded in a polymer, a very thick and dense silicon dioxide layer is deposited forming the dome. Then vias through the thick SiO<sub>2</sub> capping layer of the dome are fabricated. Further on, vapor ports are etched through the capping of the dome. After pyrolization of the polymer through the vapor ports, the resulting gaps are filled with gas and finally the vapor ports are closed.

Fig. 10: The Gas Dome Dielectric System [Wad99]

As shown in Fig. 10, the dome may be a partial dome, covering only the lower level conductors or it can be a full dome where all metal levels are embedded in the gas dielectric. For purposes of process integration, reliability and thermal conductivity, the partial dome concept seems to be more practicable. If conductors are embedded in a gas, they must be supported to maintain structural integrity. The conductors can be held in place using inorganic insulating supports and braces (i.e., SiO<sub>2</sub>) as illustrated in Fig. 10. Properly designed, these conductors can be structurally sound without the need of continuous underlying support. To add strength to long conductor lines, a thin stiffening material layer can be deposited on either the bottom or top side of the conductor [Wad99].

In the following, a possible process flow for the GDDS is depicted. Starting with a processed silicon wafer, a thick premetal dielectric (typically HDP-CVD SiO<sub>2</sub>) is deposited and patterned to fabricate the metal support structures. Then, the SiO<sub>2</sub> is etched to a depth equal to the desired thickness of the first metal level and filled with a temperature degradable polymer. After curing the polymer and planarizing, a dual damascene etch is performed to define first metal level trenches and contact holes. Then, standard metallization takes place with metal deposition and CMP. The procedure for the following metal layers is alike. The next step is to deposit a thin etch-stop layer followed by a very thick and dense oxide layer, which will act as the dome for all underlying layers. In the following figure, the removal of the polymer and the closure of the vapor filled gas dome is described [Wad99]:

Damascene vias are etched through the dome, filled with metal and planarized to contact the metal lines. In the process of building up the various metal layers and vias, large metal vapor block structures are realized. These metal vapor blocks have multiple purposes, as will be shown. The next step is to etch large vapor ports in the dome layer directly above the metal vapor blocks all the way down to the low temperature degradable polymer material.

In the presence of a vacuum, this structure is then heated from the top side (RTP) to a temperature far exceeding the degradation temperature of the polymer. This causes the polymer to ash and vaporize through the vapor ports. Applying heat to the top side of the wafer causes the metal vapor block to heat up first, thus vaporizing the polymer around it. Since the dome layer heats faster than the silicon substrate, the top polymer layers will tend to vaporize before the lower layers, resulting in an orderly vaporization.

The final step is to fill the dome volume with the desired dielectric gas and close the vapor port. For better thermal conduction, light molecular gases like H<sub>2</sub> or He are most desirable. Backfilling could be conducted by depositing a thick metal layer under vacuum on top of the dome layer, the thickness has to be selected to almost completely fill the vapor port. The vacuum chamber is then filled with the dielectric gas and the metal around each vapor port is then spot welded, possibly with a laser, to cause the metal to flow into the port to close it.

Fig. 11: Process flow of polymer removal of the gas dome concept [Wad99]

This process guarantees the lowest achievable *k*-value, but for every metal layer, an additional lithography step plus one lithography step for the vapor port will be needed, which makes this process quite complex and expensive. Because of the complexity, no experimental results have been obtained up to now.

## 2.7.2 Air gap fabrication with the sacrificial layer approach

The principle of this air gap formation is the removal of a sacrificial layer after deposition of a capping layer. The metal lines are fabricated by the damascene technique in the sacrificial layer. Afterwards, a capping layer is deposited on top of the lines respectively the sacrificial layer. The final step is the removal of the sacrificial layer leaving air cavities

between the metal lines. In the following, three different techniques to produce such air gaps are shown.

#### 2.7.2.1 Carbon layer as sacrificial material

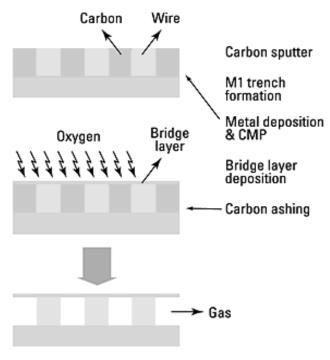

One solution of air gaps by the removal of a sacrificial layer is the so-called NURA process which was developed at Toshiba [Ana96], as shown in Fig. 12.

Fig. 12: Air gaps formed by sacrificial layer [Sin99]

The proposed process is a standard single damascene process with the only difference, that the trenches in which metals are filled are formed in a carbon layer instead of a dielectric film. The thickness of the carbon film is equal to the desired thickness of the interconnect lines as in the damascene process. Subsequently, metal is deposited to fill the trenches, followed by a CMP step to remove excessive metal. A thin SiO<sub>2</sub> dielectric capping layer (bridge layer), typically 50nm thick, is sputter deposited to cover the carbon film and the metal lines. A sputter process is chosen because this film is less dense than CVD SiO<sub>2</sub>, which is needed to decompose the carbon through the capping layer. The final step is a thermal treatment in an oxygen atmosphere at 450°C. This causes oxygen to diffuse through the thin insulator film reacting with carbon to form carbon dioxide, which is outgassing through the thin capping layer and fills the remaining air gap [Sin99]. When using the carbon layer technique in the via level, too, the NURA process can be extended to the dual damascene processing scheme.

The wire-to-wire isolation characteristic of the NURA process is comparable to dense dielectrics up to an electric field of 1MV/cm. With that approach the delay per stage could be reduced by 56% compared to dense SiO<sub>2</sub> [Ana96]. Further, the overall mechanical stability of the structure is rather weak, which is explained in more detail in the following chapter.

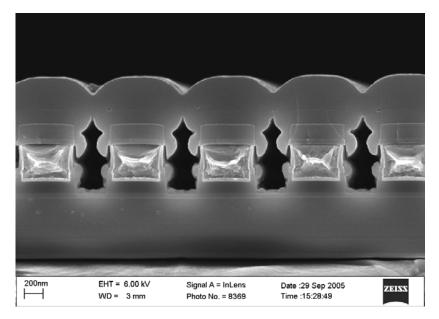

#### 2.7.2.2 Low-k material as sacrificial layer and porous capping layer

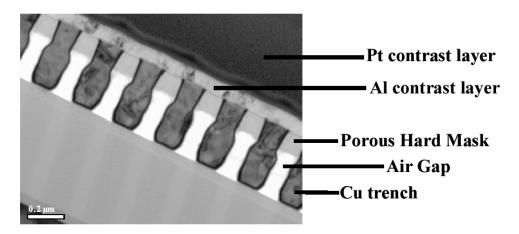

Philips Research Leuven improved the NURA process by replacing the carbon layer by a thermally degradable polymer (TDP) [Cha06]. What is even more important, they replaced the capping layer by a porous SiO<sub>2</sub>-like material (HM2800), which ensures an easier decomposition of the sacrificial layer [Daa05]. This capping layer also serves as a hard mask for the damascene trench etch. Therefore the capping layer is deposited before the damascene processing of the metal lines, see Fig. 13. The Al and Pt contrast layers are just for TEM preparation purposes.

Fig. 13: 120 nm comb structure by decomposing a thermal-degradable polymer, leaving air cavities [Daa05]

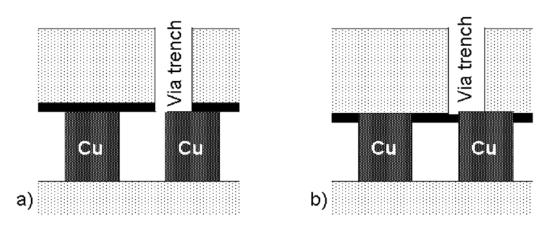

This sequence is beneficial for via integration because the porous hard mask prevents metal deposition into the air gaps when filling misaligned vias (Fig. 14b). With the pure NURA process the air gaps are opened up during via trench etch when the via lithography is severly misaligned. During the subsequent metal deposition for filling the unlanded via trenches, the air gaps would be partially filled with metal, leading to high leakage currents or shorts to neighboring lines (Fig 14a).

Fig. 14: Via integration with air gaps by removal of sacrificial material with the: a) NURA process b) Philips process

This air gap approach is problematic for wide dielectric spaces due to a collapse of the capping layer. However, this collapse is not an issue for the low-k properties because the

low effective k-value is only necessary in narrow spaced areas, but it is an issue for planarization (Fig. 15).

Fig. 15: Collapse of capping layer of wide dielectric spaces [Daa05]

To overcome this problem, either dummy metal structures in the design process can be introduced or a thick dielectric layer deposition and a subsequent polishing step have to be introduced for planarizing the wafer surface. Additionally, the whole structure is strengthened. According to simulations,  $k_{eff}$ -values below 2.0 could be achieved with this technique [Daa05].

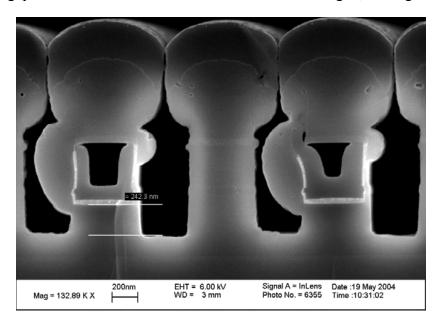

#### 2.7.2.3 Silicon oxide as sacrificial layer

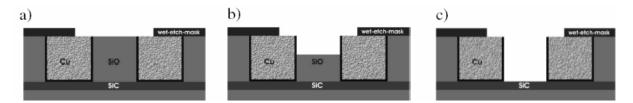

The technical university Chemnitz [Sch05] works on another sacrificial layer approach in a copper damascene processing scheme with PECVD SiO<sub>2</sub> as sacrificial material and the use of an additional lithography step. The sacrificial SiO<sub>2</sub> dielectric is capped and removed by wet buffered HF etching solution through holes in the capping layer defined by lithography. This capping layer is further on called "wet etch mask". In Fig. 16, the processing scheme of the key processes is depicted.

Fig. 16: Processing scheme of the air gaps by SiO<sub>2</sub> as sacrificial layer

As a starting point, copper damascene structures are embedded in PECVD SiO<sub>2</sub> with a standard etch stop layer at the bottom of the copper lines. Then, after CMP of the copper lines and the barrier, a capping layer, which also serves as "wet etch mask" is deposited to cover the top surface of the copper lines. Subsequently, the wet etch mask is patterned with an additional lithography mask such that orthogonal bands are etched to form small open spaces to the SiO<sub>2</sub> dielectric layer, see Fig. 16a. The distance of these bands defines the underetch of the buffered HF solution needed to remove the whole SiO<sub>2</sub> to form continuous air gaps. Then, the sacrificial SiO<sub>2</sub> dielectric between the copper lines is isotropically etched by buffered HF solution, see Fig. 16b. After proper etching time, the whole SiO<sub>2</sub> between the copper lines is removed, see Fig. 16c [Sch05].

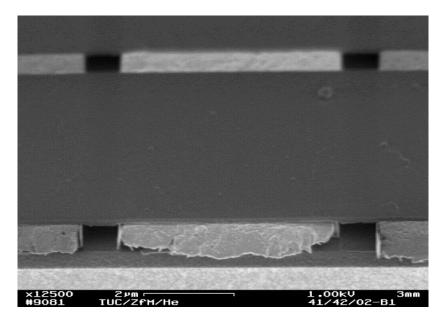

In Fig. 17, an angular SEM cross-section is depicted with the formed air gaps.

Fig. 17: Angular SEM image of air gaps by a sacrificial SiO<sub>2</sub> layer

The copper metal lines exhibit a line width of  $5\mu m$  with adjacent air gaps of  $1\mu m$  width. In the background of the image the etched orthogonal band in the wet etch mask can be seen. The light horizontal bar in the orthogonal band is the upper surface of the copper lines, divided by the air gaps (dark spots). After proper removal of the sacrificial  $SiO_2$ , the small remaining holes are closed by a non-conformal ILD CVD deposition [Sch06].

This approach can be modified with the integration of an additional capping layer of the air gaps and a spacer at the metal line sidewalls to scale down the holes for wet etch removal. Consequently, it is much easier to close the remaining holes the ILD dielectric. One big advantage for integration is that with the additional lithography the spots where air gaps are integrated can be controlled. Further on the alignment requirements for this lithography are low. The disadvantage of that approach is the need of an additional lithography and a long wet etch process, which implies the risk of underetching when etch stop layers are leaky.

## 2.7.3 Air gaps by non-conformal CVD deposition

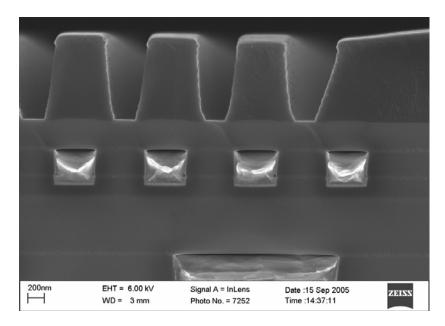

#### 2.7.3.1 Air gaps in a RIE metallization scheme

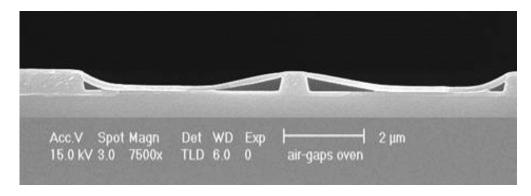

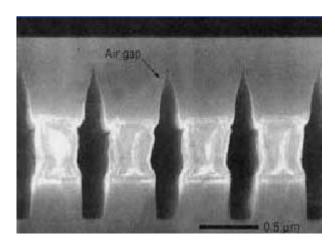

The easiest way of producing air gaps is by using a non-conformal CVD deposition in combination with an aluminum reactive ion etch RIE metallization scheme. Because of the patterning of the metal lines by etching, the spaces between the lines are already vacant, which is the perfect basis for air gaps. After the RIE process only a non-conformal CVD deposition has to be conducted to produce air gaps. In RIE metallization schemes, it is always difficult to fill the trenches between the metal lines completely. Therefore the CVD process is normally tuned to show good step coverage and conformality to suppress voids. For air gap fabrication, this CVD process is tuned to a very non-conformal deposition which generates huge voids, so-called air gaps, see Fig. 18.

Fig. 18: SEM cross-section after SiO<sub>2</sub>-air gap deposition [Shi98]

As can be seen, the CVD deposition is very non-conformal with almost no deposition at the sidewalls of the metal lines. The metal etch was also optimized to etch deep trenches beneath the metal lines to produce bigger air gaps. The non-conformal CVD deposition leads to very high pinnacles above the metal lines, which can be problematic during subsequent CMP processes. Critical requirements include air gap integrity because a misaligned via breaking through an air gap could lead to a decrease in insulation and contact yields. Another issue is that the height of the air gaps depends on the line space. Therefore, pertinent design rules have to be defined to control air cavity formation inside the interconnect structure [Arn01].

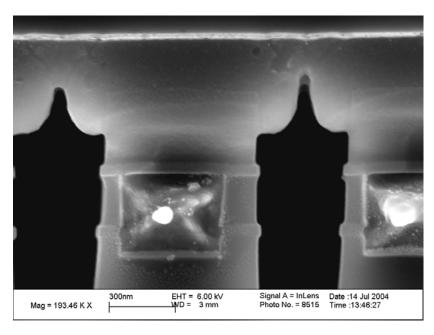

#### 2.7.3.2 Air gaps in a damascene metallization scheme

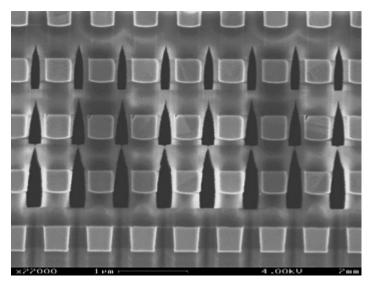

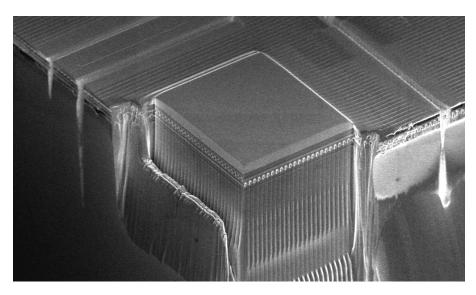

With all these mandatory requirements in mind, an architecture compatible with air gap integration with non-conformal CVD deposition was developed by ST Microelectronics [Arn01]. ST extended this air gap approach to a copper damascene processing scheme and demonstrated a 5-metal-layer structure including 3 levels with adjacent air gaps, see Fig. 19.

Fig. 19: SEM cross-section of 5 interconnect levels (metal space and width of  $0.32\mu m$ ) [Arn02]

The process steps to build these structures in a dual damascene architecture begin in a conventional way. After copper CMP at line level, an additional photo lithography and etch steps are performed to create trenches between lines for the air gaps. All trenches have the same width and are etched below the metal lines. This allows much better low-*k* performance and ensures a homogeneous formation of air gaps.

The first step is a deposition of a conformal liner. This liner serves as a spacer to center the air gaps in the middle of the trench. It is also used to form a landing zone for misaligned upper vias. The next step, the key process, is the non-conformal dielectric deposition. During this step, the air gaps are formed, the thickness of the layer is below that of the via level. The last step is a deposition of a gap fill dielectric. This step completes the stack deposition and ensures that all the air gaps formed at the lower metal level are closed well below the bottom of the interconnect lines etched in the upper dielectric level. This step was also found to planarize the surface without the need for an additional dielectric CMP process [Gos03].

The process with lithography allows to selectively integrate air gaps where a low-k value is necessary, for example around critical interconnect networks such as clock distributions or bus lines. Anywhere else, the dense dielectric material can be kept to reduce mechanical and thermal issues. With this approach, a reduction of the capacitance of 30 - 50% depending on material respectively geometry could be demonstrated [Arn02].

ST also demonstrated the integration of such air gaps with SiOC low-k material with a k-value of 2.9. A reduction of lateral capacitance of up to 58% compared to dense SiOC was observed. These values of coupling capacitances correspond to an effective permittivity of 1.7 [Gos03]. Also via and metal resistances, leakage currents and via chain yields were measured and compared with samples fabricated with standard SiO<sub>2</sub>. Via yields show that contact between via and metal is as good as in the reference samples and that the issue related to via penetration into the air gap can be overcome. In terms of reliability resilience, times to failure were comparable for air gap and conventional SiO<sub>2</sub> and no new failure modes were detected. No extrusion of metal was observed, indicating that no significant mechanical weakness is introduced by the air gap.

According to ST, the advantages of low-k dielectrics based on air gaps is that the interconnect network is built in a bulk dielectric material with processes already employed or easily derived from those currently used with silicon dioxide. Design constraints and integration challenges exist, but air gaps may be easier to integrate than completely new low-k materials. Manufacturable processes can reduce interconnect capacitance by as much as 40 - 50% for tightly spaced metal lines [Gos03a].

Our air gap approach lacks the integration issues of CMP with the high elongated tip of ST's air gap approach because a selective O<sub>3</sub>/TEOS process is used for closing the air gaps, leading to a flatter air gap tip. Details about the selective O<sub>3</sub>/TEOS deposition will be shown in Chapter 3. The proposed process steps will be stated in Chapter 4.

## 2.8 Capacitance and $k_{eff}$ of interconnects

#### 2.8.1 Plate capacitor and fringe fields

With the dielectric constant k and the dimensions of a plate capacitor, the capacitance C can easily be calculated according to the following formula. This formula only applies to

plate capacitors with thin plates, a narrow space d between the plates and large side lengths of the area A compared to the space d and plate thickness. In this case, the capacitance due to fringe fields can be neglected.

$$C = \frac{A}{d} \,\varepsilon_0 k \tag{3}$$

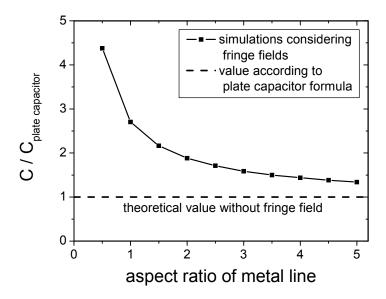

As in practice, interconnect lines have an aspect ratio of 1.0 - 2.0, the fringe fields considerably contribute to the overall capacitance. Therefore the plate capacitor formula becomes inaccurate. In Fig. 20, the value calculated with the plate capacitor formula is compared to the values obtained when considering the fringe fields in dependence of the aspect ratio of the interconnect line.

Fig. 20: Fringe field contribution to the overall capacitance [Sch03]

The calculation was carried out with parallel interconnect lines on Spicelink/Maxwell 2D, a simulation software of Ansoft. For low aspect ratios of the conductor line, the value according to equation (3) deviates massively, which is obvious since the metal lines have only a small face-to-face area but a large top area for fringe field formation. But even for very high aspect ratios of 4, the value according to equation (3) is still 44% smaller than the simulated value.

For that reason, the Maxwell equations have to be solved to exactly define the electromagnetic field between conductors. In our case, only the Poisson equation is used since we are only interested in electrostatic cases [Ans04].

$$\nabla \cdot \vec{E} = \frac{\rho}{\varepsilon_0 \cdot k} \qquad \rho \text{ charge density}$$

(4)

With the Poisson equation and the following expression, a direct correlation between the potential and the corresponding charge distribution can be affiliated.

$$\vec{E} = -grad\varphi \tag{5}$$

From the charge Q and the applied voltage V, the capacitance C can be calculated.

$$C = \frac{Q}{V} \tag{6}$$

Unfortunately, no closed form solution is known for the Maxwell equations. Consequently, it is not possible to calculate the capacitance of a complex structure by hand and, therefore, simulations were performed for approximation.

#### 2.8.2 Capacitance simulations with Maxwell Spicelink

The simulations were performed with Maxwell Spicelink of Ansoft Corp, which provides quasi-static electromagnetic-field simulation for parasitic extraction of electronic components. Maxwell Spicelink is a suite of tools including a 2D field solver, a 3D field solver, a graphical interface based schematic capture tool and Maxwell SPICE [Ans04]. The Maxwell Spicelink tool suite allows a complete range of interconnects to be analyzed. RLC parasitics for arbitrary 3D structures such as wire bonds, package leads, connectors, vias, meanders, interdigitated capacitors and cross-overs can be modeled and simulated. In our case, only the 2D Extractor was used since long, uniform interconnect lines with varying surroundings were simulated.

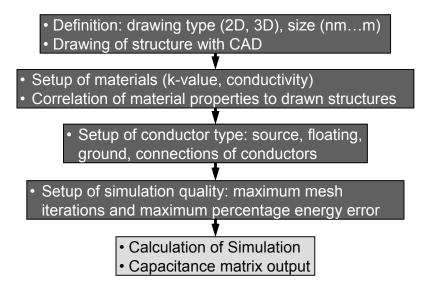

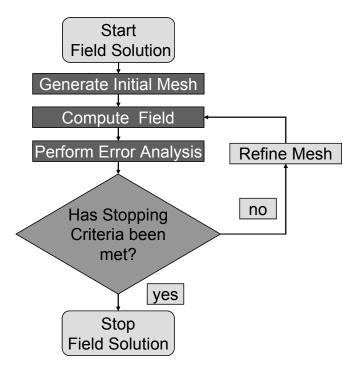

In Fig. 21, the typical workflow of a simulation with Maxwell Spicelink is depicted. At the very beginning, the demanded parameters like capacitance, inductance, and resistance have to be defined. In our case, only the capacitance was of interest. Then, the interconnect lines with their vicinity were drawn with a CAD tool. The second step is to setup and correlate the drawn structures to material properties like their specific *k*-value or conductivity. Afterwards, the conductor type like source, floating or ground, and the boundary conditions are defined. In our case, usually periodic boundary conditions were assumed, since we simulated comb structures with a large number of long fingers in parallel. The unit cell repeated periodically consists of a central conductor line and two outer lines, the latter to be considered only in half in order to take care of the periodic boundary conditions (see Fig. 22 right). The central and the outer lines are assumed to be sources with opposite potentials. The last step is the setup of the simulation quality and the stopping criteria with the maximum number of iterations and the maximum error.

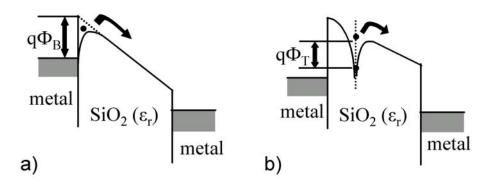

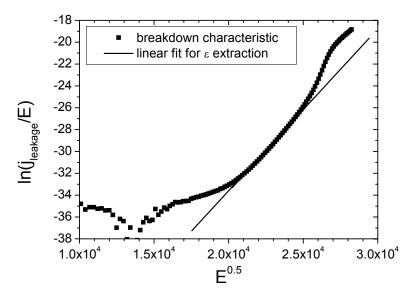

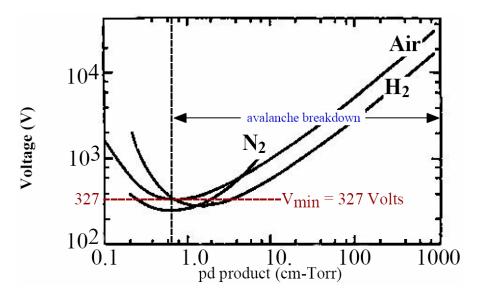

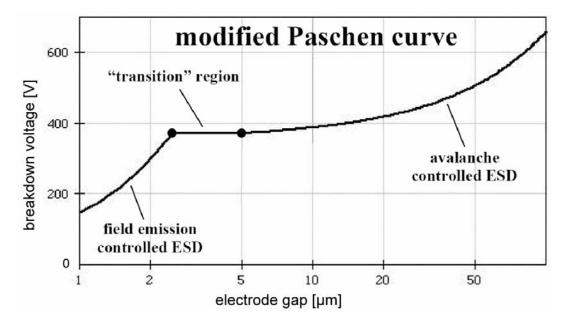

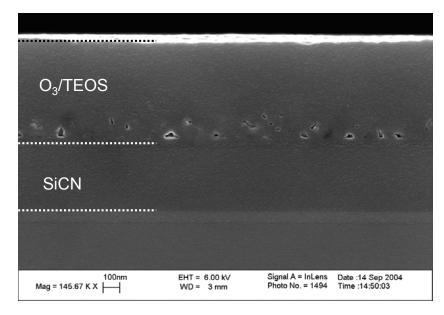

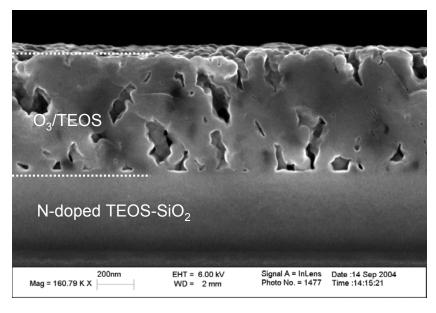

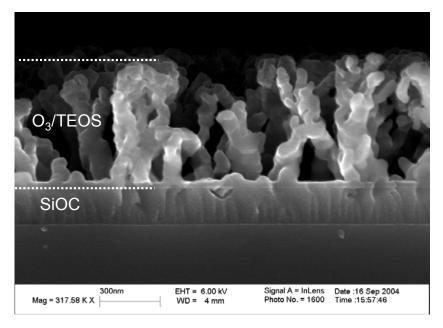

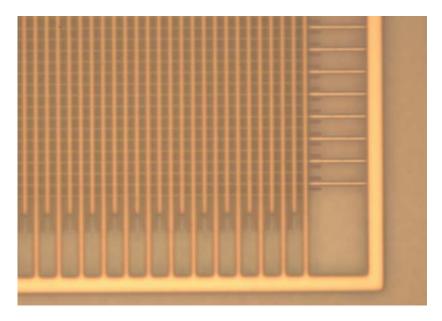

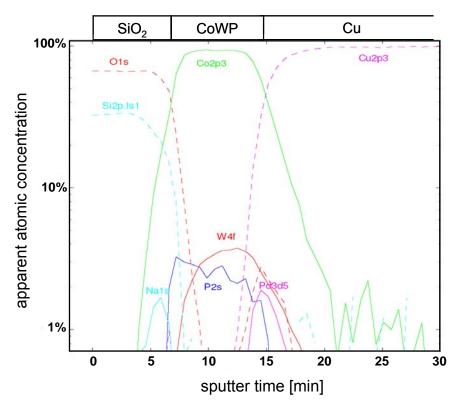

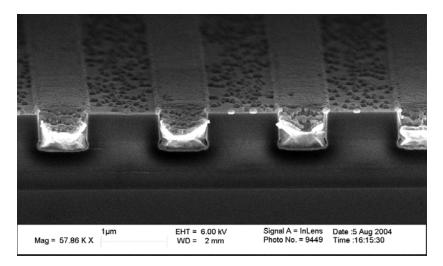

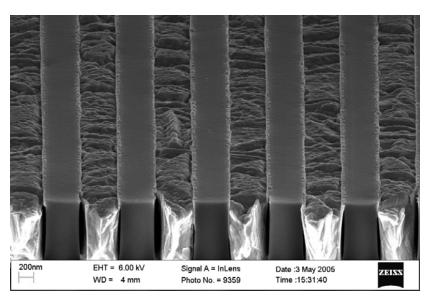

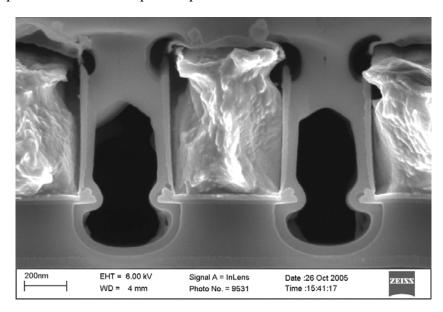

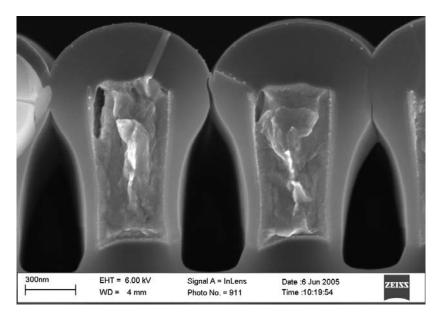

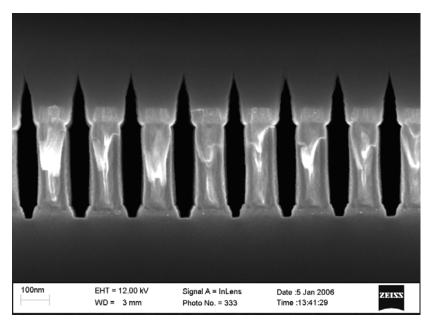

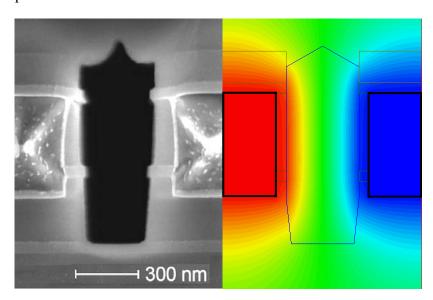

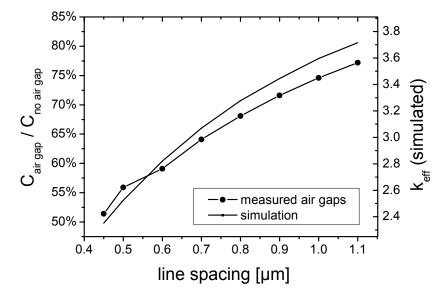

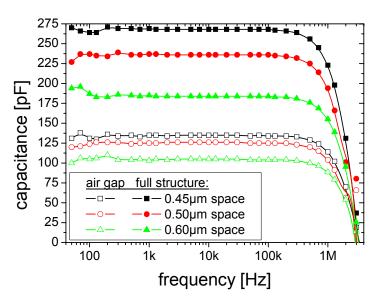

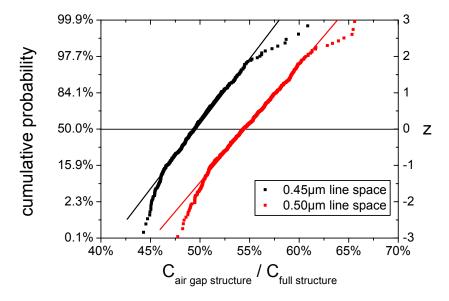

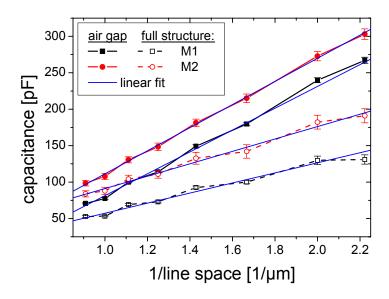

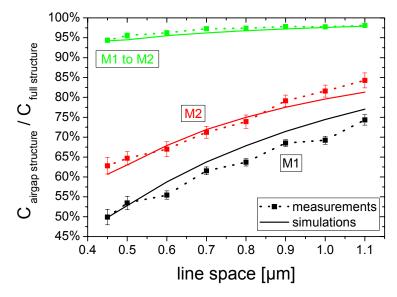

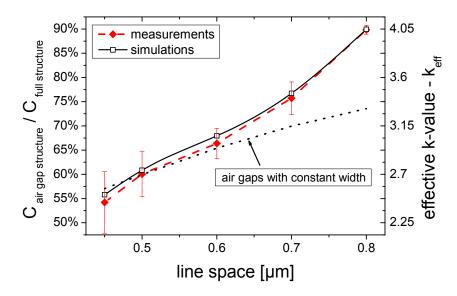

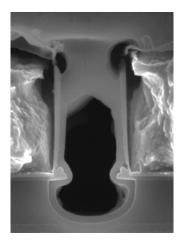

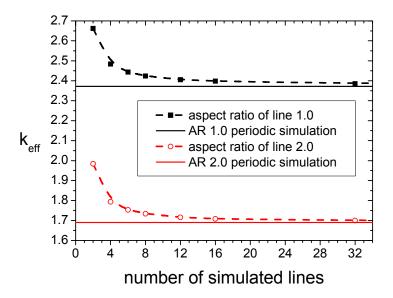

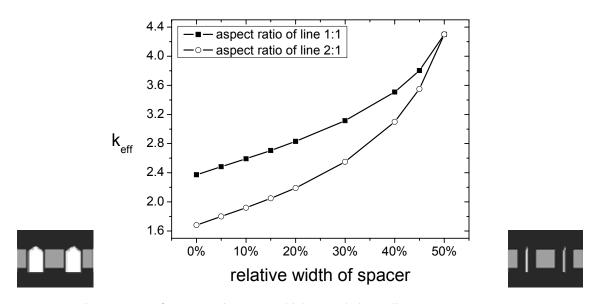

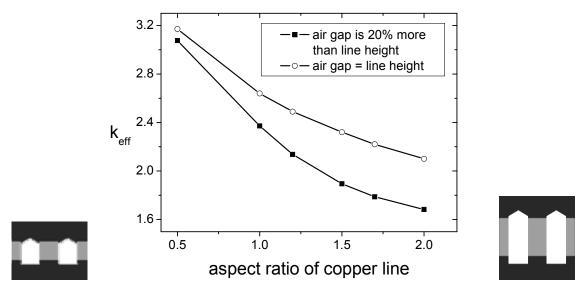

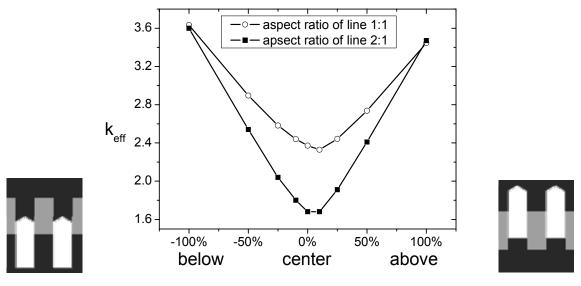

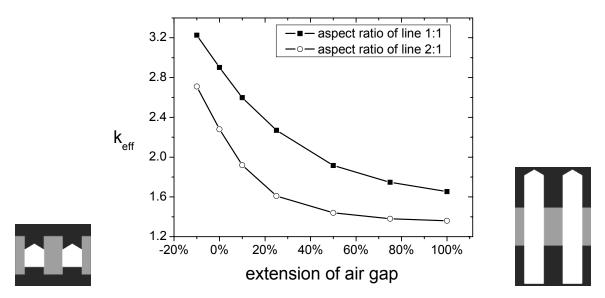

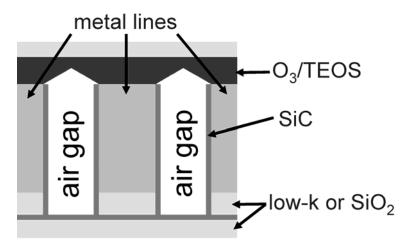

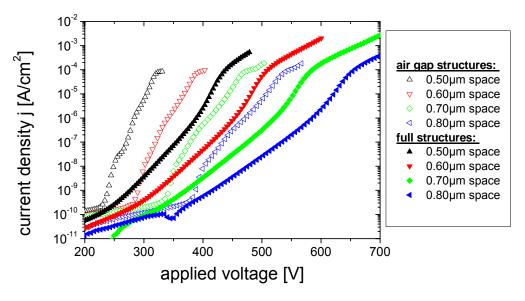

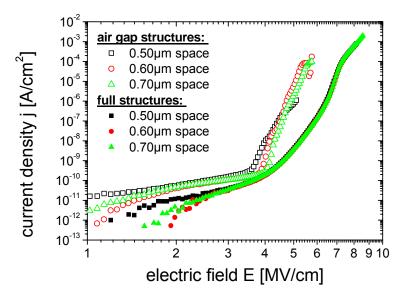

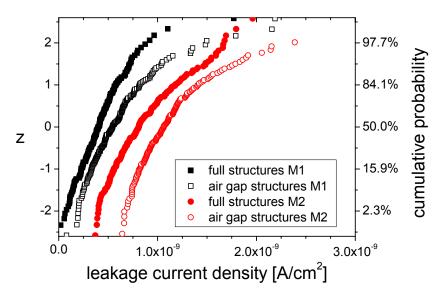

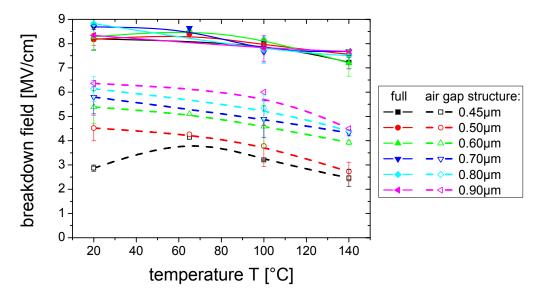

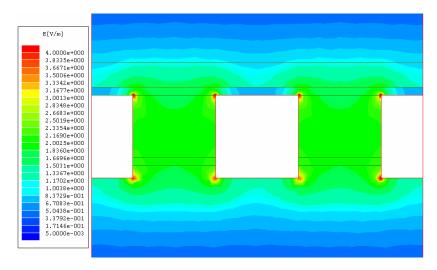

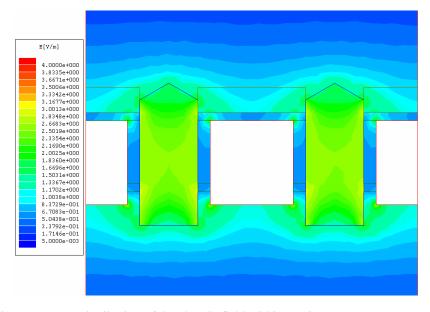

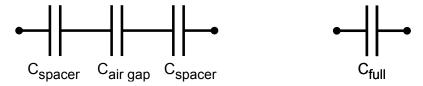

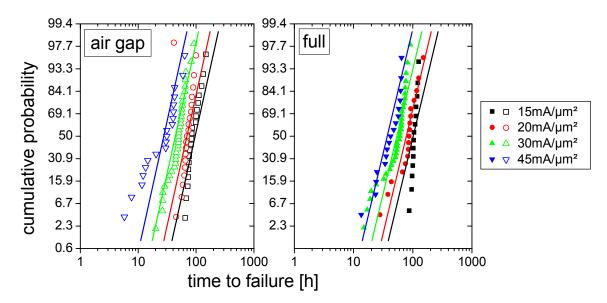

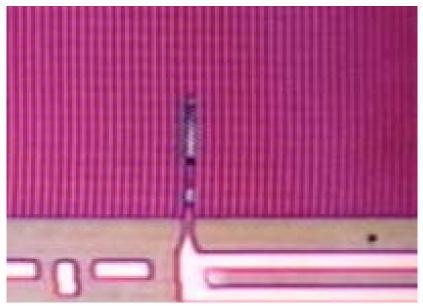

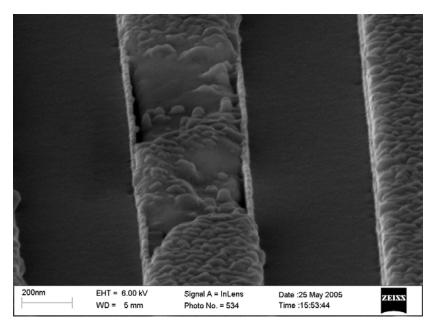

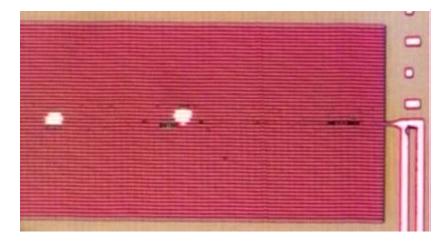

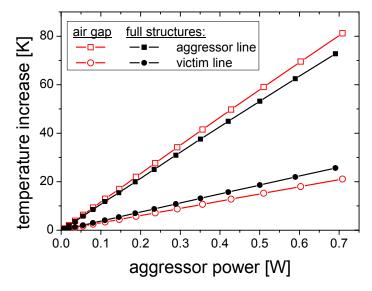

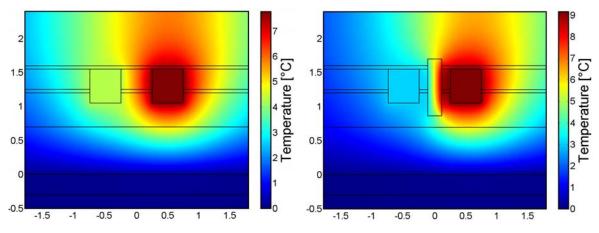

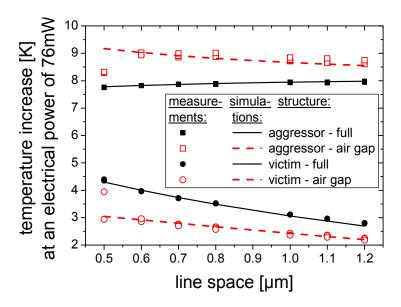

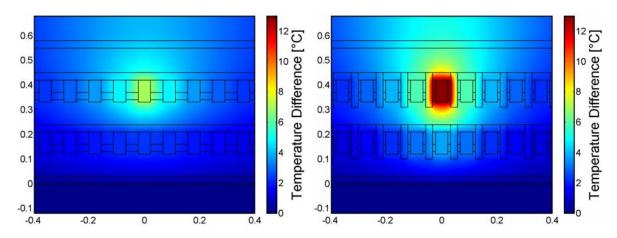

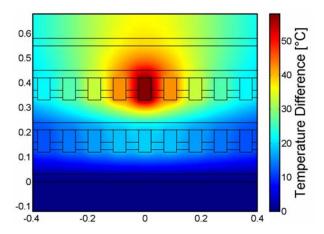

Fig. 21: Workflow of a simulation with Maxwell Spicelink