### TECHNISCHE UNIVERSITÄT MÜNCHEN

### Lehrstuhl für Integrierte Systeme

# Chip Hardware-in-the-Loop Simulation Framework

#### Christian Köhler

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften (Dr. rer. nat.) genehmigte Dissertation.

Vorsitzende: Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. sc. techn. Andreas Herkersdorf

- 2. Univ.-Prof. Dr. rer. nat. habil. Hans Michael Gerndt

- 3. Univ.-Prof. Dr.-Ing. Heinrich Theodor Vierhaus Brandenburgische Technische Universität Cottbus

Die Dissertation wurde am 30.11.2009 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 28.06.2010 angenommen.

## Eidesstattliche Erklärung

Die vorliegende Dissertation wurde von mir selbständig angefertigt. Die verwendeten Hilfsmittel und Quellen sind im Literaturverzeichnis vollständig aufgeführt. Eingetragene Warenzeichen und Copyrights werden anerkannt, auch wenn sie nicht explizit gekennzeichnet sind.

| Christian Köhler |

|------------------|

## **Danksagung**

Keine Schuld ist dringender, als die, Dank zu sagen. (Marcus Tullius Cicero, 106 v.Chr. - 43 v.Chr.)

Diesem Zitat von Cicero möchte ich an dieser Stelle entsprechen. In den letzten drei Jahren, welche ich bei der Infineon Technologies AG in München verbracht habe, erfuhr ich vielseitige Unterstützung, ohne die meine Dissertation nicht möglich gewesen wäre.

Als erstes zu nennen wäre Albrecht, mein Betreuer und Teamleiter, der mir das Angebot der Promotion bei Infineon unterbreitet hat. Danke Albrecht, für die Hilfe und die Anregungen, dein offenes Ohr für Probleme, und deine Geduld auch komplexe Lösungen auf dem Weg zur einfachen Lösung zu erdulden. Besonderer Dank gilt meinem Doktorvater Prof. Herkersdorf an der TU München. Danke für Ihre Betreuung und die Begutachtung, ebenso wie für den kritischen und scharfsinnigen Blick auf meine Ergebnisse.

Im ähnlichem Maße danke ich Herrn Prof. Vierhaus von der BTU Cottbus, welcher mich bereits seit dem Studium an der BTU begleitet hat, und welcher immer Zeit findet für die Schwierigkeiten seiner (aktuellen und ehemaligen) Studierenden.

Danke weiterhin an Herrn Prof Gerndt, welcher spontan und offen für die Rolle als Gutachter bereitgestanden hat.

Weitere Danksagungen gebühren meinen lieben (ehemaligen) Kollegen bei Infineon. Danke für die vielfältige Unterstützung die Untiefen der Infineon-Technologien zu umschiffen, und besonderen Dank für Eure Freundschaft. Danke an Thomas, Andreas, Harry, Gerlinde, Udo, Jens, Angeles, Hans, Richard und Michael, und alle anderen, die ich nicht direkt aufgeführt habe.

In den letzten Wochen der Arbeit kommt einer Gruppe von Personen ein ganz besondere Bedeutung zu: meinen Korrekturlesern. Diese hatten die herausfordernde Aufgabe, sich durch etwa 160 Inhaltsseiten zu arbeiten, um die Fehler, welche ich dort sorgsam platziert hatte, auszumerzen. Danke an Mario, Martin, Marcus und Stefan, welche mir seit der Studienzeit sehr gute Freunde sind. Besonderer Dank geht an Daniela und Nadja, welche ihre englischen Grammatikkenntnisse ganz hervorragend an meiner Arbeit demonstrieren konnten. Desweiteren aufzuführen wären Kirill und Paul, meine beiden "Proofreader"aus den USA. Danke für Eure Zeit!

Neben den fachlichen Unterstützern, Kollegen und Korrekturlesern gebührt noch den

Menschen Dank, die mir auf anderem Wege beigestanden haben. Zum einen meinen Eltern, welche mir mein Studium ermöglichten. Danke für Eure Unterstützung und Eure Hilfe!

Zum anderen meinem großen Bruder, der mich immer wieder für verschiedenste Dinge motivierte und auf den ich besonders stolz bin, dass er mich knapp mit dem Erwerb seines Doktortitels geschlagen hat. Vielen Dank Micha!

Weiterhin möchte ich meinen vielen, wenn auch in weit in der Welt verteilten, Freunden danken, von denen ich einige beim Namen nennen möchte, ohne jedoch die anderen weniger zu schätzen: Nancy, welche mir immer wieder vor Augen führt, wie viele Möglichkeiten jeder Einzelne doch hat sich zu entwickeln und neu zu erfinden, Lars, dessen subtiler Humor auch einen schlechten Tag in einen guten verwandeln kann, und "last but not least", Antje welche mir in den letzten Jahren so vieles gegeben hat und mich in meiner eigenen Entwicklung weiter vorangebracht hat.

### **Abstract**

#### Chip Hardware-in-the-Loop Simulation Framework

Using the real Microcontroller ( $\mu$ C) as a replacement for an  $\mu$ C model inside a system simulation of an  $\mu$ C based system is a big benefit because the  $\mu$ C is already verified and its maximum performance and its accuracy is much higher than any simulation model.

The Chip-Hardware-in-the-Loop Simulation (CHILS) approach covers the connection between  $\mu$ C and simulation, the interface abstraction, and the analysis and the optimization of such coupling systems. The coupling system is developed with focus on less hardware effort, capabilities to couple with different simulation environments and efficiency of coupling. The interface abstraction primarily supports the efficiency of coupling. The system analysis and optimization concept includes formal criterions to determine the fidelity of coupling systems, stability analysis of coupling systems and the numerical analysis of applied software algorithms.

## Kurzfassung

#### Chip Hardware-in-the-Loop Simulation Framework

Einen echten Microcontroller ( $\mu C$ ) als Ersatz eines  $\mu C$ -Modelles innerhalb der Simulation eines  $\mu C$  basierten Systems zu verwenden, ist durch die höhere Simulationsgeschwindigkeit, der höheren Genauigkeit und der bereits erfolgten Verifikation eine attraktive Lösung.

Der neue Ansatz der Chip-Hardware-in-the-Loop Simulation (CHILS) umfasst die Umsetzung der Kopplung von  $\mu$ C und Simulation, die Abstraktion der  $\mu$ C-Schnittstellen und die Analyse und Optimierung des Kopplungssystems. Die Kopplung wurde in Hinblick auf geringen Hardwareaufwand, Adaptivität zu verschiedenen Simulationsumgebungen und Effizienz entworfen, welche durch die Abstraktion der  $\mu$ C-Schnittstellen unterstützt wird. Das Systemanalyse- und Systemoptimierungskonzept umfasst formale Kriterien zur Qualität von allgemeinen Hardware-in-the-Loop(HIL)-Systemen, Stabilitätskriterien derartiger Systeme und die numerische Analyse der eingesetzten Software-Algorithmen.

CONTENTS xi

## **Contents**

| D  | anksa                            | igung                                               |                                         | 7                    |  |  |  |  |  |

|----|----------------------------------|-----------------------------------------------------|-----------------------------------------|----------------------|--|--|--|--|--|

| A  | bstrac                           | ct                                                  |                                         | vi                   |  |  |  |  |  |

| K  | urzfa                            | ssung                                               |                                         | i                    |  |  |  |  |  |

| C  | onten                            | ts                                                  |                                         | X                    |  |  |  |  |  |

| Li | st of                            | Figures                                             |                                         | xvi                  |  |  |  |  |  |

| Li | ist of                           | Tables                                              |                                         | xix                  |  |  |  |  |  |

| 1  | Intr<br>1.1<br>1.2<br>1.3        | Object                                              | ation                                   | . 2                  |  |  |  |  |  |

| 2  | Related Work and Work Hypothesis |                                                     |                                         |                      |  |  |  |  |  |

|    | 2.1                              | Basics 2.1.1 2.1.2 2.1.3                            | Motivation for Modelling and Simulation | . 10                 |  |  |  |  |  |

|    | 2.2                              | 2.2.1<br>2.2.2<br>2.2.3                             | Motivation for Hardware-in-the-Loop     | . 14<br>. 14<br>. 15 |  |  |  |  |  |

|    | 2.3                              | 2.2.4<br>Additi<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | Coupling Concepts                       | . 20<br>. 20<br>. 21 |  |  |  |  |  |

|    | 2.4<br>2.5                       | Comp                                                | arison of the Concepts                  | . 23                 |  |  |  |  |  |

xii CONTENTS

|   |                                                    | 2.5.1   | Connection between Hardware and Simulation           | 23 |  |  |  |  |

|---|----------------------------------------------------|---------|------------------------------------------------------|----|--|--|--|--|

|   |                                                    | 2.5.2   | Interface Abstraction                                | 24 |  |  |  |  |

|   |                                                    | 2.5.3   | Event Exchange Optimization                          | 24 |  |  |  |  |

| 3 | Con                                                | nection | n between Hardware and Simulation                    | 25 |  |  |  |  |

|   | 3.1                                                | Basics  |                                                      | 25 |  |  |  |  |

|   |                                                    | 3.1.1   | Simulator Coupling and Co-Simulation                 | 25 |  |  |  |  |

|   |                                                    | 3.1.2   | Synchronization of Co-Simulations                    | 27 |  |  |  |  |

|   | 3.2                                                | Relate  | ed Work                                              | 28 |  |  |  |  |

|   | 3.3                                                | Excha   | nge of Events between Microcontroller and Simulation | 30 |  |  |  |  |

|   |                                                    | 3.3.1   | Continuous Simulation                                | 31 |  |  |  |  |

|   |                                                    | 3.3.2   | Event Discrete Simulation                            | 34 |  |  |  |  |

|   |                                                    | 3.3.3   | Conclusions                                          | 36 |  |  |  |  |

|   | 3.4                                                | CHIL    | S Event Exchange Mechanism                           | 37 |  |  |  |  |

|   | 3.5                                                | Effects | s Caused by Coupling                                 | 39 |  |  |  |  |

|   |                                                    | 3.5.1   | Measurement of the Timing Difference                 | 40 |  |  |  |  |

|   |                                                    | 3.5.2   | Causes for the Timing Difference                     | 42 |  |  |  |  |

|   |                                                    | 3.5.3   | Possibilities for Compensation                       | 46 |  |  |  |  |

|   | 3.6                                                | Summ    | nary                                                 | 46 |  |  |  |  |

| 4 | Interfaces between Microcontroller and Environment |         |                                                      |    |  |  |  |  |

|   | 4.1                                                | Relate  | ed Work                                              | 49 |  |  |  |  |

|   | 4.2                                                | Interfa | ace Modelling and Abstraction                        | 52 |  |  |  |  |

|   |                                                    | 4.2.1   |                                                      | 52 |  |  |  |  |

|   |                                                    | 4.2.2   | Interface Representation                             | 53 |  |  |  |  |

|   | 4.3                                                | Summ    | nary                                                 | 56 |  |  |  |  |

| 5 | Opt                                                | imizati | on - Coupling System Analysis                        | 59 |  |  |  |  |

|   | $5.\bar{1}$                                        |         | ed Work                                              | 60 |  |  |  |  |

|   | 5.2                                                | Basics  | 6                                                    | 61 |  |  |  |  |

|   | 5.3                                                | Forma   | al Definitions                                       | 62 |  |  |  |  |

|   |                                                    | 5.3.1   | Transparency and Fidelity definition                 | 62 |  |  |  |  |

|   |                                                    | 5.3.2   | Application of the Coupling System Fidelity          | 67 |  |  |  |  |

|   | 5.4                                                | Exam    |                                                      | 67 |  |  |  |  |

|   | 5.5                                                | Comp    | arison of Different Coupling Systems                 | 70 |  |  |  |  |

|   |                                                    | 5.5.1   | Simulation Scenario                                  | 71 |  |  |  |  |

|   |                                                    | 5.5.2   | Interpretation of data sheets                        | 71 |  |  |  |  |

|   |                                                    | 5.5.3   | Scenarios                                            | 73 |  |  |  |  |

|   |                                                    | 5.5.4   | CHILS vs. DeskPOD <sup>TM</sup>                      | 73 |  |  |  |  |

|   |                                                    | 5.5.5   | CHILS vs. dSPACE                                     | 74 |  |  |  |  |

|   |                                                    | 5.5.6   | Comparison Results                                   | 75 |  |  |  |  |

|   | 5.6                                                | Summ    | nary                                                 | 76 |  |  |  |  |

CONTENTS xiii

| 6 | Opt         | imizati | ion - Analysis of the Real System and Environment             | 79  |

|---|-------------|---------|---------------------------------------------------------------|-----|

|   | $6.\bar{1}$ |         | rsis of Algorithms                                            | 79  |

|   |             | 6.1.1   | Related Works                                                 | 80  |

|   |             | 6.1.2   | Numerical Basics                                              | 81  |

|   |             | 6.1.3   | Arithmetic Basic Operations                                   | 82  |

|   |             | 6.1.4   | Algorithm Analysis Process                                    | 84  |

|   | 6.2         | Classi  | fication of Algorithms                                        | 89  |

|   |             | 6.2.1   | Related Work                                                  | 90  |

|   |             | 6.2.2   | Classification Process                                        | 90  |

|   | 6.3         | Analy   | rsis and Classification of Systems                            | 95  |

|   |             | 6.3.1   | Stability of Linear Time Invariant Systems                    | 96  |

|   |             | 6.3.2   | Stability of Nonlinear Time Invariant Systems                 | 97  |

|   | 6.4         | Gener   | al Analysis                                                   | 99  |

|   |             | 6.4.1   | Stability of Control Loops                                    | 99  |

|   |             | 6.4.2   | Example                                                       |     |

|   |             | 6.4.3   | Control Path Analysis                                         | 100 |

|   |             | 6.4.4   | Control Analysis - Analytical                                 | 100 |

|   |             | 6.4.5   | Control Loop Analysis                                         |     |

|   |             | 6.4.6   | Control Analysis - Numerical                                  |     |

|   | 6.5         | Summ    | nary                                                          |     |

| 7 | Ont         | imizati | ion - Runtime Analysis                                        | 107 |

| / | 7.1         |         | c Basics                                                      | 107 |

|   | 7.1         | 7.1.1   | Events                                                        |     |

|   |             | 7.1.1   | Simulation Coupling                                           |     |

|   | 7.2         |         | c Definitions                                                 |     |

|   | 7.2         | 7.2.1   |                                                               |     |

|   |             | 7.2.1   | J                                                             |     |

|   |             | 7.2.2   | Event Occurrence Accuracy                                     |     |

|   | 7.3         |         | ple                                                           |     |

|   | 7.3         | -       | nary                                                          |     |

|   | 7.1         | Juliui  | italy                                                         | 111 |

| 8 |             |         | mework - Concept                                              | 115 |

|   | 8.1         |         | ionality - CHILS Basics                                       | 115 |

|   |             | 8.1.1   | Data Exchange and Synchronization                             | 115 |

|   |             | 8.1.2   | Interface Abstraction                                         |     |

|   | 8.2         |         | controller Requirements                                       |     |

|   |             | 8.2.1   | Microcontroller Adaptations for Future Version                |     |

|   | 8.3         |         | e of Applications                                             | 119 |

|   |             | 8.3.1   | CHILS and the V-Model                                         | 119 |

|   |             | 8.3.2   | Rapid Control Prototyping                                     |     |

|   |             | 8.3.3   | Test Applications                                             |     |

|   |             | 8.3.4   | Estimation of the Real-Time Capability of Software with CHILS | 121 |

xiv CONTENTS

|    | 8.4  | Featur  | es                                            |  |   |  |   |  |   |     | 121 |

|----|------|---------|-----------------------------------------------|--|---|--|---|--|---|-----|-----|

|    |      | 8.4.1   | Simulation Coupling - CHILS-API               |  |   |  |   |  |   |     | 121 |

|    |      | 8.4.2   | Device Coupling - DAS Architecture            |  |   |  |   |  |   |     |     |

|    |      | 8.4.3   | Debugger Support - MCD-API                    |  |   |  |   |  |   |     | 123 |

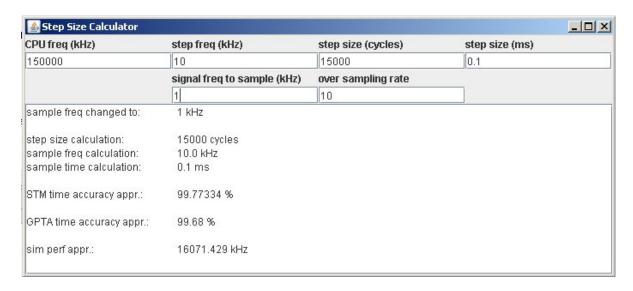

|    |      | 8.4.4   | Tools for Coupling Optimization               |  |   |  |   |  |   |     | 123 |

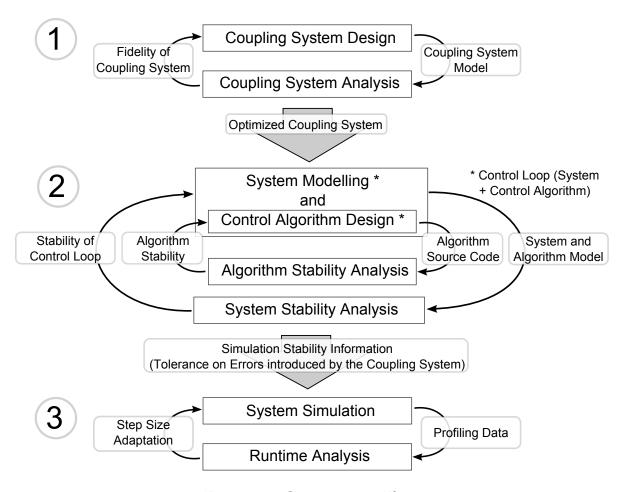

|    | 8.5  | Optim   | ization Flow                                  |  |   |  |   |  |   |     | 126 |

|    | 8.6  | Summ    | ary                                           |  | • |  |   |  |   | •   | 126 |

| 9  | CHI  | LS Fran | nework - Classification                       |  |   |  |   |  |   |     | 129 |

|    | 9.1  | Softwa  | are Models on Different Levels of Abstraction |  |   |  |   |  |   |     | 129 |

|    |      | 9.1.1   | Functional Simulation                         |  |   |  |   |  |   |     | 131 |

|    |      | 9.1.2   | Instruction Accurate Simulation               |  |   |  | • |  |   |     | 131 |

|    |      | 9.1.3   | Transactional Level with/without Time         |  |   |  |   |  |   |     | 131 |

|    |      | 9.1.4   | Cycle Accurate Models                         |  |   |  |   |  |   |     | 132 |

|    |      | 9.1.5   | Register Transfer Level                       |  |   |  |   |  |   |     | 132 |

|    |      | 9.1.6   | Physical Level                                |  |   |  |   |  |   |     | 132 |

|    | 9.2  | Embed   | dding of Hardware in Simulations              |  |   |  |   |  |   |     | 132 |

|    |      | 9.2.1   | Original Microcontroller                      |  |   |  |   |  |   |     | 132 |

|    |      | 9.2.2   | Emulation                                     |  |   |  |   |  |   |     | 136 |

|    | 9.3  |         | arison                                        |  |   |  |   |  |   |     | 136 |

|    | 9.4  | CHILS   | S Performance and Accuracy                    |  |   |  |   |  |   |     | 142 |

|    |      | 9.4.1   | CHILS Accuracy                                |  |   |  |   |  |   |     | 142 |

|    |      | 9.4.2   | CHILS Performance                             |  |   |  |   |  |   |     | 143 |

|    | 9.5  | Summ    | ary                                           |  | • |  | • |  | • | •   | 144 |

| 10 |      | 11      |                                               |  |   |  |   |  |   | 147 |     |

|    | 10.1 |         | nC-Coupling                                   |  |   |  |   |  |   |     | 147 |

|    |      |         | Virtual Peripheral Extension                  |  |   |  |   |  |   |     | 149 |

|    | 10.2 | Matlab  | p/Simulink-Coupling                           |  |   |  |   |  |   |     |     |

|    |      | 10.2.1  | CHILS-Demonstration Platform                  |  | • |  | • |  | • | •   | 154 |

| 11 | Sum  | ımary a | nd Outlook                                    |  |   |  |   |  |   |     | 157 |

|    | 11.1 |         | ary                                           |  |   |  |   |  |   |     | 157 |

|    |      |         | Connection between Hardware and Simulation    |  |   |  |   |  |   |     | 157 |

|    |      | 11.1.2  | Interface Abstraction                         |  |   |  |   |  |   |     | 158 |

|    |      |         | Event Exchange Optimization                   |  |   |  |   |  |   |     | 158 |

|    |      |         | CHILS Framework                               |  |   |  |   |  |   |     | 159 |

|    |      |         | Conclusion                                    |  |   |  |   |  |   |     | 160 |

|    | 11.2 |         | ok and Future Work                            |  |   |  |   |  |   |     | 160 |

|    |      | 11.2.1  | Driver Support                                |  |   |  |   |  |   |     | 160 |

|    |      |         | Hardware Support                              |  |   |  |   |  |   |     | 160 |

|    |      |         | Microcontroller Extensions                    |  |   |  |   |  |   |     | 160 |

|    |      | 11.2.4  | Integration into Commercial Solutions         |  |   |  |   |  |   |     | 161 |

| CONTENTS | xv |

|----------|----|

|          |    |

|              |       |        | Coupling System Analysis                  |     |  |

|--------------|-------|--------|-------------------------------------------|-----|--|

| A            | Forn  | nulars |                                           | 163 |  |

|              | A.1   | -      | er 5                                      |     |  |

|              |       | A.1.1  | Fidelity Functions of System Comparison   | 163 |  |

| В            | Tabl  | es     |                                           | 165 |  |

|              | B.1   | Chapte | er 3                                      | 165 |  |

|              |       | B.1.1  | Time Difference Measurement               | 165 |  |

|              |       | B.1.2  | Time Difference Measurement - dsync/isync | 165 |  |

|              | B.2   | Chapte | er 5                                      | 166 |  |

|              |       | B.2.1  | Result Tables of System Comparison        | 166 |  |

|              | B.3   |        | er 9                                      | 168 |  |

|              |       | B.3.1  | Synthetic Simulation Performance          | 168 |  |

| C            | Listi | ngs    |                                           | 171 |  |

|              |       |        | er 8                                      | 171 |  |

|              |       | _      | CHILS-API                                 | 171 |  |

|              | C.2   | Chapte | er 10                                     | 174 |  |

|              |       | C.2.1  | MATLAB®/Simulink® s-function              | 174 |  |

|              |       | C.2.2  | SystemC                                   | 178 |  |

| D            | Data  | sheets |                                           | 183 |  |

|              |       |        | er 2                                      | 183 |  |

|              |       |        | er 5                                      | 183 |  |

|              |       | _      | DeskPOD <sup>TM</sup> Datasheet           | 183 |  |

|              |       | D.2.2  | dSpace Datasheets                         | 183 |  |

| Bi           | bliog | raphy  |                                           | 187 |  |

| Gl           | ossar | y      |                                           | 199 |  |

| Acronyms 207 |       |        |                                           |     |  |

xvi CONTENTS

LIST OF FIGURES xvii

## **List of Figures**

| 1.1  | CHILS Schematic Diagram                               |

|------|-------------------------------------------------------|

| 1.2  | Document Structure                                    |

| 2.1  | Simulation Performance [Goo08]                        |

| 2.2  | OVP Core Model Performance in TLM 2.0 [OVP]           |

| 2.3  | Simulation Performance Challenge [DMMN03]             |

| 2.4  | System                                                |

| 2.5  | Processor-in-the-Loop                                 |

| 2.6  | Application of Simulation Techniques [Güh05]          |

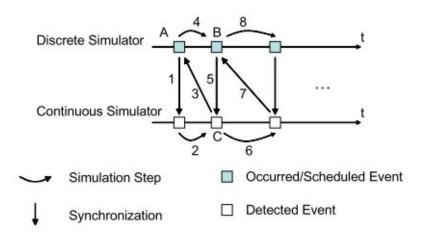

| 3.1  | Simulator Coupling Adapted from [Bra06]               |

| 3.2  | Synchronization Model from [BNAA05]                   |

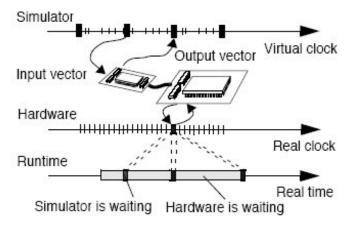

| 3.3  | Simulation-Emulator Synchronization from [HSBG98]     |

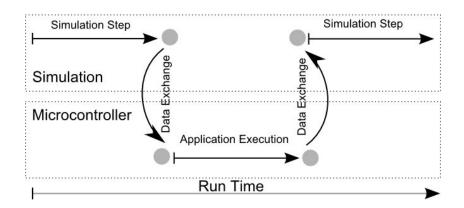

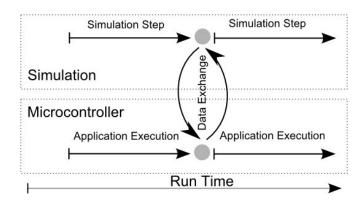

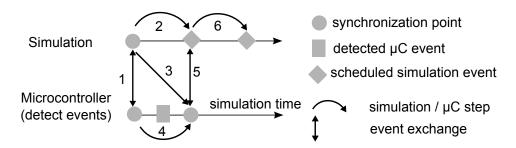

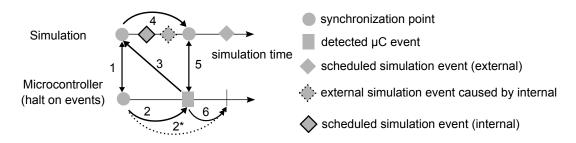

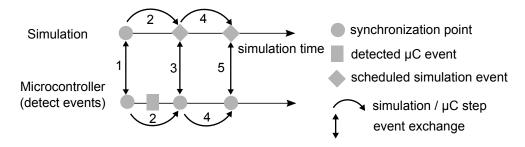

| 3.4  | Alternating Execution                                 |

| 3.5  | Parallel Execution                                    |

| 3.6  | Alternating Execution - MC Leads                      |

| 3.7  | Alternating Execution - Simulation Leads              |

| 3.8  | Parallel Execution - Simulation Leads                 |

| 3.9  | Alternating Execution - $\mu$ C Leads                 |

| 3.10 | Alternating Execution - Simulation Leads              |

| 3.11 | Alternating Execution - $\mu$ C Leads                 |

|      | Parallel Execution - Simulation Leads                 |

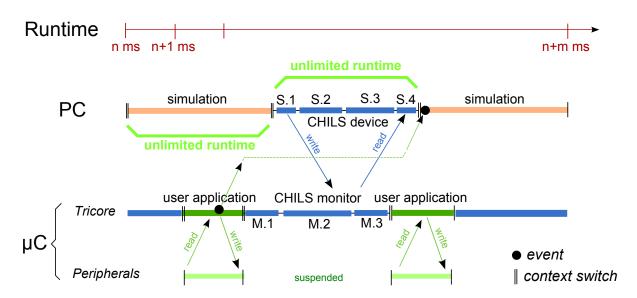

| 3.13 | CHILS Event Exchange Setup                            |

| 3.14 | CHILS Event Exchange Setup                            |

| 3.15 | Compensation by Regaining of Lost Time                |

| 4.1  | SCE-MI Interface between SW Model and DUT [HKPS05] 52 |

| 4.2  | Module Concept                                        |

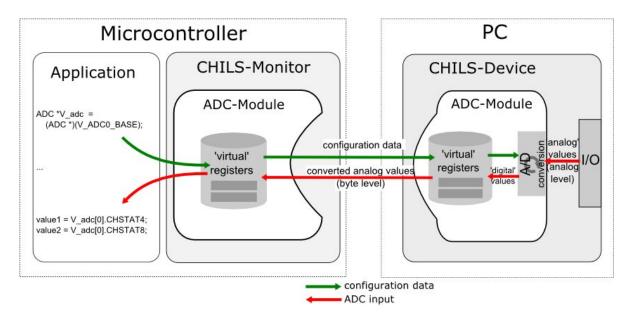

| 4.3  | ADC Module                                            |

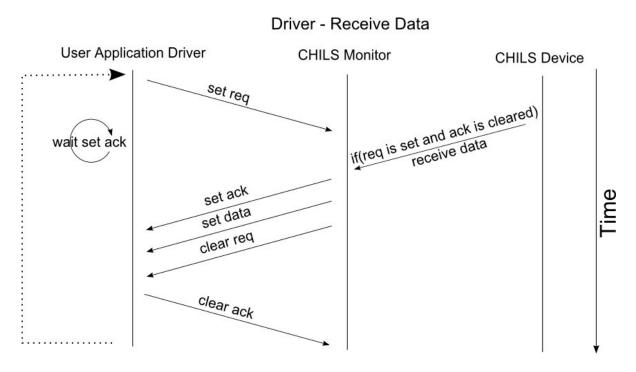

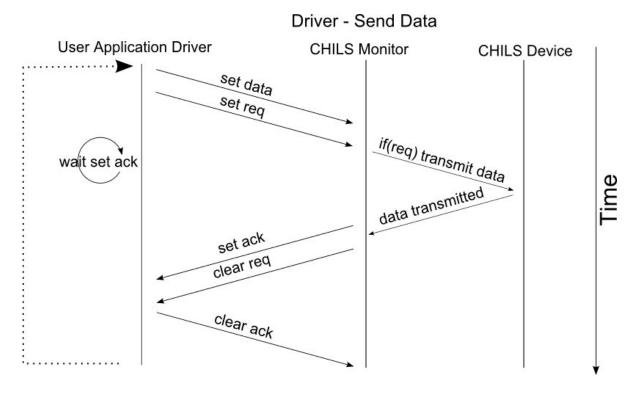

| 4.4  | Receive Synchronization Driver - Monitor              |

| 4.5  | Send Synchronization Driver - Monitor                 |

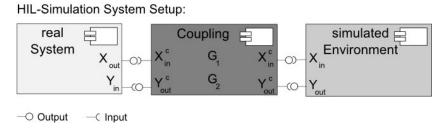

| 5.1  | HIL System                                            |

| 5.2  | HIL System                                            |

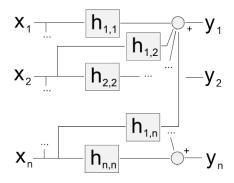

| 5.3                             | MIMO System                                      | 64                                     |

|---------------------------------|--------------------------------------------------|----------------------------------------|

| 5.4                             | Heat-Sensor-in-the-Loop                          | 67                                     |

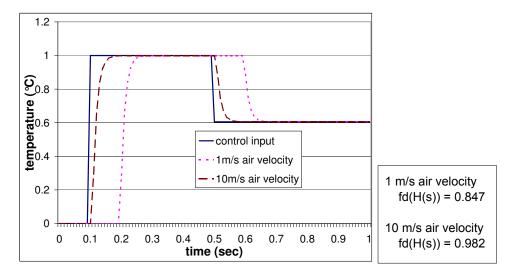

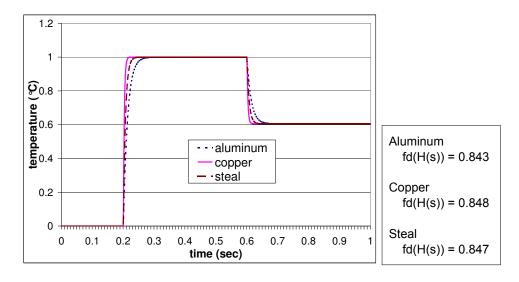

| 5.5                             | Heating System - Different Air Velocities        | 70                                     |

| 5.6                             | Heating System - Different Materials             | 70                                     |

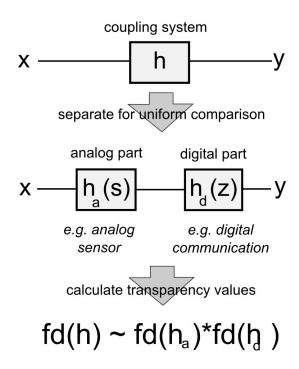

| 5.7<br>E. 8                     | System Comparison Modelling                      | 71                                     |

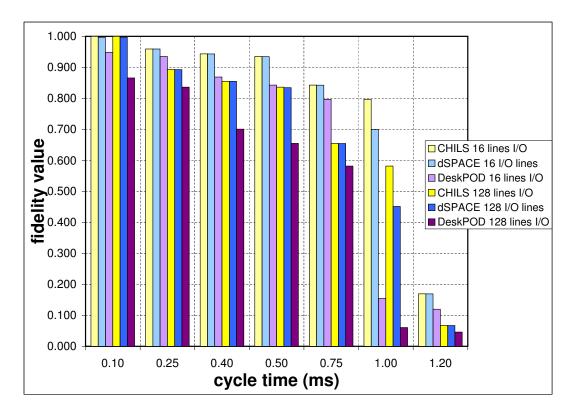

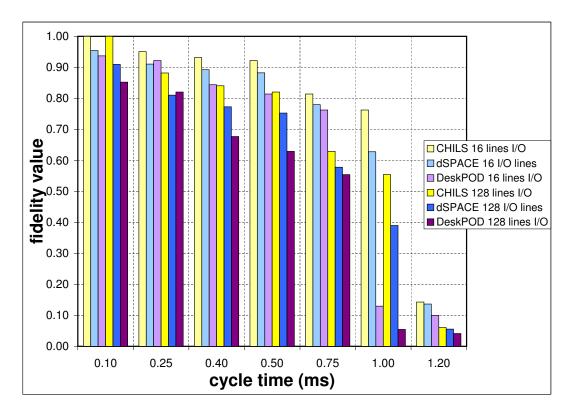

| 5.8<br>5.9                      | Scenario I - Results                             | 76<br>77                               |

| 3.9                             | Scenario II - Results                            | //                                     |

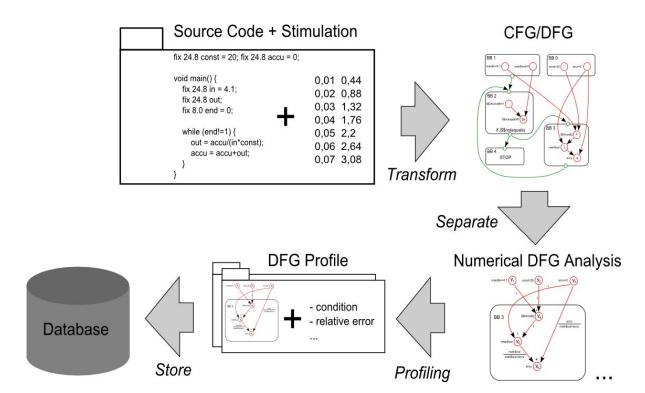

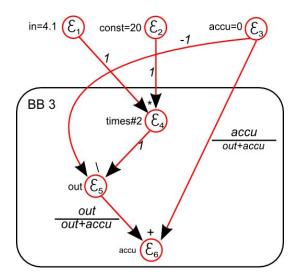

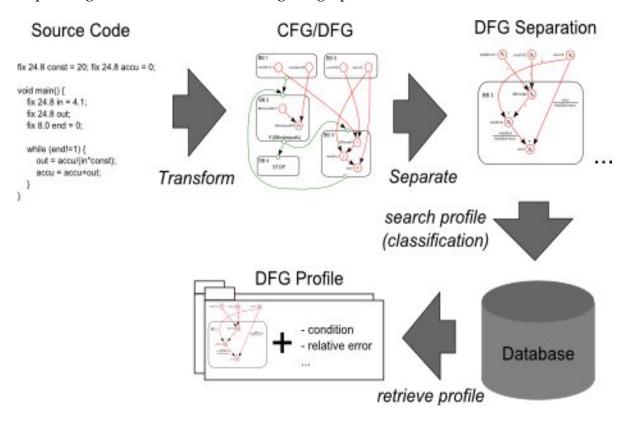

| 6.1                             | Profiling Flow                                   | 85                                     |

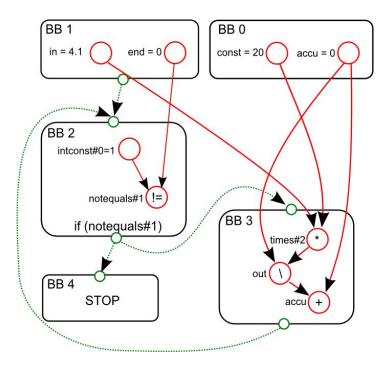

| 6.2                             | Example-CFG-DFG                                  | 87                                     |

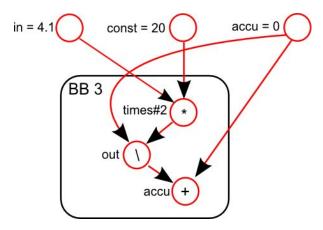

| 6.3                             | Example-DFG                                      | 87                                     |

| 6.4                             | Example-DFG-Condition-Labels                     | 89                                     |

| 6.5                             | Classification Flow                              | 91                                     |

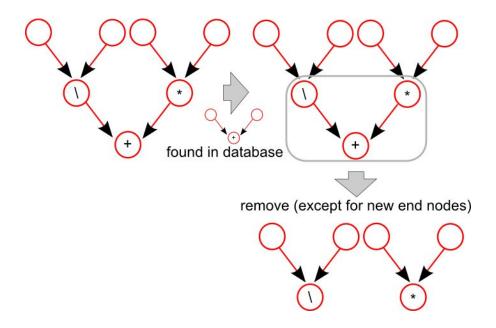

| 6.6                             | Graph Matching - Covering the DFG                | 92                                     |

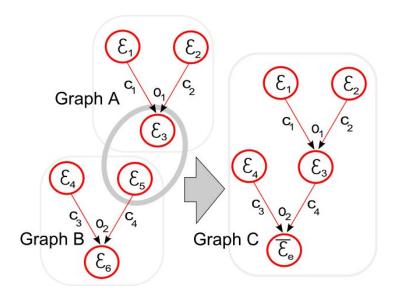

| 6.7                             | Result-Recombination                             | 94                                     |

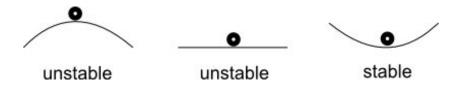

| 6.8                             | Rest Positions of a Mechanical System            | 96                                     |

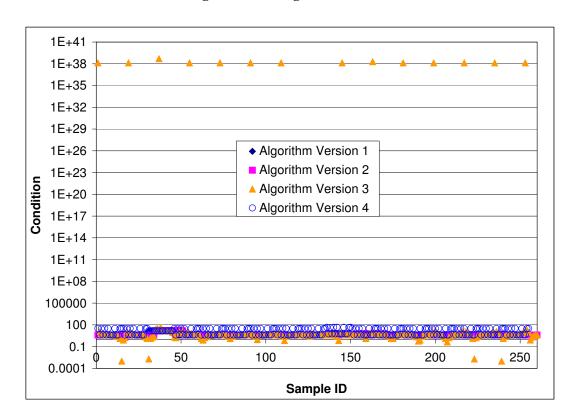

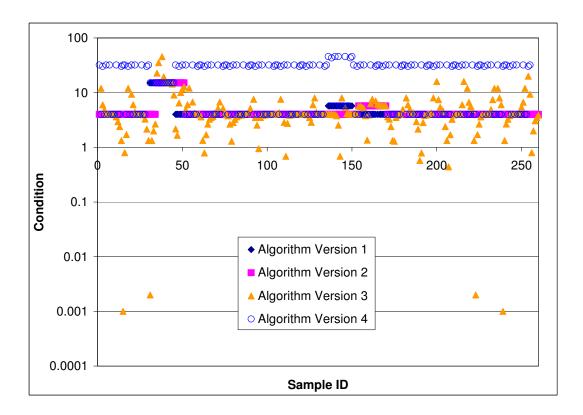

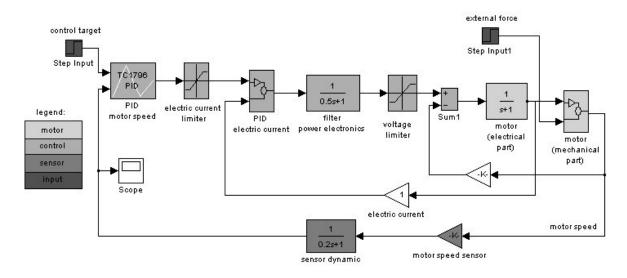

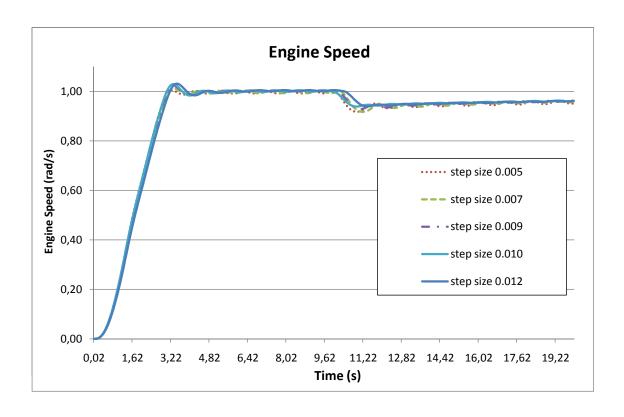

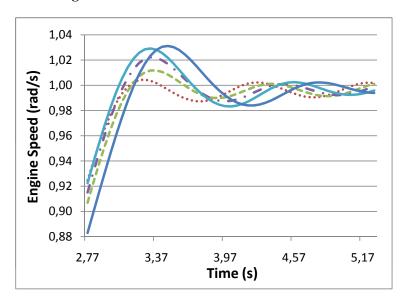

| 6.9                             | Numerical PID Control Analysis Results           | 103                                    |

| 6.10                            | Numerical PID Control Analysis Results - Extract | 104                                    |

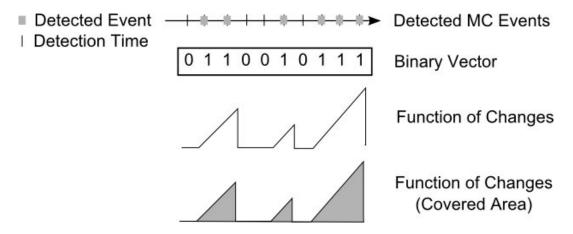

| 7.1<br>7.2<br>7.3<br>7.4        | Measure of Changes of an Event Source            | 109<br>112<br>113<br>113               |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5 | TC1767ED $\mu$ C-EasyKit-Board                   | 116<br>117<br>120<br>126<br>127        |

| 9.1<br>9.2                      | VTB-PIL Coupling from [Len04]                    |                                        |

| 10.2<br>10.3<br>10.4<br>10.5    | SystemC Output                                   | 148<br>150<br>152<br>154<br>155<br>156 |

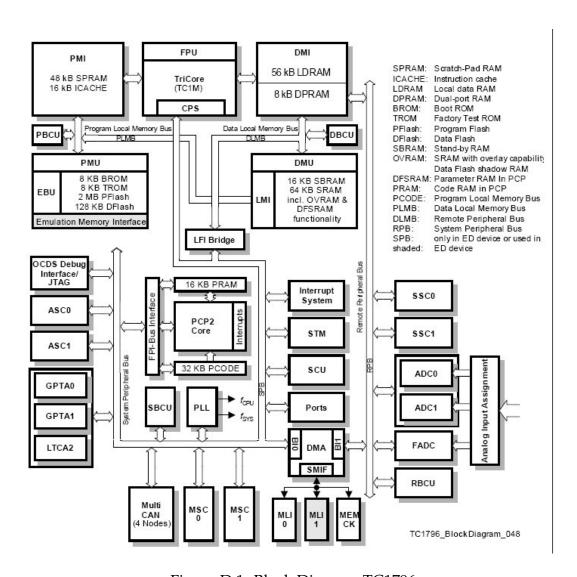

| D.1                             | Block Diagram TC1796                             | 184                                    |

LIST OF TABLES xix

## **List of Tables**

| 3.1        | Basic Concepts [BNAA05]                                             | 26  |

|------------|---------------------------------------------------------------------|-----|

| 3.2        | Exchange Principles                                                 | 32  |

| 3.3        | STM Time Difference Measurements                                    | 41  |

| 3.4        | GPTA Time Difference Measurements                                   | 42  |

| 3.5        | Runtime of Additional CHILS Monitor Instructions                    | 42  |

| 3.6        | STM Time Difference (incl. and excl. Monitor Instructions)          | 45  |

| 4.1        | Interface Abstraction [CGL <sup>+</sup> 00]                         | 50  |

| 4.2        | Interface Abstraction [JBP06]                                       | 51  |

| 4.3        | MC Interfaces Abstraction Levels                                    | 53  |

| 6.1        | Database Size                                                       | 95  |

| 6.2        | Time for Database Filling                                           | 95  |

| 6.3        | Time for Database Retrieval                                         | 95  |

| 6.4        | Attributes of Nonlinear Elements [Wen07a]                           | 97  |

| 7.1        | Event Distribution Accuracy (Mean Values)                           | 114 |

| 9.1        | Abstraction Levels [JBP06]                                          | 130 |

| 9.2        | $\mu$ C Modelling Abstraction Levels and Techniques                 | 130 |

| 9.3        | Performance of 6 Cylinder Engine Simulation with dSPACE             | 134 |

| 9.6        | STM Time Accuracy Measurements                                      | 142 |

| 9.7        | GPTA Time Accuracy Measurements                                     | 143 |

| 9.8        | CHILS-MATLAB/Simulink Sample Application Performance                | 144 |

| B.1        | STM Time Difference Measurements - PWM Generation                   | 165 |

| B.2        | STM Time Difference Measurements (isync/dsync Difference)           | 166 |

| B.3        | STM Time Difference Measurements (isync/dsync Difference)           | 166 |

| <b>B.4</b> | System Comparison - Scenario I                                      | 167 |

| B.5        | System Comparison - Scenario II                                     | 168 |

| B.6        | Synthetic Performance Values (no Oversampling for Event Detection). | 169 |

| B.7        | Synthetic Performance Values (10x Oversampling for Event Detection) | 170 |

| D.1        | DeskPOD <sup>TM</sup> Hardware Datasheets                           | 183 |

| XX  | x                    |  |  |  |  |  |  |  |  |  |  | LIST OF TABLE |  |  |  |  | LES |

|-----|----------------------|--|--|--|--|--|--|--|--|--|--|---------------|--|--|--|--|-----|

|     |                      |  |  |  |  |  |  |  |  |  |  |               |  |  |  |  |     |

| D.2 | dSPACE HW datasheets |  |  |  |  |  |  |  |  |  |  |               |  |  |  |  | 185 |

## Chapter 1

### Introduction

The complexity of embedded hardware/software systems increases every year. For example, the currently implemented embedded systems in cars consist of 10 to 100 million transistors per chip, 1 to 10 million lines of code, and 10 to 100 microcontrollers ( $\mu$ Cs) per car. Especially the automotive industry requires high-end  $\mu$ Cs for Electronic Control Units (ECUs) to fulfil the government's requirements on emissions reduction as well as the customers' demands for comfort, safety and reliability. Today, most failures in cars are caused by electronic components and not by mechanical ones anymore [Jac03]. In addition, the cycle times for new products last only a few years in the automotive industry and just several months in the communications industry.

System modelling becomes even more important to handle the high demands on complexity, reliability, and short development time mentioned above. Model-based development offers possibilities like early exploration of system designs, rapid prototyping, and extended system verification, optimization and testing. It allows the engineers to develop software and hardware in parallel to reduce the cycle times. Furthermore, these systems are often a recombination or extension of existing parts to reduce the development effort.

#### 1.1 Motivation

The present development in high-tech industry causes an exponential growth of system simulation performance requirements that cannot be covered by the rising simulation computer performance. The current method is to use different levels of abstraction, since a higher level of abstraction increases simulation speed. Modelling is a trade-off between high speed, high accuracy and low effort. It is easy to create a model covering two of these three attributes but it is nearly impossible to build high speed and high accuracy models spending only a small amount of effort. This trade-off is especially critical if system software development is supposed to begin on the simulated system hardware. Because of this, software developers need highly accurate and fast models.

### 1.2 Objective of the Thesis

Many complex hardware/software systems are a combination of existing parts like  $\mu$ Cs, memory subsystems, interconnect structures, input/output (I/O) modules and hardware accelerators. The possibility to embed a real  $\mu$ C into a system simulation of a larger technical context would be a great benefit. Compared to a model, the real  $\mu$ C will run with high speed and full accuracy. This is an advantage especially for early software development. The challenge is to embed the  $\mu$ C into the simulation environment so that it is transparent to the system simulation whether it is a simulated or a real  $\mu$ C. This kind of solution needs to meet different demands, namely:

- The data exchange and synchronization between real hardware and simulated hardware has to be realized in an efficient and effective way.

- A certain accuracy of the coupling system has to be guaranteed.

- The hardware has to be coupled with different simulation environments.

- In order to reduce the amount of exchanged data a suitable level of abstraction for the  $\mu$ C interfaces and peripherals has to be found.

- Transparency of the coupling between simulated environment and the  $\mu C$  to the executed  $\mu C$  is needed to minimize the influence of the coupling to the simulation results.

- The hardware effort for coupling determines the practicability of the solution.

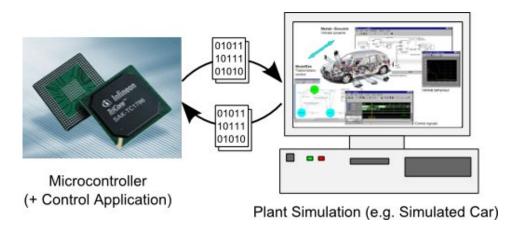

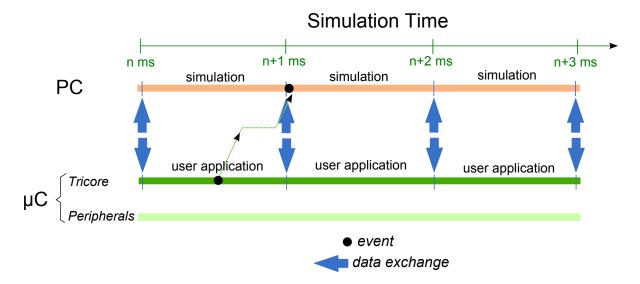

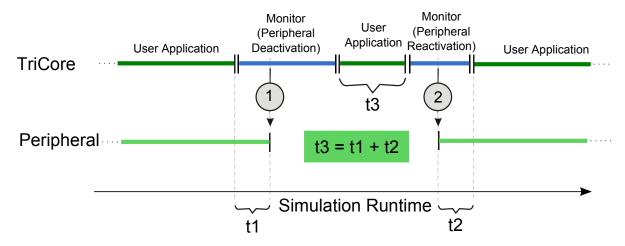

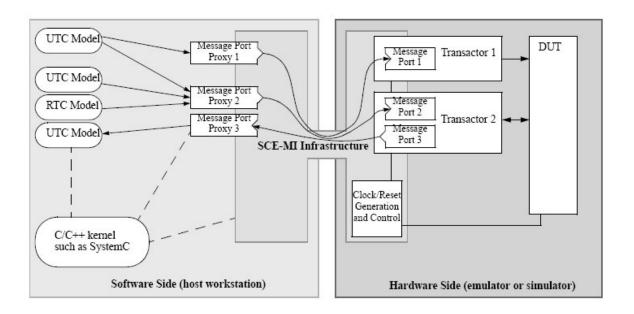

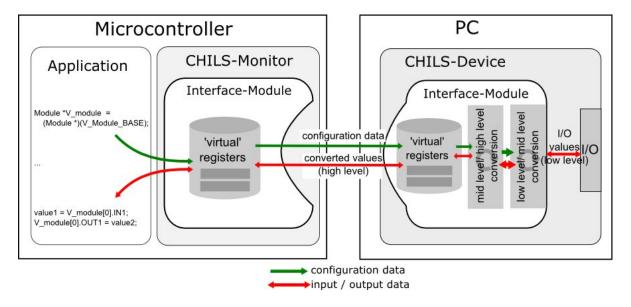

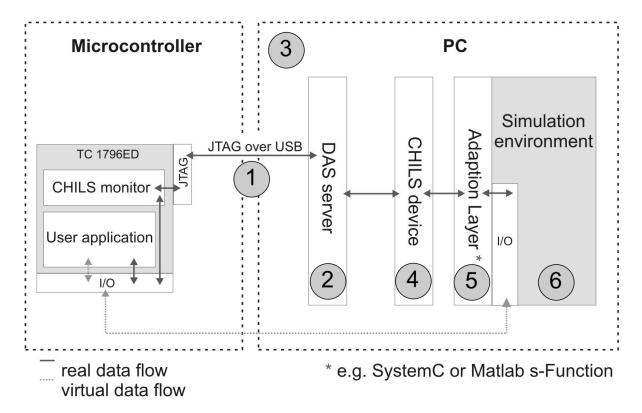

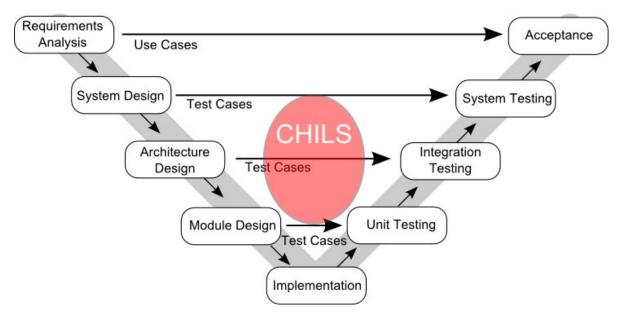

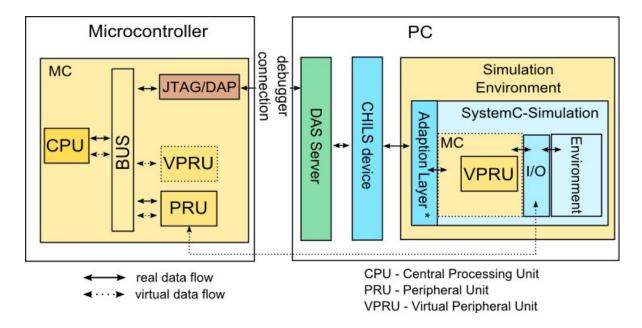

Figure 1.1: CHILS Schematic Diagram

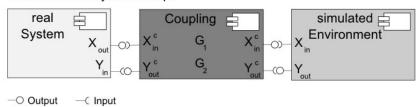

With respect to the existing concept of Hardware-in-the-Loop (HIL) simulation, the presented approach is called Chip-Hardware-in-the-Loop Simulation (CHILS) (see figure 1.1). HIL simulation is a technique that is used in the development and testing of complex embedded systems. In a HIL simulation, the represented system consists

of the simulated part and a real part, the "hardware-in-the-loop". CHILS meanwhile focuses on complex hardware/software systems designed with existing  $\mu$ Cs.

### 1.3 Thesis Organization

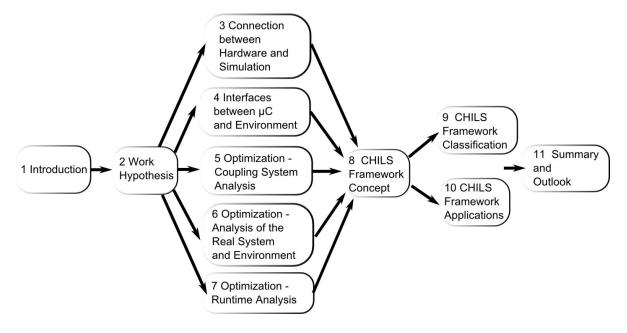

The thesis organization is shown in figure 1.2. The following chapter includes the working hypothesis, related work and the basics of the thesis. Three main topics are identified: the connection between hardware and simulation, the representation of  $\mu$ C interfaces in the coupling of hardware and simulation, and the event exchange optimization between hardware and simulation. These topics are examined in the following five chapters. Chapter 3 introduces the  $\mu$ C hardware to simulation coupling which is used to realize the CHILS approach. The representation of the  $\mu$ C interfaces, from the simulation point of view and from  $\mu$ C point of view, is explained in chapter 4. Chapters 5, 6 and 7 cover different aspects of the hardware to simulation coupling optimization. Chapter 8 gives an overview of the complete CHILS framework. Chapter 9 covers the classification of the CHILS framework. A comparison with other solutions is presented. Some applications for the CHILS approach are shown in chapter 10. Finally, the conclusions can be found in chapter 11.

Figure 1.2: Document Structure

<sup>&</sup>lt;sup>1</sup>The term hardware to simulation coupling as well as the terms  $\mu$ C to simulation coupling and  $\mu$ C hardware to simulation coupling denote all the same setup of a coupling between a  $\mu$ C and a simulation environment on the PC.

## **Chapter 2**

### Related Work and Work Hypothesis

The dilemma of modelling complex hardware/software systems is the combination of the three main aspects: speed, accuracy and effort. The target is to have high speed models with high accuracy, combined with a low effort for model creation and application. For  $\mu$ C applications this means to have nearly 100 percent cycle accurate models, which are created or generated automatically, and which run in real time on a standard Personal Computer (PC).

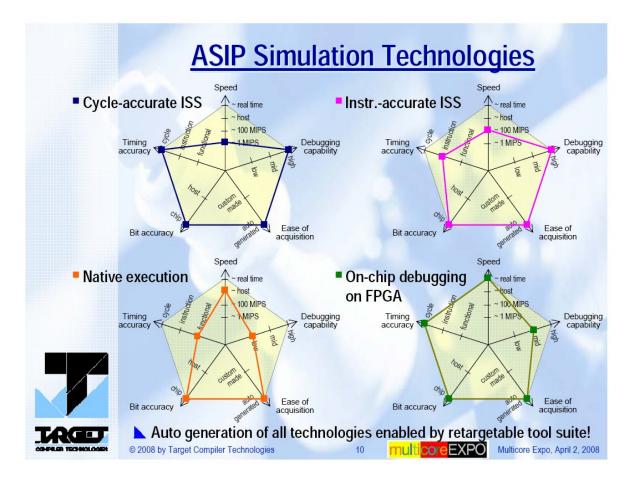

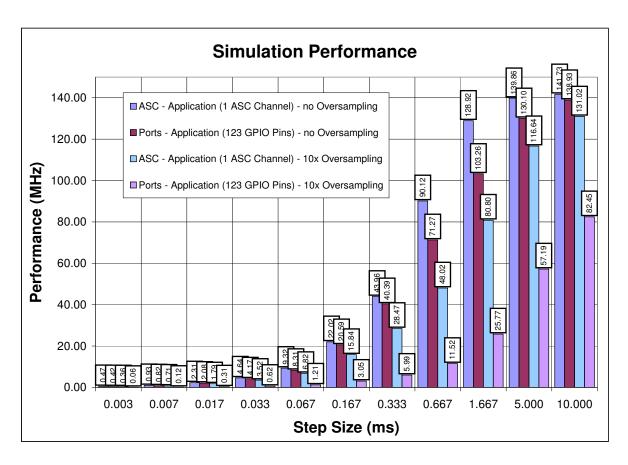

This requirement is nearly impossible to fulfill. Figure 2.1 shows performance measurements presented by the company Target Compiler Technologies [ReT] at the conference and exhibition multicore EXPO in 2008 [Goo08]. A cycle accurate Instruction Set Simulator (ISS) has a performance of about one Million Instructions per Second (MIPS). This is very fast for a cycle accurate model, but this model is just an ISS, so it contains no peripheral module models. A  $\mu$ C contains a lot of peripheral modules in addition to the main core, the Central Processing Unit (CPU). The target device used in this thesis, the high-end 32bit TriCore®  $\mu$ C<sup>1</sup> series shown in figure D.1, contains several complex peripherals like the General Purpose Timer Array (GPTA). The GPTA provides a set of timer, compare and capture functionalities, which can be flexibly combined to form signal measurement and signal generation units. The combination of over one hundred timers and thousands of trigger combinations between them makes this module hard to model. A speed-up in modelling is mostly achieved by reducing the events <sup>2</sup> and the state changes produced within a model. If hundreds of sources and sinks for events exist, for example inside the GPTA, the task becomes very difficult. A less accurate model, with the focus set to instruction accuracy and not in addition to timing accuracy, can achieve about 100 MIPS (see figure 2.1). Such an instruction accurate model will be less time accurate, because of the simplification of the instruction execution process (pipelining is often not included) and of the memory access (the cache behaviour is not modelled). A complete  $\mu$ C modelled

$<sup>^{1}</sup>$ The TriCore is a 32-bit  $\mu$ C-Digital Signal Processor (DSP) architecture which is optimized for real-time embedded systems. Its main applications are engine control, body and safety applications within the automotive sector an industrial applications.

<sup>&</sup>lt;sup>2</sup>An event can be defined as an indicator for a change [ZPK00].

Figure 2.1: Simulation Performance [Goo08]

on that abstraction level can have a performance which is the tenth part of a model which only covers the CPU. Within the project *Open Virtual Platforms* [OVP] core models modelled in Transactional Level Modelling (TLM) 2.0 <sup>3</sup> with a performance of some hundred MIPS can be found. The peak performance is higher than 1000 MIPS (see figure 2.2), but these are only models of processor cores without peripherals.

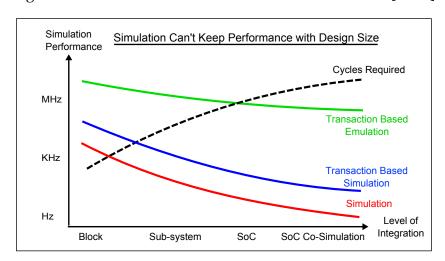

The raising abstraction level of models primarily addresses the biggest problem of current Systems-on-Chip (SoC) and  $\mu$ C modelling. The available performance grows slower than the demand for it, caused by the rising complexity of such systems. "Simulation Can't Keep Pace with Design Size" [DMMN03].

Beyond the modelling itself, another important part is the verification of the correctness of the model. The model is useless if the functional correctness is not

<sup>&</sup>lt;sup>3</sup>TLM 2.0 is the current standard in transaction level modelling. TLM is mostly connected with SystemC [Sys]. It is an interface standard that enables the interoperability and reuse of SystemC models at the transaction level.

2.1. BASICS 7

| TLM2.0/OVP                        | Single                    | : ARM       | Core           | MultiCore:                | 2 MIF       | S Cores        | ManyCore: 24 ARC Cores    |             |                |  |  |

|-----------------------------------|---------------------------|-------------|----------------|---------------------------|-------------|----------------|---------------------------|-------------|----------------|--|--|

| Benchmark                         | Simulated<br>Instructions | Run<br>time | Simulated MIPS | Simulated<br>Instructions | Run<br>time | Simulated MIPS | Simulated<br>Instructions | Run<br>time | Simulated MIPS |  |  |

| linpack                           | 578,061,601               | 1.33s       | 435            | 442,853,216               | 2.61s       | 170            | 100,419,903,936           | 348.56s     | 288            |  |  |

| fibonacci                         | 328,512,265               | 1.35s       | 243            | 1,075,056,992             | 4.21s       | 255            | 14,692,840,992            | 61.48s      | 239            |  |  |

| Dhrystone                         | 4,544,054,499             | 12.29s      | 370            | 1,010,144,280             | 2.36s       | 427            | 14,977,987,872            | 10s         | 365            |  |  |

| peakSpeed1                        | 5,600,001,624             | 4.93s       | 1137           | 11,200,002,620            | 9.36s       | 1197           | 144,000,042,864           | 147.83s     | 974            |  |  |

| All measurements on 3 GHz Pentium |                           |             |                |                           |             |                |                           |             |                |  |  |

Figure 2.2: OVP Core Model Performance in TLM 2.0 [OVP]

Figure 2.3: Simulation Performance Challenge [DMMN03]

verified. The silicon test benches for  $\mu$ C verification will fail on a model of a high abstraction level, because the tests require a cycle accurate behaviour <sup>4</sup>.

All this leads to the idea to use the real  $\mu C$  as a replacement for a modelled  $\mu C$  inside of a system simulation. The  $\mu C$  is already verified and the maximum performance reachable with a  $\mu C$  is its natural performance. The overall system performance is primarily limited by the performance of the coupling system between real hardware and simulation.

#### 2.1 Basics

The introduction refers to the importance of system modelling and simulation and the complexity of doing so. This section introduces the motivation behind these techniques. Furthermore the different types of simulations are presented as well as the basics of modelling. Modelling is the task to find a suitable description of a system.

<sup>&</sup>lt;sup>4</sup>The test benches are composed of sets of input data and sets of expected output data including hard deadlines. The tests will fail if the system-under-test-response does not match with the expected response in time.

The *Deutsches Institut für Normung (German Institute for Standardization*) defines in DIN 19226 [DIN] a **system** as follows:

**Definition 2.1.1.** A system is an arrangement of entities in an observed context which are related to each other. This arrangement is separated from the environment by defined conditions.

Ein System ist eine in einem betrachteten Zusammenhang gegebene Anordnung von Gebilden, die miteinander in Beziehung stehen. Diese Anordnung wird aufgrund bestimmter Vorgaben von ihrer Umgebung abgegrenzt.

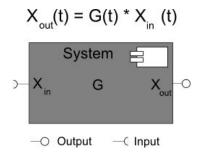

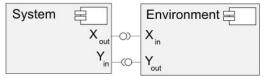

Figure 2.4: System

This is a general definition but it contains the important aspects. A system consists of related parts and it can be separated from its environment. In the book *Signale und System* (Signals and Systems) [Kie98] Uwe Kiencke defines a system as a construction which reacts on an input signal with an output signal (figure 2.4). A **signal** is defined as a physical quantity which changes over time and contains information. So another property of a system is the existence of inputs and outputs.

**Definition 2.1.2.** *In summary a system can be defined by (see [Abe03a]):*

- the system boundary (real physical boundary or imaginary boundary)

- input and output variables which pass the boundary

- *internal variables* (the internal states)

- the behaviour which defines the relation between input, output and internal states

DIN 19226 [DIN] includes in addition a definition for a **model**:

**Definition 2.1.3.** A model is a mapping of a system or a process to another conceptual or representational system, which is created by using known principles, an identification or assumptions. The model has to represent the system or the process sufficiently accurately with respect to the question at hand.

2.1. BASICS 9

Ein Modell ist die Abbildung eines Systems oder Prozesses in ein anderes begriffliches oder gegenständliches System, das aufgrund der Anwendung bekannter Gesetzmäßigkeiten, einer Identifikation oder auch getroffener Annahmen gewonnen wird und das System oder den Prozeß bezüglich interessierender Fragestellungen hinreichend genau abbildet.

The phrase "sufficiently accurately" is the most interesting part of the definition. The needed accuracy depends on the field of application of the model. A model will never be identical with the system which is modelled. It is just a representation of the system or rather a representation of certain aspects of the system. Different modelling principles exist to model these certain aspects. If the target is to model a  $\mu$ C or a System-on-Chip (SoC), the modeller can fulfil the task for example in the physical domain by modelling the transistors and their charge, or he or she can write a model which realizes the pure functionality and no physical aspects.

#### 2.1.1 Motivation for Modelling and Simulation

Now the question is why do we need to model and simulate a system? Due to the rising complexity of systems in all domains it is not reasonable to design and build real systems via trial and error from scratch. The effort in terms of time and cost would be too high. The design of real prototypes has to be reduced. The goal is to build a system "first time right", so that the first prototype works properly. Modelling and simulation are the tools to reach that goal. André Lüdecke mentions in *Simulationsgestützte Verfahren für den Top-Down-Entwurf heterogener Systeme* [Lüd03a] the following motivations for simulations.

- The system specification can be validated very early (Am I building the product right?). The system design could be wrong because of system interactions which were not understood or not taken into account during the specification phase. A simulation can help to discover such failures and leads to a deeper understanding of a system.

- Components are sometimes not available in an early stage of system development. Especially if systems are developed in a top-down approach. At an early stage of development, only the specification of the whole system is available. Simulations can help to make early design decisions regarding the components and reduce the iterations in the design process. A big issue in the design of combined hardware/software systems is the hardware/software partitioning. The main question is which part of the system should be software (more flexibility) and which part should be hardware (more efficiency). A lot of research is done in this area (a short overview can be found in *Hardware/Software Codesign Pedagogy for the Industry* [HTW+08]).

- Sometimes the observation of internal states of a system is not possible in an experimental environment. A simulation enables the user to observe all internal

states, variables and parameters (as long as they are modelled). Moreover, the functional and the timing behaviour of the simulation will not change if the observation is running, unlike the behaviour of the real hardware.

- The costs are very high for measurements with real prototypes. A simulation is often cheaper than a real experiment (think about a car crash simulation in automotive industry). Experiments are mostly very time consuming and require cost intensive measurement equipment. The main purpose is to use experiments just for verification of the models.

- Experiments with real prototypes can be dangerous and destructive. Simulation enables to explore the system limits.

Simulation is a powerful tool in system design, but one has to be aware that a model is only a simplified representation of the system.

#### 2.1.2 Modelling Basics

In general, the differentiation between **structural** and **pragmatic modelling** can be made (see [PLG02]). **Structural modelling** is also called **white-box modelling**. The inner structure of the systems is known. The modelling is done by abstracting the given system parts. At **pragmatic** or **black-box modelling** the inner structure is unknown. Only the interaction of the systems, the external behaviour or the reaction on signals can be observed. The modelling is done by the imitation of the observed behaviour as so-called **behaviour models**. This is also called behaviour modelling (see [Lüd03b]). Combinations of both approaches are called **grey-box modelling**. This is often the most efficient way.

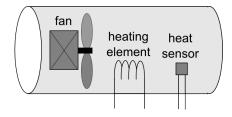

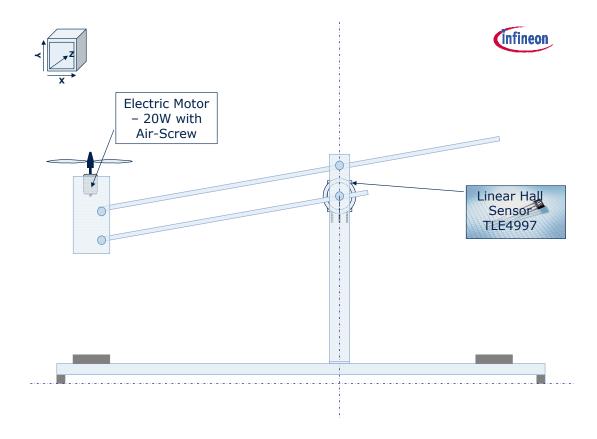

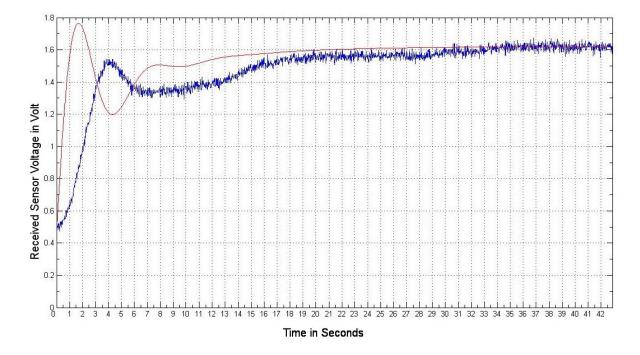

**Behaviour models** represent the system by equations or tables, for example as a characteristic curve. The behaviour of a system can be described by underlying physics of the system or by measured or simulated input and output values. A typical example is the control path of the CHILS demonstrator system presented in chapter 10 in subsection 10.2.1. The demonstrator consists of a rocker with an air-screw attached, which is controlled by a TC1796  $\mu$ C. The rocker-air-screw system is modelled by determining the transfer function of the system by measurements.

**Structural models** consist of mostly hierarchical sub-models. These sub-models can also contain other sub-models or basic models. These basic models can be structural or behaviour models. A typical example of structural models are models of SoCs or  $\mu$ Cs.

Both structural and behaviour models can be used on different levels of abstraction. A good overview can be found in Daniel D. Gajski's and Frank Vahid's book *Specification and Design of embedded Systems* [GVNG94].

Additional differentiations between **heterogeneous** and **homogeneous modelling** are possible. Modelling languages and simulation systems are often bound to spe-

2.1. BASICS 11

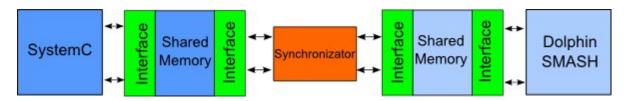

cial domains. In **heterogeneous modelling**, a specific language and/or simulation environment can be applied for each domain of a system to create the model. So it is possible to choose the language and/or simulation environment which fits best to the modelling task. This can reduce the effort for modelling enormously. Sometimes this technique is called **multi-language approach**. The major problem arising from multi-language modelling is the coupling of different simulation environments. This topic is discussed in detail in chapter 3.

In homogeneous modelling or single-language modelling, the system is described by only one modelling language. Only one simulator is needed so problems caused by coupling are eliminated. The whole handling of the simulation is easier. Perhaps some parts of the system have to be described in a language that does not fit well to the domain of these parts. This can be a disadvantage.

#### 2.1.3 Simulation Systems

Simulation is the method to perform experiments on models of systems. During the simulation the state of the model changes. This state change can be seen as **simulated time or simulation time**. This internal time is independent from the **simulation runtime**, the external time. It is called **realtime simulation** if the simulated time and the runtime of the simulation are identical. Furthermore, the (software) environment running the simulation is called a **simulator**.

Depending on the domain of modelling different types of simulation techniques and principles have been developed. Basic theoretical contemplations can be found in Bernard P. Zeigler's, Herbert Praehofer's and Tag Gon Kim's book *Theory of modelling and simulation - integrating discrete event and continuous complex dynamic systems* [ZPK00]. They differ between three respectively two basic types. These are:

**DESS** - Differential Equation System Specification - continuous in time and values

**DTSS** - Discrete Time System Specification - a time discrete system

$\textbf{DEVS}\,$  - Discrete Event Systems Specification - it can be seen as more general version of DTSS  $^5$

An even more detailed hierarchy of simulation methods can be found in *Diskrete Simulation – Prinzipien und Probleme der Effizienzsteigerung durch Parallelisierung* written by F.Mattern and H. Mehl [MM89]. The main differentiation is also between **continuous** and **discrete simulation systems**, but the authors do not see Discrete Event Systems Specification (DEVS) as an even more general version of Discrete Time

<sup>&</sup>lt;sup>5</sup>A change of a state can happen at every point of time, in contrast to a DTSS system. Time steps are variable and they will be adapted to the events. The point in time of the next event has to be known.

System Specification (DTSS). DESS systems are often called continuous simulation systems <sup>6</sup>. F.Mattern's and H. Mehl's hierarchy is defined as follows:

- continuous

- discrete

- event-driven

- \* event-oriented

- \* activity-oriented

- \* process-oriented

- \* transactional

- time-driven

- quasi-continuous

The principles of continuous and discrete simulation are independent from the level of abstraction. Further explanations about different levels of abstraction are given in chapter 9. The CHILS Framework is compared with  $\mu$ C models of different abstraction levels. An overview about these simulation methods can be found in Stefan Eilers *Zeitgenaue Simulation gemischt virtuell-realer Prototypen* [Eil06].

#### **Continuous Simulation**

Time and values are continuous in a continuous simulation, so the model changes continuously. The models are often based on differential equation systems, which are solved by numerical integration. In reality the simulation is only quasi-continuous due to the numerical solving on a computer. The time steps, which are performed by the numerical solver, are often adapted to the differential equation system which is to be solved. This is caused by the non-exact solving behaviour of numerical algorithms. An exact analytical solution is not possible for general differential equation systems (see [Bec05]).

In continuous (or quasi-continuous) simulators like Simulink®, the numerical solver can be chosen by the user. There are different numerical methods: the single-step and the multi-step method. The accuracy of the methods depends on their order. A method of a higher order usually leads to a higher computational resource consumption for calculation. Willi Törnig and Peter Spellucci provide a good overview about these methods in the book *Numerische Mathematik für Ingenieure und Physiker* [TS90].

<sup>&</sup>lt;sup>6</sup>In fact most continuous simulation system are only quasi-continuous due to the discrete nature of simulation computers. From now on the term continuous simulation or Differential Equation System Specification (DESS) is used for that kind of simulation system.

2.1. BASICS 13

#### **Discrete Simulation**

In a discrete simulation, the state changes of the model occur at determined points in time. The time jumps from one change to the other. The state change is caused by incrementing the simulation time, which is called **time-driven**, or caused by events, which is called **event-driven**. A time-driven simulation can run on an event-driven simulator by generating time-events (see definition in Bernard P. Zeigler's book [ZPK00]).

**Definition 2.1.4.** *An event is an indicator for a change.*

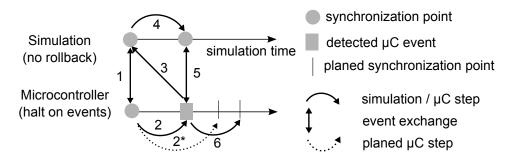

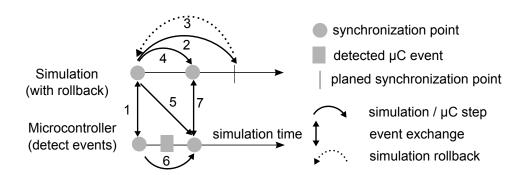

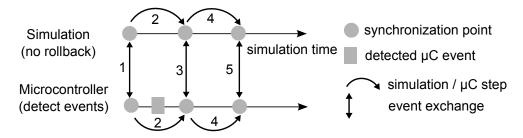

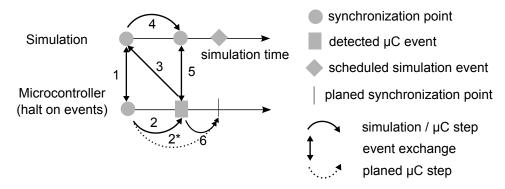

Event-driven Simulation In an event-driven simulation events, which are marked by time stamps, cause the state changes of the model. If the event-driven simulation contains only one model, which runs in one simulator, the functionality can be described as follows. A global event queue sorts the events based on their time stamps. The simulator chooses a non-processed event with the smallest proximity in time in difference to the actual simulation time. Then the simulation time is set to the time stamp of this event and the event is processed. The event processing changes the state of the model. New events can be produced and these events are sorted into the global event queue. If more than one model (and possibly more than one simulator) are used, the models have to be synchronized, because each model has its own simulation time. Stefan Eilers [Eil06] mentions two principles to obtain the causal order of the events: the **conservative** and the **optimistic principles**.

Conservative principles guarantee the maintenance of the causal order. The simulation time is only incremented if all relevant events can be determined. The simulation step size is chosen in the way that all events are processed to the exact point of time of occurrence. Sometimes this can cause deadlocks or slow down the simulation by producing empty synchronization events.

**Optimistic methods** are based on the assumption that violations of the causal order are seldom. The simulation is incremented even if not all relevant events are known. If an event is detected with a time-stamp smaller than the actual simulation time, the simulation is set back to a point of time before the event occurs. Now the next step can be set exactly to the right point of time. This principle is called rollback or backtracking. Previous simulation states have to be stored. One version of the rollback simulation is the **time-warp method**.

These principles are basics of simulator coupling and Co-simulation. In chapter 3 *Connection between Hardware and Simulation* this topic is evaluated.

In general, event-driven simulation is very efficient because computation time is only consumed if state changing events occur. Dead times with no changes do not consume computation time, unless all relevant events are known.

A popular event driven simulator is the SystemC simulation framework [Sys] which is one of the target frameworks to couple with CHILS.

**Time-driven Simulation** The simulation time is incremented in fixed or variable steps (see [Eil06]). All events with a time stamp between the last and the present simulation point of time are processed. It is important that the time step is small enough, so that the events processed in the same interval only influence events in simulation future. Time-driven simulation is normally slower than event-driven simulation because time steps without processed events must not be ignored.

A general time-driven simulator works as follows ([HP02]). First the simulator initializes the system state and simulation time. As long as the simulation is not finished, the following steps have to be repeated: collecting statistics about the current state, handling events that occurred between the last step and incrementing the simulation time. Time-driven simulators are used for example in network simulations.

### 2.2 Possibilities of Hardware-Simulation-Coupling

The concept of hardware-simulation coupling has been existing for several years. Sheran Alles, Curtis Swick, Syed Mahmud and Feng Lin [ASML92] present an integrated HIL simulation systems which does not differ from actual systems. The simulation runs on standard PC hardware, while the coupling is realized with special I/O cards.

Paul Baracos defines the term HIL simulation in the following way [BMRJ01]:

**Definition 2.2.1.** *In HIL, either a simulated plant is wired to a real controller, or a real plant to a simulated controller.*

So two types of HIL simulations can be distinguished. In *Design of the Embedded Software Using Flexible Hardware-In-the-Loop Simulation Scheme* D. Virzonis, T. Jukna and D. Ramunas call these types **plant simulation** and a **controller behaviour simulation** [VJR04]. Other terms with identical meaning or specialization can be found in literature, too.

Within a **plant simulation** the mathematical model of the control object, called plant, is running on a general purpose computer. For example, the controller is connected via a Data Acquisition (DAQ) board with the simulation PC. The **controller behaviour simulation** inverts the situation. The prototype of a control programme runs on a general purpose computer which is connected to a real plant for example through a DAQ board. Sometimes special simulation computers instead of general purpose computers are used to run the simulation. The solutions of dSPACE [dsp] are one example (see subsection 2.2.2). They will be discussed later in this chapter.

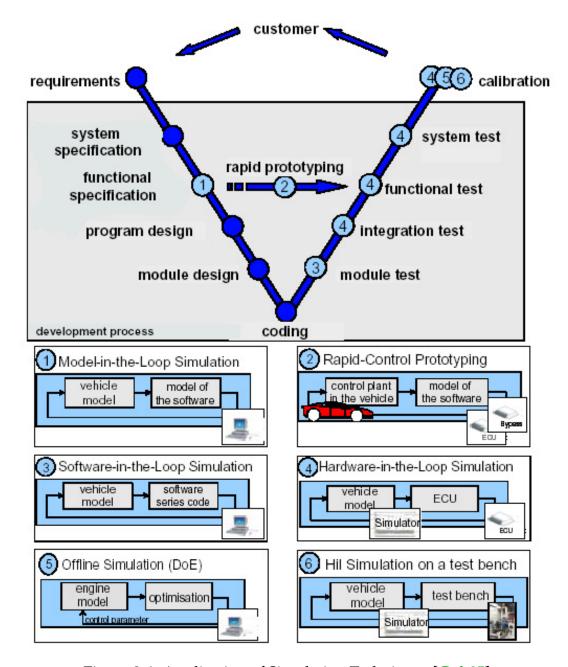

### 2.2.1 Motivation for Hardware-in-the-Loop

HIL simulation is a widely used concept. Especially within the automotive industry, it is used mainly for rapid prototyping, test and optimization of systems. A typical example of HIL simulations is a connection between a complete ECU (including a

$\mu$ C) and a simulated car environment. The environment is the plant, while the ECU is the controller in this setup. [WMH04],[Güh05], and [PSF04] are typical examples for this application. Jae-Cheon Lee and Myung-Won Suh describe in [JCL99] a HIL simulator for testing an ECU for an Anti-Lock Braking System (ABS) and Traction Control System (TCS). Such an application is a typical HIL supported test scenario. Several reasons lead to the development of HIL simulation systems (see [Abe03b], [WMH04] and [Rot04]).

- Critical scenarios can be tested without compromising hardware or people.

Safety-critical components (such as drive-by-wire) can be tested without danger.

- Test automation is possible.

- HIL tests are cost-efficient tests. A scenario is easier to configure in a virtual environment than in a real environment. So, for instance, fewer test drives and test bench experiments are needed, and also fewer vehicle prototypes or vehicle components - resulting in cost savings.

- On one hand, the virtual environment can be easily modified, so a real control (the real ECU) can be tested in different control loops. On the other hand, a real control loop (for example an engine) can be easily tested with different simulated controllers (or control algorithms). Difficult ambient conditions (winter tests, rain, high or low temperatures) can be simulated by simple parameter changes.

- Tests are immediately repeatable, so component failures and associated emergency scenarios can be tested reproducibly.

- The hardware can be tested in parallel in different working environments (for example in a climate chamber).

- If some parts of a system are too complex to model, they can be replaced inside the simulation by the real hardware.

- The embedded real hardware can accelerate the whole simulation.

- The hardware and software of ECU can be tested at an early stage of development. A real engine or a real transmission is not needed.

### 2.2.2 Commercial Hardware-in-the-Loop Solutions

Especially the importance of HIL-simulation for the industry leads to a wide offering of commercial solutions. Simulation software like MATLAB®/Simulink® is well established to design complex systems. HIL solutions need to offer the interface between the simulation software and the "hardware-in-the-loop". Depending on the field of application, the system also has to be real-time capable (for example for

ECU-in-the-Loop scenarios). The following simulation frameworks are an overview about available commercial solutions. The principles are more or less identical. A standard PC or a dedicated simulation computer, often designed from standard PC hardware, hosts the simulation while the connection to the hardware is realized by DAQ cards or external units. Classical HIL simulations require more often than not real-time capable simulations, because the hardware-in-the-loop, like an ECU, cannot be slowed down.

#### **MathWorks**<sup>TM</sup>

MATLAB® from MathWorks<sup>TM</sup> [Mat] is a well known solution for technical computing. It offers great capabilities for numerical computations. Based on this computation solution, MathWorks<sup>TM</sup> delivers Simulink®. Simulink® is an environment for model-based design of complex dynamic systems. Systems can be designed on a high level by modelling the interactions between functional blocks. The calculations of the blocks are done by MATLAB®.

With xPC Target<sup>TM</sup>, MathWorks<sup>TM</sup> offers a solution for rapid prototyping and HIL-simulation (see [xPC09]). xPC Target<sup>TM</sup> delivers I/O interface blocks for Simulink® models. These interface blocks represent I/O boards inside a PC. xPC Target<sup>TM</sup> executes the models under a realtime kernel on the PC. The "hardware-in-the-loop" is attached to the I/O boards.

MATLAB®/Simulink® is one example for a simulation environment which can be coupled to a  $\mu$ C via the CHILS approach. The CHILS demonstrator platform presented in chapter 10 *CHILS Framework - Applications* uses MATLAB®/Simulink® to simulate the control path.

In addition, MathWorks<sup>TM</sup> offers an auto-code generator bundled with a Processor-in-the-Loop (PIL) solution <sup>7</sup> which is called *Link for TASKING*® [Lin09]. *Link for TASKING*® links MATLAB® and Simulink® to the TASKING [TAS] environment. Depending on the  $\mu$ C, the generated code runs on an ISS or a real device.

#### **dSPACE**

dSPACE [dsp] offers hardware and software for rapid control prototyping and HIL simulation. MATLAB®/Simulink® is used for high level modelling while dSPACE provides I/O hardware for hardware to simulation coupling and additional software for example for target code generation<sup>8</sup> from models. The dSPACE simulator hardware for HIL simulation is modular. In addition, I/O boards can be added. Complete solutions, for example for rapid control prototyping, are available. The automotive

<sup>&</sup>lt;sup>7</sup>PIL simulation is special kind of a HIL or a Software-in-the-Loop (SIL) simulation for complex embedded systems which consist of a plant part and a controller part. The control algorithm interacts with the model of the plant. It can be executed either on the real  $\mu$ C or on an ISS.

<sup>&</sup>lt;sup>8</sup>A target code generator is able to transform the an high-level description of an algorithm into source code (for example C-code) for a target system (normally a  $\mu$ C).

industry is one of the main dSPACE-customers. A typical dSpace solution is used for a comparison with the CHILS approach in chapter 5.

## Modelica/Dymola

Modelica® [mod] is an object-oriented modelling language for complex physical systems, containing mechanical, electrical, electronic, hydraulic, thermal, control and electric power or process-oriented subcomponents that allows homogeneous modelling. Modelica® is more suitable for mixed dynamic systems with different types of components than MATLAB®/Simulink®.

Dymola® is a commercial modelling and simulation environment for Modelica. Interfaces to MATLAB®/Simulink® exist, so models can be embedded as special block diagrams (S-functions) into Simulink.

Dymola® [dym]) offers the capability of HIL-simulation in combination with dSPACE, xPC Target<sup>TM</sup> or RT-LAB. The Modelica® language is translated into C-Code which is compiled for the simulation execution.

Because of the multi-domain single language capabilities Modelica®, the language has a fast growing community. HIL-simulations are implemented for example by the working group of Professor Dr.-Ing. Clemens Gühmann (*Hardware-in-the-Loop simulation of a hybrid electric vehicle using Modelica/Dymola* [WG06a], *Synchronizing a Modelica Real-Time Simulation Model with a Highly Dynamic Engine Test-Bench System* [WG06b]).

#### **National Instruments**

National Instruments offers a variation of HIL solutions based on the LabVIEW simulation environment [Lab09]. LabVIEW offers a graphical programming language to program and to control the I/O interfaces from the simulation to the "hardware-in-the-loop". LabVIEW can execute models of other simulation environments or it interfaces directly to MATLAB®/Simulink® for example. Various DAQ boards are provided including Field Programmable Gate Array (FPGA) boards.

#### **Visual Solutions**

Visual Solutions VisSim is, like Simulink®, a visual block diagram language for modelling and simulation of complex dynamic systems. Interfaces to MATLAB® are available. Simulink® blocks can be imported directly into VisSim. Identical to MathWorks<sup>TM</sup> solutions, it is possible to generate C-Code from the block model.

The VisSim Embedded Controls Developer provides an integrated solution for rapid control prototyping based on  $\mu$ Cs from Texas Instruments.

VisSim Real-TimePRO provides HIL-simulation capabilities. Analogue and digital I/O boards from different manufacturers are supported, as well as serial connections to programmable logic controllers or distributed control systems.

#### **ETAS**

ETAS [ETA] provides pre-configured HIL systems for example for power train control units. The PT-LABCAR [Anh06], one ETAS HIL solution, offers as I/O interfaces 300 signal pins and 50 additional high-current pins. The basic system is designed for testing ECUs that control 8-cylinder gasoline engines or 12-cylinder diesel engines. It can be extended for handling high-end applications, such as tests of ECUs that control 16-cylinder engines too.

## 2.2.3 Non-Commercial Hardware-in-the-Loop Solutions

Non-Commercial HIL solutions are mainly projects of universities. The general setup does not differ from the commercial solutions. A standard PC equipped with DAQ cards hosts the simulation. The DAQ cards establish the connection to the hardware. Also FPGAs are used as configurable I/Odevices ([VGB04a],[BMG05]).

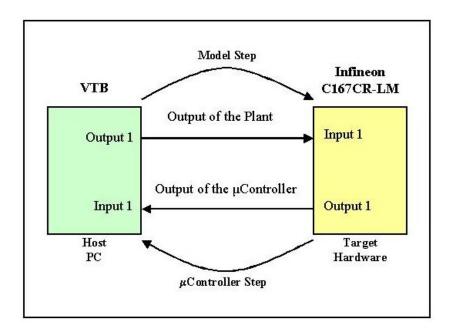

### University of South Carolina - Virtual Test Bed

The Virtual Test Bed (VTB) [vtb], developed by the Electrical Engineering department of the University of South Carolina, is a software for prototyping of large-scale, multi-technical dynamic systems. The VTB embeds models from different simulation environments into a unified simulation environment. The VTB models can be created in different ways. For instance, they can be imported from other simulation tools, such as MATLAB®/Simulink®, SPICE or ACSL. The modular VTB solver can be used with Windows, Linux and Mac OS-X. Different analogue and digital I/O boards from different manufactures are supported to build a HIL setup.

#### ETH Zürich - Generic Hardware-in-the-loop Framework

A generic HIL framework is designed by Marco Sanvido ([San02], [SCS02]). This framework adds new approaches in testing embedded systems based on temporal logic and fault generation.

#### University of Twente - Borderc project

In the context of the Borderc project (*Beyond the Ordinary: Design of Embedded Real-time Control*) HIL solutions were developed to support the design of embedded systems. The publications of Peter M. Visser, Marcel A. Groothuis and Jan F. Broenink present applications for embedded control systems ([VGB04a],[VGB04b]). 20-sim [20S] is used as the simulation environment. 20-sim is a modelling and simulation programme that can simulate the behaviour of dynamic systems, such as electrical, mechanical and hydraulic systems or any combination of these.

#### University of Karlsruhe - COMPASS

At the University of Karlsruhe a configurable modular rapid prototyping system called COMPASS has been developed for automotive systems ([BMG05], [Bie07]). The system uses FPGAs cards as versatile configurable I/O interfaces.

## 2.2.4 Coupling Concepts

For a general HIL simulation, there is only one possibility of designing it. A physical connection of each hardware interface is needed to capture signals and to stimulate the hardware. General HIL simulation does not only covers digital or analogue signals which are transmitted over electrical wires but also forces or heat. Let us think about a Damper-in-the-Loop simulation. The damper has to be stimulated with a real force and it produces an opposing force.

For a  $\mu$ C-in-the-Loop simulation this means that every input and output pin of the  $\mu$ C has to be connected to the simulation computer. Hundreds of connections are needed to do so. The advantage is that no special adaption on the side of the  $\mu$ C is needed. The disadvantages are the demands on the coupling hardware and the real time capability of the simulation. The last disadvantage can be overcome by controlling the  $\mu$ C clock system, if it is possible to do so. The DeskPOD<sup>TM</sup> from the SimPOD company [Sima] is a hardware solution which uses this concept. Later on the CHILS approach is compared with the DeskPOD<sup>TM</sup> in chapter 5 in section 5.5

Figure 2.5: Processor-in-the-Loop

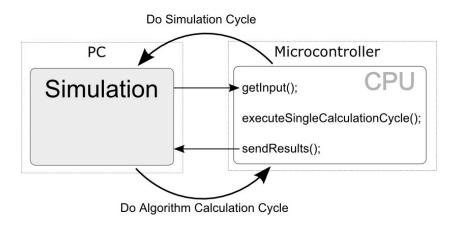

With  $\mu$ Cs as the "in-the-loop" hardware, there is another possibility for the simulation connection. If interfaces of the  $\mu$ C are stimulated from inside, the connection can be realized on a higher level of abstraction over a single physical connection. The only physical connection between hardware and simulation can for example be the debugger interface. The solution is very attractive because of the a low hardware effort for coupling. PIL solutions, based on evaluation boards, often use this

simple connection over general serial interfaces or the debugger interface. But a PIL approach does not use any peripherals<sup>9</sup> of the  $\mu$ Cs. The data exchange with the simulation is realized by bypass functions at the beginning and the end of a single control-cycle of the algorithm (see figure 2.5). The *Link for TASKING* [Lin09] solution from MathWorks<sup>TM</sup> mentioned above is a popular example. Further details on PIL solutions are described in chapter 9 in section 9.2. Vase Klandzevski [KM06] also describes the usage of a serialized pin interface and internal stimulation as preceding work of the current approach.

## 2.3 Additional Concepts