#### TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Technische Elektronik

# Variationen und ihre Kompensation in CMOS Digitalschaltungen

#### Thomas Baumann

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. techn. Josef A. Nossek

Prüfer der Dissertation:

- 1. Univ.-Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

- 2. Univ.-Prof. Dr.-Ing. Tobias G. Noll, Rheinisch-Westfälische Technische Hochschule Aachen

Die Dissertation wurde am 25.03.2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 14.09.2010 angenommen.

#### Danksagung

"Leider läßt sich eine wahrhafte Dankbarkeit mit Worten nicht ausdrücken."

(Johann Wolfgang von Goethe)

Obwohl ich J. W. von Goethe zustimme, möchte ich dennoch versuchen, meiner Dankbarkeit Ausdruck zu verleihen.

Ich danke meiner Doktormutter, Prof. Doris Schmitt-Landsiedel für die Betreuung meiner Industrie-Promotion und die warmherzige Aufnahme am Lehrstuhl für technische Elektronik. Herrn Prof. Noll danke ich für die Begutachtung meiner Arbeit.

Ein großer Dank geht an Dr. Matthias Schoebinger, Infineon Abteilungsleiter von Advanced Systems and Circuits (ASC). Ich freue mich sehr darüber, dass Sie mir die Möglichkeit gegeben haben, meine Arbeit im freundlichen Umfeld der ASC Kollegen durchzuführen.

Besonderer Dank gilt auch meinen Kollegen Dr. Jörg Berthold und Dr. Karl Hofmann, die mir stets für Diskussionen zur Verfügung standen und mit vielen fruchtbaren Gesprächen täglich zu meiner Motivation beigetragen haben.

Dr. Christian Pacha - mein Ansprechpartner und Gruppenleiter von ASC TOC - gilt in diesem Zusammenhang mein größter Dank. Lieber Christian, ich möchte mich für die zahlreichen Gespräche und Diskussionen bei Dir bedanken, die mich ermuntert haben, die Ergebnisse meiner Arbeit immer wieder kritisch zu hinterfragen. Ohne deine tägliche Motivation und die ehrliche und aufrichtige Art und Weise technische Probleme zu diskutieren, hätte ich nicht soviel gelernt, wie ich es in den letzten Jahren getan habe. Vielen Dank dafür!

Doch mein größter Dank gilt meinen Eltern, Helmut und Theresia Baumann. Ich danke Euch, dass Ihr meine Affinität zur Technik schon früh gefördert habt. Besonders dankbar bin ich auch für den Aufwand, den Ihr getrieben habt, damit ich schon zur Jugendzeit meinen Lieblingssport ausüben konnte. Auch heute noch ist dieser Sport das beste Mittel für mich um vom beruflichen Alltag abschalten zu können. Insbesondere in stressigen Zeiten konnte ich dabei wieder Kraft sammeln und neue Energien freisetzen.

Dank Euch konnte ich meine Schulausbildung und mein Studium frei von finanziellen Sorgen absolvieren. Dafür bin ich Euch sehr dankbar! Doch viel wichtiger war mir Euer Rückhalt, der mir in schweren Zeiten Kraft gab.

Liebes Schwesterherz auch Dir danke ich für immer offene Ohren, gute Gespräche und motivierende Worte. Ich bin froh, dass es Dich gibt.

Liebe Karin auch Dir gilt besonderer Dank! Danke für Dein Verständnis, dass viele Abende und Wochenenden vorwiegend mit Arbeit belegt waren, danke, dass Du immer ein offenes Ohr für mich hattest und danke fürs "Glücklichmachen" .

Zu guter Letzt noch ein Gruß an meine Oma! Gerne hätte ich dieses Ereignis noch mit Dir gefeiert. Leider blieb mir dieser Wunsch verwehrt. Aber ich bin mir sicher, Du freust Dich mit mir.

## Inhaltsverzeichnis

| 1 | Eini                     | nleitung |                                                                 |     |  |  |

|---|--------------------------|----------|-----------------------------------------------------------------|-----|--|--|

| 2 | Vorg                     | gehens   | weise zur abstraktionsebenenübergreifenden Variationsanalyse    | 17  |  |  |

| 3 | Vari                     | atione   | n in modernen sub-100nm low-power CMOS Technologien             | 21  |  |  |

|   | 3.1                      |          | liche und zeitliche Klassifizierung von Variationen             | 21  |  |  |

|   |                          | 3.1.1    | Prozessvariationen                                              |     |  |  |

|   |                          | 3.1.2    | Umgebungsvariationen                                            | 32  |  |  |

|   |                          | 3.1.3    | Alterungseffekte                                                |     |  |  |

|   |                          | 3.1.4    | Zeitliche Klassifizierung von Variationen                       | 37  |  |  |

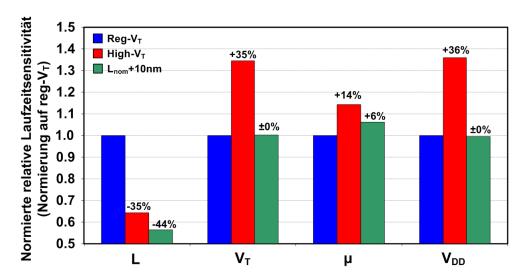

|   | 3.2                      | Sensit   | ivitätsanalyse und technologiebasierte Trendaussagen            |     |  |  |

|   |                          | 3.2.1    | Analyse der Laufzeitsensitivität                                | 39  |  |  |

|   |                          | 3.2.2    | Schwankungen bei fortschreitender Technologieskalierung         | 43  |  |  |

|   |                          | 3.2.3    | Schaltungstechnische Aspekte der Laufzeitsensitivität           | 49  |  |  |

| 4 | Mik                      | roproze  | essormodell zur Bestimmung technologischer und mikroarchitek-   | _   |  |  |

| - | tonischer Einflussgrößen |          |                                                                 |     |  |  |

|   | 4.1                      |          | uranalyse eines ARM926 Mikroprozessor Produktdesigns            | 53  |  |  |

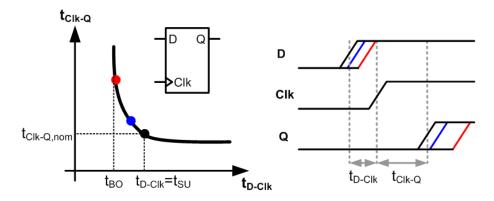

|   |                          | 4.1.1    | Setup-Zeit kritische Pfade                                      |     |  |  |

|   |                          |          | Beschaffenheit des Logikteils                                   | 54  |  |  |

|   |                          |          | Beschaffenheit des Taktbaums                                    |     |  |  |

|   |                          | 4.1.2    | Hold-Zeit kritische Pfade                                       | 63  |  |  |

|   |                          |          | Beschaffenheit des Logikteils                                   |     |  |  |

|   |                          |          | Beschaffenheit des Taktbaums                                    | 65  |  |  |

|   | 4.2                      | Aufba    | u des Mikroprozessormodells                                     | 66  |  |  |

|   |                          | 4.2.1    | Modellierung der Registeranzahl                                 | 67  |  |  |

|   |                          | 4.2.2    | Modellierung des Logikblocks                                    |     |  |  |

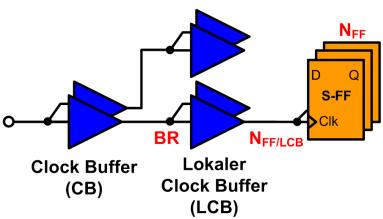

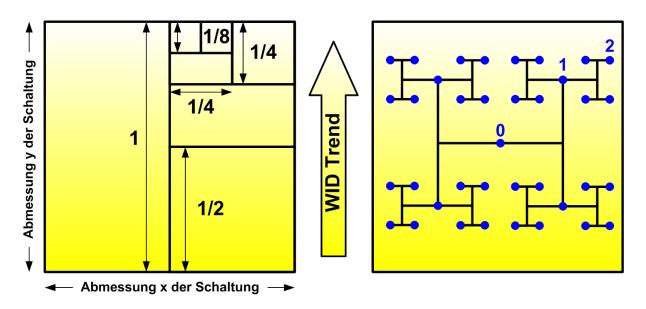

|   |                          | 4.2.3    | Modellierung des Taktverteilungsnetzes                          | 76  |  |  |

|   |                          | 4.2.4    | Auswirkungen auf das Timing Verhalten                           | 82  |  |  |

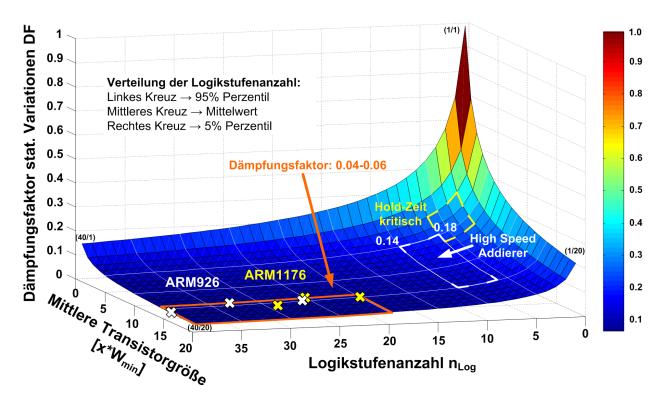

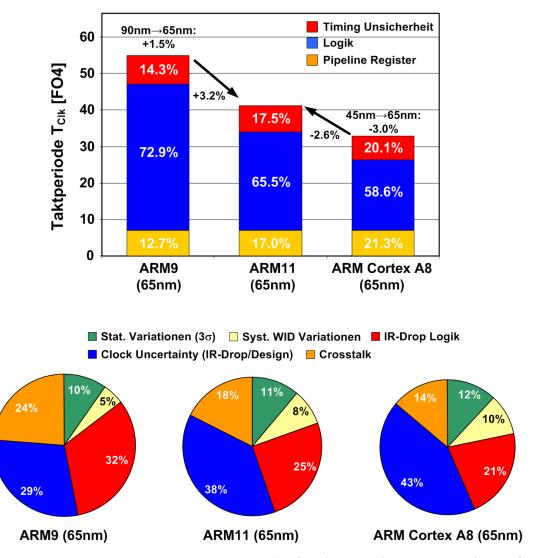

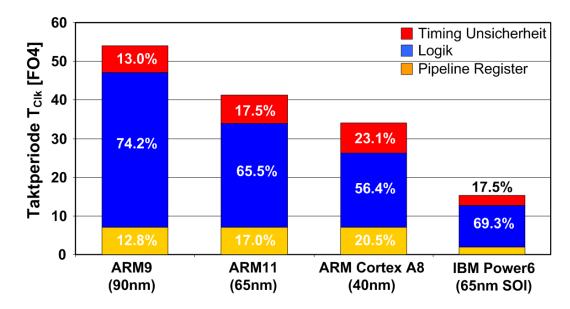

|   | 4.3                      | Ergeb    | nisse für die ARM Mikroprozessor-Familie                        | 83  |  |  |

|   | 4.4                      | Bemer    | kungen zu den Ergebnissen                                       | 91  |  |  |

| 5 | Тор                      | ologiea  | analysen und Robustheit                                         | 95  |  |  |

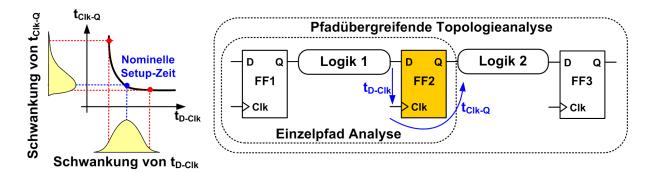

|   | 5.1                      | _        | bergreifende Topologieanalyse                                   | 96  |  |  |

|   | 5.2                      |          |                                                                 |     |  |  |

|   |                          | 5.2.1    | Topologische Korrelationen in kritischen Pfaden                 |     |  |  |

|   |                          | 5.2.2    | Struktur- und topologieabhängige Bewertung der Schaltungssensi- |     |  |  |

|   |                          |          | tivität                                                         | 111 |  |  |

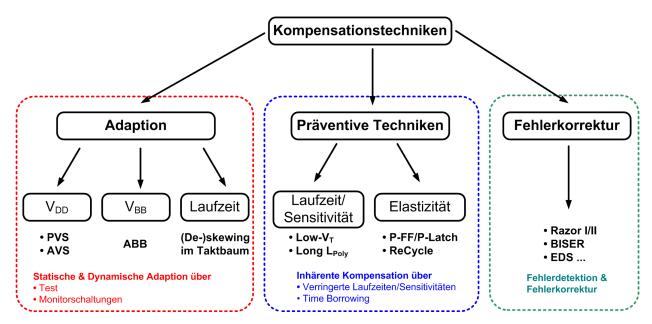

| 6  | Sch    | Schaltungstechnische Ansätze zur Kompensation von Laufzeitschwankun- |                                                                        |       |  |  |

|----|--------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------|--|--|

|    | gen    |                                                                      |                                                                        | 117   |  |  |

|    | 6.1    | Globa                                                                | le Post-Fabrikation Adaptionstechniken                                 | . 118 |  |  |

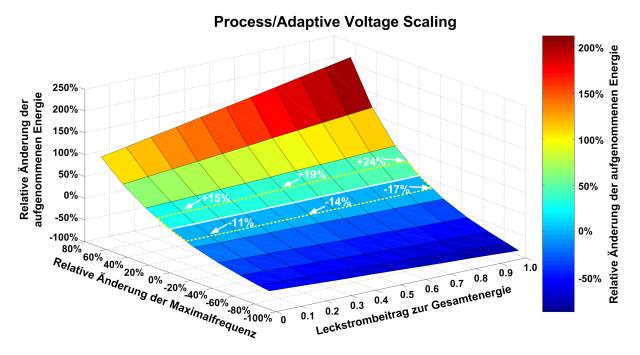

|    |        | 6.1.1                                                                | Process und Adaptive Voltage Scaling                                   | . 118 |  |  |

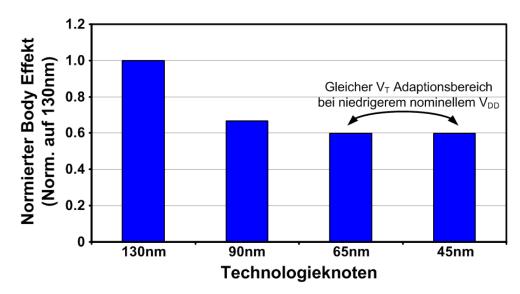

|    |        | 6.1.2                                                                | Adaptive Body Biasing                                                  | . 122 |  |  |

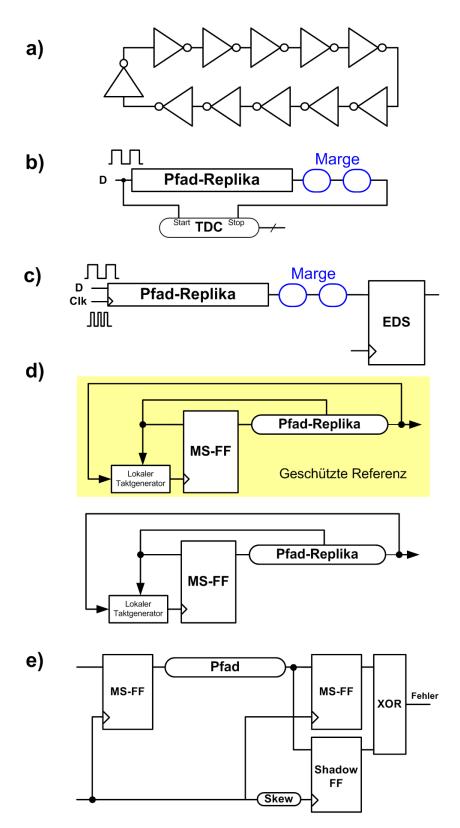

|    |        | 6.1.3                                                                | On-Chip Monitorschaltungen                                             | . 129 |  |  |

|    |        | 6.1.4                                                                | Vergleich der Techniken                                                | . 133 |  |  |

|    | 6.2    | Präver                                                               | ntive Kompensationstechniken                                           | . 134 |  |  |

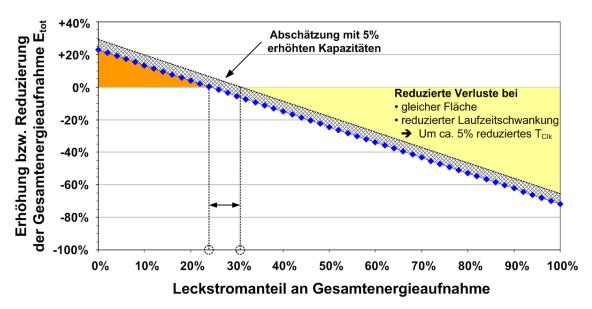

|    |        | 6.2.1                                                                | Long- $L_{Poly}$ Design                                                | . 134 |  |  |

|    |        | 6.2.2                                                                | Selektiver Einsatz von low- $V_T$ Zellen im Taktbaum                   | . 137 |  |  |

|    |        | 6.2.3                                                                | Selektiver Einsatz von low- $V_T$ Zellen in geschwindigkeitskritischer | ı     |  |  |

|    |        |                                                                      | Pfaden                                                                 |       |  |  |

|    |        | 6.2.4                                                                | Einsatz von gepulsten Flip Flops (P-FF) / Latches (P-L)                | . 145 |  |  |

|    |        |                                                                      | Selektiver Einsatz von P-FFs in geschwindigkeitskritischen Pfaden      | . 146 |  |  |

|    |        |                                                                      | Globaler Einsatz von gepulsten Latches (Pulsed Latch Design)           | . 154 |  |  |

|    |        | 6.2.5                                                                | Einfluss der Techniken auf die Schaltungssensitivität                  | . 161 |  |  |

|    |        | 6.2.6                                                                | Validierung des Sensitivitätsfaktors als Robustheitsmaß                | . 164 |  |  |

| 7  | Zus    | ammer                                                                | nfassung und Schlussfolgerung                                          | 171   |  |  |

|    | 7.1    |                                                                      | nmenfassung                                                            | . 171 |  |  |

|    | 7.2    |                                                                      | sfolgerung                                                             |       |  |  |

| Pι | ıblika | tionsli                                                              | ste                                                                    | 193   |  |  |

| Αŀ | bildı  | ungsve                                                               | rzeichnis                                                              | 194   |  |  |

| Τź | belle  | nverze                                                               | ichnis                                                                 | 200   |  |  |

## Abkürzungen und Formelzeichen

$\alpha_{dyn}$  Dynamisches  $\alpha$ zur Modellierung des spannungsabhängigen Laufzeitverhaltens

$\alpha_{FF}$  Exponent zur Modellierung des super-linearen Anstiegs der Register/Flip Flop

Anzahl mit zunehmender Pipelinetiefe

$\alpha_{Schalt}$  Schaltaktivität

$A_{VT0}$  Mismatch-Konstante der Transistoreinsatzspannung

β Glitch-bedingte Schaltaktivität

BEOL Back-End Of Line, d.h. Prozessierung der Verdrahtung

BR Branching im Taktbaum, d.h. Aufspaltung eines Netzes im Taktbaum  $BR_{Log}$  Branching in der Logik, d.h. Aufspalung eines Netzes im Logikpfad Konstante in der gatterspektrenabhängigen Gewichtung des Schaltungs-

sensitivitätsfaktors

$C_{eff}$  Effektive Lastkapazität

$C_K$  Koppelkapazität zwischen benachbarten Leitungen

$C_{K_{eff}}$  Effektive, d.h. schaltende Koppelkapazität benachbarter Leitungen

$C_{Ltq}$  Leitungskapazität

$C_{MOS}$  Eingangskapazität von MOS Transistoren

$C_{Off}$  Offset Kapazität zur Berechnung zellinterner Laufzeitbeiträge

$C_{ox}$  Oxidkapazität

$C_{stat}$  Statische Haltekapazität bei der Crosstalkberechnung

D2D Die-to-Die Variationen

DF Dämpfungsfaktor statistischer

DIBL Drain Inducded Barrier Lowering

D-TB Dynamisches Time-Borrowing

DUT Device under Test

$E_{FF}$  Empfangendes Flip Flop am Ende eines Logikpfades

$E_{tot}$  Gesamtenergie

$\epsilon_{ox}$  Dielektrizitätskonstante des Gateoxids

F Flächenfaktor ( $\mu P$ -Modell)

$f_{Clk}$  Taktfrequenz  $\phi_F$  Fermipotential

$F_{rel}^{Clk}$  Relative Laufzeitänderung eines Taktpfads aufgrund von IR-Drop  $F_{rel}^{Log}$  Relative Laufzeitänderung eines Logikpfads aufgrund von IR-Drop FEOL Front-End Of Line, d.h. Prozessierung aktiver Schaltelemente

$\gamma_{V_T}$  Temperaturkoeffizient der Einsatzspannung

H(x) Häufigkeitsverteilung des Parameters x

$H_{Ltq}$  Vertikaler Leitungsabstand

$I_D$  Transistor Drainstrom (allgemein)

$I_{eff}$  Effektiver Transistorstrom

$I_H$  Transistor Drainstrom bei  $V_{GS} = V_{DD} \& V_{DS} = V_{DD}/2$  $I_L$  Transistor Drainstrom bei  $V_{GS} = V_{DD}/2 \& V_{DS} = V_{DD}$

$I_{leak}$  Leckstrom (allgemein)

$I_{lin}$  Transistror Drainstrom bei  $V_{GS} = V_{DD} \& V_{DS} = 50 mV$

$I_{sc}$  Kurzschlussstrom eines CMOS Gatters während des Schaltvorgangs

$k_{\mu}$  Temperaturkoeffizient der Beweglichkeit  $\kappa_{Top}$  Topologischer Korrelations Faktor (TKF)

L Transistor-Gatelänge (allgemein)

L2L Los-zu-Los Variationen

$L_{eff}$  Effektive Transistor-Gatelänge

$\lambda_{XT}^{WC}$  Skalierungsfaktor des von der STA angegebenen Crosstalkbeitrags  $\sigma_{L_{eff}}$  Standardabweichung der statistischen Gatelängenschwankung

$\delta_{L_{eff}}$  Lokale statistische Gatelängenschwankung  $\Delta L_{eff,glo}$  Globale systematische Gatelängenschwankung Lokale systematische Gatelängenschwankung

$L_{Ltq}$  Leitungslänge

$L_{nom}$  Nominelle Transistor-Gatelänge  $\mu$  Ladungsträgerbeweglichkeit

$\sigma_{\mu}$  Standardabweichung der statistischen Beweglichkeitsschwankung

$\delta_{\mu}$  Lokale statistische Beweglichkeitsschwankung  $\Delta \mu_{glo}$  Globale systematische Beweglichkeitsschwankung  $\Delta \mu_{lok}$  Lokale systematische Beweglichkeitsschwankung

$\mu_{nom}$  Nominelle Ladungsträgerbeweglichkeit

$N_{\sigma}$  Anzahl der zu berücksichtigenden Standardabweichungen der stat. Variationen

$N_{Aqqr}$  Aggressoranzahl

$n_{Arch}$  Architekturbedingte zusätzliche Logikstufenanzahl

$n_{CB}$  Anzahl von Buffer-Zellen im Taktverteilungsnetz (Clock Buffer)

$N_{Dot}$  Dotierstoffkonzentration

$N_{FF}$  Flip Flop Anzahl

$N_{FF/LCB}$  Anzahl der von einem LCB versorgten Flip Flop Zellen

$N_{G/P}$  Mittlere Anzahl von Gattern pro Pfad

$n_{Gatter}$  Gatteranzahl

$N_{Gatter}$  Gesamtgatteranzahl einer Schaltung

$n_{Log}$  Logiktiefe eines Pfades

$n_{Pfade}$  Pfadanzahl

$N_{Pipeline}$  Pipelinestufenanzahl  $R_{Ltq}$  Leitungswiderstand

$\rho_{Ltq}$  Spezifischer Widerstand des Leitungsmaterials

$R_{Tr}$  Effektiver Transistorwiderstand

RSAT Relative Signal Arrival Time, d.h. zeitlicher Abstand zweier Signale

$s_1, s_2$  Schaltungssensitivität bzw. Schaltungssensitivitätsfaktor

$S_{C_k}$  Skalierungsfaktor der lateralen Koppelkapazität zweier Leitungen

$S_i$  Laufzeitsensitivität gegenüber Einflussgröße i

$S_{i,rel}$  Relative Laufzeitsensitivität gegenüber Einflussgröße i

$S_{Ltq}$  Horizontaler Leitungsabstand

S-FF Sendendes Flip Flop am Anfang eines Logikpfades

$\sigma_{HD-Pfad}$  Statistische Laufzeitschwankung von  $t_{Clk-Q} + t_{Log} + t_{HD}$

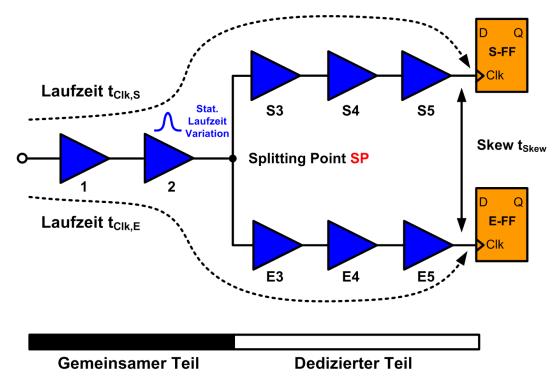

SP Splitting Point im Taktbaum (Zählung beginnend von der Takteinspeisung)

SSTA Statistische Statische Timing Analyse

STA Statische Timing Analyse S-TB Statisches Time-Borrowing

T Temperatur

TKF Topologischer Korrelations-Faktor  $t_{CB}$  Laufzeit einer Clock Buffer Zelle

$\sigma_{t_{CB},rel}$  Relative statistische Laufzeitschwankung einer Clock Buffer Zelle

$T_{Clk}$  Taktperiode

$t_{Clk,E}$  Laufzeit des Taktpfades zum empfangenden Flip Flop  $t_{Clk,S}$  Laufzeit des Taktpfades zum sendenden Flip Flop

$t_{Clk-Q}$  Clock-Q Laufzeit von Flip Flop/Latch

$t_{Comb}$  Laufzeit der Kombinatorik  $(t_{Clk-Q}, t_{SU}, t_{Log})$   $t_{Comb}^{IR}$  IR-Drop induzierte Laufzeitschwankung

$\Delta t_{Comb}^{IR}$  Korrekturterm bei gleichzeitiger Berücksichtigung von Clock Jitter und

IR-Drop induzierter Laufzeitschwankung im Mikroprozessormodell

$t_d$  Laufzeit (allgemein)

$\sigma_{t_{d,rel}}(k)$  Statistische Laufzeitschwankung aufgrund von Strom-Mismatch

$t_d^{nom}$  Nominelle Laufzeit

$t_{D-Clk}$  Data-Clk Laufzeit von Flip Flop/Latch  $t_{D-Q}$  Data-Q Laufzeit von Flip Flop/Latch

$t_{Gatter}$  Gatterlaufzeit

$\sigma_{t_{Gatter}}$  Statistische Laufzeitschwankung eines Einzelgatters (allgemein)

$T_{HD}$  Pfad Timing von Hold-Zeit kritischen Pfaden

$t_{HD}$  Hold-Zeit

$t_{Jitter}$  Clock Jitter induzierte Laufzeitschwankung  $\Delta T_{krit}$  Kritischer Timing Bereich innerhalb  $\Delta T_{Var}$

$t_{Log}$  Logiklaufzeit  $T_{Ltg}$  Leitungshöhe  $t_{ox}$  Gateoxiddicke  $t_{Pfad}$  Pfadlaufzeit

$T_{Pfad}$  Gesamtlaufzeit eines Pfades

$\sigma_{t_{Pfad}}$  Statistische Laufzeitschwankung eines Pfades

$t_{Pfad}^{max}$  Maximale Pfadlaufzeit  $t_{Pipeline}$  Laufzeit einer Pipelinestufe  $t_{RC}$  RC Laufzeit der Leitungen

$t_{RW}$  Laufzeitanteil des Leitungswiderstandes

$t_{Sig}^{Agr}$  Signalflanke des Aggressornetzes

$t_{Skew}$  Zeitlicher Unterschied im Taktverteilungsnetz (Clock Skew)

$t_{Skew}^{Design}$  Clock Skew aufgrund von Designunsicherheiten

$t_{Skew}^{IR}$  IR-Drop induzierter Clock Skew in Hold-Zeit kritischen Pfaden  $t_{Skew}^{WID}$  Clock Skew aufgrund systematischer WID Prozessvariationen

$T_{SU}$  Pfad Timing von Setup-Zeit kritischen Pfaden

$t_{SU}$  Setup-Zeit

$\Delta T_{Var}$  Zeitliche Spanne der Laufzeitvariation

$t_{Var}^{HD}$  WID Timing Unsicherheit Hold-Zeit kritischer Pfade (allgemein)  $t_{Var}^{SU}$  WID Timing Unsicherheit Setup-Zeit kritischer Pfade (allgemein)

$\Delta t_{WID,rel}$  Systematische relative WID Laufzeitschwankung

$t_{XT}$  Crosstalk induzierte Laufzeit

$\Delta t_{XT}^{WC}$  Worst-case Crosstalk-Beitrag eines Pfades der von der STA berechnet wird

TB Time-Borrowing

$V_{DD}$  Versorgungsspannung

$\Delta V_{DD,glo}$  Globale systematische Versorgungsspannungsschwankung  $\Delta V_{DD,lok}$  Lokale systematische Versorgungsspannungsschwankung

$V_{DD,nom}$  Nominelle Versorgungsspannung

$V_{DIBL}$  Einsatzspannungsabsenkung durch DIBL

$V_{DS}$  Drain-Source Spannung eines MOS-Transistors  $V_{GS}$  Gate-Source Spannung eines MOS-Transistors

$V_T$  Transistoreinsatzspannung

$\sigma_{V_T}$  Standardabweichung der statistischen Einsatzspannungsschwankung

$\delta_{V_T}$  Lokale statistische Einsatzspannungsschwankung  $\Delta V_{T,glo}$  Globale systematische Einsatzspannungsschwankung Lokale systematische Einsatzspannungsschwankung

$V_{T,nom}$  Nominelle Transistoreinsatzspannung  $V_{T_{eff}}$  Effektive Transistoreinsatzspannung

$V_{T_{sat}}$  Einsatzspannung des Transistors im Sättigungsbereich

W Transistorweite

$w(t_d)$  Pfad Timing abhängiger Gewichtungsfaktor des Gatterspektrums

bei Bestimmung der Schaltungssensitivität

$W_{Lta}$  Leitungsweite

$W_{min}$  Minimale Transistorweite einer Standardzellenbibliothek

W2W Wafer-zu-Wafer Variation

WID Within-Die Variation (Variation innerhalb eines Dies/Chips)

$X_{Schalt}$  Mikroarchitekturabhängiger Gewichtungsfaktor des Crosstalk-indu-

zierten Laufzeitbeitrags

$Z_{Log}$  Vorfaktor zur Berücksichtigung der stärkeren Spannungsabhängigkeit von Logik- gegenüber Taktpfaden

## 1 Einleitung

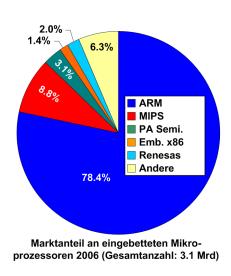

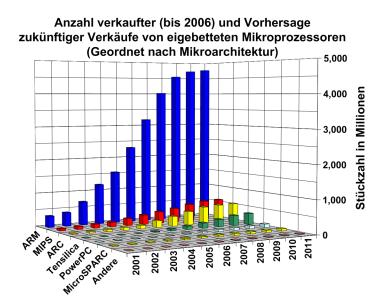

Die Reduzierung der Energieaufnahme ist wesentlicher Faktor der fortschreitenden CMOS Technologieskalierung. Doch neben der Absenkung der Versorgungsspannung wird beim Übergang zu einer neuen Technologiegeneration auch die für die Schaltung benötigte Fläche deutlich reduziert. Dieser Flächengewinn ist Voraussetzung, um zusätzliche Funktionalität wie z.B. superskalare und Multi-Core Mikroprozessoren, Multimedia Erweiterungen etc. kosteneffizient implementieren zu können. Insbesondere mobile Anwendungen wie z.B. Mobiltelefone und Handheld PCs erfordern eine stete Reduzierung der aufgenommen Energie, um die Batterielaufzeiten zu erhöhen, während die Geschwindigkeitsanforderungen aufgrund neuer Standards wie z.B. HSxPA weiter ansteigen. Deshalb werden vermehrt Schaltungsblöcke verwendet, die für dedizierte Anwendungen optimiert sind (Hardware-Beschleuniger). All diese Veränderungen führen zu immer komplexeren, heterogenen Systemen [1].

Zusätzlich erhöht sich mit fortschreitender Technologieskalierung und der einhergehenden Absenkung der Versorgungsspannung unter 1V der Einfluss von prozess- und betriebsbedingten Variationen auf die Geschwindigkeit und Energieaufnahme von Digitalschaltungen. Zusammen mit der steigenden Schaltungskomplexität erschweren die erhöhten Laufzeitsensitivitäten den Entwurf von Digitalschaltungen in variationsbehafteter Umgebung.

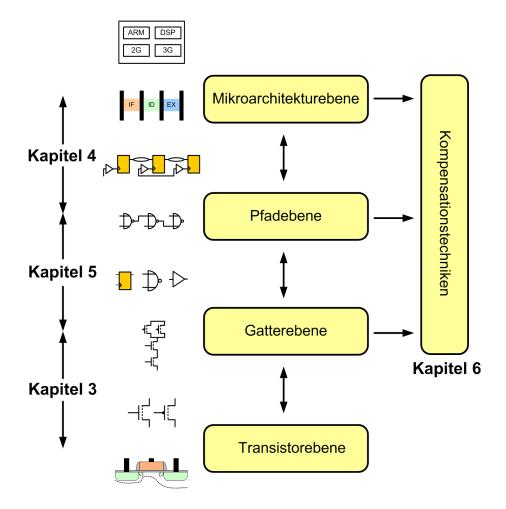

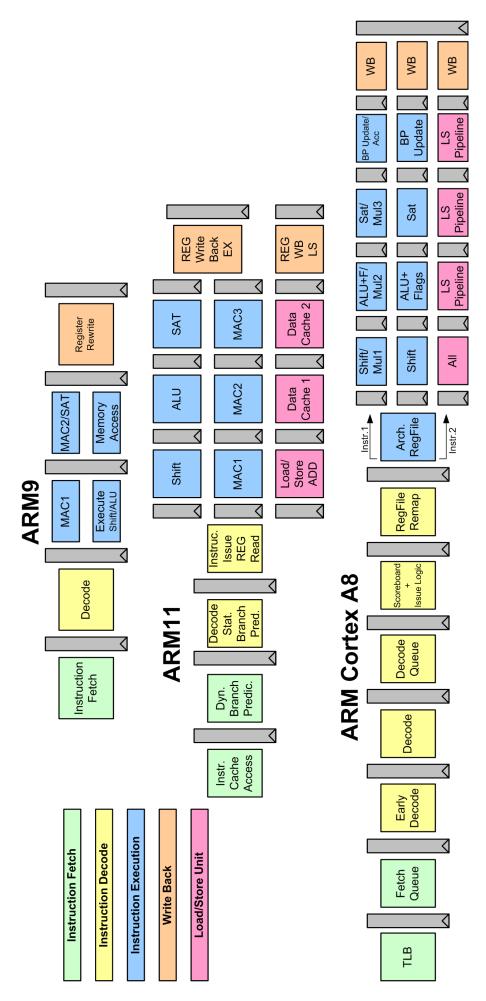

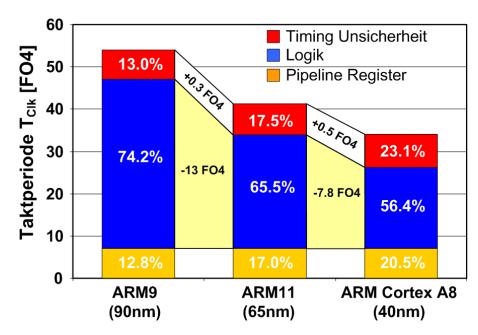

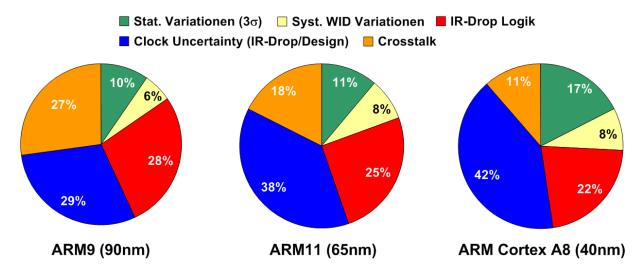

Daher behandelt diese Arbeit den Einfluss von Prozess- und Umgebungsvariationen auf die Laufzeitschwankung in digitalen sub-100nm CMOS Logikschaltungen. Der Schwerpunkt der Arbeit liegt dabei auf der Analyse eingebetteter Mikroprozessoren in lowpower CMOS Technologien. Dazu wird ein auf alle Digitalschaltungen verallgemeinerbarer Ansatz zur Identifikation, Klassifizierung, Quantifizierung und Bewertung von sensitiven Schaltungsstrukturen sowie der Quantifizierung der einzelnen Variationsbeiträge zur Laufzeitschwankung erarbeitet. Die einzelnen Variationseffekte werden in dieser Arbeit nicht isoliert behandelt, d.h. bei der Bewertung der Effekte werden die Interaktion und Randbedingungen der verschiedenen Effekte sowie der im Schaltungsentwurf durchlaufenen Abstraktionsebenen berücksichtigt (siehe Bild 1.1). Die vorgenommenen Untersuchungen beschränken sich auf den digitalen Logikteil der jeweiligen Mikroprozessoren. Cache- und on-chip Kommunikationsstrukturen werden nicht behandelt, da der Einfluss von Variationen auf diese Schaltungsteile im Gegensatz zu Mikroprozessorkerne bereits ausführlich untersucht wurden [2, 3, 4, 5, 6, 7]. Unter Berücksichtigung der gewonnenen Kenntnisse werden Kosten und Nutzen bekannter schaltungstechnischer Maßnahmen und daraus abgeleitete Erweiterungen zur Kompensation von Laufzeitschwankungen in Semi-Custom CMOS Digitalschaltungen bestimmt. Zur Bewertung der Robustheit einer Schaltung gegenüber Within-Die Prozess-, und on-chip Umgebungsvariationen erfolgt die erstmalige Definition mehrerer Kenngrößen, die als Metrik für die Verwundbarkeit einer Schaltung dienen. Diese Kenngrößen werden auch zur Bewertung der angewandten Kompensationstechniken verwendet.

Bild 1.1: Gliederung der Arbeit nach verschiedenen Abstraktionsebenen.

Kapitel 2 beschreibt die entwickelte Vorgehensweise zur Bewertung des Einflusses von Variationen auf die Geschwindigkeit einer getakteten Digitalschaltung. Dabei wird das Zusammenspiel der in Kapitel 3, 4, 5 und 6 erarbeiteten Erkenntnisse hervorgehoben und die verwendeten Simulatoren bzw. Tools aufgeführt.

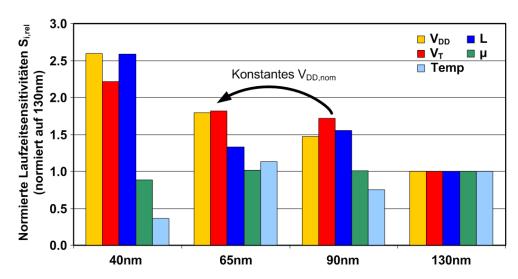

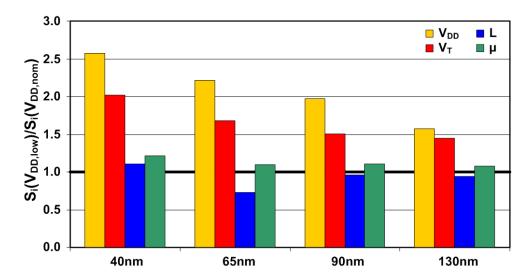

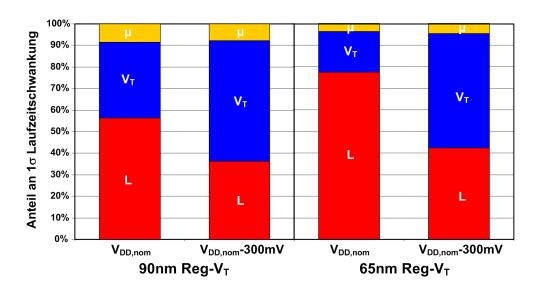

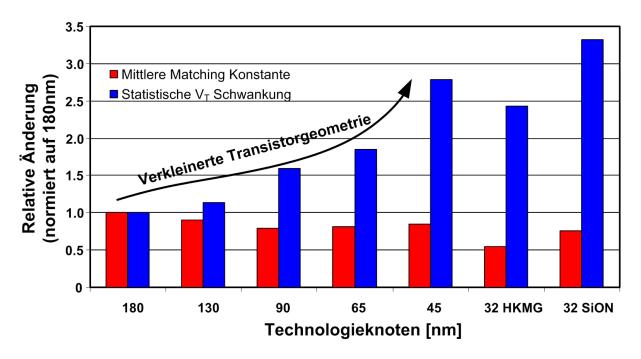

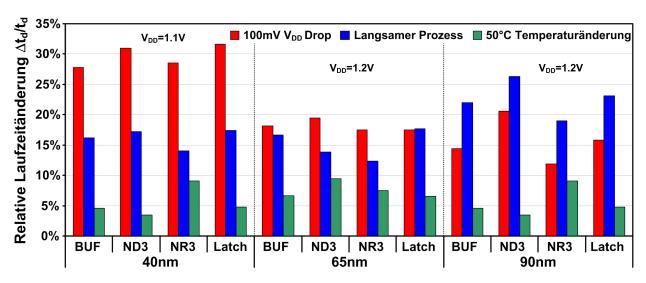

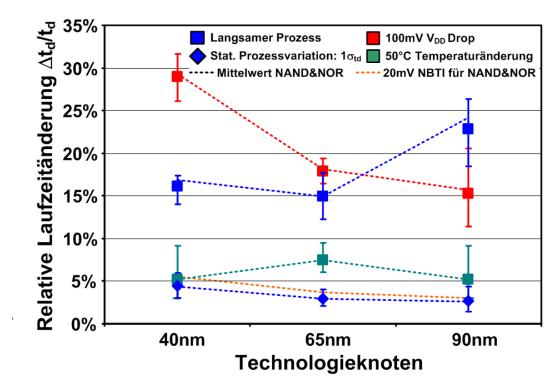

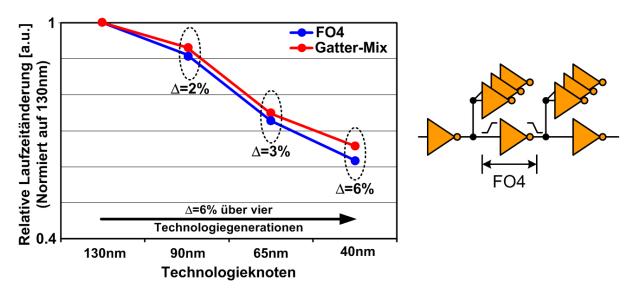

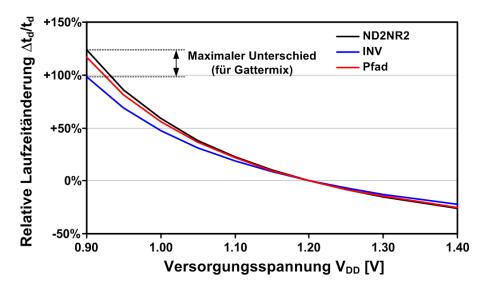

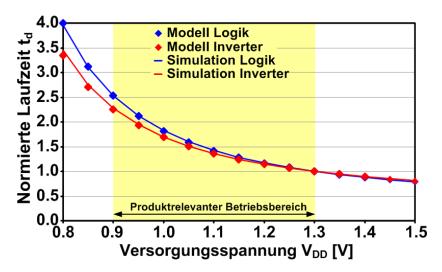

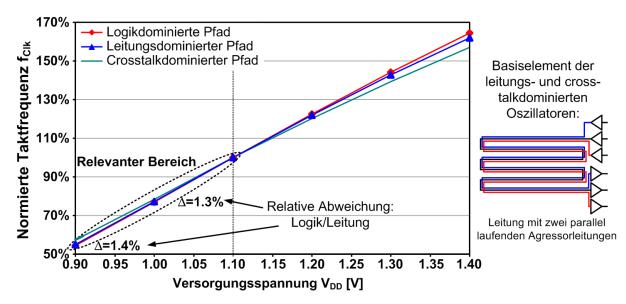

In Kapitel 3 werden alle relevanten Variationsquellen nach ihrem Auftreten klassifiziert und ihr Einfluss auf die Laufzeitschwankung analysiert. Dazu werden die physikalischen Einflussgrößen betrachtet und deren Beitrag zur Laufzeitschwankung quantifiziert. Um technologische Trendaussagen treffen zu können, werden die Laufzeitsensitivitäten von 130nm bis 40nm CMOS Technologien gegenüber den wichtigsten Variationsquellen untersucht und verglichen. Ergänzend werden auch die für low-power Schaltungen charakteristischen wechselnden Betriebsbereiche (Dynamic Voltage Scaling) berücksichtigt.

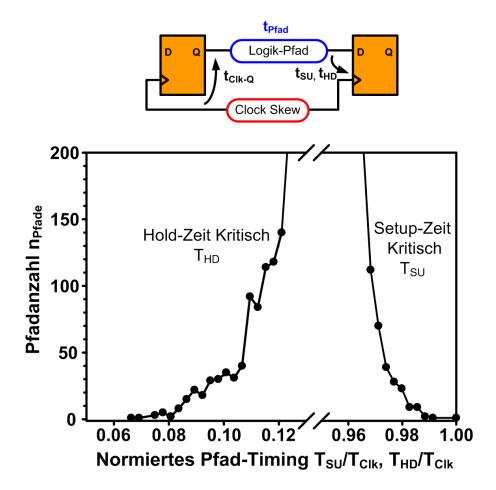

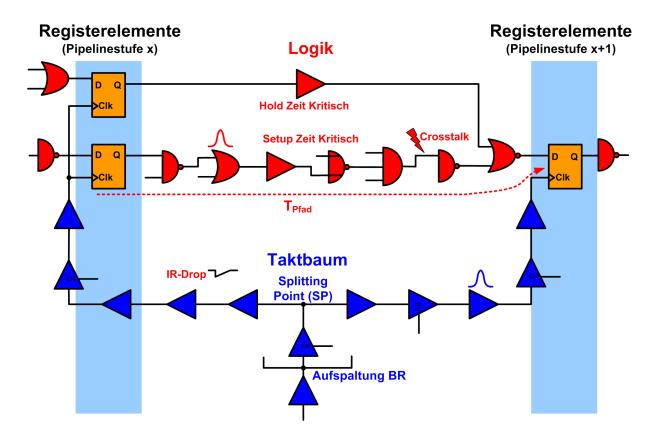

Kapitel 4 beinhaltet eine detaillierte strukturelle Analyse der kritischen Strukturen eines ARM926 Produktdesigns in 90nm low-power CMOS Technologie. Die Untersuchung des - in der Praxis relevantesten - Vertreters eines fünfstufigen RISC Prozessors ermöglicht die repräsentative Analyse struktureller und topologischer Eigenschaften wie z.B. Abfolge kritischer Pfade, die Aufspaltung im Taktverteilungsnetz etc. sowie der einzelnen Laufzeitbeiträge. Die Analyse erfolgt unter der Berücksichtigung von Randbedingungen und

Designkriterien eines state-of-the-art Design Flows, der alle Anforderungen an ein konkurrenzfähiges low-power Produktdesign erfüllt.

Auf Basis der strukturellen Analyse wird ein Mikroprozessormodell vorgestellt, das für die Abschätzung der einzelnen Laufzeitbeiträge sowohl technologische als auch strukturelle, topologische und mikroarchitektonische Aspekte berücksichtigt. Der wesentliche Kern des Mikroprozessormodells beruht auf der Beschreibung von Pipelinestrukturen mittels eines generischen 'kritischen Pfad' Modells, das neben Register zu Register Pfaden auch die Registerelemente (Flip Flops) und das Taktverteilungsnetz beinhaltet. Aufgrund des generischen Charakters ist das hier vorgestellte Modell auf beliebige getaktete Digitalschaltungen anwendbar. Ziel des Modells ist die Quantifizierung aller strukturabhängiger Beiträge von WID Prozess- und on-chip Umgebungsvariationen zur Laufzeitschwankung und die Bewertung von schaltungstechnischen Maßnahmen zur Kompensation von variationsbedingten Einflüssen.

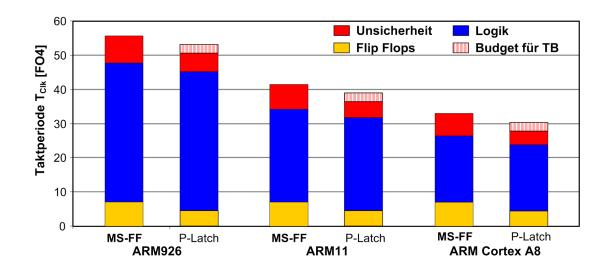

Um den Einfluss von tieferem Pipelining auf das Laufzeitverhalten in variationsbehafteter Umgebung zu zeigen, werden auf Basis des Mikroprozessormodells stellvertretend für alle RISC Prozessoren der ARM926, ARM1176 und ARM Cortex A8 der ARM Mikroprozessorfamilie analysiert.

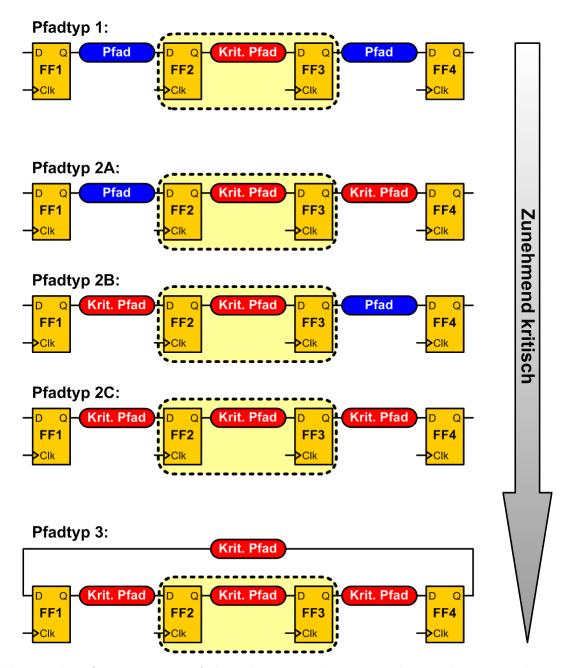

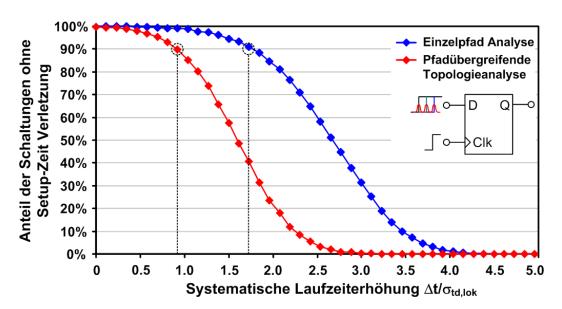

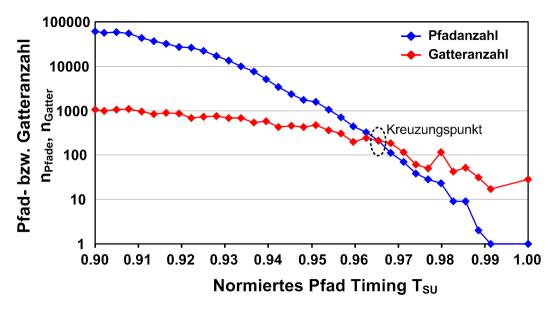

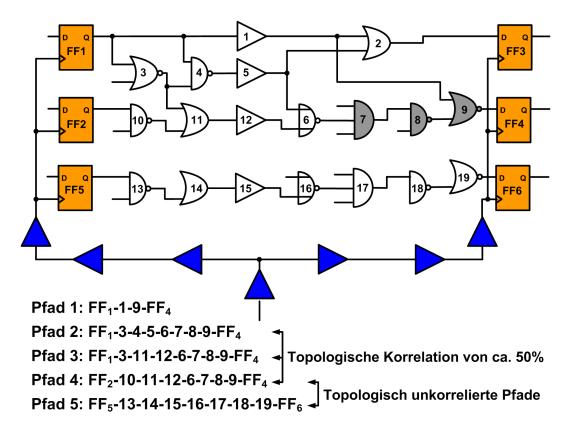

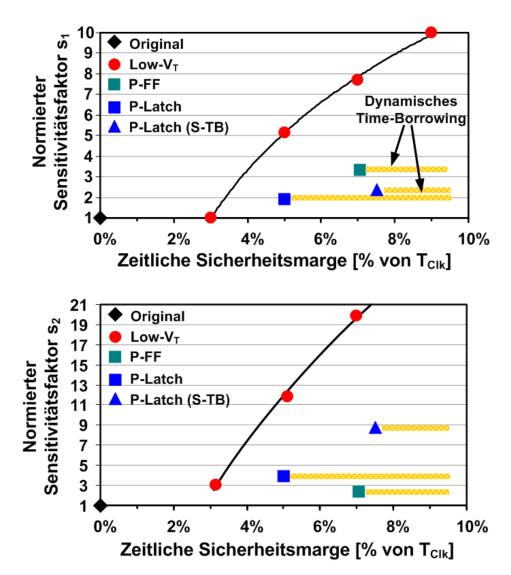

Kapitel 5 behandelt die Beschreibung und Quantifizierung des Einflusses schaltungsspezifischer Eigenschaften auf die Sensitivität einer Schaltung gegenüber Variationen. Zum einen wird die Auswirkung verschiedener Pfadtopologien auf das Laufzeitverhalten einer Schaltung analysiert. Die Unterscheidung der einzelnen Topologien hinsichtlich ihres Einflusses auf die Funktionalität der Schaltung erfolgt auf Basis neu definierter Pfadtopologien. Zum anderen wird erstmals der Einfluss von Pfad- bzw. Gatterspektrum und Pipeline-interner topologischer Korrelationen auf das Laufzeitverhalten digitaler Schaltungen untersucht. Mit der Definition des topologischen Korrelationsfaktors wird die Verflechtung der Gatter in geschwindigkeitskritischen Strukturen und somit der Einfluss lokaler Variationen auf die Gesamtschaltung beschrieben. Aus der Analyse der 'kritischen Hardware' erfolgen zwei Vorschläge zur Definition der Schaltungssensitivität gegenüber Variationen.

In Kapitel 6 werden globale Adaptionstechniken und präventive Designtechniken zur Kompensation bzw. Vermeidung variationsbedingter Laufzeitschwankungen bewertet. Als präventive Kompensationstechniken von Within-Die (WID) Laufzeitschwankungen, d.h. die Berücksichtigung von WID Laufzeitvariationen während des Schaltungsentwurfs, werden der selektive Einsatz von low- $V_T$  Gattern und gepulsten Flip Flops in geschwindigkeitskritischen Pfaden sowie die globale Ersetzung der Standard Master-Slave Flip Flops durch gepulste Latches und Pulsgenerator diskutiert. Die Evaluation von Kosten und Nutzen erfolgt auf Basis der in Kapitel 4 erarbeiteten Erkenntnisse. Zur Bewertung der einzelnen präventiven Maßnahmen werden neben den herkömmlichen Größen wie Geschwindigkeit, Leistungsaufnahme und Flächenbedarf die in Kapitel 5 definierten Bewertungskenngrößen für die Robustheit einer Schaltung verwendet.

Zur Reduzierung der Laufzeitsensitivitäten findet eine Untersuchung des globalen Einsatzes von Long- $L_{Poly}$  Gattern und des selektiven Einsatzes von low- $V_T$  Gattern im Taktverteilungsnetz statt.

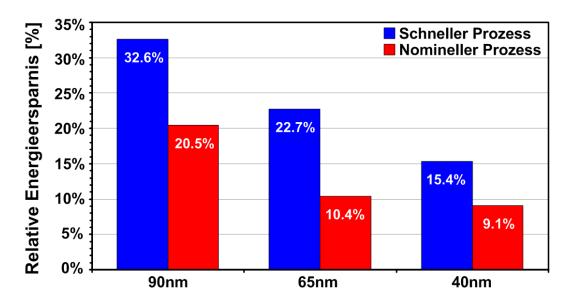

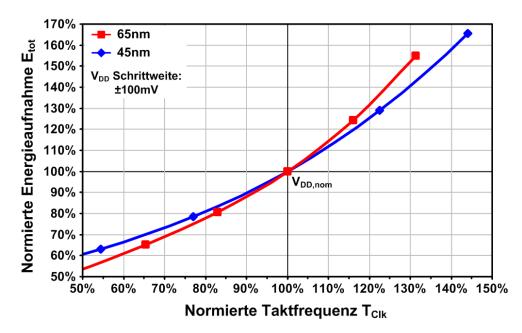

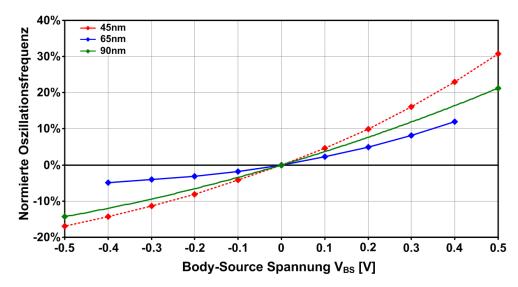

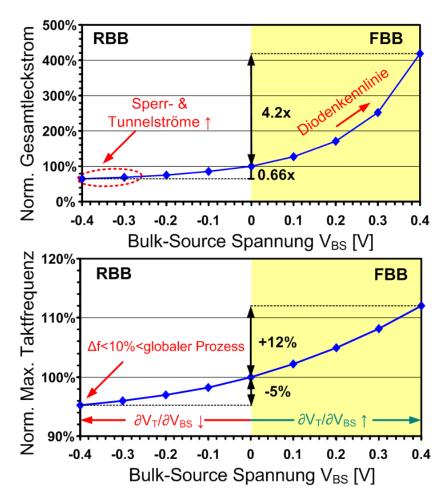

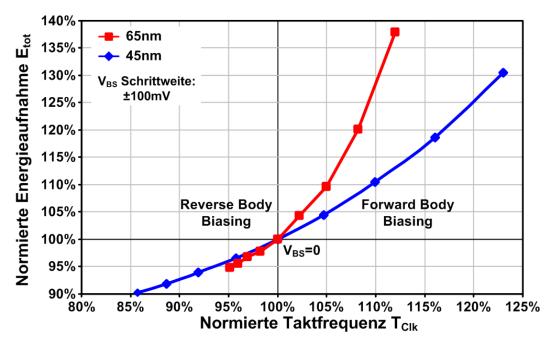

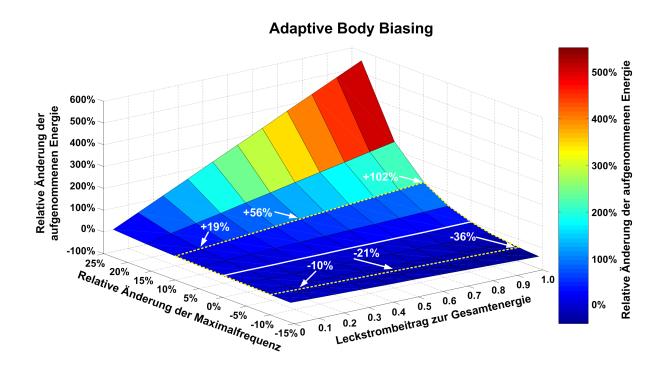

Als globale Adaptionstechniken werden das aus der Literatur bekannte Process/Adaptive Voltage Scaling (PVS/AVS) sowie Adaptive Body Biasing (ABB) behandelt und der für die Implementierung erforderliche Aufwand gegenübergestellt. Hierzu werden auch expe-

rimentelle Ergebnisse in 90nm, 65nm und 45nm CMOS verwendet. Als Teststrukturen dienen repräsentative Schaltungsstrukturen und -topologien, die aus den Erkenntnissen der Mikroprozessoranalyse in Kapitel 4 abgeleitet wurden.

Das letzte Kapitel der Arbeit fasst die wichtigsten Ergebnisse, Erkenntnisse und Wertungen zusammen und gibt einen Ausblick auf die Bedeutung der gewonnenen Erkenntnisse für kommende Generationen digitaler CMOS Schaltungen.

## 2 Vorgehensweise zur abstraktionsebenenübergreifenden Variationsanalyse

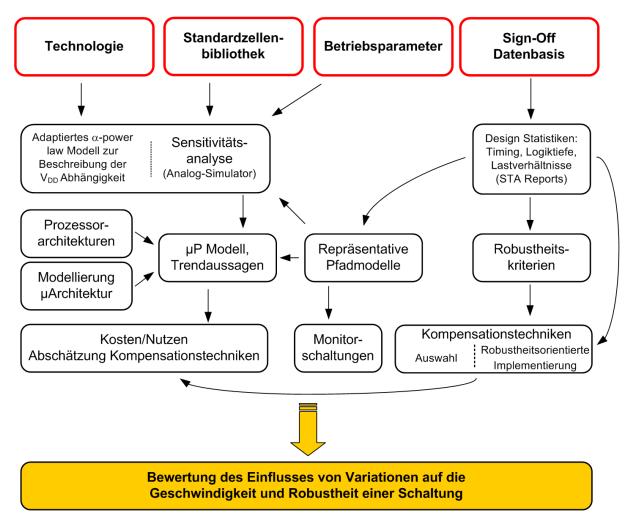

In diesem Abschnitt wird die erarbeitete Vorgehensweise zur Bewertung des Einflusses von Variationen auf die Geschwindigkeit und Robustheit von Digitalschaltungen vorgestellt. Die Bewertung von Variationseffekten wird durch zunehmende Schaltungskomplexität und verschiedene Betriebsbedingungen von low-power Schaltungen erschwert. Neben über 300 Parametern eines aktuellen BSIM Transistormodells, mehreren 100 Gattern einer Standardzellenbibliothek und mehreren 100.000 Gattern eines eingebetteten Mikroprozessors, die mehrere 100.000 kritischen Pfade bilden, müssen bei der Bewertung von Variationen auch die unterschiedlichen Versorgungsspannungs- und Temperaturbereiche der zu entwerfenden Schaltung berücksichtigt werden. Diese Beispiele zeigen, dass eine Aussage zum Einfluss von Variationen auf die Geschwindigkeit einer Schaltung nicht isoliert auf einer der in Bild 1.1 gezeigten Abstraktionsebenen getroffen werden kann, sondern die Berücksichtigung aller Ebenen vom Transistor bis hin zur Mikroarchitektur erfordert. Dies bedarf einer umfassenden Vorgehensweise zur Abstraktion und Bewertung aller verfügbaren Daten, wie sie im Rahmen dieser Dissertation erarbeitet wurde.

Bild 2.1 gibt einen Überblick über die wichtigsten Komponenten der Vorgehensweise. Ausgangspunkte sind Technologie-Datenbasen, Standarzellenbibliotheken, Betriebsparameter sowie Sign-Off Daten von eingebetteten Mikroprozessoren, hier eines ARM926 in 90nm CMOS.

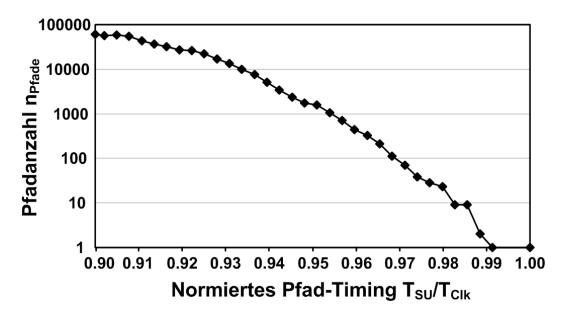

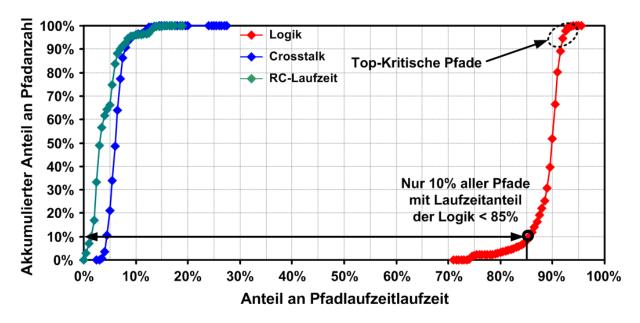

Unter Sign-Off Status versteht man den Status eines Schaltungsentwurfs zum Zeitpunkt der Freigabe zur Produktion, d.h. nach der erfolgreichen Verifikation der Spezifikationen mittels EDA Tools. Diese Daten beinhalten auch layoutspezifische Informationen, die durch Extraktion des Layouts gewonnen wurden. Durch die Verwendung von Timing-Tools wie z.B. der Statischen Timing Analyse (STA) können zeitkritische Strukturen identifiziert werden. Während des herkömmlichen Timing Sign-Offs werden nur dedizierte Informationen ausgegeben, um zum einen geringen Rechenaufwand und damit verbundene geringe Rechnerlaufzeiten zu gewährleisten, zum anderen die zu bewertende Datenmenge gering zu halten. So wird z.B. während des Timing Sign-Offs im Wesentlichen nur der Slack des zeitkritischsten aller Pfade zur Verifikation der in der Spezifikation angegebenen Taktfrequenz herangezogen. Mit Slack wird in diesem Zusammenhang die zeitliche Marge eines Pfades bezeichnet, die vorhanden ist, bevor eine Setup-Zeit Verletzung hervorgerufen wird. Ist der Slack positiv, so wird davon ausgegangen, dass die spezifizierte Geschwindigkeit gewährleistet werden kann. Im vorliegenden Fall eines ARM926 ergab eine herkömmliche STA Analyse (PrimeTime SI) der oberen 10% des Timings Daten im Umfang von ca. 100MB, um den Slack des kritischsten Pfades bestimmen zu können. Der Dateninhalt der in dieser Arbeit verwendeten Timing-Reports ist für den gleichen Timing-Bereich um einen Faktor von ca. 100 erhöht. Diese erhöhte Datenmenge resultiert aus der Aufhebung

Bild 2.1: Überblick über die einzelnen Komponenten der konzipierten Vorgehensweise zur Bewertung des Einflusses von Variationen auf die Geschwindigkeit und Robustheit von integrierten Schaltungen.

struktureller Beschränkungen wie z.B. die beschränkte Anzahl an Pfaden pro empfangendem Register. Zusammen mit weiteren Informationen aus Sign-Off Reports z.B. zur Verteilung und Größe von Kapazitäten, beträgt die erzeugte Datenmenge eines untersuchten Mikroprozessors zwischen 20 und 25GB, was in etwa der Größenordnung von 10.000.000 DIN-A4 Text-Seiten entspricht (DIN-A4: ca. 2kB). Hier wird die Notwendigkeit einer geeigneten Abstraktion der zur Verfügung stehenden Informationen besonders deutlich.

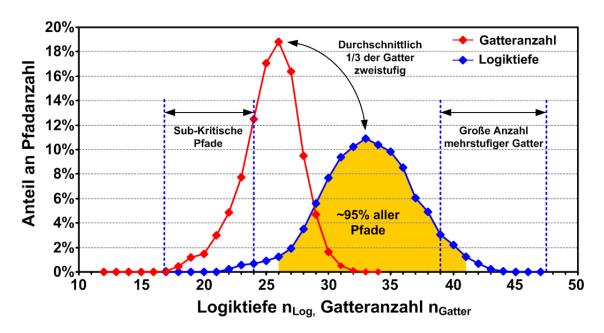

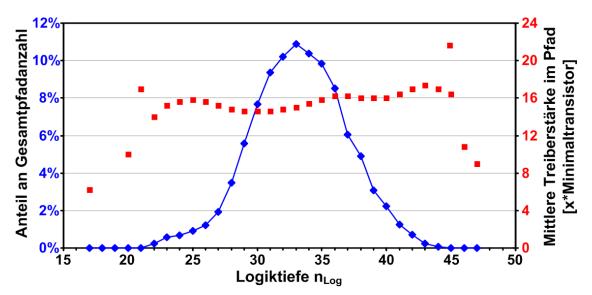

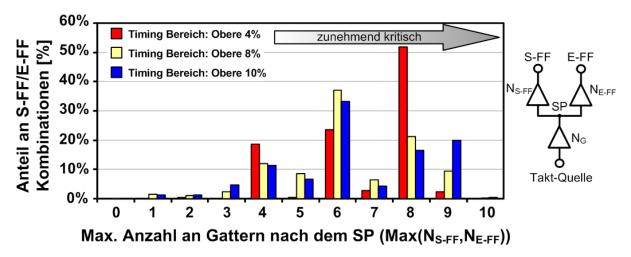

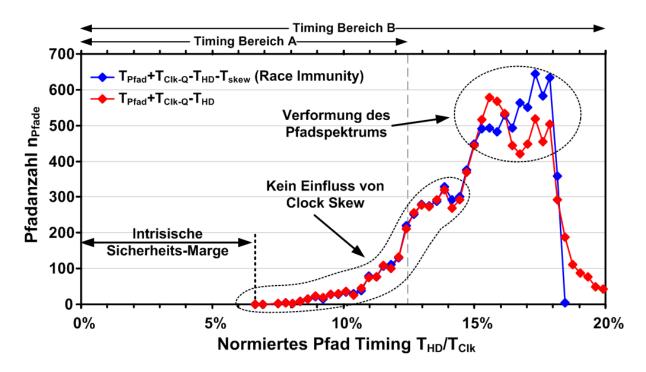

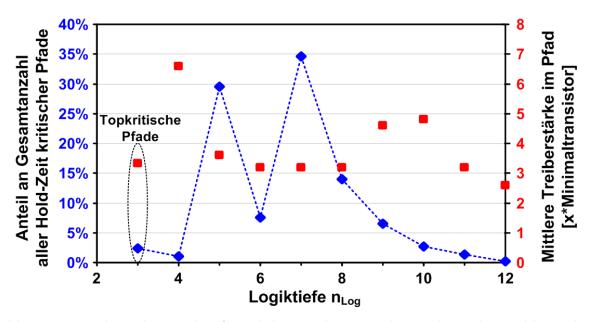

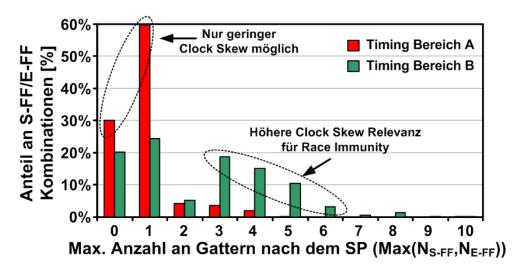

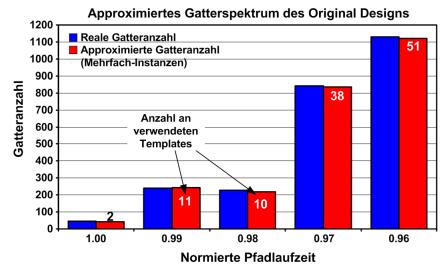

Um repräsentative Aussagen generieren zu können, wurden Statistiken über topologische Kenngrößen wie z.B. die verwendeten Transistorgrößen und Gattertypen in den kritischen Pfaden, Treiber-Last Verhältnisse, die pipeline-übergreifende Abfolge von kritischen Pfaden etc. und strukturellen Kenngrößen wie z.B. die Lage des Aufspaltungspunktes von sendendem und empfangendem Taktpfad, Logiktiefe der kritischen Pfade etc. erzeugt. Dazu wurden die Daten der einzelnen Sign-Off Reports mittels neu erstellter Add-On Software verknüpft und topologische bzw. strukturelle Eigenschaften extrahiert.

Die Häufigkeitsverteilungen der jeweiligen Kenngrößen wurden analysiert und repräsentative Eigenschaften durch Abstraktion der Daten identifiziert. Diese Ergebnisse dienen als Basis für repräsentative Pfadmodelle, neu definierte Robustheitskriterien und zur Be-

Tabelle 2.1: Übersicht über die technologischen Kernparameter von 180nm bis 45nm lowpower CMOS Technologien (reg- $V_T$  Transistoren).

|                            | 180nm | 130nm | 90nm | 65nm | 45nm |

|----------------------------|-------|-------|------|------|------|

| $V_{DD,nom}$ [V]           | 1.8   | 1.5   | 1.2  | 1.2  | 1.1  |

| $T_{ox}$ [nm]              | 3.5   | 2.2   | 1.6  | 1.6  | 1.8  |

| $V_{TN}$ [mV]              | 430   | 385   | 370  | 380  | 410  |

| $V_{TP}$ [mV]              | 380   | 310   | 290  | 340  | 380  |

| $I_{on,N}$ $[\mu A/\mu m]$ | 600   | 935   | 890  | 600  | 650  |

| $I_{on,P} [\mu A/\mu m]$   | 260   | 450   | 390  | 275  | 320  |

wertung von Kosten und Nutzen verschiedener Kompensationstechniken.

Die Überwachung des Schaltungszustandes nach der Produktion bzw. während des Betriebs der Schaltung (Monitoring) gewinnt weiter an Bedeutung, wie an der vermehrten Anzahl von Publikationen zum Thema Monitorschaltungen in den letzten Jahren zu erkennen ist. Hier spielt die Auswahl geeigneter, repräsentativer Testschaltungen CUT (Circuits Under Test) eine wichtige Rolle. In High-Performance Mikroprozessoren kommen häufig Monitorkonzepte zum Einsatz, die durch einen aufwendigen Off-Chip Test konfiguriert und kalibriert werden. Im Vergleich zu diesen standalone Prozessoren, die für mehrere 100 Dollar verkauft werden, sind für günstige low-power Schaltungen, wie sie z.B. in Mobiltelefonen eingesetzt werden, geringe Testkosten besonders wichtig, da diese einen großen Anteil am Produktpreis haben. Der Anspruch an die Implementierung von Monitoring-Konzepten ist daher, keine zusätzlichen Testkosten zu verursachen. Deshalb ist es insbesondere hier wichtig eine präzise Auswahl von geeigneten Testschaltungen bereits während des Schaltungsentwurfs zu treffen. Die Abstraktion von strukturellen und topologischen Schaltungseigenschaften zur Auswahl von repräsentativen Testschaltungen gewinnt daher an Bedeutung.

Eine ähnliche Abstraktion findet auf der Technologieebene incl. der zur Verfügung stehenden Standardzellenbibliothek statt. Zur Modellierung von Prozessvariationen werden ca. 20 Transistormodellparameter verwendet, die sich verschiedenartig auf die Geschwindigkeit von CMOS Logikschaltungen auswirken. Hier wurden Analysen vorgenommen, um die wichtigsten Parameter, d.h. die Parameter mit größtem Einfluss auf die Schaltgeschwindigkeit eines CMOS Gatters, zu identifizieren. Die wichtigsten nominellen Transistoreigenschaften der in dieser Arbeit verwendeten CMOS Technologien sind in Tabelle 2.1 zusammengefasst [8, 9, 10, 11, 12].

Unter Verwendung des Infineon internen Analog-Simulators Titan wurde die Sensitivität von repräsentativen Pfaden gegenüber den wichtigsten Prozess- und Betriebsparametern analysiert.

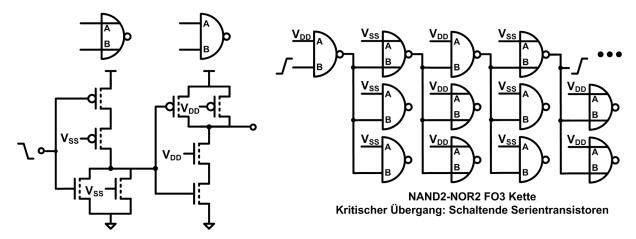

Um die Eigenschaften der repräsentativen kritischen Pfade nachbilden zu können, wurde die Laufzeitsensitivität von Standardzellen untersucht. Dazu wurden Gatter ausgewählt, die die wichtigsten schaltungstechnischen Unterschiede der Standardzellenbibliothek repräsentieren. Ein Vergleich der Laufzeitsensitivitäten von einzelnen Gattertypen und kritischen Pfaden ermöglicht somit die Nachbildung des Verhaltens kritischer Pfade gegenüber Variationen durch vereinfachte generische Pfadmodelle.

Diese repräsentativen Pfadmodelle und die für verschiedene Technologiegenerationen ermittelten Laufzeitsensitivitäten bilden zwei der drei Säulen des entwickelten Mikroprozes-

sormodells.

Dritte Säule des Modells bildet die Modellierung von Schaltungsstruktur und -topologie in Abhängigkeit mikroarchitektonischer Eigenschaften wie z.B. erhöhter Parallelität, tieferem Pipelining etc.. Hierzu wurden aus den Strukturanalysen eines ARM926 strukturelle und topologische Kenngrößen definiert, die eine Modellierung der Mikroarchitektur hinsichtlich des Einflusses von Variationen auf die Geschwindigkeit einer Schaltung ermöglichen.

Neben den Laufzeitsensitivitäten erfordert das Mikroprozessormodell auch die Eingabe von Schwankungsbreiten der einzelnen Prozess- und Umgebungsvariationen um den Beitrag variationsbedingter Laufzeitschwankungen zur Gesamtlaufzeit abschätzen zu können.

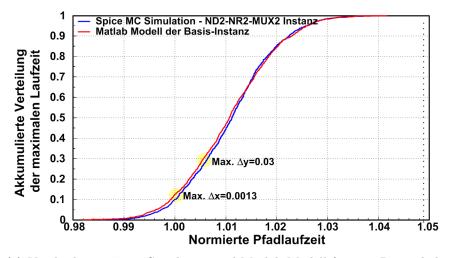

Zur Bewertung der Robustheit einer Schaltung werden Kenngrößen definiert. Diese basieren auf den Erkenntnissen der detaillierten Strukturanalyse der Schaltungen. Bei der Untersuchung der im Kapitel 5 eingeführten Robustheitskriterien wurden sowohl Titan-Simulationen als auch Matlab Modelle verwendet. Matlab Modelle wurden eingesetzt um Laufzeitverteilungen kleinerer generischer Gatternetzlisten für die strukturelle Extrapolation auf Schaltungen größerer Gatteranzahl verwenden zu können.

In dieser Arbeit wird besonders auf die Repräsentativität der gewonnen Ergebnisse geachtet. Aus diesem Grund wurde mit der ARM Mikroprozessor-Familie die repräsentativsten Vertreter eines RISC Prozessors zur Analyse und Bewertung von Variationseffekten auf die Geschwindigkeit einer Schaltung ausgewählt. Die untersuchten ARM Mikroprozessor-Designs wurden unter Verwendung von state-of-the-art Synthese und Place & Route Tools sowie unter industriellen Randbedingungen und Anforderungen an ein konkurrenzfähiges low-power Schaltungsdesign entworfen.

Zur Kosten- und Nutzenanalyse von verschiedenen Kompensationstechniken werden die ursprünglichen Schaltungsdesigns, die Ergebnisse des Mikroprozessormodells und die erstmals in dieser Form definierten Robustheitskriterien herangezogen. So werden im einen Fall die bestehenden Schaltungsdesigns abgeändert und das Timing mittels STA neu berechnet, im anderen Fall werden veränderte Laufzeitsensitivitäten und strukturelle Kenngrößen im Mikroprozessormodell berücksichtigt, um den Einfluss der Kompensationstechnik auf die Geschwindigkeit der jeweiligen Schaltung abzuschätzen.

Somit ergibt sich ein ganzheitlicher Blick auf die Wirkung von Variationen auf allen Abstraktionsebenen und die Möglichkeit zur Bewertung des Einflusses von Variationen aller Art auf die Geschwindigkeit und Robustheit einer Schaltung.

Obwohl die hier vorgestellte Vorgehensweise anhand detaillierter Analysen von eingebetteten Mikroprozessoren in sub-100nm CMOS Technologien konzipiert wurde, ist sie auf alle getakteten Digitalschaltungen übertragbar. Die detaillierten Teil- und Gesamtergebnisse der hier vorgestellten Vorgehensweise werden in den folgenden Kapiteln diskutiert.

# 3 Variationen in modernen sub-100nm low-power CMOS Technologien

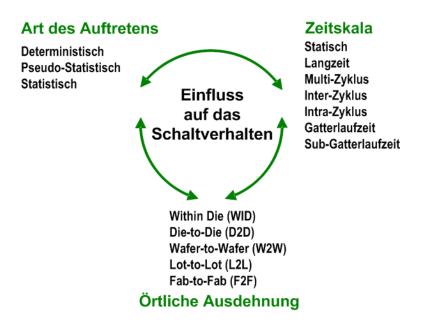

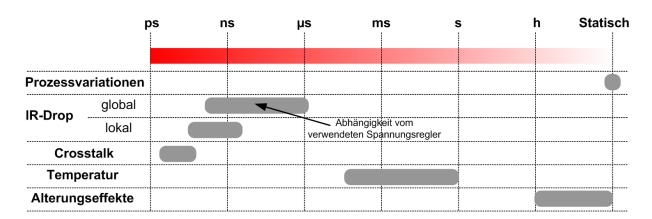

Die Abweichung eines Prozess- bzw. Betriebsparameters vom nominellen Wert wird in der Mikroelektronik als Variation bezeichnet [13]. Variationen lassen sich nach der Art ihres Auftretens, der Zeitskala ihres Wirkens und ihrer örtlichen Ausdehnung klassifizieren (Bild 3.1).

Die Art des Auftretens unterscheidet man nach deterministischem, pseudo-statistischem und statistischem Verhalten. Deterministische Schwankungen treten nach einer bestimmten Systematik auf. Deshalb werden diese Variationen oftmals auch als systematische Variationen bezeichnet. Beispiel hierfür sind z.B. unterschiedliche Ätzzeiten und Aberrationen der Projektionslinsen [14] oder topologische Abhängigkeiten auf Layoutebene (STI stress, n-well proximity).

Statistische Variationen hingegen sind unkorrelierte Variationen, die statistisch unabhängig von Transistor zu Transistor schwanken. Beispiel hierfür sind statistische Dotierstoffatom-Schwankungen (Random Dopant Fluctuations RDF) und die Genauigkeit bei der Abbildung des Transistor-Gates (Line Edge Roughness LER).

Mit pseudo-statistischen Variationen bezeichnet man betriebsbedingte Schwankungen, die im Schaltungsentwurf meist über worst-case Annahmen berücksichtigt werden, da deren Größenordnung und Auswirkungen auf die Schaltung z.B. von Betriebsparametern wie der Schaltaktivität und Temperatur abhängig sind [15]. Als Beispiel hierfür dient der dynamische Einbruch der Versorgungsspannung (IR-Drop), der aufgrund betriebs- bzw. benutzerspezifischer Lastwechsel durch die Aktivierung bzw. Deaktivierung verschiedener Schaltungsblöcke hervorgerufen wird. Die Komplexität der Schaltung ist jedoch häufig zu groß um z.B. Schaltaktivitäten vorherzusagen bzw. zu bestimmen, so dass man trotz systematischen Ursprungs von einem pseudo-statistischen Verhalten sprechen kann.

Die weitere Differenzierung von Variationen nach Variationsquelle, räumliche Ausdehnung und den Zeitkonstanten ihres Wirkens erfolgt in den folgenden Abschnitten.

## 3.1 Räumliche und zeitliche Klassifizierung von Variationen

Der Fokus dieser Arbeit liegt auf dem Einfluss von Variationen auf die Geschwindigkeit digitaler Schaltungen. Im Schaltungsentwurf muss sichergestellt werden, dass die Schaltung selbst unter worst-case Bedingungen die spezifizierte Geschwindigkeit bzw. Taktfrequenz erreicht. Für die Modellierung der Laufzeit in Abhängigkeit von Transistor- und Betriebsparametern existieren in Genauigkeit und Komplexität verschiedenste Ansätze [16, 17, 18]. Für die Modellierung der Laufzeit unter nominellen Betriebsbedingungen liefert die Methode des effektiven Schaltstroms ausreichend genaue Ergebnisse [19] um

Bild 3.1: Kriterien zur Klassifizierung von Variationen.

generelle Trends zur Geschwindigkeit von CMOS Technologien zu untersuchen. Die Laufzeit eines Inverters berechnet sich wie folgt:

$$I_H = I_{DS} \mid_{(V_{GS} = V_{DD}, V_{DS} = V_{DD}/2)}$$

(3.1)

$$I_L = I_{DS} \mid_{(V_{GS} = V_{DD}/2, V_{DS} = V_{DD})}$$

(3.2)

$$I_{eff} = \frac{I_H + I_L}{2} \tag{3.3}$$

$$t_d = \frac{C_{Last} \cdot V_{DD}}{2 \cdot I_{eff}} \tag{3.4}$$

Eine Erweiterung des effektiven Stroms zur Berechnung der Laufzeit komplexerer Gatter wurde in [17] vorgestellt. Der Effektivstrom  $I_{eff}$  beinhaltet hier gewichtete Anteile von  $I_H$ ,  $I_L$  sowie  $I_{lin} = I_{DS} \mid_{(V_{GS} = V_{DD}, V_{DS} = 0.05 \cdot V_{DD})}$ . Die Gewichtung dieser Anteile hängt von der jeweiligen Gattertopologie ab, d.h. für NAND, NOR und Inverter Gatter müssen verschiedene Gewichtungsfaktoren bestimmt werden. Die Gewichtungsfaktoren ergeben sich aus der Schalttrajektorie des jeweiligen Gatters, die wiederum von der zu treibenden Lastkapazität  $C_{Last}$  und der Signalflanke am Gattereingang abhängt.

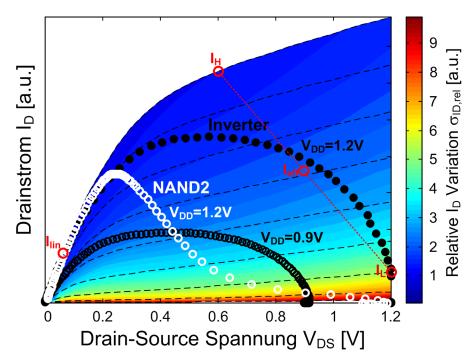

Bild 3.2 zeigt die Schalttrajektorie eines Inverters und eines 2-fach NAND Gatters. Im Hintergrund ist die Schwankung des Drainstroms  $I_D$  aufgrund von Prozessvariationen gezeigt. Es ist zu erkennen, dass beide Gatter unterschiedlich sensitive Bereiche während des Schaltvorgangs durchlaufen. Die Berücksichtigung dreier verschiedener Basisströme im erweiterten Modell ermöglicht eine frühe Abschätzung der Geschwindigkeit einer Schaltung für künftige Technologiegenerationen. Der Einfluss der Eingangs- und Ausgangsflanken auf die Laufzeit wird in diesem Modell nicht berücksichtigt. Auch die Schwankung der Laufzeit aufgrund von Prozess- und Umgebungsvariationen kann nicht mit ausreichender Genauigkeit modelliert werden. Versuche, die Schwankungen der drei Stromkomponenten zur Bestimmung der Laufzeitschwankung zu verwenden, zeigen signifikante Unterschiede zur Simulation extrahierter Netzlisten, so dass sich dieser Ansatz nicht zur Untersuchung des Einflusses von Variationseffekten auf die Laufzeit einer Schaltung eignet.

Im Allgemeinen führen Variationen, steigende Kurzkanaleffekte sowie dynamische Ef-

Bild 3.2: Schalttrajektorien von Inverter und 2-fach NAND in 65nm. Im Hintergrund ist die globale, prozessbedingte  $1\sigma$  Schwankung des Drainstroms  $I_D$  eines NMOS Transistors gezeigt.

fekte während des Schaltens wie z.B. (Ent-)laden von internen Kapazitäten, kapazitive Kopplungen (Miller-Effekt) etc. zu erhöhtem Aufwand und erhöhter Komplexität bei der Modellierung von Transistorströmen und daraus resultierenden Laufzeiten. Da die zu bestimmenden variationsbedingten Schwankungsbreiten in der Größenordnung der Modellierungsgenauigkeit vereinfachter Laufzeitmodelle (wenige Modellparameter) liegen, ist für die Bestimmung des Einflusses von Prozess- und Umgebungsvariationen ein genaues Kompakt-Modell erforderlich. Deshalb werden in dieser Arbeit, bis auf vereinzelt gekennzeichnete Ausnahmen, nur Ergebnisse aus SPICE Simulationen mit BSIMv4.5 Modellen verwendet (312 Modellparameter).

Im Folgenden wird die Variation der Transistorparameter diskutiert, die den größten Einfluss auf die Schwankung von Gatter- und Pfadlaufzeiten haben.

#### 3.1.1 Prozessvariationen

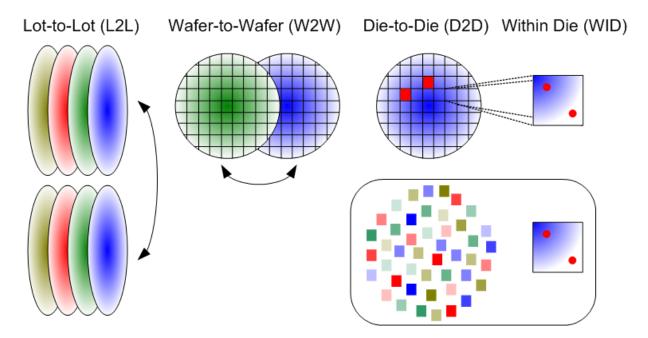

Prozessvariationen sind Abweichungen von Transistor- und Leitungsstrukturen vom nominellen Wert (Target-Value), die aufgrund der begrenzt möglichen Prozesskontrolle während der einzelnen Herstellungsschritte auftreten. Bild 3.3 zeigt die räumliche Klassifizierung von Prozessvariationen. Man unterscheidet Prozessschwankungen zwischen einzelnen Losen (L2L), zwischen Wafern des gleichen Loses (W2W), zwischen einzelnen Dies (Chips) eines Wafers (D2D), sowie zwischen identischen Strukturen auf einem einzelnen Die (WID). Auf Schaltungsebene, d.h. auf einem einzelnen Die, werden L2L, W2W und D2D Variationen als globale, WID Variationen als lokale Schwankungen bezeichnet.

Da alle Variationen außer den WID Variationen global wirken, findet man in der Literatur auch eine vereinfachte Klassifizierung, die nicht zwischen L2L, W2W und D2D Variationen unterscheidet, sondern diese Parameterschwankungen unter dem Begriff D2D Variationen zusammenfasst, wie in Bild 3.3 angedeutet ist.

Bild 3.3: Räumliche Klassifizierung von Prozessvariationen.

Im Schaltungsentwurf werden die Schwankungsbreiten aller systematischen und statistischen Prozessvariationen einer Technologie als Monte-Carlo Parameter in Simulationsdateien abgelegt. Diese Parameter repräsentieren die Schwankungsbreiten aller Modellparameter dieser Technologie. Unabhängig davon, ob die Quelle der Variation systematischen oder statistischen Ursprungs ist, wird für alle Schwankungen als Wahrscheinlichkeitsverteilung die Gauß'sche Normalverteilung gewählt. Der Mittelwert  $\mu_i^{MC}$  liegt beim Target-Wert des jeweiligen Parameters i, die Standardabweichung des Parameters i bei  $\sigma_i^{MC}$ . Im digitalen Schaltungsdesign wird der  $\mu+3\sigma$  Wert der Laufzeitschwankung oftmals als worst-case Szenario bezeichnet. Da aufgrund von Modellierungsproblemen selbst systematische Variationen als statistische Schwankungen modelliert werden [20, 21], wird in dieser Arbeit auch im Zusammenhang systematischer Schwankungen von Mittelwert und Standardabweichung gesprochen.

Im folgenden Abschnitt werden die Schwankungsquellen und -beiträge der wichtigsten Transistorparameter diskutiert.

• Gatelänge:

$$L_{eff} = L_{nom} + \underbrace{\Delta L_{eff,glo} + \Delta L_{eff,lok} + \delta_{L_{eff}}}_{\sigma_L^{MC}}$$

Die Gatelänge eines Transistors verändert sich z.B. aufgrund von systematischen Unterschieden in der Belichtung (Zeit und Dosis), unregelmäßiger Belackung, sowie Schwankungen im Ätzprozess. Die Gatelängenschwankung setzt sich aus einem globalen Anteil, bestehend aus L2L, W2W und D2D Komponenten, sowie einem lokalen Anteil zusammen.

Die globale, systematische Schwankungsbreite  $\Delta L_{eff,glo}$  hängt dabei vorwiegend von der Prozesskontrolle ab. Inhomogenitäten im Layout, basierend auf unterschiedlicher Anordnung und Dichte der Transistor-Gates, führen zu inhomogener Belichtung, Belackung und Ätzraten [22]. Dies resultiert in einem systematischen, lokalen Anteil der Gatelängenschwankung  $\Delta L_{eff,lok}$ . Systematische Variationsquellen können durch verbessertes OPC (Optical Proximity Correction) [23], auflösungsverbessern-

der Maßnahmen (Resolution Enhancement Techniques RET) [24] und regulären Layoutstrukturen wie z.B. PLA oder Logic Bricks Designs [25, 26] verringert werden. Der statistische Anteil der Gatelängenschwankung  $\delta_{L_{eff}}$ , der sich aufgrund von Mittelungseffekten mit zunehmender Weite des Transistors verringert, beruht unter anderem auf Quanteneffekten während der Belichtung. Beispiel hierfür ist die diskrete Anzahl von Photonen, die bei der Belichtung vom Photolack absorbiert werden. Ein zusätzlicher Anteil an der statistischen Schwankung der Gatelänge wird beim Ätzen des Poly-Gates hervorgerufen. Hier wird die Gatelänge durch statistische Schwankungen der Reaktanden beim Ätzvorgang beeinflusst. Die Bedeutung von LER nimmt aufgrund eines steigenden relativen Anteils an der Gatelänge für künftige Technologieknoten zu [27, 28]. In den aktuell verwendeten Technologien bis zu 45nm ist dieser Effekt in der digitalen Logik jedoch noch nicht sichtbar. Aufgrund der im Vergleich zur Logik kleinen Transistorweiten in SRAM Zellen wird dieser Effekt erstmals dort zu sehen sein.

• Einsatzspannung:

$$V_T = V_{T,nom} + \underbrace{\Delta V_{T,glo} + \Delta V_{T,lok} + \delta_{V_T}}_{\sigma_{V_T}^{MC}}$$

In modernen CMOS Technologien hängt die Einsatzspannung von verschiedenen Dotierungsschritten ab. Das effektive Dotierprofil nach Implantation der Substratdotierung und Halo-Dotierung bestimmt die Einsatzspannung des Transistors. Da die Einsatzspannung nicht nur vom Dotierprofil selbst sondern auch von der Aktivierung der Dotieratome abhängt, ist es wichtig, bei der Aktivierung der Dotierstoffe (Rapid Thermal Anneal RTA) einen Temperaturgang auf dem Wafer bzw. den einzelnen Dies zu vermeiden. Schwankungen während der Dotierstoff-Implantation und Temperaturunterschiede während des RTA stellen globale, systematische Quellen der Einsatzspannungsschwankung  $\Delta V_{T,glo}$  dar.

Als lokale systematische Quellen gelten layoutabhängige Schwankungen der Einsatzspannung  $\Delta V_{T,lok}$ [29]. Dazu zählen WID Temperaturgradienten während des RTA [30], z.B. durch Irregularitäten der Transistorgate-Dichte, Umgebungseffekte wie z.B. die Lage des Transistors zur n-Wanne (n-well proximity) [31] sowie der Einfluss der Transistorisolierung auf die Gitterstruktur des Transistor-Kanalgebiets (STI stress) [32].

Die Einsatzspannung hängt neben der Temperatur auch von der Gatelänge des Transistors ab  $(V_T \text{ roll-off})$  [33]. Je kürzer die Gatelänge desto kleiner die Einsatzspannung, d.h. Gatelängen- und Einsatzspannungsschwankungen korrelieren partiell.

Die statistische Einsatzspannungsschwankung  $\delta_{V_T}$  basiert vorwiegend auf der statistischen Verteilung (Random Dopant Fluctuations RDF) der Dotierstoffatome. Da sich die zu dotierende Fläche bzw. das zu dotierende Volumen für Bulk-Transistoren von einer Technologiegeneration zur nächsten stark verringert, nimmt die Anzahl der Dotieratome, die die Einsatzspannung bestimmen, ab. Die relative Schwankung, die durch ein einzelnes gestreutes Dotieratom verursacht wird, nimmt daher für fortschreitende Technologieskalierung zu. Dabei zeigt die statistische Schwankung der Einsatzspannung folgende Abhängigkeit [34, 35]:

$$\sigma_{V_T} = \frac{A_{VT0}}{\sqrt{WL}} \sim \frac{N_{Dot}^{\frac{1}{4}}}{C_{ox}} \cdot \frac{1}{\sqrt{WL}} = \frac{t_{ox} \cdot N_{Dot}^{\frac{1}{4}}}{\varepsilon_{ox}} \cdot \frac{1}{\sqrt{WL}}$$

(3.5)

$A_{VT0}$  ist die Mismatch-Konstante der Einsatzspannung,  $t_{ox}$  die Dicke des Gateoxids,

$N_{Dot}$  die Dotierstoffkonzentration im Kanal,  $\varepsilon_{ox}$  die Dielektrizitätskonstante des Gateoxids und  $W \cdot L$  die Transistorgeometrie.

Die Mismatch-Konstante  $A_{VT0}$  zeigt eine lineare Abhängigkeit von  $t_{ox}$ . Ein weiteres Skalieren der Oxiddicke ist mittelfristig zu erwarten [36]. Für low-power Technologien kann eine Oxiddicke von 1.5nm als untere Grenze gesehen werden, um einen weiteren Anstieg der Gate-Leckströme zu verhindern [37]. Die Erhöhung der Kanaldotierung, die sich für moderne Bulk-Transistoren in der Größenordnung von  $10^{18} - 10^{19} \frac{1}{cm^3}$  befindet [37], hat zwar eine geringere Auswirkung auf die Einsatzspannungsschwankung, trägt aber dennoch zu erhöhten  $V_T$ -Variationen mit fortschreitender Technologieskalierung bei. Die Größe der Einsatzspannungsschwankung in Bulk-CMOS Technologien wird vorwiegend durch die Transistorgeometrie beeinflusst, was eine weitere Zunahme der statistischen Einsatzspannungsschwankung für künftige Technologien zur Folge hat. Eine verringerte Schwankung der Einsatzspannung kann über eine erhöhte Dielektrizitätskonstante des Gateoxids erfolgen (high-k), oder bedarf einer fundamentalen Änderung des Transistors, z.B. die Einstellung der Einsatzspannung über das Gate-Material (metal gate) anstatt über die Dotierstoffkonzentration im Kanal. So kann die Dotierstoffkonzentration  $N_{Dot}$  signifikant reduziert werden bzw. wegfallen, und somit die Einsatzspannungsschwankung deutlich verringert werden.

• Beweglichkeit:

$$\mu = \mu_{nom} + \underbrace{\Delta \mu_{glo} + \Delta \mu_{lok} + \delta_{\mu}}_{\sigma_{\mu}^{MC}}$$

Die Beweglichkeit der Ladungsträger im Kanal wird durch die freie Weglänge der Ladungsträger und damit durch die Häufigkeit deren Streuung an Gitteratomen bestimmt. Diese ist abhängig von der Beschaffenheit der Oxid-Kanal-Grenzfläche, sowie von der Dotierstoffkonzentration und -verteilung im Kanal. Die Beweglichkeit nimmt mit geringerer Oxiddicke ab, da das vertikale elektrische Feld ansteigt, und die Ladungsträger stärker in Richtung Oxid-Kanal-Grenzfläche beschleunigt werden, was zu erhöhter Streuung der Ladungsträger an der Grenzfläche führt. So hängt die Beweglichkeitsschwankung auch von der Oxiddickenschwankung ab. Während die durch Oxiddickenschwankung hervorgerufene Beweglichkeitsschwankung vorwiegend global  $\Delta \mu_{glo}$  auftritt, trägt die Schwankung der Dotierstoffatome sowohl zur globalen als auch lokalen ( $\Delta \mu_{lok}$ ) Beweglichkeitsschwankung bei.

Zusätzliche systematische Komponenten resultieren aus Verspannungen der Gitterstruktur, die z.B. aufgrund von STI und Ätz-Stop Schichten hervorgerufen werden. Kompressiver Stress bewirkt eine deutlich erhöhte Beweglichkeit von positiven Ladungsträgern (Löchern), die Beweglichkeit der negativen Ladungsträger (Elektronen) wird reduziert [32, 38]. In neuen Technologien werden zur Verbesserung der Beweglichkeit spezielle Schichten auf PMOS und NMOS Transistoren aufgebracht, um kompressive Verspannung im PMOS Kanal sowie Zugspannung im NMOS Kanal zu induzieren. Die von der Transistorstruktur und -anordnung abhängige Verspannung ist ebenfalls eine weitere Quelle systematischer Beweglichkeitsschwankung.

Neben den systematischen Quellen existieren auch statistische Schwankungen in der Gitterstruktur, der Oxid-Kanal-Grenzfläche etc., die in dem statistisch schwankenden Anteil der Beweglichkeit  $\delta_{\mu}$  zusammengefasst werden.

In der Praxis werden neben statistischen Einsatzspannungsschwankungen durch RDF auch statistische Drainstrom-Schwankungen (Strom-Mismatch) gemessen die

als statistische Schwankung der Beweglichkeit modelliert wird. Der Strom-Mismatch wird auch mit  $\sigma_k$  bezeichnet und entspricht im Wesentlichen  $\delta_{\mu}$ .

#### • Oxiddicke: $t_{ox}$

Variationen bei der thermischen Oxidation zur Herstellung des Gateoxids haben eine unterschiedliche Oxiddicke zur Folge. Eine relativ hohe Fertigungsgenauigkeit bei der thermischen Oxidation und Nitridierung des Oxids ermöglicht eine sehr gute Reproduzierbarkeit und nahezu konstante Oxiddicken. Eine starke Verringerung der physikalischen Gateoxiddicke ist für zukünftige low-power CMOS Technologien nicht zu erwarten, da der damit verbundene Anstieg der Gateleckströme nicht hinnehmbar ist [37, 39, 36]. Die Schwankung der Oxiddicke wird sich daher für künftige Technologien nicht wesentlich verändern. Gegenüber den Schwankungen von L und  $V_T$  ist die Variation des Gateoxids gering [14].

#### • Verdrahtung: $R_{Ltg}, C_{Ltg}$

Neben den Schwankungen in den FEOL Prozessen (Front End of Line FEOL) treten auch Variationen in den BEOL Prozessschritten (Back End of Line BEOL) auf, die sich sowohl auf den Widerstands- als auch den Kapazitätsbelag der einzelnen Metallebenen auswirken. Im Allgemeinen liegt die Schwankungsbreite des Widerstands deutlich über der der Leitungskapazität [40]. Der globale Beitrag zur Widerstandsschwankung liegt bei über 90%, der in globalen Prozess-Cornern abgedeckt wird. Der Within-Die Anteil resultiert aus Schwankungen der Leitungsgeometrie (Lithographie) und CMP-induzierten Schwankungen der Leitungshöhe [40, 41]. Diese lokalen, umgebungsabhängigen Schwankungen sind auch für die Schwankung der Leitungskapazität verantwortlich.

Kapazität  $C_{Ltg}$  und Widerstand der Leitung  $R_{Ltg}$ , sowie die Laufzeit vom Gattereingang des Treibergatters bis zum Ende der Leitung können wie folgt modelliert werden [42]:

$$C_{Ltg} = \varepsilon L_{Ltg} \left[ 1.15 \left( \frac{W_{Ltg}}{H_{Ltg}} \right) + 2.8 \left( \frac{T_{Ltg}}{H_{Ltg}} \right)^{0.222} \right]$$

$$+ 2\varepsilon L_{Ltg} \left( \frac{S_{Ltg}}{H_{Ltg}} \right)^{-1.34} \left( 0.03 \left( \frac{W_{Ltg}}{H_{Ltg}} \right) + 0.83 \left( \frac{T_{Ltg}}{H_{Ltg}} \right) - 0.07 \left( \frac{T_{Ltg}}{H_{Ltg}} \right)^{0.222} \right)$$

$$(3.6)$$

$$R_{Ltg} = \rho_{Ltg} \cdot \frac{L_{Ltg}}{W_{Ltg} \cdot T_{Ltg}}$$

$$t_d = 0.69 \cdot R_{Tr} \left( C_{Off} + C_{MOS} + C_{Ltg} \right) + R_{Ltg} \left( 0.38 \cdot C_{Ltg} + 0.69 \cdot C_{MOS} \right)$$

$$(3.8)$$

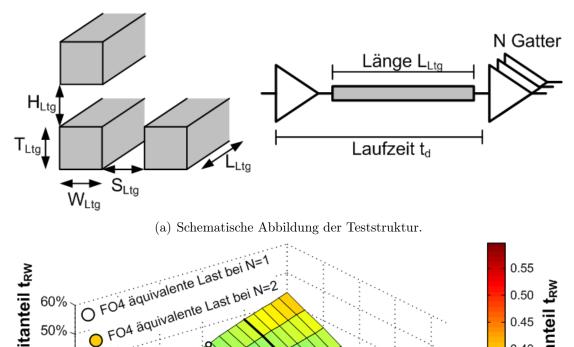

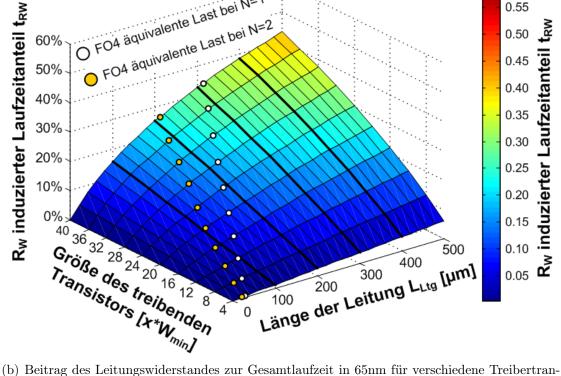

Die Größen  $W_{Ltg}, T_{Ltg}, S_{Ltg}, H_{Ltg}$  beschreiben wie in Bild 3.4(a) gezeigt die Geometrie der Leitung.  $R_{Tr}$  ist der effektive Widerstand des Treibergatters,  $C_{Off}$  repräsentiert die zellinternen intrinsischen Kapazitäten,  $C_{MOS}$  ist die Kapazität der Eingangspins am Ende der Leitung,  $C_{Ltg}$  und  $R_{Ltg}$  sind Widerstand und Kapazität der Leitung.  $\rho_{Ltg}$  ist der spezifische Widerstand des Metalls z.B. Kupfer, Aluminium

Für die folgende Untersuchung wird der effektive Widerstand des Treibergatters

(b) Beitrag des Leitungswiderstandes zur Gesamtlaufzeit in 65nm für verschiedene Treibertransistoren und Leitungslängen (nomineller Prozess.

Bild 3.4: Modellierung zur Bestimmung des Beitrags des Leitungswiderstands zur Laufzeit eines Pfades.

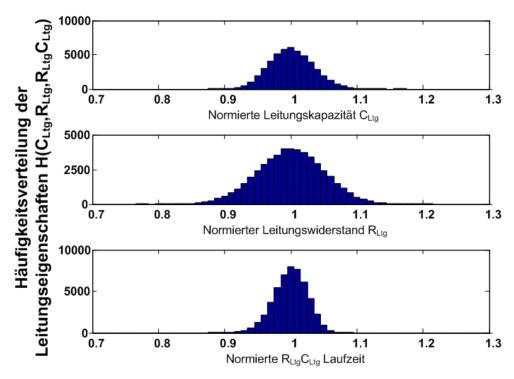

über den Effektivstrom  $I_{eff}$  bei der jeweiligen Versorgungsspannung  $V_{DD}$  berechnet. Wie bereits in diesem Kapitel diskutiert wurde, eignet sich der Effektivstrom vorwiegend zur Modellierung der Laufzeit unter nominellen Transistorparametern. Da in diesem Fall der Einfluss des Leitungswiderstandes bestimmt werden soll, werden die nominellen Transistoreigenschaften zur Bestimmung von  $I_{eff}$  herangezogen. Bild 3.4(b) zeigt den Laufzeitanteil der Gesamtlaufzeit  $t_d$ , die durch den Leitungswiderstand der in Bild 3.4(a) gezeigten Leitungsstruktur hervorgerufen wird. Die Ergebnisse wurden für verschiedene Transistorgrößen und Leitungslängen in 65nm CMOS berechnet. Als Leitungsparameter werden die Eigenschaften von Minimalleitungen der Metallebenen M2-M4 verwendet. Für jede Transistorgröße wird die äquivalente Leitungslänge berechnet, die zusammen mit der Anzahl N an Gattern am Ende der Leitung die vierfache kapazitive Last der Eingangslast des Treibergatters ergibt (Fanout-4 Last, FO4). Dieses Verhältnis von kapazitiver Last am Gatterausgang und Gattereingang wird von vielen Tools im Schaltungsentwurf angestrebt, um eine annähernd minimale Pfadlaufzeit zu erzielen [43, 44]. Neben der Auswirkung auf die Laufzeit werden ferner steile Signalflanken gewährleistet, was zum einen geringe Verluste durch Kurzschlussströme, zum anderen einen verminderten Einfluss von Crosstalkeffekten auf die Propagation des Signals zur Folge hat. In Bild 3.4(b) ist deutlich zu erkennen, dass für Gatter, bestehend aus Transistoren mit der Treiberstärke eines Transistors der Weite  $W = 16W_{min}$ , der resistive Laufzeitbeitrag einer solchen Leitung bei nur 7% liegt. Selbst eine Widerstandsschwankung von 10% führt zu einer Laufzeitschwankung von weniger als 1%. Für Treibertransistoren mit 40facher Minimalgröße liegt der Beitrag bei 34%. Derartige Strukturen sind hauptsächlich im Taktbaum und in Bus-Strukturen zu finden. Während im Taktbaum der Leitungsanteil an der kapazitiven Last aufgrund einer erhöhten Anzahl N > 2 an Empfangsgattern geringer ist, stellt eine Bus-Struktur eine Punkt-zu-Punkt Verbindung dar. In diesen Strukturen werden Leitungen verwendet, die deutlich breiter sind als die Minimalgröße, so dass sich der Widerstand der Leitung deutlich reduziert, während der Kapazitätsbelag aufgrund der höheren Kopplung auf die untere und obere Metallebene ansteigt. Die FO4-äquivalente Leitungslänge nimmt somit ab. Geometriebedingte  $R_{Ltg}$  und  $C_{Ltg}$  Schwankungen kompensieren sich hinsichtlich ihres Einflusses auf die Laufzeit jedoch teilweise gegenseitig, da beide stark negativ korrelieren, so dass die Schwankungsbreite der  $R_{Ltq} \cdot C_{Ltq}$  Laufzeit deutlich geringer ist als die Schwankungsbreiten von Leitungskapazität und -widerstand. Bild 3.5 zeigt die nach Gleichung 3.6 und 3.7 berechneten globalen, geometrieabhängigen Schwankungen von  $R_{Ltg}$ ,  $C_{Ltg}$  und  $R_{Ltg} \cdot C_{Ltg}$  für 65nm CMOS unter der Annahme normalverteilter Geometrieschwankungen. Es ist deutlich zu erkennen, dass die negative Korrelation von  $R_{Ltg}$  und  $C_{Ltg}$  zu geringeren Schwankungsbreiten der  $R_{Ltg} \cdot C_{Ltg}$ Laufzeit führen.

Im geschwindigkeitskritischen worst-case Fall, d.h. bei langsamem Prozess, verringert sich zudem der Einfluss von Widerstandsschwankungen der Verdrahtung auf die Laufzeit, da der effektive Transistorwiderstand und somit der Laufzeitanteil des Treibergatters an der Gesamtlaufzeit ansteigt.

Im Gegensatz zur Schwankung des Leitungswiderstandes führt eine veränderte Kapazitätsschwankung bereits bei kürzeren Leitungen zu Laufzeitschwankungen. Die vorwiegend systematischen Variationen der Leitungsstrukturen wirken sich jedoch wesentlich geringer auf die Geschwindigkeit der Schaltung aus, als die Schwankungen der Transistorparameter [45, 46].

Bild 3.5: Häufigkeitsverteilung von Leitungskapazität, -widerstand und RC Laufzeit der Verdrahtung (nach Glg. 3.6, 3.7) in 65nm CMOS unter der Annahme globaler, normalverteilter Geometrieschwankungen.

Die geometrieabhängige Schwankung von  $R_{Ltg}$  und  $C_{Ltg}$  wird neben Lithographie-Effekten hauptsächlich durch Dishing und Erosion verursacht. Diese wirken sich auf die Dicke der Leiterbahn und somit auf die Kapazität und den Widerstand der Leitung aus. Sie treten beim chemisch-mechanischen Polierschritt (Chemical Mechanical Polishing CMP) auf und sind abhängig von der Dichte und Breite der Leiterbahnen. Somit ergibt sich eine vorwiegend lokale, systematische Schwankung in der Verdrahtung.

Statistische Effekte wie LER in der Verdrahtung nehmen aufgrund von Mittelungseffekten mit der Länge der Leitung ab. Schwankungen in kurzen Leitungen bewirken vernachlässigbar kleine Laufzeitschwankungen, da deren Kapazität und Widerstand nur einen geringen Anteil zur Gatter- bzw. Pfadlaufzeit beitragen.

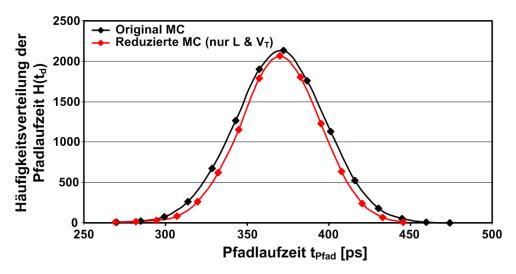

Die Ergebnisse der in dieser Arbeit durchgeführten Untersuchungen zeigen, dass die Schwankungen von Gatelänge L und Einsatzspannung  $V_T$  für ca. 90% der Laufzeitschwankungen im gesamten produktrelevanten Betriebsbereich ( $V_{DD} \in [V_{DD_{nom}} - 300mV; V_{DD_{nom}}]$ ) verantwortlich sind. Ähnliche Erkenntnisse werden in [40, 47, 48] berichtet. Bild 3.6 zeigt die Ergebnisse einer Monte-Carlo Simulation eines extrahierten NAND2-NOR2 Pfades in 65nm CMOS Technologie für den originalen sowie einen reduzierten Parametersatz bei nomineller Betriebsspannung. Anstelle von 17 global schwankenden Parametern beinhaltet der reduzierte Parametersatz lediglich die globale Schwankung der Gatelänge L und der Einsatzspannung  $V_T$ . Der Parametersatz der lokal schwankenden Größen bleibt unverändert und beinhaltet die schwankenden Größen  $V_T$  und  $\mu$ . Es ist deutlich erkennbar, dass sich die Schwankungsbreite der Pfadlaufzeit für den reduzierten Parametersatz nur geringfügig gegenüber der Verwendung des vollständigen Parametersatzes ändert.

Die weiteren Untersuchungen beschränken sich daher im Folgenden auf die Betrachtung

Bild 3.6: Vergleich von Monte Carlo Simulationen mit standardmäßigem und reduziertem Parametersatz ( $V_{DD}=V_{DD}^{nom},~{\rm T=27^{\circ}C}$ ).

der drei wichtigsten Transistorparameter  $L, V_T$  und  $\mu.$

Bild 3.7: Schematische Darstellung der einzelnen IR-Drop Komponenten.

#### 3.1.2 Umgebungsvariationen

Neben Prozessvariationen beeinflussen auch Umgebungsvariationen das Schaltverhalten von Transistoren. Diese Variationen, die während des Betriebs der Schaltung auftreten, sind im Wesentlichen von Betriebsparametern (z.B.  $V_{DD}$ , T) und der Schaltungstopologie abhängig. Während des Schaltungsentwurfs kann z.B. über die Dimensionierung der Leitungen Einfluss auf die Sensitivität der Schaltung gegenüber Umgebungsvariationen genommen werden. Das Schaltverhalten während des Betriebs der Schaltung, d.h. Schaltaktivität, Schaltprofile (switching pattern) etc. ist allerdings nicht bekannt. Die Emulation bzw. Modellierung all dieser Parameter während des Designs ist aus Komplexitätsgründen nicht möglich. Aus diesem Grund spricht man von einem pseudo-statistischen Charakter der Umgebungsvariationen. Im Folgenden werden die wichtigsten Quellen von Umgebungsvariationen diskutiert:

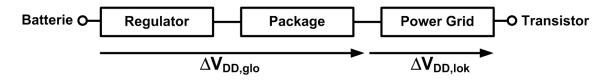

#### • IR-Drop: $V_{DD} = V_{DD,nom} + \Delta V_{DD,qlo} + \Delta V_{DD,lok}$

Der IR-Drop, d.h. der Spannungsabfall  $\Delta V$  an einem Widerstand bei Stromfluss, entlang von Versorgungsleitungen zum einzelnen Transistor, reduziert die effektive Betriebsspannung des Transistors und damit den Gate-Overdrive  $V_{DD} - V_T$ . Der Spannungsabfall ist abhängig vom Schaltverhalten der gesamten Schaltung (Aktivität der Schaltung), sowie von Unterschieden in der lokalen Leistungsdichte [49]. Die effektive Betriebsspannung des Transistors setzt sich aus der externen Versorgungsspannung (Batterie), den Pegelverlusten am externen Spannungsregler und an den Widerständen des 'Package'  $\Delta V_{DD,glo}$ , sowie an den Leitungswiderständen  $\Delta V_{DD,lok}$  zusammen. Bild 3.7 zeigt schematisch alle Komponenten des Spannungseinbruchs bis zum einzelnen Transistor der Schaltung.

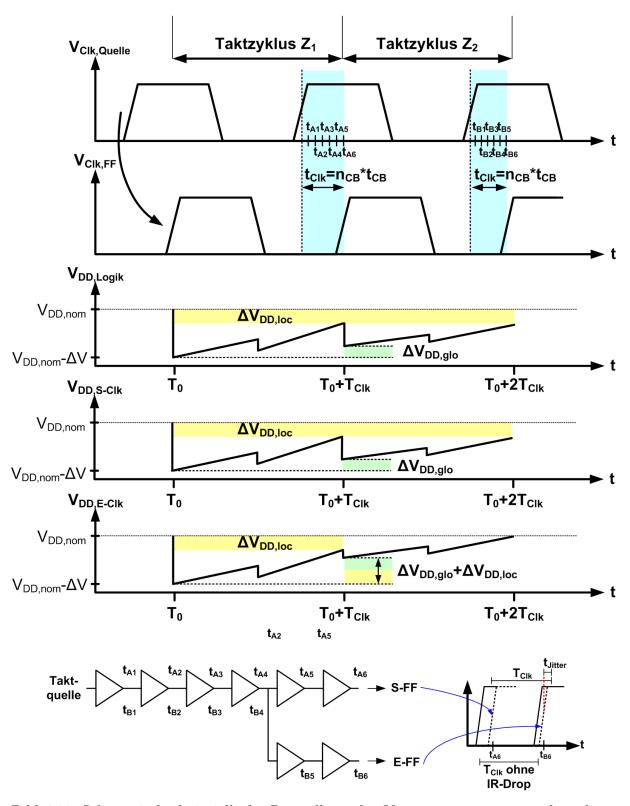

Die Höhe des Spannungseinbruchs ist abhängig von der Positionierung der Schaltung relativ zur Package-Chip Schnittstelle [50, 51]. Die am Transistor anliegende effektive Versorgungsspannung wird durch diesen Spannungsabfall verringert und beeinflusst aufgrund des reduzierten Gate-Overdrives  $V_{DD} - V_T$  das Schaltverhalten des Transistors und somit auch die Laufzeit von Pfaden. Dabei dient der Zyklusmittelwert des Spannungseinbruchs als Hauptindikator bezüglich des Einflusses auf die Pfadlaufzeit [51].

Der Spannungsabfall in der Versorgungsspannung resultiert im Taktverteilungsnetz (Clock Tree) in zeitabhängigen, zeitlichen Unausgeglichenheiten des Clock Trees. Dies führt neben einem Intra-Zyklus Anteil des Clock Skews zu einem von Zyklus zu Zyklus unterschiedlichen Spannungsabfall an den Clock-Buffern. Dieser Clock Jitter hat eine Vergrößerung bzw. Verkleinerung der effektiven Taktperiode zur Folge.

Neben diesem resistiven Spannungsabfall ist es möglich, dass über starke Lastwechsel und damit verbundenen Sprüngen im Stromverlauf, das Versorgungsnetz zu einer Schwingung angeregt wird. Man spricht vom  $\frac{dI}{dt}$  Effekt. Die Dämpfung der angereg-

Tabelle 3.1: Relevanter Temperaturbereich von CMOS Digitalschaltungen.

| Anwendung           | Minimale Temperatur | Maximale Temperatur |

|---------------------|---------------------|---------------------|

| Automobilelektronik | -40°C               | 125°C               |

| Mobiltelefon        | -20°C               | 85°C                |

ten Schwingung ist dabei vom Widerstand, der Kapazität sowie der Induktivität der Schaltung abhängig. Für die Betrachtung der Laufzeitschwankung kann dieser Effekt im Allgemeinen jedoch vernachlässigt werden [51].

#### • Betriebstemperatur: T:

Sowohl die Einsatzspannung der Transistoren als auch die Beweglichkeit der Ladungsträger zeigt eine deutliche Temperaturabhängigkeit [52, 53]:

$$\mu(T) = \mu(T_0) \cdot \left(\frac{T}{T_0}\right)^{-k_\mu} \tag{3.9}$$

$$V_T(T) = V_T(T_0) - \gamma_{V_T} \cdot (T - T_0) \tag{3.10}$$

T bezeichnet die Temperatur [°K],  $T_0$  die Temperatur zum Zeitpunt t=0.  $k_{\mu}$  ist der Beweglichkeits-Temperaturkoeffizient und liegt zwischen 1.2 und 2.0.  $\gamma_{V_T}$  bezeichnet den Temperaturkoeffizienten der Einsatzspannung.

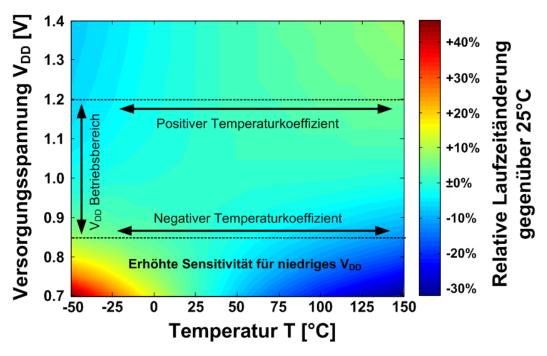

Mit zunehmender Temperatur nimmt die Beweglichkeit der Ladungsträger im Kanal aufgrund erhöhter Streuungen an Phononen ab und verringert somit den Transistorstrom. Gleichzeitig führt die Zunahme der thermischen Energie zu einem reduzierten Fermi-Potential  $\phi_F$ , das eine verringerte Einsatzspannung zur Folge hat und der beweglichkeitsbedingten Abnahme des Transistorstroms entgegenwirkt. Je nach Versorgungsspannung  $V_{DD}$  hat eine der beiden Größen einen dominierenden Einfluss auf die Laufzeit. Für hohe Versorgungsspannungen dominiert das Temperaturverhalten der Beweglichkeit, für niedriges  $V_{DD}$  das Temperaturverhalten der Einsatzspannung. Bei einer bestimmten Versorgungsspannung  $V_{DD}$  kompensieren sich beide Beiträge, und die Laufzeit bleibt unverändert. Dieser Punkt wird als Zero Temperature Coefficient Point (ZTCP) bezeichnet und liegt für 90nm CMOS bei ca. 0.85V [53].

Die Temperatur kann als globaler Betriebsparameter betrachtet werden. Signifikante Temperaturunterschiede treten vorwiegend zwischen Prozessorkern und Speicher bzw. Peripherie, sowie zwischen einzelnen Mikroprozessorkernen (Multi-Core Design) auf. Selbst für diese räumlich getrennten Komponenten werden in den häufigsten Fällen Temperaturgradienten von lediglich 10°C gemessen [54, 55]. Die meisten zeitkritischen Strukturen befinden sich im Prozessorkern und weisen keine großen räumlichen Distanzen auf [56], so dass insbesondere in kleinen Schaltungen keine signifikanten lokalen Temperaturgradienten zu erwarten sind.

Neben dem direkten Einfluss der Temperatur auf die Laufzeit von Gattern und Pfaden führt eine erhöhte Temperatur zur verstärkter Alterung durch NBTI (Negative Bias Temperature Instability, siehe 3.1.3). Tabelle 3.1.2 zeigt für verschiedene Anwendungsbereiche die für den Betrieb der Schaltung relevanten Temperaturbereiche.

Bild 3.8: Schematische Darstellung eines Crosstalk relevanten Netzes in einem Fanout-4 Inverter Pfad.

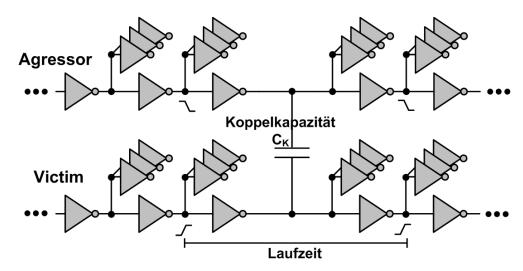

#### • Übersprechen/Crosstalk:

Die kapazitive Kopplung zwischen zwei Netzen führt beim Schaltvorgang zur gegenseitigen Beeinflussung des Potentials durch Ladungsverschiebung, d.h. der Signalwechsel an einem der Netze (Aggressor) beeinflusst den Spannungspegel am ruhenden bzw. ebenfalls schaltenden anderen Netz (Victim). Bild 3.8 zeigt eine schematische Anordnung zweier kapazitiv gekoppelter Netze innerhalb eines Fanout-4 Inverter Pfades.

Liegt das schaltende Victim-Netz in einem kritischen Pfad, so beeinflusst der Crosstalkeffekt die minimal mögliche Taktperiode der Schaltung. Für gleichgerichtete Schaltvorgänge am Victim- und Aggressor-Netz verringert sich die Laufzeit, bei entgegengesetzten Transitionen erhöht sich die Laufzeit des Pfades im Vergleich zu einem ruhenden Aggressor-Netz. Der Einfluss auf die veränderte Laufzeit des Victim Netzes lässt sich unter Annahme eines gleichzeitigen Schaltvorgangs von Victim und Aggressor wie folgt beschreiben [43]:

$$\Delta t_D \sim \frac{C_{K_{eff}}}{C_{K_{eff}} + C_{stat}} \cdot \frac{1}{t_{Siq}^{Agr}}$$

(3.11)

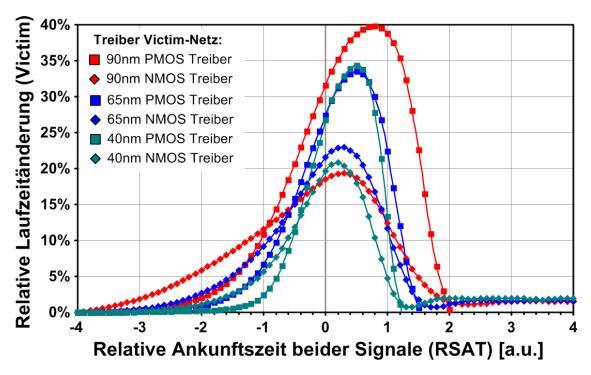

$C_{Keff}$  bezeichnet die effektive Koppelkapazität,  $C_{stat}$  die statische Kapazität des Victim Netzes, die sich aus der Leitungskapazität  $C_{Ltg}$  zu nicht schaltenden Netzen sowie den Diffusionskapazitäten von VP1, VN1 und den Gatekapazitäten von VP2, VN2 zusammensetzt. Die Koppelkapazität beinhaltet den erhöhten Wert der im statischen Fall wirkenden Kapazität  $C_K$ , deren effektiver Wert durch den Miller-Effekt bei schaltendem Aggressor steigt [57]. Dabei hängt der Miller-Effekt von der Steilheit der Signalflanken ab, d.h. je steiler die Signalflanke des Aggressornetzes  $t_{Sig}^{Agr}$ , desto höher die Laufzeiterhöhung [58]. Zusätzlich hängt die Größe der Laufzeitänderung vor allem von der zeitlichen Synchronität der Signalwechsel auf Aggressor und Victim-Netz ab (Relative Signal Ankunftszeit RSAT). Generell gilt, je größer der zeitliche Abstand zwischen den jeweiligen Signalwechseln, desto kleiner die Laufzeitänderung [59].

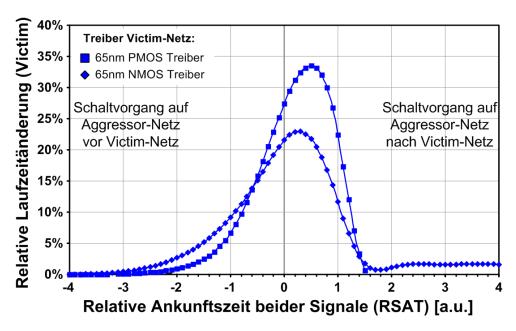

Bild 3.9 zeigt die in 65nm simulierte Laufzeiterhöhung bei entgegengesetzt schaltenden Aggressor- und Victim-Netzen in Abhängigkeit der zeitlichen Synchronität

Bild 3.9: Simulierte crosstalk-bedingte Laufzeiterhöhung der in Bild 3.8 gezeigten Testschaltung in 65nm CMOS ( $V_{DD} = V_{DD,nom} + 10\%$ , T=27°C).

beider Signalwechsel. Bei schwacher Flanke am Victim-Netz (PMOS-Treiber) und steiler Flanke am Aggressor-Netz (NMOS Treiber) ist bei zeitlicher Synchronität der Signalwechsel ein deutlich erhöhter Einfluss auf die Laufzeit zu erkennen als im umgekehrten Fall. Dies verdeutlicht die Abhängigkeit des Effektes von der Flankensteilheit an den gekoppelten Netzen.

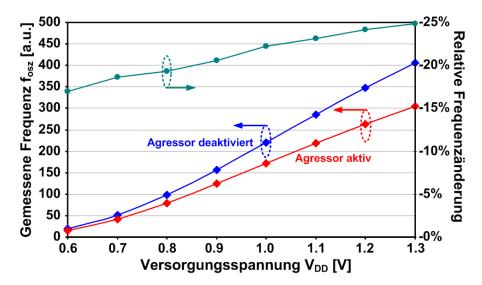

Bild 3.10 zeigt die gemessene Frequenz eines Ringoszillators mit Crosstalk-Struktur, d.h. kapazitiv gekoppelten Leitungsstrukturen als Lastelemente, in 45nm CMOS Technologie bei deaktiviertem und aktiviertem Aggressor. Bei steigender Versorgungsspannung erhöht sich die Steilheit der Signalflanken und die effektive Last am Crosstalk-behafteten Netz erhöht sich aufgrund des stärker wirkenden Miller-Effektes. Somit nimmt die relative Frequenzabnahme mit steigendem  $V_{DD}$  zu.

Insbesondere Netze mit starker Kopplung zu benachbarten Signalleitungen und einem geringen Anteil der Gatterlast (Fanout) sind potentiell anfällig für Crosstalk. Derartige Netzstrukturen sind vor allem in Bussen und im Taktbaum zu finden, die Signale über lange Strecken auf dem Chip verteilen. Für Leitungen, die das Taktsignal führen, werden deshalb alle benachbarten Leitungen oftmals mit zweifachem Minimalabstand (double spacing) positioniert, um den Anteil der Koppelkapazität an der Gesamtkapazität des Netzes zu verringern [60]. Somit wird ein Crosstalkinduzierter Beitrag zum Clock Jitter deutlich reduziert. Für kritische Strukturen im Taktbaum und in Busstrukturen werden zahlreiche Maßnahmen wie z.B. Gate-Sizing (Anpassung der Gattertreiberstärken an Victim- und Aggressor-Netz) [61], relative Signalverzögerung [62], Abschirmung (Shielding) [63], Kodiertechniken für Busstrukturen [64] usw. angewandt, um den Beitrag der Crosstalk induzierten Laufzeitschwankung gering zu halten. In [65] werden diese und weitere Techniken zusammengefasst und einzeln diskutiert.

Bild 3.10: Gemessene Frequenz einer Crosstalk-Struktur in 45nm low-power CMOS Technologie bei  $T=27^{\circ}C$ .

#### 3.1.3 Alterungseffekte

Neben statischen Prozessvariationen verändern Alterungseffekte die Transistoreigenschaften und beeinflussen somit Gatter- und Pfadlaufzeiten. Die für die Geschwindigkeit der Schaltung relevantesten Alterungseffekte werden im Folgenden diskutiert:

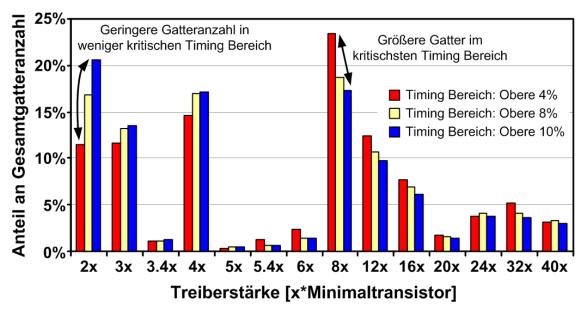

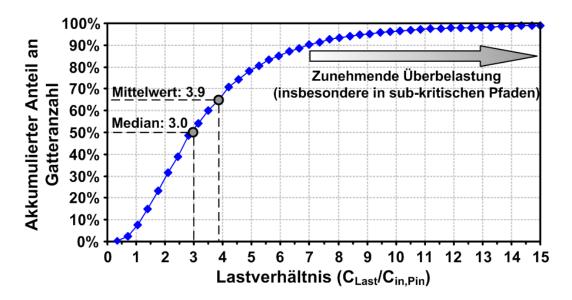

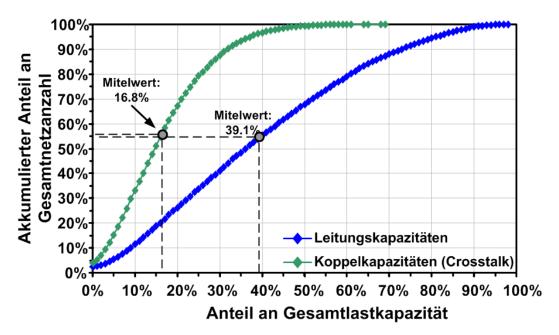

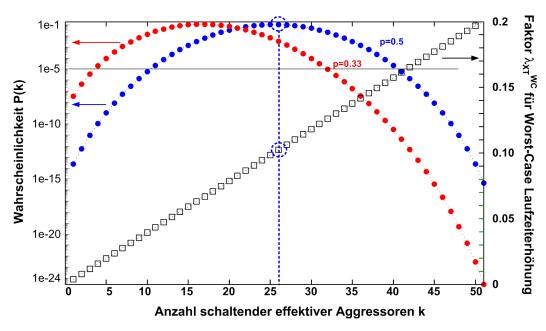

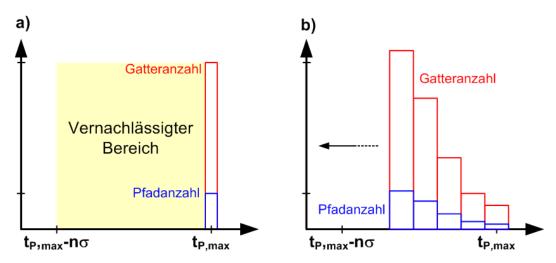

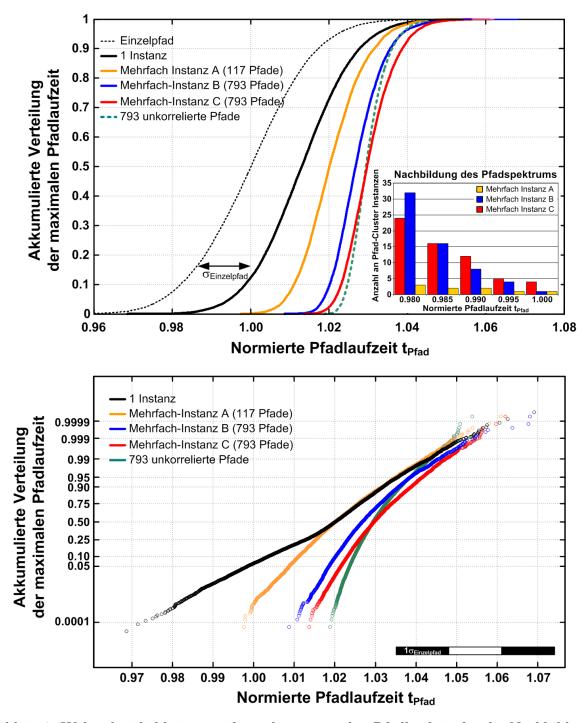

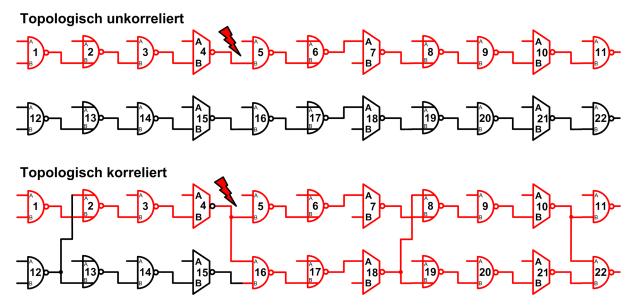

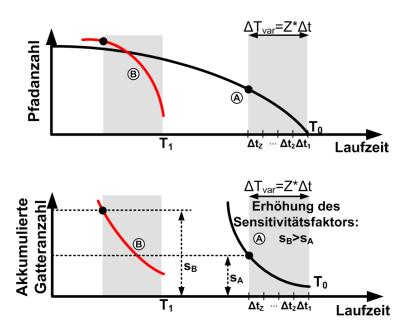

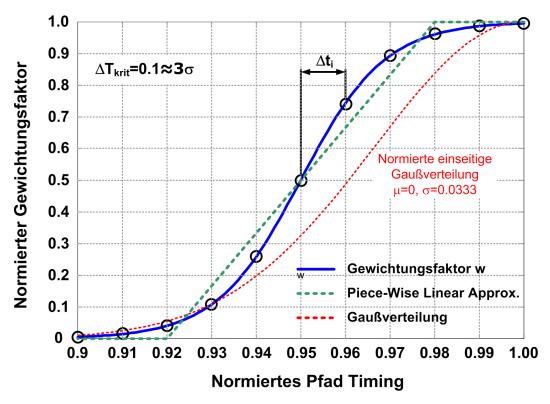

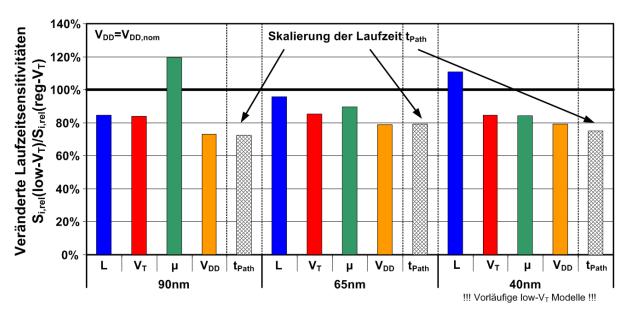

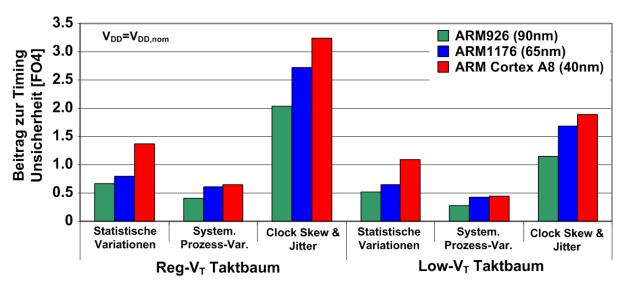

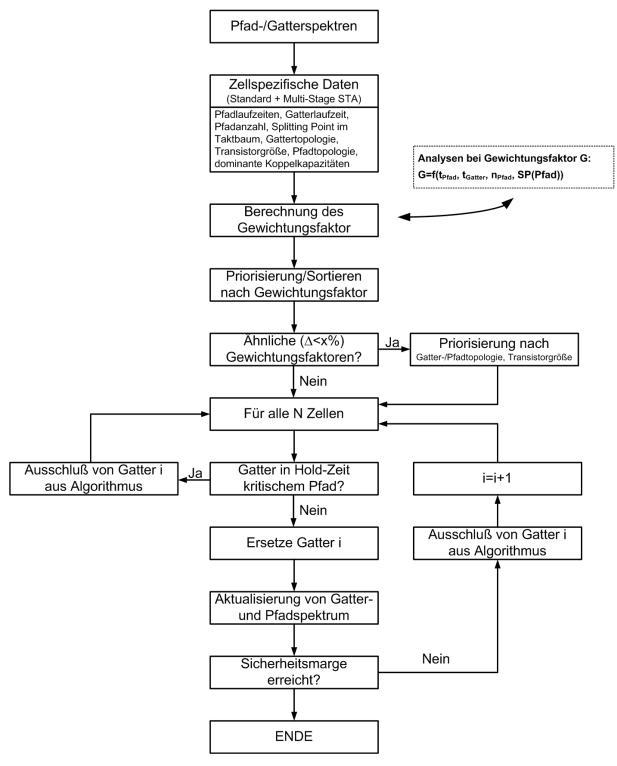

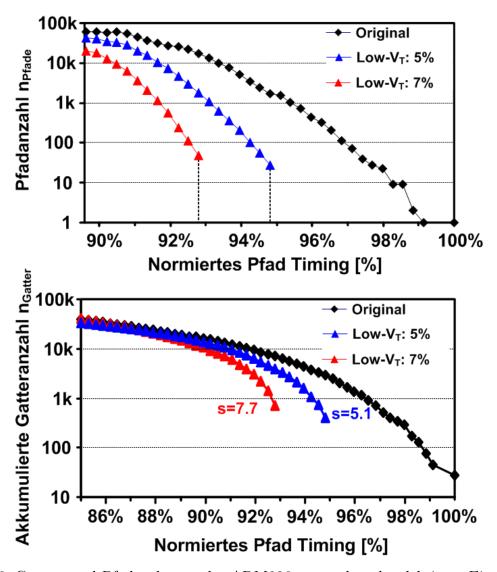

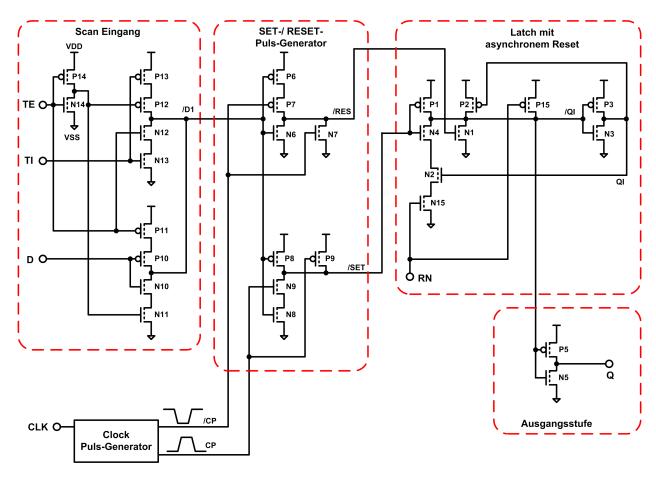

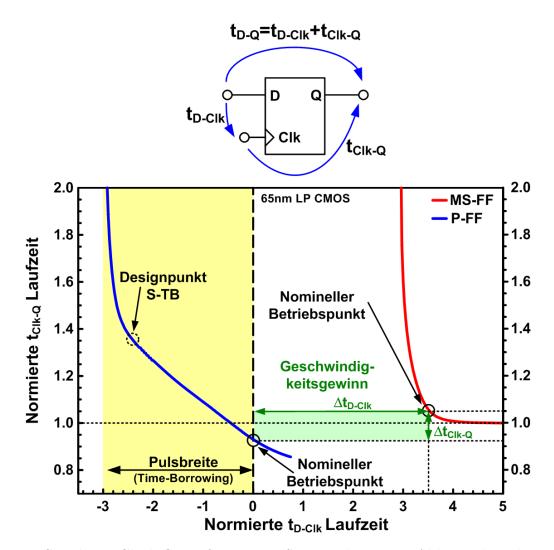

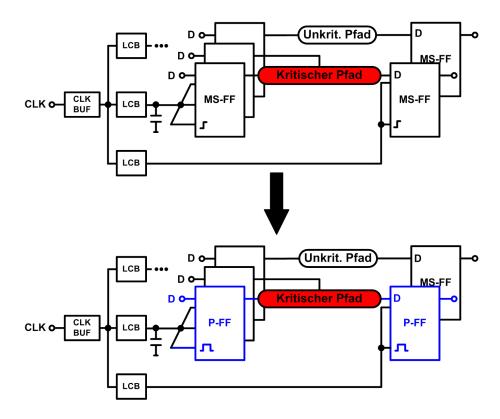

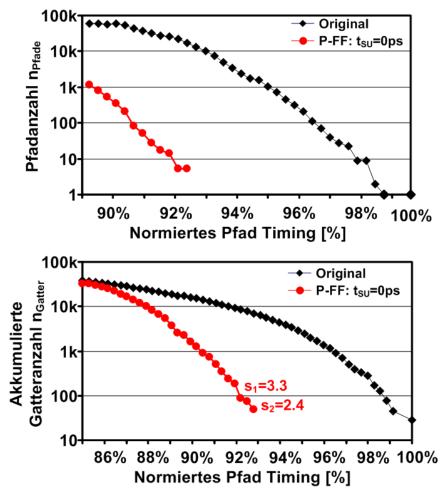

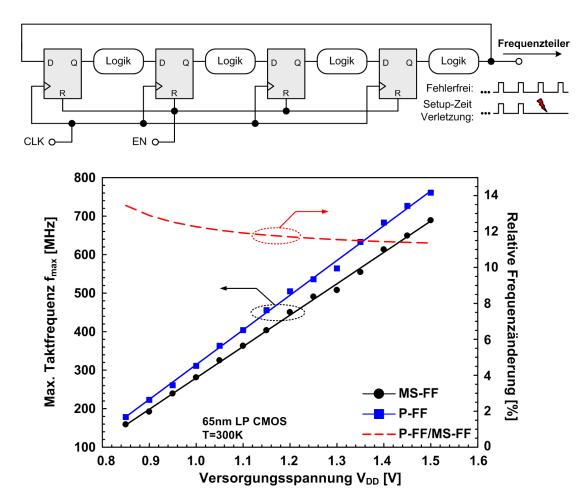

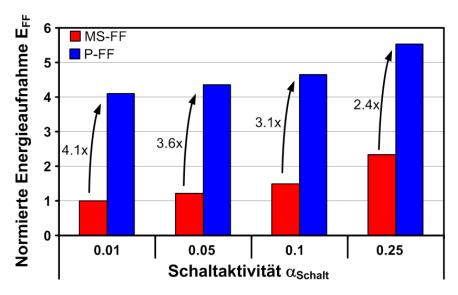

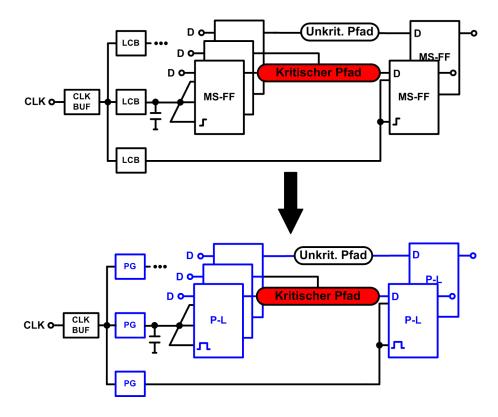

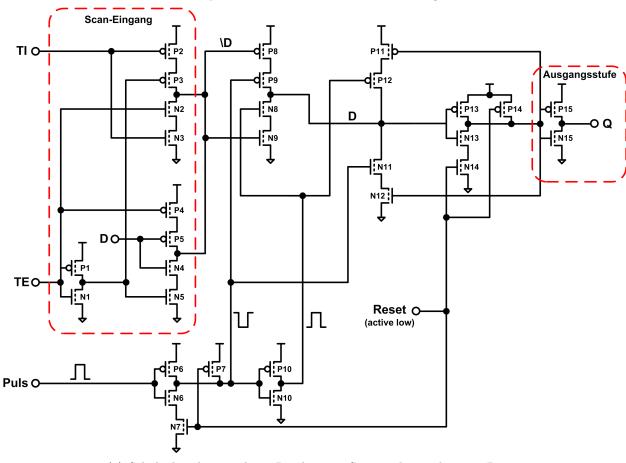

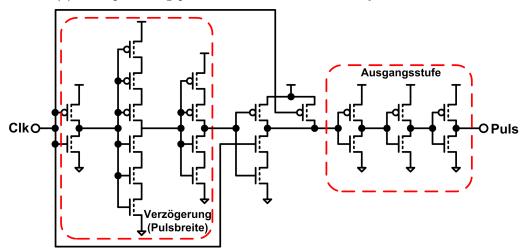

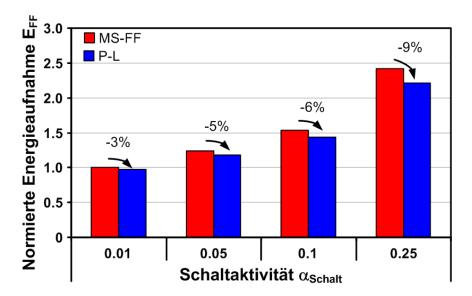

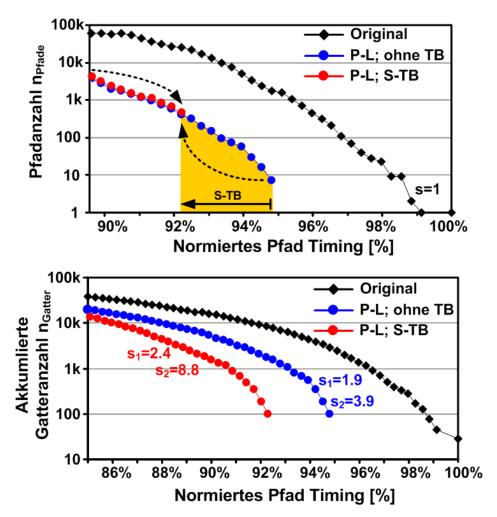

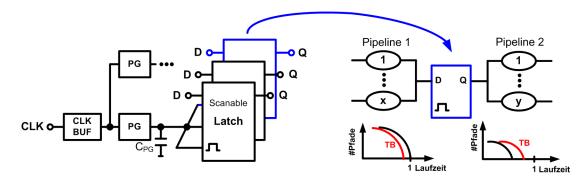

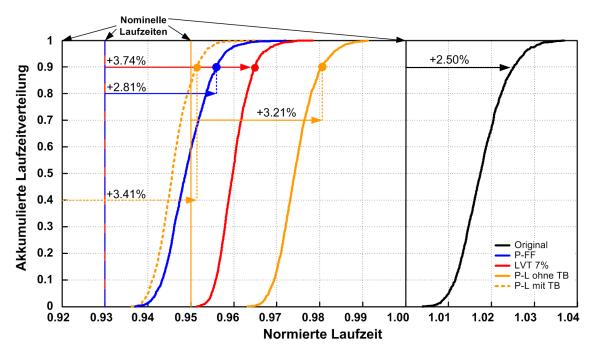

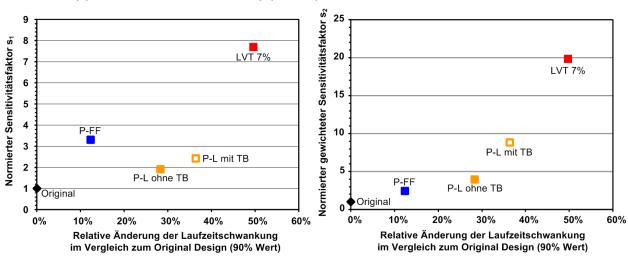

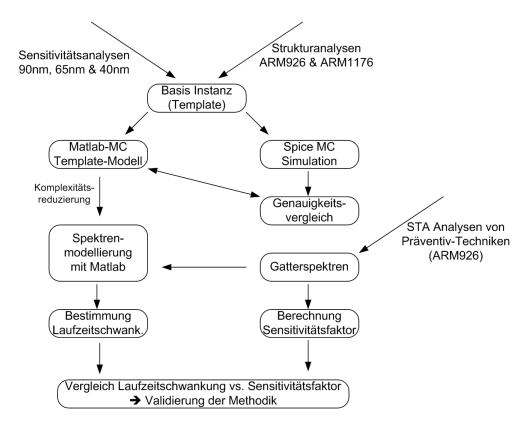

#### • Negative/Positive Bias Temperature Instability (NBTI/PBTI):