# Inference of Large Phylogenetic Trees on Parallel Architectures

Michael Ott

# TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Rechnertechnik und Rechnerorganisation / Parallelrechnerarchitektur

Inference of Large Phylogenetic Trees on Parallel Architectures

### Michael Ott

Vollständiger Abdruck der von der Fakultät für Informatik der Technischen Universität München zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften (Dr. rer. nat.)

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr. H. M. Gerndt

Prüfer der Dissertation: 1. Univ.-Prof. Dr. A. Bode

2. TUM Junior Fellow Dr. A. Stamatakis

Die Dissertation wurde am 15.07.2010 bei der Technischen Universität München eingereicht und durch die Fakultät für Informatik am 08.10.2010 angenommen.

# Abstract

Due to high computational demands, the inference of large phylogenetic trees from molecular sequence data requires the use of HPC systems in order to obtain the necessary computational power and memory. The continuous explosive accumulation of molecular data, which is driven by the development of cost-effective sequencing techniques, amplifies this requirement additionally. Furthermore, a continuously increasing degree of parallelism is necessary in order to exploit the performance of emerging multi-core processors efficiently.

This dissertation describes scalable parallelization schemes for the inference of large phylogenetic trees as well as tangible implementations of those which also eliminate memory requirements as a limiting factor for phylogenetic analyses. Additionally, it pinpoints the properties of current multi-core shared and distributed memory architectures and describes novel approaches for their efficient exploitation.

# Acknowledgments

Many people have contributed to the success of this work. First of all, I would like to thank Prof. Dr. Arndt Bode for providing such a supportive working environment at the Lehrstuhl für Rechnertechnik und Rechnerorganisation (LRR) and for the freedom he granted me for my research over the last years. I am particularly grateful to Dr. Alexandros Stamatakis who has been accompanying and supporting me since my undergraduate studies and spent a great effort on supervising my work. Furthermore, I am very thankful to the numerous helpful colleagues at the LRR – too many to be named individually – who have offered their advice when it was needed and supported me in many different ways.

My position at the LRR was funded by KONWIHR, the Bavarian Competence Network for Technical and Scientific High Performance Computing. KONWIHR is an initiative by the Bavarian State Ministry of Sciences, Research and the Arts for supporting research in computationally challenging scientific domains that require the use of High Performance Computing in order to obtain new knowledge and insights.

# Contents

| 1        | Intr | roduction                                  | 1 |

|----------|------|--------------------------------------------|---|

|          | 1.1  | Motivation                                 | 1 |

|          | 1.2  | Scientific Contribution                    | 3 |

|          | 1.3  | Structure of the Thesis                    | 4 |

| <b>2</b> | Phy  | vlogenetic Tree Inference                  | 5 |

|          | 2.1  | Introduction                               | 5 |

|          | 2.2  | The Optimization Problem                   | 7 |

|          | 2.3  | Models of Sequence Evolution               | 8 |

|          |      | 2.3.1 The Substitution Rate Matrix         | 9 |

|          |      | 2.3.2 The Substitution Probability Matrix  | 1 |

|          |      | 2.3.3 Rate Heterogeneity                   | 1 |

|          | 2.4  | Distance Methods                           | 3 |

|          |      | 2.4.1 Least-Squares                        | 3 |

|          |      | 2.4.2 UPGMA                                | 3 |

|          |      | 2.4.3 Neighbor-Joining                     | 4 |

|          |      | 2.4.4 Objections Against Distance Methods  | 4 |

|          | 2.5  | Maximum Parsimony                          | 5 |

|          | 2.6  | Maximum Likelihood                         | 5 |

|          |      | 2.6.1 The Phylogenetic Likelihood Function | 6 |

|          |      | 2.6.2 The Pulley Principle                 | 0 |

|          |      | 2.6.3 Optimization of the Likelihood Score | 1 |

|          | 2.7  | Bootstrapping                              | 3 |

|          | 2.8  | Bayesian Inference                         | 5 |

|          | 2.9  | Programs for Phylogenetic Tree Inference   | 7 |

|          |      | 2.9.1 RAxML                                | 7 |

|          |      | 2.9.2 PHYLIP                               | 8 |

|          |      | 2.9.3 GARLI                                | 9 |

|          |      | 2.9.4 MrBayes                              | 9 |

|          |      | 2.9.5 PAUP*                                | 0 |

VIII

| 3 | Sha | ared Memory Multiprocessors 31                                             |

|---|-----|----------------------------------------------------------------------------|

|   | 3.1 | Introduction                                                               |

|   | 3.2 | Multi- and Many-Cores                                                      |

|   |     | 3.2.1 The Power Wall                                                       |

|   |     | 3.2.2 From Single- to Multi-Core                                           |

|   | 3.3 | The Memory Subsystem                                                       |

|   |     | 3.3.1 The Memory Wall                                                      |

|   |     | 3.3.2 Memory Hierarchies                                                   |

|   |     | 3.3.3 UMA and NUMA Architectures                                           |

|   | 3.4 | Shared Memory Programming                                                  |

|   | 3.5 | Distributed Memory Programming on Shared Memory Architectures 40           |

|   | 3.6 | Efficient Exploitation                                                     |

|   |     | 3.6.1 Shared Caches                                                        |

|   |     | 3.6.2 Dealing with the Memory Wall                                         |

|   |     | 3.6.3 Thread Pinning                                                       |

|   | 3.7 | An Outlook on Automated Thread Pinning: autopin                            |

| 4 | Dis | tributed Memory Systems 55                                                 |

|   | 4.1 | Introduction                                                               |

|   | 4.2 | Characteristics                                                            |

|   | 4.3 | The Message-Passing Interface MPI                                          |

|   |     | 4.3.1 MPI-1 Functionality                                                  |

|   |     | 4.3.2 The MPI Profiling Interface                                          |

|   | 4.4 | An Outlook on Automated Performance Analysis                               |

|   |     | 4.4.1 Automated Performance Analysis                                       |

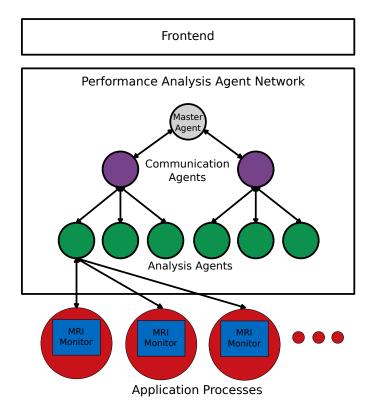

|   |     | 4.4.2 The Architecture of Periscope                                        |

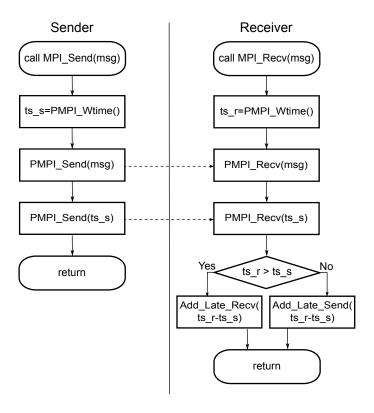

|   |     | 4.4.3 Identifying MPI Performance Properties 67                            |

| 5 | Par | rallel Phylogenetic Tree Inference 71                                      |

|   | 5.1 | Introduction                                                               |

|   | 5.2 | Sources of Parallelism                                                     |

|   |     | 5.2.1 Embarrassing Parallelism                                             |

|   |     | 5.2.2 Inference Parallelism                                                |

|   |     | 5.2.3 Loop-level Parallelism                                               |

|   | 5.3 | Parallel Implementations of RAxML                                          |

|   |     | 5.3.1 Exploitation of Loop-level Parallelism                               |

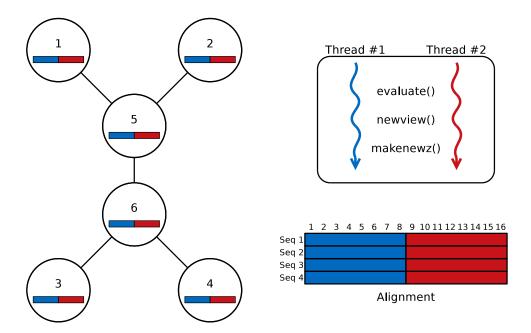

|   |     | 5.3.2 PThreads Parallelization                                             |

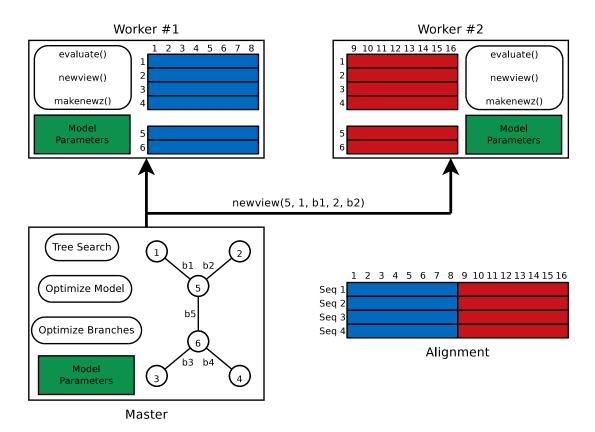

|   |     | 5.3.3 Simultaneous Exploitation of Loop-level and Embarrassing Parallelism |

|   |     | with MPI                                                                   |

| C0 | ONTE  | ENTS                                              | IX  |

|----|-------|---------------------------------------------------|-----|

| 6  | Eva   | luation                                           | 89  |

|    | 6.1   | Experimental Setup                                | 89  |

|    | 6.2   | OpenMP                                            | 91  |

|    | 6.3   | PThreads                                          | 95  |

|    | 6.4   | MPI                                               | 99  |

|    | 6.5   | Performance of the Hybrid MPI/MPI Parallelization | 104 |

| 7  | Con   | iclusion and Future Work                          | 107 |

|    | 7.1   | Conclusion                                        | 107 |

|    | 7.2   | Future Work                                       | 109 |

| Bi | bliog | graphy                                            | 111 |

# Chapter 1

# Introduction

This chapter provides the motivation for developing methods and tools for the inference of large phylogenetic trees, summarizes the scientific contribution of the work, and outlines the structure of this thesis.

#### 1.1 Motivation

The evolutionary history of all life forms on earth and their relation to each other – often referred to as The Tree of Life – has preoccupied mankind for centuries. While a comprehensive tree of life mainly serves human curiosity, phylogenetic trees at a lower scale that only comprise a smaller group of species have practical applications in many scientific fields. Besides their importance in systematic studies, phylogenetic trees allow for, predicting the evolution of infectious diseases [22] as well as the functions of uncharacterized genes [33] and can also be utilized for studying the dynamics of microbial communities [35]. Additionally, they play an important role in the discovery of new drugs [16] and vaccines [51, 64] and are even used in modern forensics [114].

As the number of potential applications of phylogenetic trees is steadily growing, there is an increasing demand for tools that allow for inferring such trees from molecular data like DNA sequences efficiently. This demand is amplified by the continuously growing amount of molecular data: recent advances in cost-effective high-throughput sequencing techniques such as, e.g., pyrosequencing [122] have generated an unprecedented molecular data flood. Public databases like GenBank [9] grow exponentially and with steadily decreasing costs for wholegenome sequencing – the 1,000\$ human genome is within reach – this development is about to continue.

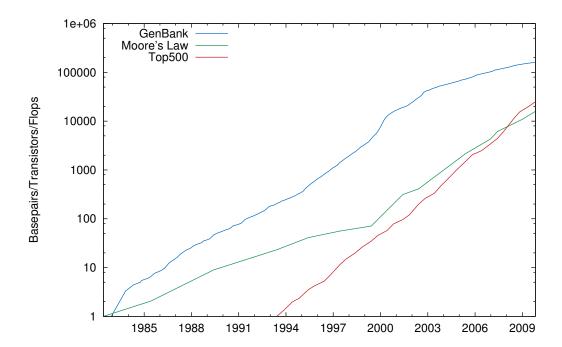

Unfortunately, the computational power of modern microprocessors does not keep pace with this data flood. Although Moore's law still holds and suggests that the performance of microprocessors doubles approximately every two years, there is an increasing gap – which we call the bio-gap – between the growth rates of molecular sequence data and microprocessor performance (see Figure 1.1). Additionally, over the last couple of years this performance increase was mainly achieved by the introduction of multi-core CPUs, i.e., by increasing the number

Figure 1.1: Growth of molecular data available in GenBank, of microprocessor performance according to Moore's Law, and of aggregate performance of the Top500 supercomputer list.

of cores per CPU while the actual performance per core remained constant. Consequently, sequential applications experienced almost no performance gain in recent years but only parallel applications that allow for utilizing multiple cores simultaneously were able to benefit from the latest developments in computer technology. Hence, in order to exploit the computational performance of modern multi-core processors for phylogenetic analyses, appropriate parallelization schemes need to be devised that allow for distributing the workload over multiple processor cores.

However, even a highly efficient parallelization approach for multi-core processors will not close the bio-gap but will only alleviate its impact. Closing the gap between computational power and data growth will require computer systems that experience performance increases at a rate that is significantly higher than the growth rate of molecular databases. The only class of systems that meets this criterion are high performance computing (HPC) systems. As can be seen from Figure 1.1, the aggregate performance of the systems in the Top500 supercomputer list [3] grows significantly faster than the performance of individual microprocessors and even outperforms the growth rate of GenBank. The only viable solution for closing the bio-gap therefore is to utilize HPC systems that provide the necessary computational power for dealing with the molecular data flood. Yet, the same trend that can been witnessed for microprocessors, also applies to supercomputers: exploiting the performance of those systems requires a continuously increasing level of parallelism of the utilized applications. As of June 2010 there is not a single system in the Top500 list with less than 1024 processor cores and the number one

system even comprises 224,162 cores. Utilizing such HPC resources for large-scale phylogenetic analyses therefore requires parallel applications that are able to scale up to thousands of cores.

Furthermore, the huge amount of molecular data that is to be used for phylogenetic analyses poses challenges not only in terms of computational performance but also in terms of memory requirements. Given that the memory footprints of large-scale analyses can easily exceed 100 GB and that due to high costs, computers are typically equipped with less than 128 GB of main memory, memory requirements are effectively a limiting factor for phylogenetic analyses. This also applies to supercomputers, although they have a significantly larger amount of aggregate main memory. However, modern supercomputers are typically designed as distributed memory architectures that comprise hundreds or thousands of compute nodes, each of which is equipped with a rather low amount of memory (typically less than 32 GB). Any parallelization approach that aims at facilitating such large-scale analyses therefore needs to distribute not only the computational workload over thousands of cores but also the data structures that are required for the computations over multiple distributed memory nodes.

Besides the application-specific challenges, the parallel computer architectures that have emerged over recent years pose new challenges of their own for the development of highly efficient applications: the multi-core revolution led to parallel microprocessors and computer systems with heterogeneous properties that need to be accounted for in order to avoid performance bottlenecks. The massive parallelism that is required for exploiting the performance of state-of-the-art HPC systems requires new approaches not only in terms of highly parallel applications but also in terms of scalable development and debugging tools.

### 1.2 Scientific Contribution

This dissertation is an interdisciplinary work in Bioinformatics and Computer Science and as such comprises scientific contributions to both domains. These contributions can generally be divided into three categories:

Firstly, the characteristics of emerging multi-core architectures have been thoroughly analyzed and potential pitfalls and bottlenecks that could impact application performance on such systems have been described. Additionally, the autopin framework has been developed which facilitates automated and performance-aware thread placement on multi-core systems and hence maximizes the parallel efficiency on such systems without user interaction.

Secondly, a scalable approach for the automatic detection of performance bottlenecks in large-scale MPI (Message Passing Interface) applications that is solely based on summary information has been developed and integrated into the Periscope tool for automatic performance analysis.

Thirdly, a generic parallelization approach for Maximum Likelihood based tools for phylogenetic tree inference has been presented and implemented in RAxML. It allows for exploiting loop-level parallelism in the phylogenetic likelihood function on shared memory as well as distributed memory architectures and overcomes memory requirements as a limiting factor for phylogenetic analyses.

Furthermore, the MPI-based parallelization of RAXML has been used to conduct the most computationally intensive phylogenetic study to date [68]: over 2.25 million CPU hours have been utilized for analyzing several datasets of 94 bilaterian animals, the largest one comprising 270,580 basepairs in 1,487 genes (see respective press releases by Technische Universität München on October 29, 2009 and Brown University on September 23, 2009). The aim of the study was to assess the root of bilaterian animals and was conducted in co-operation with 15 researchers from the United States, France, Germany, Sweden, Spain, and the United Kingdom.

Moreover, the MPI parallelization has recently been included as 125.RaxML in the SPEC MPI2007 v2.0 benchmark suite [102, 110] which is used for assessing the performance of high performance computers. Technische Universität München and Leibniz Computing Centre jointly published a respective press release on April 14, 2010 on this occasion, that has also been covered by the popular press.

The scientific results of this thesis have been incrementally published in eight peerreviewed conference papers [141, 152, 112, 113, 109, 139, 140, 110] and five journal articles [111, 86, 138, 52, 68]. The papers are available for download in PDF format at http://www.lrr.in.tum.de/~ottmi.

#### 1.3 Structure of the Thesis

The remainder of this thesis is organized as follows: Chapter 2 introduces the basic concepts and methods for inferring phylogenetic trees from molecular data. Chapter 3 gives an overview of the properties of (multi-core) shared memory systems and describes approaches for exploiting their performance efficiently. The Characteristics of distributed memory systems as well as the prevailing program paradigm (MPI) and concepts for performance optimizations on those systems are discussed in Chapter 4. Potential sources of parallelism in phylogenetic analyses and tangible parallel implementations are described in Chapter 5. The performance of these implementations is evaluated in Chapter 6 and Chapter 7 provides a conclusion of the thesis and gives an outlook on future work.

# Chapter 2

# Phylogenetic Tree Inference

This chapter introduces the basic concepts of phylogenetic tree inference and the associated optimization problem. Furthermore, it describes the most commonly used methods and how they model the evolutionary process. Finally, it provides an overview over state-of-the-art tools for inferring phylogenetic trees.

### 2.1 Introduction

Phylogenetic trees represent the evolutionary history of a set of organisms. In traditional phylogenetics, which more or less date back to the 19th century and Charles Darwin's seminal book The Origin of Species [28], morphological data was used to derive the evolutionary relationship between individual organisms. By its nature, such data is imprecise and for many organisms it is hard if not impossible to acquire: while it might be possible to classify some species by certain distinguishing characteristics like the presence of wings, shape of bones, size of certain organs, etc., such characterizing properties may be hard to define for very small organisms like bacteria or viruses. Moreover, morphological properties may not allow for comparing such small organisms with complex organisms like mammals or for comparing very morphologically distant organisms in general. Additionally, the assumption that similar body parts imply a relationship between two species may be misleading, as they could also have developed from independent lineages (so-called homoplasy). For example, bats and sparrows both have wings, but they descended from very different lineages: sparrows belong to the class of birds while bats belong to the class of mammals.

In contrast, molecular phylogenetics utilizes nucleotide sequences which can encode genes or amino acid sequences which can encode proteins to classify organisms. Such sequences can be used as input data for computational phylogenetic algorithms that allow for deriving a phylogenetic tree of the species represented by these sequences. In general, these sequences are composed of a series of characters drawn from a limited alphabet. There are 4 possible characters in the case of nucleotide sequences (A, C, G, T for DNA data and A, C, G, U for RNA data) and 20 possible characters (A, C, D, E, F, G, H, I, K, L, M, N, P, Q, R, S, T, V, W, Y) in the

case of amino acid sequences.<sup>1</sup>

Though some alignment-free methods exist (see [75] for an overview), most methods for molecular tree inference require the input data to be provided as multiple sequences alignment, which is a matrix whose lines consist of the sequences of the individual organisms. The sequences have to be aligned to each other such that all sites (i.e., the columns of the matrix) are homologous, which means that all characters are related by a common evolutionary history. Finding an optimal multiple sequences alignment is a NP-hard problem [151]. Multiple algorithms and heuristics have been proposed for this task, ranging from dynamic programming approaches [92], progressive techniques [105, 147], and iterative methods [18, 57] to hidden Markov models [74] and genetic algorithms [104]. However, all of these approaches are beyond the scope of this thesis and will therefore not be discussed. For the rest of this chapter we assume that the multiple sequences alignments we use as input for the phylogenetic tree inference are given. Keep in mind that the quality of the obtained tree topology highly depends on the quality of the input alignment.

In the context of computational phylogenetics, a phylogenetic tree is usually an unrooted, strictly bifurcating tree: every node has either none (terminal nodes) or exactly two child nodes (internal nodes). The terminal nodes (also called tips or leaves) of the tree represent the organisms for which we have sequences in the input data set, i.e., the organisms in whose phylogeny we are actually interested in. The internal nodes represent hypothetical extinct ancestors. Evolutionary events such as mutations of sites are modeled to occur along the branches of the tree, between ancestor and descendant. Depending on the method that is used for the inference of the phylogenetic tree, the branches of the tree may be weighted. In this case they could provide information, e.g., about the time that was needed for the sequence at the parent node to develop into the sequence at the child node.

Unrooted trees only describe the relatedness of the species represented by the molecular sequences at the terminal nodes of the tree topology. As opposed to rooted trees, they do not allow for any assumption about a single common ancestor which is contrary to the intuitive expectations one would have about a phylogenetic tree, especially a *Tree of Life*. Though it is easily possible to convert a rooted tree into an unrooted tree simply by removing the root, the contrary direction is not as straightforward. As every branch could be designated the root of the tree, additional knowledge about the ancestral relationships is needed to pick a reasonable one. It is common practice to add an additional so-called outgroup to the alignment and use this outgroup for rooting the tree after the inference has been completed. The outgroup species must not be closely related to any other species of the tree in order not to disturb the tree inference of the species one is actually interested in. However, using a too distant outgroup may also bias the phylogenetic analysis. For a detailed discussion on outgroup choice see [59].

<sup>&</sup>lt;sup>1</sup>The respective alphabet may be larger if ambiguous character encoding is allowed.

## 2.2 The Optimization Problem

Reconstructing phylogenetic trees from molecular data is a combinatorial optimization problem: given a certain number of feasible solutions and a scoring function that evaluates the quality of a solution according to some optimality criterion, we are searching for the solution that achieves the highest score.

In the context of phylogenetic tree inference, any tree topology that contains the species of interest is a feasible solution. That is, any binary unrooted tree that has all species assigned to its leaves is a potential candidate for the optimal phylogenetic tree. Thus, for a given sequence alignment containing n species, the feasible solutions are all binary unrooted trees with n leaves.

The scoring function evaluates a given tree topology and reduces its complexity to a single numerical value that is a measure for the fit of the tree to the data. Every scoring function relies on a model of evolution that describes the process of a molecular sequence evolving over time (see Section 2.3). The numerical value returned by the scoring function allows for comparing two tree topologies and deciding which topology fits the given molecular sequences better under the assumed model of evolution.

Besides the actual evolutionary model utilized, scoring functions can additionally be divided into two classes: distance methods and character-based methods. Distance methods initially compute pairwise distances of the molecular sequences and perform all following operations on these numerical values only. Thus, they loose information about the molecular sequences which might affect the trustworthiness of the obtained result. In contrast, character-based methods utilize the molecular sequences as a whole through the entire process. In general, distance methods are considered to be faster but less accurate than character-based methods. Actually, only two character-based methods are regularly used for phylogenetic tree inference: Maximum Parsimony (MP, see Section 2.5) and Maximum Likelihood (ML, see Section 2.6). The best known distance methods are described more closely in Section 2.4.

There have been extensive discussions over the last 25 years about the superiority of one method over the other. However, it is now widely accepted that Maximum Likelihood-based approaches obtain more accurate results [72, 124, 164]. Yet, this accuracy comes at a high price: Maximum Likelihood (ML) is by far the most expensive method regarding computational resources – memory as well as computations. Consequently, the computationally inexpensive distance methods or the less elaborate Maximum Parsimony approach are still used under some circumstances, for example for analyzing huge datasets whose computational requirements are prohibitive for more elaborate methods.

Regardless of the actual scoring function used, the algorithmic challenge in phylogenetic tree inference is due to the huge solution set of the optimization problem. The scoring function only gives a numerical measure for the fit of the tree to the input data. It does not provide any hint whether there is a better tree or how to optimize a given tree in order to improve the score. Hence, the naive approach for finding the optimal tree would be to create all feasible topologies and evaluate their quality by means of the scoring function. Unfortunately, the number of possible tree topologies grows factorially with the number of species. For n species the number

of possible binary unrooted trees T(n) is [31]:

$$T(n) = \prod_{i=3}^{n} (2i - 5)$$

(2.1)

A few exemplary figures for this formula are given in Table 2.1. Already for 50 species T becomes unimaginably large. Thus, enumeration and evaluation of all potential trees is not an option, regardless of the actual scoring function used. In fact, it has been shown for Maximum Likelihood [25] as well as for Maximum Parsimony [29] that finding the optimal tree is a NP-hard problem. Hence, the only feasible approach is to use heuristics that approximate the optimal solution. However, heuristics are – by their nature – not guaranteed to actually find it.

| # Species | # Possible Tree Topologies |

|-----------|----------------------------|

| 3         | 1                          |

| 4         | 3                          |

| 5         | 15                         |

| 6         | 105                        |

| 7         | 945                        |

| 10        | 2,027,025                  |

| 15        | 7,905,853,580,625          |

| 20        | $2.21 \cdot 10^{20}$       |

| 50        | $2.84 \cdot 10^{76}$       |

Table 2.1: Number of possible tree topologies for 3–50 species

As for most optimization problems, numerous heuristics have been proposed and implemented in different programs for phylogenetic inference. Section 2.9 gives an overview over several state-of-the-art programs and the heuristics they implement. Distance methods often use greedy algorithms that build a tree by consecutively adding new nodes to the topology according to the scoring function used. Discrete methods frequently implement hill-climbing algorithms: initially they create a tree topology and reorganize it step by step in order to improve its quality or more precisely, its score under the given optimality criterion. The typical standard topological rearrangement moves which are used for this task are Nearest Neighbor Interchange (NNI), Subtree Pruning and Re-grafting (SPR), and Tree Bisection and Reconnection (TBR). In general all of these moves result in removing a sub-tree and inserting it at another position in the tree such that the score of the tree topology improves. A detailed description of these rearrangement moves is given by Swofford et. al in [145].

# 2.3 Models of Sequence Evolution

Every phylogenetic analysis relies on a model of sequence evolution, i.e., a model that describes the process of one sequence evolving into another. Maximum Parsimony-based approaches assume a model of minimum evolution that mainly considers the number of differing sequence characters when determining the relatedness of two species. This specific model will be described in Section 2.5 along with the Maximum Parsimony approach itself. In contrast, most distance methods as well as Maximum Likelihood-based approaches utilize explicit probabilistic evolutionary models. These models usually assume individual sequence sites to be evolving independently of each other. The change at any particular site from one character state to another state is commonly modeled using continuous-time Markov chains with the potential sequence states being the states of the chain (e.g. A,C,G,T for DNA sequences). The main feature of a Markov chain is the so-called Markovian property: it has no memory. Thus, the probability of a chain changing its state solely depends on its current state. Any state that the chain might have had previously will not affect any future state change. Additionally the state changes of a sequence site are assumed to be time-reversible, which means that the evolutionary process is identical regardless in which direction of time it is followed: if a site has state s at present, the probability that it has emerged from state r in the past is identical to the probability that it will emerge into state r in the future. Note that the reversibility is assumed because of mathematical reasons and not because of biological reasons. Though non-reversible models have also been proposed (see, e.g., [13]), this thesis will concentrate on reversible models as most programs for phylogenetic inference require this property for an efficient implementation.

Appropriate models have been developed for various molecular sequence types such as nucleotide sequences (see next Section) as well as amino acid [30, 83, 154] or codon sequences [55, 103]. In general, phylogenetic analyses are not restricted to molecular sequences. Any sequence type that sufficiently characterizes a species and for which a biologically meaningful model of sequence evolution is available is suitable for phylogenetic analyses. As long as the above listed properties are met (independently evolving sites, Markovian property, time-reversibility), new models can easily be added to existing applications for phylogenetic analyses. For example, discrete morphological data can also be used for computational phylogenetic tree inference [90].

#### 2.3.1 The Substitution Rate Matrix

The process of molecular evolution is modeled by a continuous-time Markov process. Such a process is defined by the transition rates  $q_{ij}$  that describe the instantaneous rate of change from chain state i to j: let X(t) be the state of the chain at time t. If the chain is in state i at time t, the probability that it has made the transition to some other state  $j \neq i$  after time  $\Delta t$  is given by

$$Pr\{X(t+\Delta t) = j|X(t) = i\} = q_{ij}\Delta t. \tag{2.2}$$

The transition rates  $q_{ij}$  are specified by the transition rate matrix Q which is often also called substitution rate matrix or instantaneous rate matrix in the context of models for molecular evolution. The matrix has dimension  $n \times n$  where n is the number of possible states of the data. For simplicity, we will concentrate on models for DNA data in the following, i.e., n=4 and the possible character states are A,C,G,T. However, analogous models are available for amino acid sequences (n=20) as well as codon sequences (n=61). The principles described in this

chapter apply to them accordingly. The j-th entry of the i-th row of the matrix corresponds to the transition rate  $q_{ij}$ .

The most general form of Q for DNA data is given by equation (2.3) (rows and columns are ordered by the alphabetical order of the bases A,C,G,T):

$$Q = \begin{pmatrix} -\mu(a\pi_C + b\pi_G + c\pi_T) & \mu a\pi_C & \mu b\pi_G & \mu c\pi_T \\ \mu g\pi_A & -\mu(g\pi_A + d\pi_G + e\pi_T) & \mu d\pi_G & \mu e\pi_T \\ \mu h\pi_A & \mu j\pi_C & -\mu(h\pi_A + j\pi_C + f\pi_T) & \mu f\pi_T \\ \mu i\pi_A & \mu k\pi_C & \mu l\pi_G & -\mu(i\pi_A + k\pi_C + l\pi_G) \end{pmatrix}$$

(2.3)

The parameter  $\mu$  represents the mean instantaneous substitution rate from one nucleotide to another. The relative rate parameters a, b, ..., l correspond to each of the possible 12 transformation types between distinct bases. The product of the mean instantaneous substitution rate and a relative rate parameter constitutes a rate parameter. However,  $\mu$  is usually set to 1 and a, b, ..., l are scaled such that the average substitution rate is 1. It is assumed that the nucleotide substitutions are at equilibrium, i.e., the proportions of the individual bases stay constant over time. Thus, the overall base composition of the input alignment, i.e., the occurrence frequency of the individual bases A,C,G,T – often called base frequencies – as represented by the parameters  $\pi_A, \pi_C, \pi_G, \pi_T$  also serves as the stationary distribution of the Markov process  $\pi = (\pi_A, \pi_C, \pi_G, \pi_T)$  and constitutes the prior probabilities. The diagonal elements of Q are chosen such that every row sums up to zero, i.e.,  $q_{ii} = -\sum_{i \neq j} q_{ij}$ . Thus  $-q_{ii}$  describes the rate at which the Markov chain leaves state i, that is, the substitution rate of nucleotide i.

The proportion of time the Markov chain spends in state i is described by  $\pi_i$ , whereas  $q_{ij}$  is the rate at which the chain's state changes from i to j. Hence,  $\pi_i q_{ij}$  describes the amount of flow from state i to j and  $\pi_j q_{ji}$  the flow in the opposite direction. As discussed above, the Markov chain used to model the molecular substitution process usually needs to be time-reversible. According to the *detailed-balance* condition, this requires the following equation to hold:

$$\pi_i q_{ij} = \pi_j q_{ji}$$

, for all  $i \neq j$ . (2.4)

However, the matrix of equation (2.3) does not meet this requirement as the relative rate parameters are not symmetric, e.g.,

$$\pi_A q_{AC} = \pi_A \mu a \pi_C \neq \pi_C \mu g \pi_A = \pi_C q_{CA}. \tag{2.5}$$

Consequently, we need to modify Q accordingly by setting g = a, h = b, i = c, j = d, k = e, l = f, i.e., reducing the number of rate parameters and hence enforcing symmetry:

$$Q = \begin{pmatrix} -(a\pi_C + b\pi_G + c\pi_T) & a\pi_C & b\pi_G & c\pi_T \\ a\pi_A & -(g\pi_A + d\pi_G + e\pi_T) & d\pi_G & e\pi_T \\ b\pi_A & d\pi_C & -(h\pi_A + j\pi_C + f\pi_T) & f\pi_T \\ c\pi_A & e\pi_C & f\pi_G & -(c\pi_A + e\pi_C + f\pi_G) \end{pmatrix}$$

(2.6)

Note that, additionally  $\mu$  has been set to 1 as described above for better readability. The evolutionary model described by this simplified matrix is known as the *General Time-Reversible* (GTR) model [88]. It allows for four distinct base frequencies and 6 rate parameters. Other models have been proposed which utilize an even more simplified matrix to reduce computational

demands. This is achieved by further reducing the number of rate parameters and/or the number of base frequencies. The best known models are JC69 by Jukes and Cantor [84] (1 rate parameter, equal base frequencies), F81 by Felsenstein [42] (1 rate parameter, 2 base frequencies), K2P by Kimura [85] (2 rates, equal base frequencies), and HKY85 by Hasegawa, Kishino, and Yano [66] (2 rates, 4 base frequencies). However, these simple models have rarely been used for recent phylogenetic analyses [121] as GTR now is feasible thanks to efficient software implementations and powerful CPUs.

#### 2.3.2 The Substitution Probability Matrix

As mentioned above, any entry  $q_{ij}$  of the instantaneous rate matrix Q specifies the probability that a given nucleotide i will change to a different nucleotide j in an infinitely small time interval  $\Delta t$  (eq. (2.2)). However, to describe the process of molecular evolution sufficiently, we need a substitution probability matrix over time t > 0:  $P(t) = \{p_{ij}(t)\}$  with

$$p_{ij}(t) = Pr\{X(t) = j | X(0) = i\}.$$

(2.7)

P(t) describes the probability that a nucleotide in state i will evolve to state j after time t and is the solution to the differential equation

$$\frac{dP(t)}{dt} = P(t)Q, (2.8)$$

with the boundary condition P(0) = I, the identity matrix. This has the solution

$$P(t) = e^{Qt}. (2.9)$$

The exponential can be evaluated by decomposing Q into its eigenvalues and eigenvectors. For the simpler models like JC69, K2P, or HKY85 there exist closed form expressions of P that allow for a direct analytical computation of the matrix elements. For GTR however, the decomposition of Q has to be solved numerically as no closed form expression exists. See [89] for a closer discussion of potential numerical decomposition methods.

#### 2.3.3 Rate Heterogeneity

The GTR model described above as well as most other evolutionary models assume that all sites of the molecular sequences evolve at the same rate. Yet, this assumption over-simplifies the complex evolutionary process. For example, in case of protein coding genes, the third nucleotide position of codons usually evolve faster than the first and second position. Additionally, some sites may be resistant to change due to strong selective constraints: the mutation of a specific site may result in the loss of a unique property that the species needs to survive in its ecological niche. The mutated gene would therefore never be observed in the wild. Hence, accounting for rate heterogeneity is important when modeling the evolutionary process. In fact, several studies have shown that ignoring rate variation among sites can have a devastating impact on

the results of phylogenetic analyzes [15, 49, 159].

Rate heterogeneity can be incorporated into evolutionary models by modifying the substitution rates by an additional relative rate component r, i.e., by multiplying Q by r. Note that, only r varies from site to site, whereas Q is fixed. The respective substitution probability matrix P(t,r) can then be calculated with

$$P(t,r) = e^{rQt} (2.10)$$

In the simplest case, each site k is assigned an individual rate  $r_k$ . Typically, such an assignment would be based on some a priori classification of sites into functional categories and an assignment of relative rates to these categories. For example, in case of the above mentioned protein coding genes, the categorizations might be (first, second) and third codon position. However, finding suitable categorizations and manually estimating the relative rates of the categories can be difficult and may also bias the phylogenetic analysis. Hence, several approaches have been proposed to automate this process. G. Olsen developed a program for nucleotide sequences which performs a maximum likelihood estimate of the individual per site rates for a fixed tree topology (DNArates [107]). Additionally, there are several stochastic models available that account for rate heterogeneity. In these models, the rate r for any site is a random variable drawn from a – either discrete or continuous – statistical distribution.

#### 2.3.3.1 Discrete-Rates Model

In case of the discrete distribution of rates it is assumed that sites fall into K classes of different rates. Each site falls into class k and thus has the rate parameter  $r_k$  with probability  $p_k$ , k = 1, 2, ..., K. The probabilities sum to  $1 (\sum p_k = 1)$  and the average rate is  $\sum p_k r_k = 1$ .

A special case of a discrete-rates model is the *invariable-sites* model as implemented in HKY85, which assumes two classes of sites: variable sites and invariable sites. The rate of invariable sites is  $r_0 = 0$  and their proportion is  $p_0$ . As the average rate needs to be 1, the rate of variable sites is  $r_1 = (1 - p_0)^{-1}$ .

#### 2.3.3.2 Gamma-Rates Model

The best known continuous distribution for modeling rate variation among sites is the  $\Gamma$  distribution model proposed by Z. Yang [157]. Note that, the choice of the  $\Gamma$  distribution is arbitrary and any other continuous distribution could be used. However, the use of the  $\Gamma$  distribution has meanwhile been well studied and proven to be appropriate.

The  $\Gamma$  density function is

$$g(r;\alpha,\beta) = \frac{\beta^{\alpha} r^{\alpha-1} e^{-\beta r}}{\Gamma(\alpha)}.$$

(2.11)

Generally, the  $\Gamma$  distribution is parametrized by the shape parameter  $\alpha$  and the scale parameter  $\beta$ . However,  $\beta$  is set to  $\alpha$  in order to obtain a mean distribution rate of 1 and thus maintain Q's mean substitution rate of 1. The  $\alpha$  parameter is inverse to the coefficient of variation of the substitution rate, i.e., a low  $\alpha$  means high rate variation, a high  $\alpha$  means low rate variation. For  $\alpha \to \infty$  the distribution degenerates into a model of a single rate for all sites.

#### 2.3.3.3 Discrete-Gamma Model

Yang also proposed an approximation for the Gamma-Rates Model, known as the discrete  $\Gamma$  model [158]. In this model, the continuous rate distribution is approximated with a discrete distribution: the sites are divided into K equally probable rate categories, i.e.,  $p_k = 1/K$ . The rate  $r_k$  of each category is represented by the mean of the rates falling into that category.

Yang showed that approximating the  $\Gamma$  distribution by 4 discrete rates, achieves similar results for most real world datasets, but significantly reduces computational requirements. Consequently, the discrete  $\Gamma$  model is used instead of the continuous  $\Gamma$  model in most programs for phylogenetic inference.

### 2.4 Distance Methods

Distance methods do not use the actual molecular sequence alignment during the tree inference but calculate a symmetric  $n \times n$  matrix from the input alignment in the beginning. The entries of this matrix are the pairwise-distances of the n sequences. The actual tree inference is then performed solely on the basis of this matrix. For computing the matrix a distance function  $\delta(S_i, S_j)$  i, j = 1, ..., n is required that provides a measure for the genetic distance of each pair of the n sequences in the input alignment. In the simplest case this function would only count the number of differing characters of the two sequences. More elaborate functions, however, utilize a sophisticated model of molecular evolution as described in the previous section. The most frequently used distance-based approaches are probably the LS (Least-Squares) method [23] and the UPGMA (Unweighted Pair Group Method with Arithmetic Mean) [130] and NJ (Neighbor-Joining) [126] heuristics.

#### 2.4.1 Least-Squares

The Least-Squares method estimates the branch lengths of a tree topology by matching the distances described by them as closely as possible to the values of the pairwise distances matrix. This is achieved by minimizing the sum of squared differences between the given (by the distances matrix) and the predicted distances. The predicted distance between two sequences is calculated as the sum of the branch lengths along the path connecting both of them. The sum of all squared differences represents a measure for the fit of the tree to the given sequence data: the tree with the minimal sum is the optimal tree. The complexity of LS is  $O(n^3)$ .

#### 2.4.2 **UPGMA**

UPGMA is a clustering algorithm that builds a rooted tree topology by stepwise addition. A molecular clock is assumed for the evolutionary process, which means that all species contained in the phylogenetic tree are supposed to evolve at the same rate. This assumption leads to the fact that trees obtained by UPGMA are ultrametric trees, that is, all end nodes (representing the species of interest) are equidistant from the root.

The algorithm works as follows: In the beginning, each node represents a cluster. At each step, the two clusters whose associated sequences have minimal distance according to the distance matrix are joined. Their entries are removed from the matrix and an entry for the new cluster is added. The distance of the new cluster to other clusters is computed as the mean distance of the sequences contained in each cluster. The algorithm terminates when all clusters have been joined into a single cluster. The complexity of UPGMA is  $O(n^2)$ .

### 2.4.3 Neighbor-Joining

Neighbor-Joining is also a clustering algorithm and is based on the minimum-evolution criterion. The tree that explains the sequence data with the minimal amount of change, i.e., the tree which minimizes the sum of all branch lengths (the total tree length), is the optimal tree.

The algorithm starts with a star-tree. At each step, two nodes are removed from the tree and reconnected via a common newly added internal node. The distance of both nodes to any other node of the tree (i.e., the sum of the branch lengths on the path connecting the nodes) stays constant. Yet, the total tree length is reduced as two rather long branches are replaced by three shorter branches. The nodes to be reorganized are selected such that the greatest reduction of the tree length is achieved. This procedure is repeated until the tree is fully resolved.

The complexity of the original NJ implementation is  $O(n^3)$  which can be reduced to  $O(n^2)$  by using a more sophisticated algorithm for selecting the nodes to be joined [162].

#### 2.4.4 Objections Against Distance Methods

The main objection against distance methods is the fact that transforming the input alignment to a simple distance matrix at a very early stage of the tree reconstruction process evidently neglects information which might be valuable for inferring the relationships between the species being analyzed.

Furthermore, UPGMA as well as NJ are greedy algorithms. By their nature, such algorithms behave optimally only locally at each step of the iterative process. The final result, however, might not be optimal with regard to the underlying optimality criterion.

The molecular clock that is assumed by UPGMA probably oversimplifies the evolutionary process. While this assumption might be suitable for closely related species, the clock is often violated if the sequences are divergent.

The minimum-evolution criterion applied by NJ implies that mutations of molecular bases are always minimal, e.g., that a DNA mutation  $A \to C$  always happens directly and not via a detour  $A \to G \to C$ . Potentially unobserved mutations (e.g.  $A \to G \to A$ ) are also neglected.

In the strict sense, the Least-Squares method is not a method for inferring a tree topology for a given sequence alignment but for evaluating the fit of a given topology to the alignment. Consequently, it additionally requires a proposal algorithm that provides suitable tree topologies for evaluation. As pointed out in Section 2.2, the number of possible tree topologies grows factorially with the number of sequences. Though LS is a distance-based method, the main

benefit of these methods – their speed – is negligible as the computational complexity of a tree inference under LS will be imposed by the search algorithm.

## 2.5 Maximum Parsimony

Maximum Parsimony [45] favors the tree topology which explains the given data (the multiple sequences alignment) with the least amount of change, i.e., the lowest number of nucleotide or amino acid substitutions. In this sense, it is similar to the minimum-evolution criterion of NJ. However, MP computes the distance between two sequences on a per-column (per-site) basis and considers only so-called informative sites. Those are the columns of the sequence alignment that contain at least two different kinds of characters, each of which is represented in at least two of the sequences. The distance between two sequences is the number of differing characters at informative sites and is attributed as weight to the branch connecting the two sequences. For the inner nodes of the tree hypothetical sequences are calculated such that the distances between an inner node and its adjacent nodes are minimal. The Maximum Parsimony score of a tree can be calculated by summing up the weights of all branches. The tree with minimal score is the most parsimonious tree and thus the optimal tree under the Maximum Parsimony optimality criterion.

Since the Maximum Parsimony criterion is very similar to the minimum-evolution criterion, it also suffers from identical shortcomings (see Section 2.4). Additionally, the phenomenon of so-called long branch attraction [41] can be observed on MP-inferred phylogenies: sequences which are connected to the tree by very long branches, might be grouped together though they developed from very different lineages. Long branches indicate a high rate of change, i.e., the sequence at the terminal node of the branch differs from the hypothetical sequence at the internal node in many sites. Maximum Parsimony only accounts for the fact that some substitution took place at a specific site and not which substitution. Thus, it groups the two nodes with the long branches together solely because both highly differ from the other sequences. The fact that both of them also are highly different to each other is neglected.

Nevertheless, Maximum Parsimony is still frequently used for phylogenetic inference for several reasons [56]: Firstly, it is a character-based method and as such considered to be superior to distance methods at it uses all information that is contained in the input alignment for the tree reconstruction. Secondly, it is fast and therefore an alternative to Maximum Likelihood for large-scale datasets if computational resources are restricted. Thirdly, the phenomenon of *long branch attraction* is only an issue for small datasets. Fourthly, many biologists appreciate the fact that MP only makes few assumptions about the evolutionary process besides evolutionary change being rare.

#### 2.6 Maximum Likelihood

In general, Maximum Likelihood is a parametric statistical method for fitting a mathematical model to some data. The principle of likelihood suggests that the explanation that makes the observed outcome the most likely occurrence is the one to be preferred. Formally, given some data D and a hypothesis  $\theta$ , the likelihood of that data is given by

$$L(D;\theta) = f(D|\theta) \tag{2.12}$$

which is the probability of obtaining D given  $\theta$ . Though both terms are colloquially used synonymously, it is important to distinguish between probability and likelihood here. Informally, probability allows one to predict unknown outcome based on known parameters, whereas likelihood allows one to predict unknown parameters based on known outcome. In the context of phylogenetic inference, D is the (known) input alignment and the (unknown) hypothesis  $\theta$  the combination of a phylogenetic tree and a model of molecular evolution along with its parameters. Thus,  $L(D;\theta)$  describes how likely it is that the observed molecular sequences contained in the input dataset could have emerged from a specific phylogenetic tree under a specific model of evolution. More formally,  $\theta$  comprises a tree topology  $\tau$ , a parameter vector  $\nu$  containing all branch lengths and a vector  $\phi$  of evolutionary model parameters.

The absolute likelihood value has no specific meaning and does not allow for any conclusion whether the given phylogenetic tree actually is the true tree. It is only meaningful for comparing several trees to each other: the one with the highest likelihood value explains the given data the best. Thus, the two problems which need to be resolved are:

- 1. Which parameters  $\nu$  and  $\phi$  make the observed data D more likely for a given tree topology  $\tau$ ?

- 2. Which tree topology  $\tau_i$  of all possible tree topologies  $\tau_{1...n}$  yields the highest likelihood?

In order to find the optimal phylogenetic tree – under this specific optimality criterion – one would have to create and evaluate all possible tree topologies. As already pointed out in Section 2.2, the number of possible tree topologies grows factorially with the number of organisms in the input dataset. Evaluating all possible tree topologies, i.e., optimizing  $\nu$  and  $\phi$  and calculating the likelihood score, therefore is not an option for more than 10 organisms. Instead, elaborate heuristics are required that significantly reduce the search space but still approximate the optimal tree topology. Some approaches to this problem will be discussed in more detail in Section 2.9.

#### 2.6.1 The Phylogenetic Likelihood Function

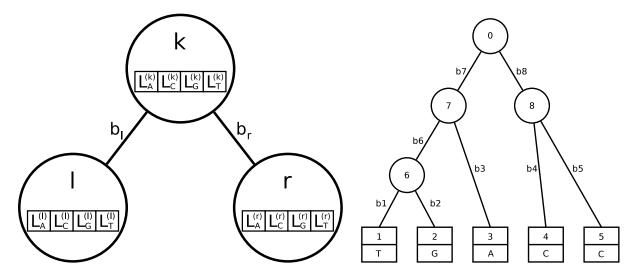

Calculating the actual likelihood score of a given tree topology is the essential step to infer trees under the Maximum Likelihood criterion. This computation is carried out according to Felsenstein's pruning algorithm [42]: at each node k, the conditional probability  $L_{s_k}^{(k)}$  is calculated, which describes the probability of observing the data at the descendants of node k given the data at node k is  $s_k$ , with  $s_k \in \{A, C, G, T\}$ . As mentioned in Section 2.1, the species contained in the input sequence alignment along with their actual sequence data are stored at the tips of the tree. These are called operational taxonomic units (OTU). The internal nodes

Figure 2.1: Computation of the conditional probabilities vector at an internal node k from the vectors of its child nodes l and r.

Figure 2.2: A rooted 5 taxon tree

represent common, probably extinct ancestors for which we have no sequence data and are hence called hypothetical taxonomic units (HTU). The unavailability of sequence data for the internal nodes is the reason why we need to compute the conditional probabilities. Casually speaking, we consecutively assume that k has state A, C, G, T and compute the respective probabilities of the child nodes effectively having the nucleotide states as given by the input alignment. So we need to compute four conditional probabilities  $L_{s_k}^{(k)}$  – one for each of the four feasible nucleotide states – which are combined to a vector of conditional probabilities  $\vec{L}^{(k)} = [L_A^{(k)}, L_C^{(k)}, L_C^{(k)}, L_T^{(k)}]$ .

Since different nucleotide sites are assumed to evolve independently of each other (see Section 2.3), the conditional probabilities can be calculated site-by-site by iterating over the sequence alignment columns. Therefore, we will only examine the process of computing the conditional probabilities and the likelihood score for a specific site of the sequence alignment and will extend this to the whole alignment at the end of this section.

The individual entries of the conditional probabilities  $\vec{L}^{(k)}$  are computed as follows: if the node k is a tip with state s, the conditional probabilities are:

$$L_{s_k}^{(k)} = \begin{cases} 0, & s_k \neq s \\ 1, & s_k = s. \end{cases}$$

(2.13)

A special case are sequence positions that contain ambiguous characters, i.e., characters that do not encode one of the four DNA bases A, C, G, T but multiple bases simultaneously. In this case,  $L_{s_k}^{(k)}$  is set to 1 for all bases that are encoded by the ambiguous character. If k is an internal node, with descendants l and r and the corresponding branch lengths  $b_l$  and  $b_r$  (see

Figure 2.1 for a schematic representation), the conditional probability can be computed as

$$L_{s_k}^{(k)} = \left[ \sum_{s_l=A}^T p_{s_k s_l}(b_l) L_{s_l}^{(l)} \right] \times \left[ \sum_{s_r=A}^T p_{s_k s_r}(b_r) L_{s_r}^{(r)} \right].$$

(2.14)

Since all descendant tips of node k are either descendants of its immediate child nodes l or r, the probability  $L_{s_k}^{(k)}$  of observing the data at the descendant tips of k given  $s_k$  is equal to the probability of observing the data at the descendant tips of l given  $s_k$  times the probability of observing the data at the descendant tips of r given  $s_k$ . These are the terms within the two pairs of brackets of equation (2.14). The left bracket corresponds to child node l and the right bracket corresponds to r. Thus, the left term describes the probability  $p_{s_k s_l}(b_l)$  that  $s_k$  will evolve into  $s_l$  over time  $s_l$  times the probability  $s_l$  of observing the data at  $s_l$  is tips given the state  $s_l$ , summed over all possible states  $s_l \in A, C, G, T$ . The same applies to the right bracket accordingly.

In order to compute the likelihood score of the tree, one needs to compute the conditional probability vectors for all nodes of the tree. This can be done bottom-up from the tips to the root, i.e., by a post-order tree traversal.

In the following, we will use the sample tree depicted in Figure 2.2 to outline Felsenstein's pruning algorithm. The rectangles denote terminal nodes (numbered 1 to 5), while internal nodes (numbered 6 to 8) as well as the root (numbered 0) are represented by circles. The terminal nodes additionally show the associated species' nucleotide characters of an arbitrary site as given by the input matrix. The branch lengths  $b_1..b_8$  represent the expected number of nucleotide substitutions per site and are fixed for the likelihood computation.

Node 1 and 2 are tips with state T and G, hence  $\vec{L}^{(1)} = [0,0,0,1]$  and  $\vec{L}^{(2)} = [0,0,1,0]$ . This allows for computation of  $\vec{L}^{(6)}$ :

$$L_{s_6}^{(6)} = \left[ \sum_{s_1=A}^{T} p_{s_6 s_1}(b_1) L_{s_1}^{(1)} \right] \times \left[ \sum_{s_2=A}^{T} p_{s_6 s_2}(b_2) L_{s_2}^{(2)} \right]$$

$$= p_{s_6 T}(b_1) \times p_{s_6 G}(b_2)$$

(2.15)

With  $\vec{L}^{(3)} = [1, 0, 0, 0]$ :

$$L_{s_7}^{(7)} = \left[ \sum_{s_6 = A}^{T} p_{s_7 s_6}(b_6) L_{s_6}^{(6)} \right] \times \left[ \sum_{s_3 = A}^{T} p_{s_7 s_3}(b_3) L_{s_3}^{(3)} \right]$$

$$= \left[ \sum_{s_6 = A}^{T} p_{s_7 s_6}(b_6) p_{s_6 T}(b_1) p_{s_6 G}(b_2) \right] \times p_{s_7 A}(b_3)$$

(2.16)

$\vec{L}^{(8)}$  can be computed from  $\vec{L}^{(4)} = [0, 1, 0, 0]$  and  $\vec{L}^{(5)} = [0, 1, 0, 0]$ :

$$L_{s_8}^{(8)} = \left[ \sum_{s_4=A}^T p_{s_8 s_4}(b_4) L_{s_4}^{(4)} \right] \times \left[ \sum_{s_5=A}^T p_{s_8 s_5}(b_5) L_{s_5}^{(5)} \right]$$

$$= p_{s_8 C}(b_4) \times p_{s_8 C}(b_5)$$

(2.17)

And finally, the probability vector  $\vec{L}(0)$  at the root can be computed with:

$$L_{s_{0}}^{(0)} = \left[\sum_{s_{7}=A}^{T} p_{s_{0}s_{7}}(b_{7})L_{s_{7}}^{(7)}\right]_{7} \times \left[\sum_{s_{8}=A}^{T} p_{s_{0}s_{8}}(b_{8})L_{s_{8}}^{(8)}\right]_{8}$$

$$= \left[\sum_{s_{7}=A}^{T} p_{s_{0}s_{7}}(b_{7})\left(\sum_{s_{6}=A}^{T} p_{s_{7}s_{6}}(b_{6})L_{s_{6}}^{(6)}\right)\left(\sum_{s_{3}=A}^{T} p_{s_{7}s_{3}}(b_{3})L_{s_{3}}^{(3)}\right)\right]_{3} \times \left[\sum_{s_{8}=A}^{T} p_{s_{0}s_{8}}(b_{8})\left(\sum_{s_{4}=A}^{T} p_{s_{8}s_{4}}(b_{4})L_{s_{4}}^{(4)}\right)\left(\sum_{s_{5}=A}^{T} p_{s_{8}s_{5}}(b_{5})L_{s_{5}}^{(5)}\right)\right]_{5} \right]_{8}$$

$$= \left[\sum_{s_{7}=A}^{T} p_{s_{0}s_{7}}(b_{7})\left(\sum_{s_{6}=A}^{T} p_{s_{7}s_{6}}(b_{6})\left(p_{s_{6}T}(b_{1})\right)\left(p_{s_{6}G}(b_{2})\right)\right)\right]_{2} + \left(\sum_{s_{7}=A}^{T} p_{s_{9}s_{8}}(b_{8})\left(p_{s_{8}C}(b_{4})\right)\left(p_{s_{8}C}(b_{5})\right)\right)_{5} = 0$$

$$\left[\sum_{s_{8}=A}^{T} p_{s_{9}s_{8}}(b_{8})\left(p_{s_{8}C}(b_{4})\right)\left(p_{s_{8}C}(b_{5})\right)\right]_{5} = 0$$

$$(2.18)$$

For better readability, the terms have been grouped according to the tree structure. Round brackets indicate terminal nodes, whereas square brackets and the curly brackets describe internal nodes. The numerical subscripts correspond to the respective node numbers.

Once the conditional probability vectors for all nodes have been computed, the likelihood score for a specific site S can be computed at the root by means of:

$$f(S|\theta) = \sum_{s_0=A}^{T} \pi_{s_0} L_{s_0}^{(0)}$$

(2.19)

Here,  $\theta$  incorporates the parameters of the respective model of sequence evolution as well as the branch lengths of the tree. For the computation of the likelihood score,  $\theta$  is assumed to be fixed.  $\pi_{s_0}$  is the prior probability that the root has state  $s_0$  as given by the base frequency of the specific nucleotide under the chosen model.

The overall likelihood score of the tree can be calculated by multiplying  $f(S|\theta)$  over all m sites:

$$L = \prod_{S=0}^{m-1} f(S|\theta). \tag{2.20}$$

However, since all entries  $p_{ij}$  of the substitution probability matrix are  $\leq 1$ , the individual  $L_{s_k}^{(k)}$

values and consequently the  $f(S|\theta)$ 's can be very small. Hence, the log likelihood l is computed instead of L:

$$l = log(L) = \sum_{S=0}^{m-1} log(f(S|\theta)).$$

(2.21)

### 2.6.2 The Pulley Principle

As pointed out in Section 2.3.1, most evolutionary models utilize time-reversible Markov chains. Reversibility means that the Markov chain does not distinguish whether time is running forward or backward. With equation (2.4) this implies that

$$\pi_i p_{ij}(t) = \pi_i p_{ii}(t), \text{ for all } i \neq j.$$

(2.22)

Another feature of Markov chains is expressed by the Chapman–Kolmogorov equation which states that

$$p_{ij}(b_1 + b_2) = p_{ik}(b_1)p_{kj}(b_2). (2.23)$$

This allows for an important property for the computation of the *phylogenetic likelihood function* which Felsenstein called the *pulley principle*. It allows for placing the root anywhere within the tree with no effect on the likelihood score of the tree. This is important for two reasons: firstly, it allows us to easily root any unrooted tree just by inserting a *virtual root* into any branch of the tree. Secondly, it allows us to maximize the likelihood score of the tree by optimizing its branch lengths (see Section 2.6.3.1 for more details).

For example, combining equations (2.18) and (2.19) results into:

$$f(S|\theta) = \sum_{s_0=A}^{T} \sum_{s_7=A}^{T} \sum_{s_8=A}^{T} \pi_{s_0} p_{s_0 s_7}(b_7) L_{s_7}^{(7)} p_{s_0 s_8}(b_8) L_{s_8}^{(8)}.$$

(2.24)

With equation (2.22) we can replace  $\pi_{s_0}p_{s_0s_7}(b_7)$  by  $\pi_{s_7}p_{s_7s_0}(b_7)$  and with equation (2.23)  $\sum_{s_0} p_{s_7s_0}(b_7)p_{s_0s_8}(b_8) = p_{s_7s_8}(b_7 + b_8)$  holds. Hence, we have

$$f(S|\theta) = \sum_{s_7=A}^{T} \sum_{s_9=A}^{T} \pi_{s_7} p_{s_7 s_8} (b_7 + b_8) L_{s_7}^{(7)} L_{s_8}^{(8)}.$$

(2.25)

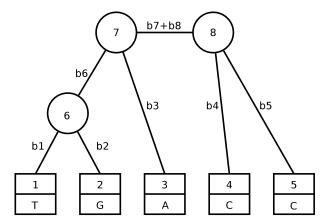

This obviously corresponds to the likelihood score of the unrooted tree as depicted by Figure 2.3 which can be derived from the rooted counterpart of Figure 2.2 by removing the root at node 0 and merging the branches connecting node 7 and 8 to a single branch with length  $b_7 + b_8$ . Or, if looked at in the opposite direction, this allows for adding a *virtual root* to the unrooted tree by splitting the branch between nodes 7 and 8 and inserting a new node. In fact, adequate application of equations (2.22) and (2.23) shows that the *virtual root* can be placed on any branch of the tree.

Another interesting observation that can be made from equation (2.25) is the fact that the likelihood score only depends on  $b_7$  and  $b_8$  via their sum. As a consequence, equation (2.24)

Figure 2.3: An unrooted 5 taxon tree

can be rewritten to

$$f(S|\theta) = \sum_{s_0=A}^{T} \sum_{s_7=A}^{T} \sum_{s_8=A}^{T} \pi_{s_0} p_{s_0 s_7}(b_7 + x) L_{s_7}^{(7)} p_{s_0 s_8}(b_8 - x) L_{s_8}^{(8)}.$$

(2.26)

Thus, the root can be placed anywhere on the branch between node 7 and node 8 and will always yield the same likelihood score as long as  $b_7 + b_8$  remain constant. This is the reason why Felsenstein called it the *pulley principle*. The *virtual root* can be regarded as a pulley and all components to both sides of the pulley can be moved up and down without altering the likelihood score of the tree as long as they are moved by the same amount on both sides.

#### 2.6.3 Optimization of the Likelihood Score

As already pointed out in the beginning of this section, the goal of phylogenetic tree inference under the ML criterion is to find the one phylogenetic tree with the highest likelihood score. The score, however, is not only influenced by the tree topology itself, but also by the branch lengths of the tree as well as the parameters of the evolutionary model. In that sense, both the branch lengths and the model parameters can be considered as parameters of the likelihood function. The Maximum Likelihood approach allows us to estimate these parameters so that the highest likelihood score for a given tree topology is achieved.

For the purpose of maximizing the likelihood score, the tree topology is assumed to be fixed and only the parameters are to be modified. Although the parameters of the likelihood function comprise the branch lengths  $\nu$  and the model parameters  $\phi$ ,  $\nu$  and  $\phi$  are usually optimized separately for several reasons. Most importantly, the computational costs of the optimization increase with the number of parameters to be optimized. Since the branch lengths and the model parameters are not strongly correlated for most evolutionary models, a multivariate estimation of both is not necessarily required. Estimating  $\nu$  and  $\phi$  separately therefore saves computing time. Additionally, the branch lengths need to be optimized after each change to

the tree topology. As most programs for phylogenetic tree inference implement hill-climbing algorithms that frequently remove and re-insert subtrees, the branches need to be optimized very frequently. The model parameters on the other hand need to be optimized less frequently during the tree search: in the initial phase of the tree search they quickly converge to their optima and stay rather constant once a "reasonable" tree topology has has been established. Note, however, that typically not all branches of the tree are recomputed after topological modifications in most heuristics but only the branches of the surrounding nodes in order to reduce the computational effort.

#### 2.6.3.1 Branch Length Optimization

Due to the numerical complexity of multivariate optimization techniques, the branch lengths are usually optimized one by one. The model parameters as well as all branches except the one branch to be optimized are assumed to be fixed. The optimization of the branch can then be performed by exploiting the *pulley principle*. It allows for placing a virtual root on any branch of the tree and guarantees that the likelihood score of the tree will only depend on the lengths of the branches leading to the virtual root.

If we consider the unrooted tree of Figure 2.3 and assume we want to optimize the length of the branch connecting node 7 with node 8, we would place the virtual root on that branch. Eventually, we would obtain the rooted tree of Figure 2.3 with node 0 being the virtual root. Yet, we would place the virtual root immediately besides node 8 such that  $b_8 = 0$ . As the likelihood score of the tree depends on  $b_7$  and  $b_8$  via their sum, it effectively only depends on  $b_7$  as can be seen by inserting  $b_8 = 0$  into equation (2.24). Generally, for any two nodes i and j and their connecting branch with length b, this equation can be rewritten to

$$f(S|\theta) = \sum_{s_i=A}^{T} \sum_{s_j=A}^{T} \pi_{s_i} p_{s_i s_j}(b) L_{s_i}^{(i)} L_{s_j}^{(j)}.$$

(2.27)

The likelihood score of the tree can then be optimized by altering b accordingly.

Most univariate optimization methods require at least the first partial and second partial derivatives of the objective function – in our case the likelihood function – with respect to the parameter to be optimized for finding the minimum and maximum values of the function. With equation (2.27) the first and second derivatives of l with respect to b can be calculated analytically (see [160]), which facilitates the application of many univariate methods for optimizing the branch lengths. In practice the *Newton-Raphson* method is often used for this task due to its favorable convergence properties. Appropriate algorithms are discussed in almost any textbook on numerical optimization (see [46] for example).

#### 2.6.3.2 Model Parameter Optimization

The parameters of the evolutionary model that need to be estimated usually comprise the rate parameters of the substitution rate matrix (a, ..., e for GTR, f is usually fixed to 1) and

optionally the parameters that account for rate heterogeneity among sites. In the case of a discrete-rates model, these are the rates  $r_k$  as well as the probabilities  $p_k$ . For the continuous as well as the discrete gamma-rates model only the shape parameter  $\alpha$  needs to be estimated ( $p_k$  is fixed in case of the discrete gamma-rates model).

As the rate parameters are correlated they should be optimized simultaneously by means of a multivariate optimization method [161]. However, since no analytical solution for the partial derivatives of the likelihood function with respect to the rate parameters exists, they would have to be approximated by the difference method which is computationally very expensive. Though derivative-free optimization methods could be used instead, in practice they are not applied to this task as they impose similar computational effort but are considered to be less efficient [54]. Consequently, multivariate optimization methods like Newton-Raphson or Broyden-Fletcher-Goldfard-Shanno (BFGS) are typically not used for this task but univariate optimization techniques like Brent's method [14].

The  $\alpha$  shape parameter of the gamma distribution is typically optimized with Brent's method, too. Regarding the discrete-rates model parameters, the same arguments as for the rate parameters and multivariate optimization apply. Hence, they are usually optimized individually with some univariate optimization method.

Note that, any change to the model parameters results in a modified substitution probability matrix and therefore requires all conditional probabilities at all inner nodes to be recomputed. Hence, a quickly converging optimization method is of paramount importance for an efficient implementation of the Maximum Likelihood approach.

## 2.7 Bootstrapping

Generally, nonparametric bootstrapping [32] is a method for assigning confidence values to statistical estimates. Felsenstein proposed to apply it to phylogenetic tree inference in order to obtain confidence limits on phylogenies [43]. Bootstrapping can be applied to any method for tree reconstruction, distance-based methods as well as character-based methods.

The method works as follows: A number of pseudo alignments, so-called bootstrap samples or bootstrap replicates, are generated by re-sampling sites from the original sequence alignment with replacement. The bootstrap samples have the same number of sites as the original alignment. The sites to be re-sampled are chosen randomly from the original alignment, so that some sites may be sampled multiple times while other sites may not be sampled at all. The bootstrap samples are then used in the same way as the original alignment to reconstruct phylogenetic trees, i.e., with the same algorithm and under the same evolutionary model. Afterwards, a consensus tree is built from the resulting bootstrap trees (see, e.g., [20] for a comprehensive review of consensus tree methods) that assigns support values to the individual clades of the phylogenetic tree resulting from the original alignment. A clade is a monophyletic group, i.e., a group of species consisting of a single common ancestor and all its descendants. A clade's support value is the proportion of bootstrap trees that include the clade.

While the process of bootstrapping and the computation of bootstrap support values is

straight-forward, the interpretation of the values is not. Often, the bootstrap supports are interpreted as a measure of the probability that the tree or clade is true, i.e., as a measure of accuracy. However, the only conclusion that can be drawn from bootstrapping is that the same tree or clade would be estimated from repeated sampling of the species' molecular sequences. This is the true nature of bootstrapping: instead of sequencing the species of interest multiple times and thereby creating multiple sequence alignments, we only re-sample from one single alignment and create pseudo alignments. In this sense, the bootstrap support values are a measure of repeatability. Yet, Hillis and Bull showed that under certain conditions, bootstrap proportions of over 70% usually correspond to a true clade [71] and consequently are a measure of accuracy. Many phylogeneticists have adopted the 70% value and use it as a rule of thumb. However, most of them neglect the "certain conditions" under which this value was obtained. One of the conditions is equal rate of change among sites which is an inappropriate assumption for most phylogenies as described in Section 2.3.3. In the same paper, Hillis and Bull point out that values over 50% are an overestimate of accuracy, if these conditions are not met. Hence, for most phylogenetic analyses (i.e., such that assume rate heterogeneity) a high bootstrap support does not allow for any conclusion about the correctness of the inferred tree topology. Bootstrapping does however provide "a systematic method of assessing the robustness of a data set to perturbation" as summarized by Sanderson [127].

Further discussion about the usefulness of bootstrap support values are clearly beyond the scope of this thesis. Nonetheless, most systematics journals require bootstrap support values on phylogenetic trees to be published. Consequently, the possibility to compute bootstrap support values is requested by most systematicists and has to be provided by any phylogenetic inference software if the inferred trees are to be published.

The actual implementation typically requires only little modification to existing programs as most of them already provide the possibility to assign weight values to individual sequence columns. These weights are multiplied with each site's likelihood score when computing the total likelihood score of the tree by means of equation (2.20). Due to the commutative property of the multiplication, the order of the sequence columns does not influence the tree's likelihood score. Re-sampling of the sequence alignment can therefore be easily implemented by assigning weights to the individual sites that correspond to the number of times the particular site has been sampled. For example, a site that has been sampled twice has a weight of 2, whereas a site that has not been sampled at all has a weight of 0.

Additionally to the question of how to interpret the bootstrap support values, another question that arises is "How many bootstrap replicates are enough?". Computing one single bootstrap replicate requires approximately the same runtime as a normal tree inference. As normal tree inference under Maximum Likelihood already is a very compute intensive task, the number of bootstrap replicates that are being computed is often determined by the computing power and time available. The rule of thumb is that one typically requires 100-1000 bootstrap replicates, the more the better. Pattengale et al. [115] recently proposed two stopping criteria that allow for determining when enough bootstrap replicates have been generated at runtime. They assess their approach with 17 real-world DNA datasets and conclude that typically 100-500

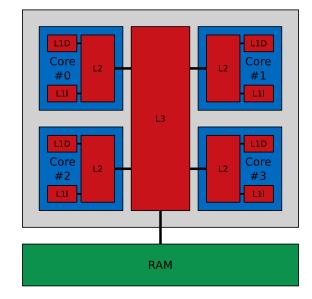

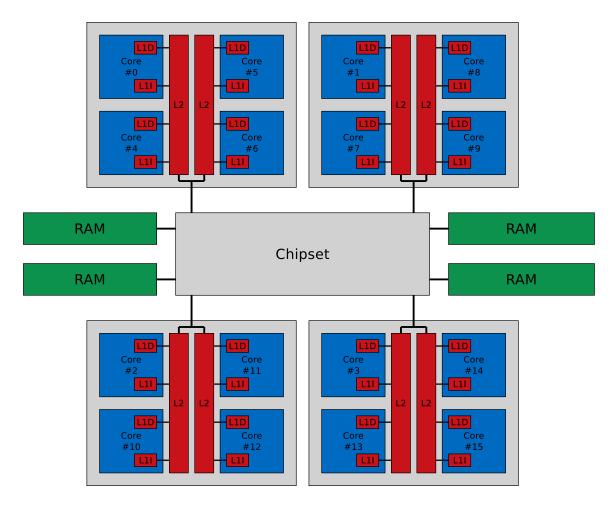

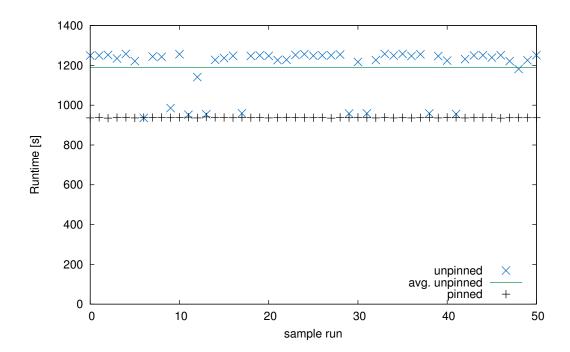

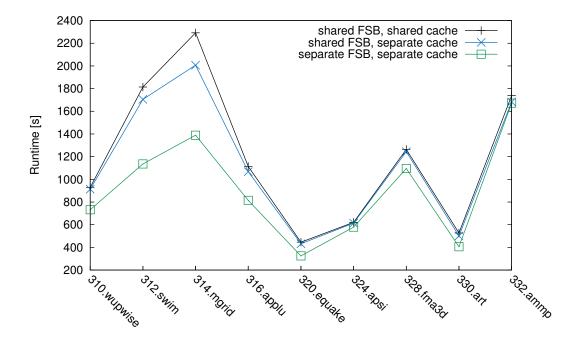

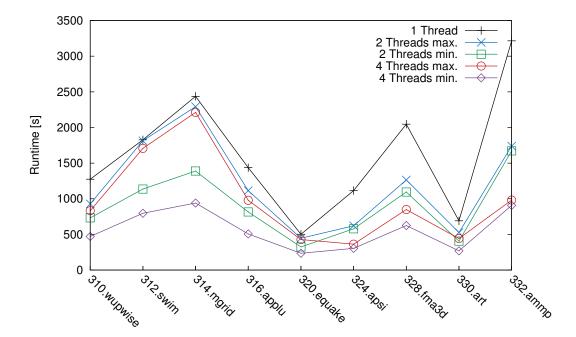

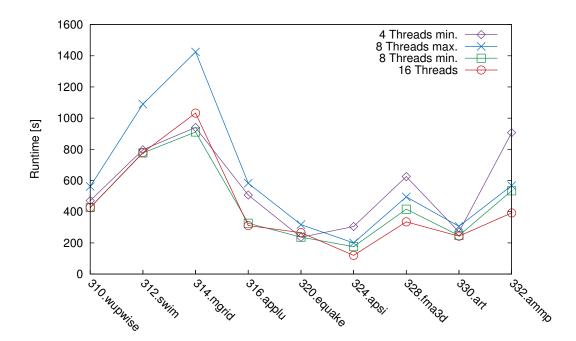

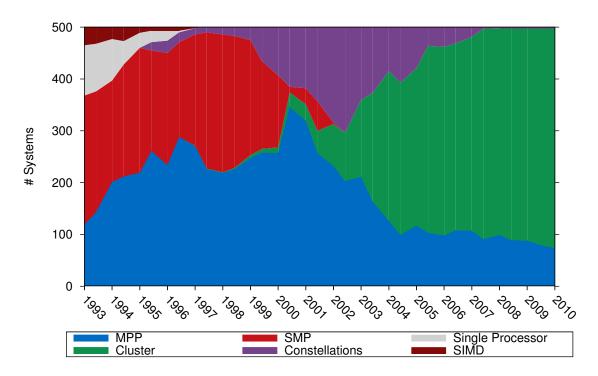

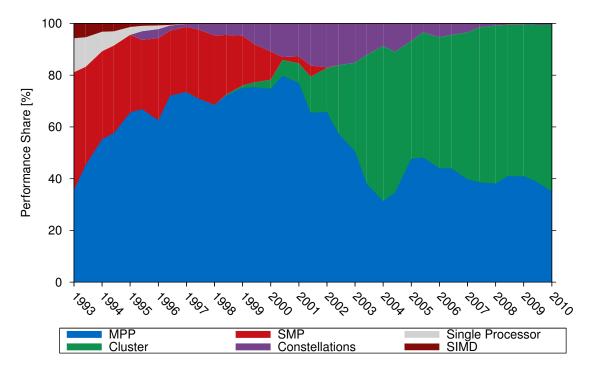

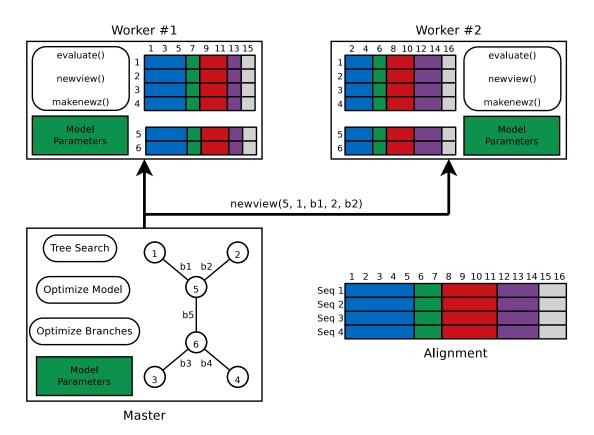

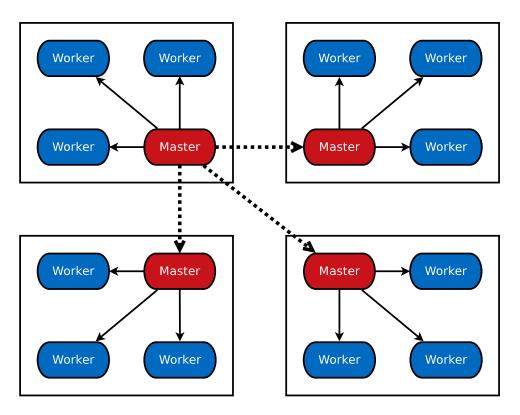

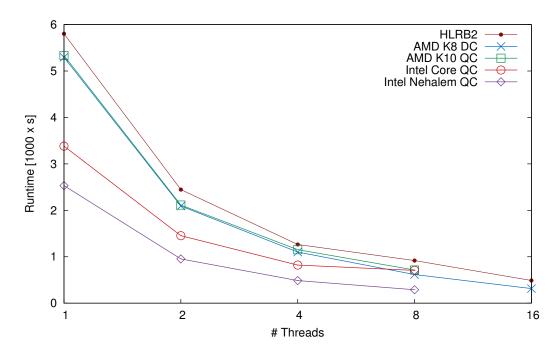

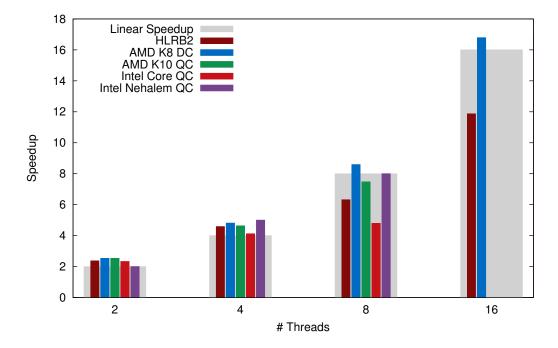

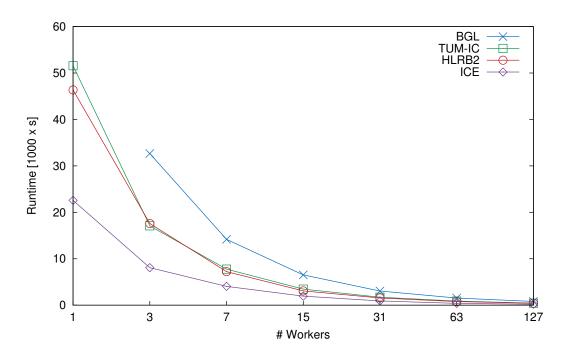

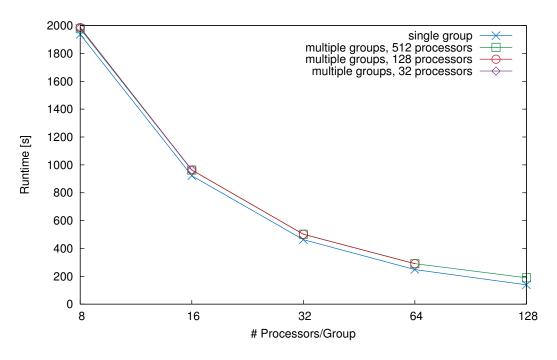

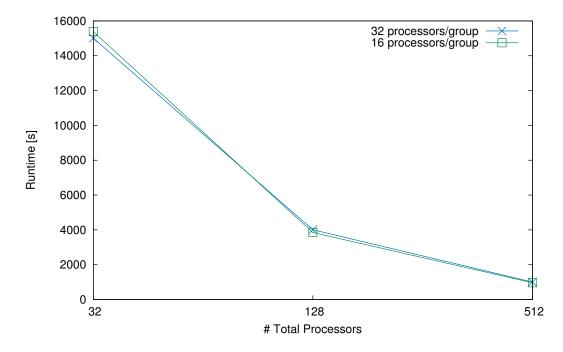

replicates are sufficient.